Изобретение относится к радиотехнике и связи, предназначено для получения синусоидальных колебаний по сигналам программного управления и может быть использовано в системах измерения и контроля.

Целью изобретения является увеличение стабильности уровня выходного напряжения.

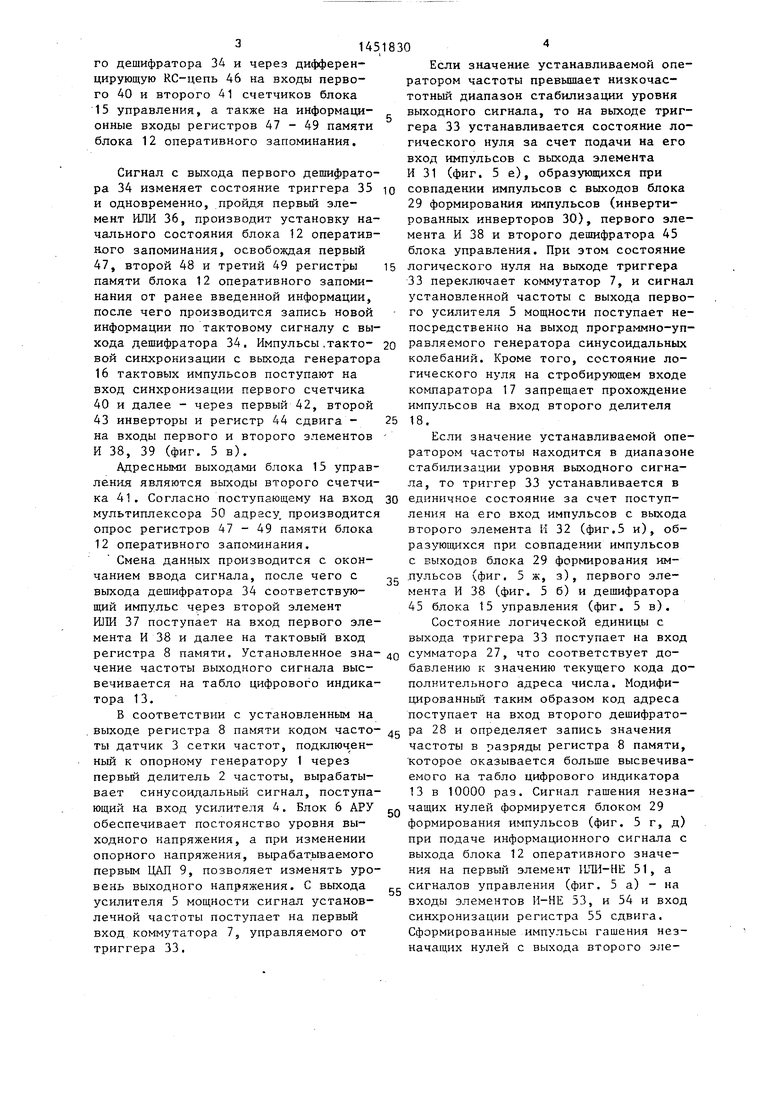

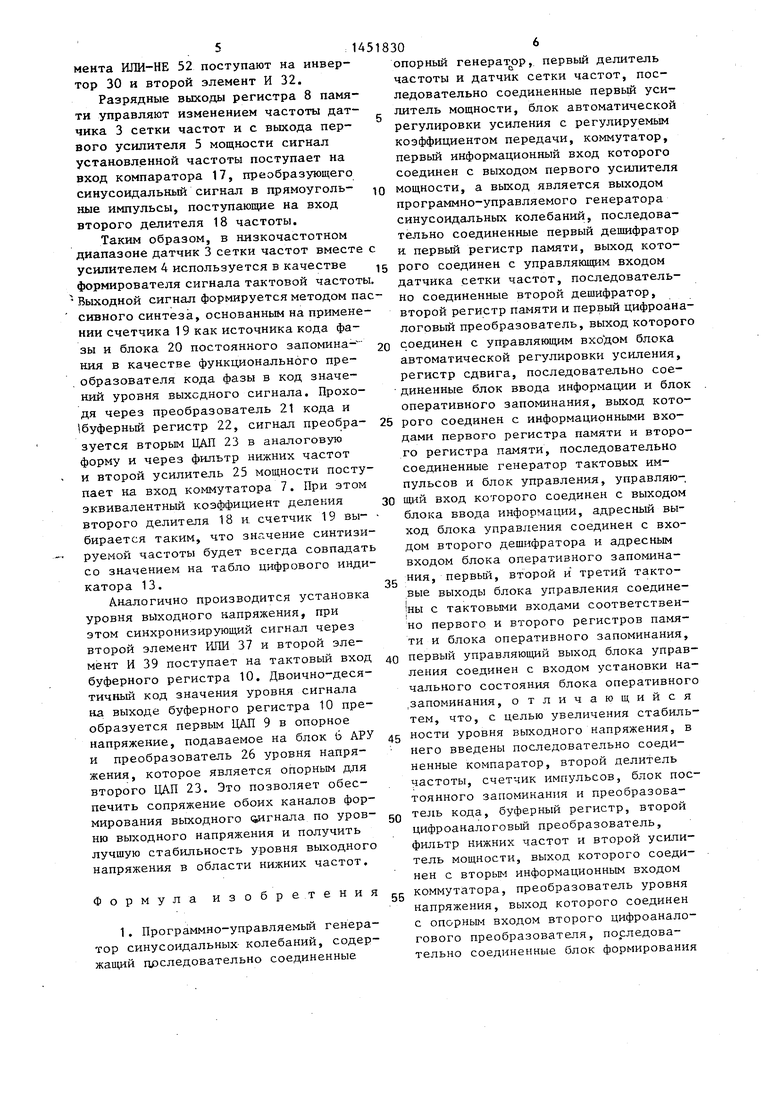

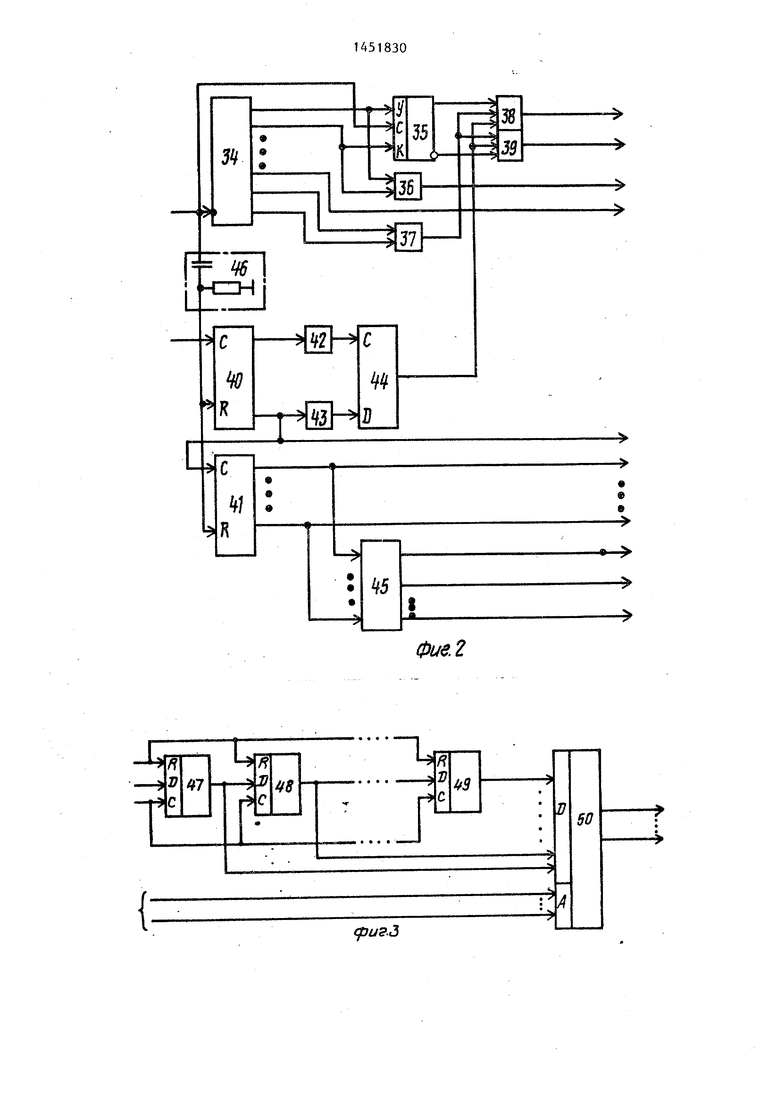

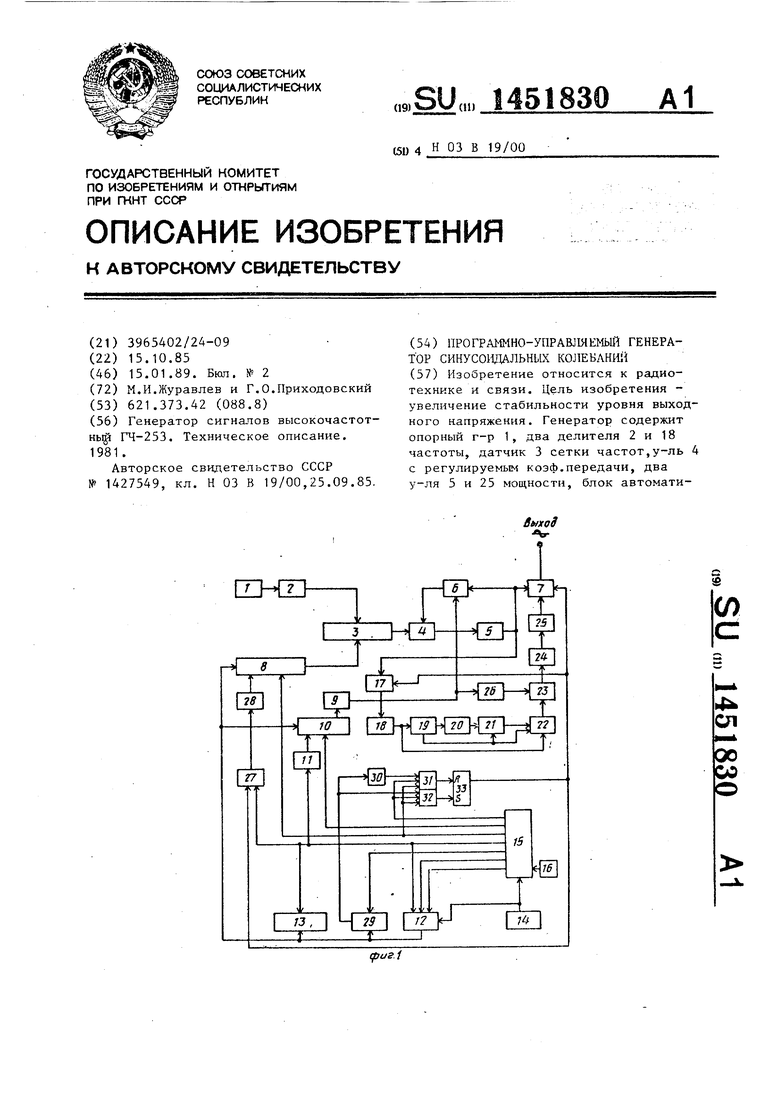

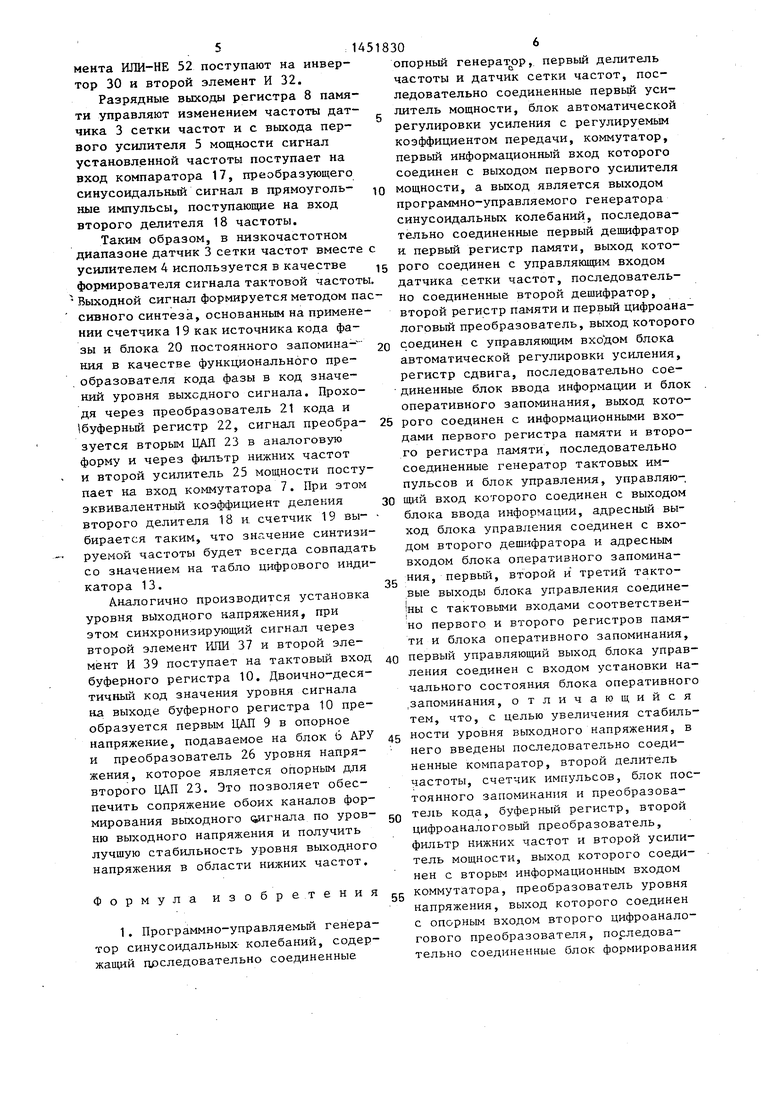

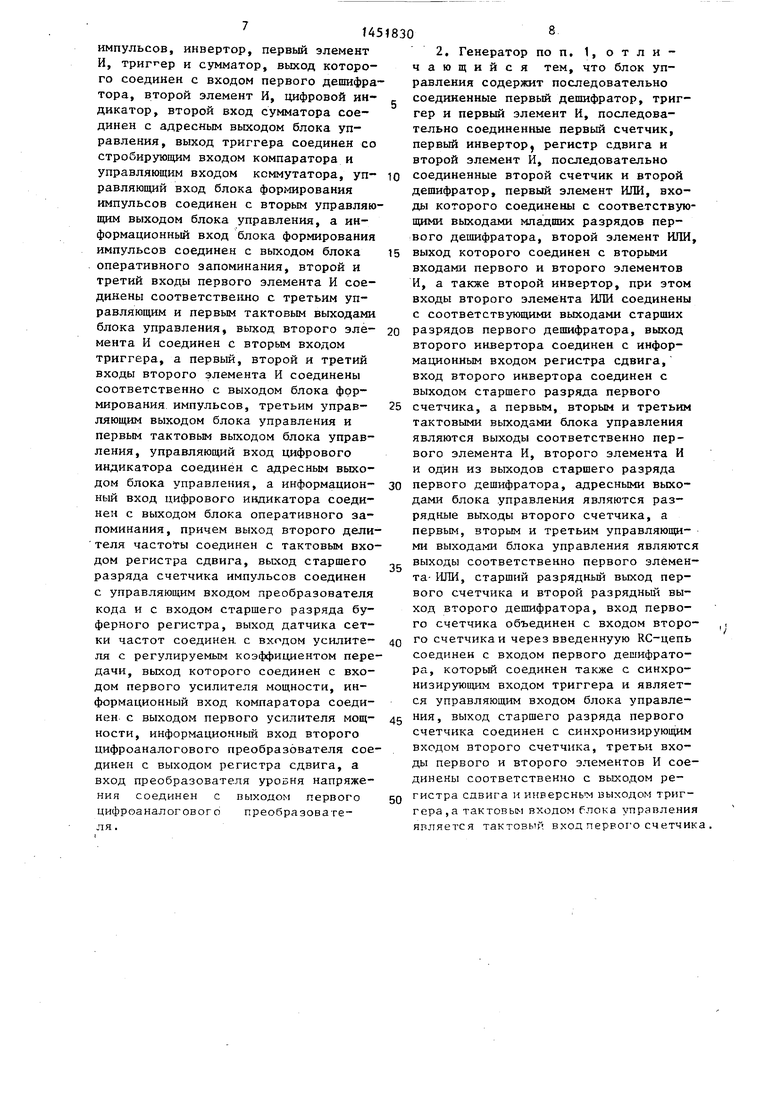

На фиг. 1 представлена структурная электрическая схема программно-управляемого генератора синусоидальных колебаний; на фиг. 2 - то же, блока управления; на фиг. 3 - то же, блока оперативного запоминания; на фиг. 4 то же,блока формирования импульсов; на фиг. 5 а, б, в, г, д, е, ж, з, и временные диаграммы, поясняющие работу программно-управляемого генератора колебаний.

Программно-управляемый генератор

синусоидальных колебаний (фиг.1) содержит опорный генератор 1, первый делитель 2 частоты, датчик 3 сетки частот, усилитель 4 с регулируемым - коэффициентом передачи, первый усилитель 5 мощности, блек 6 автоматической регулировки усиления (АРУ), коммутатор 7,первый регистр 8 памяти, первый цифроаналоговый преобразовател (ЦАП) 9, второй регистр 10 памяти, второй дешифратор 11, блок 12 оперативного запоминания, цифровой индикатор 13, блок 14 ввода информации, блок 15 управления, генератор 16 так товых импульсов, компаратор 17, втоf,

рой делитель 18 частоты, счетчик 19 импульсов, блок 20 постоянного запоминания, преобразователь 21 кода, буферный регистр 22, второй ЦАП 23, фильтр 24 нижних частот, второй усилитель 25 мощности, преобразователь 26 уровня напряжения, сумматор 27, первый дешифратор 28, блок 29 формирования импульсов, инвертор 30, первый элемент И 31, второй элемент И 32

триггер 33.

Блок 15 управления (фиг.2) содержит первый дешифратор 34, триггер 35, первый и второй элементы ИЛИ 36, 37, первый и второй элементы И 38, 39, первый и второй счетчики 40, 41, пер- вьй и второй инверторы 42, 43, регистр 44 сдвига, второй дешифратор 45, дифференцирующую КС-цепь 46.

Блок 12 оперативного запоминания (фиг.З) содержит первый, второй и третий регистры 47 - 49 памяти, мультиплексор 50.

Блок 29 формирования импульсов (фиг.4)содержит первый и второй элементы ИПИ-НЕ 51 ,52, элемент И-НЕ 53, элемент И 54, регистр 55 сдвига.

Программно-управляемый генератор синусоидальных колебаний работает следующим образом.

Сигналы программного управления частотой и амплитудой выходного сигнала последовательно вводятся оператором посредством блока 14 ввода информации, с выхода которого, управля- ющий сигнал поступает на вход перво31451830

го дешифратора 34 и через дифференцирующую КС-цепь 46 на входы первого 40 и второго 41 счетчиков блока 15 управления, а также на информационные входы регистров 47 - 49 памяти блока 12 оперативного запоминания.

Сигнал с выхода первого дешифратора 34 изменяет состояние триггера 35 и одновременно, пройдя первый эле- мен-т ИЛИ 36, производит установку начального состояния блока 12 оперативного запоминания, освобождая первый 47, второй 48 и третий 49 регистры памяти блока 12 оперативного запоминания от ранее введенной информации, после чего производится запись новой информации по тактовому сигналу с выЕсли значение устанавливаемой оператором частоты превышает низкочастотный диапазон стабилизации уровня выходного сигнала, то на выходе триггера 33 устанавливается состояние логического нуля за счет подачи на его вход импульсов с выхода элемента И 31 (фиг. 5 е), образую1цихся при совпадении импульсов с выходов блока 29 формирования импульсов (инвертированных инверторов 30), первого элемента И 38 и второго дешифратора 45 блока управления. При этом состояние логического нуля на выходе триггера 33 переключает коммутатор 7, и сигнал установленной частоты с выхода первого усилителя 5 мощности поступает непосредственно на выход программно-уп

| название | год | авторы | номер документа |

|---|---|---|---|

| Программно-управляемый генератор синусоидальных колебаний | 1986 |

|

SU1460768A1 |

| Программно-управляемый генератор синусоидальных колебаний | 1984 |

|

SU1427549A1 |

| Самонастраивающееся устройство управления | 1983 |

|

SU1130830A1 |

| Цифровой генератор трехфазных гармонических колебаний | 1987 |

|

SU1411915A1 |

| Устройство для контроля многоканального аппарата магнитной записи | 1986 |

|

SU1420615A1 |

| Устройство для ввода и вывода информации | 1982 |

|

SU1048466A1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Система экстремального регулирования | 1985 |

|

SU1352452A1 |

| Устройство для программного управления | 1981 |

|

SU987579A1 |

Изобретение относится к радиотехнике и связи. Цель изобретения - увеличение стабильности уровня выходного напряжения. Генератор содержит опорный г-р 1, два делителя 2 и 18 частоты, датчик 3 сетки частот,у-ль 4 с регулируемым коэф.передачи, два у-ля 5 и 25 мощности, блок автоматиВыход

хода дешифратора 34. Импульсы.такто- 20 равляемого генератора синусоидальных

вой синхронизации с выхода генератора 16 тактовых импульсов поступают на вход синхронизации первого счетчика 40 и далее - через первый 42, второй 43 инверторы и регистр 44 сдвига - на входы первого и второго злементов И 38, 39 (фиг. 5 в).

Адресными выходами блока 15 управления являются выходы второго счетчика 41. Согласно поступающему на вход мультиплексора 50 адресу, производится опрос регистров 47 - 49 памяти блока 12 оперативного запоминания.

Смена данных производится с окончанием ввода сигнала, после чего с выхода дешифратора 34 соответствующий импульс через второй элемент ИЛИ 37 поступает на вход первого элемента И 38 и далее на тактовый вход регистра 8 памяти. Установленное зна- чение частоты выходного сигнала высвечивается на табло цифрового индикатора 13.

мента И 38 (фиг. 5 б) и дешифратора 45 блока 15 управления (фиг. 5 в). Состояние логической единицы с выхода триггера 33 поступает на вход сумматора 27, что соответствует добавлению к значению текущего кода дополнительного адреса числа. Модифицированный таким образом код адреса поступает на вход второго дешифратоВ соответствии с установленным на выходе регистра 8 памяти кодом часто- g pa 28 и определяет запись значения ты датчик 3 сетки частот, подключ ен- частоты в разряды регистра 8 памяти, ный к опорному генератору 1 через которое оказывается больше высвечива- первый делитель 2 частоты, вырабаты- емого на табло цифрового индикатора вает синусоидальный сигнал, поступа- 13 в 10000 раз. Сигнал гашения незнающий на вход усилителя 4. Блок 6 АРУ gQ чащих нулей формируется блоком 29

обеспечивает постоянство уровня выходного напряжения, а при изменении опорного напряжения, вырабатываемого первым ЦАП 9, позволяет изменять уровень выходного напряжения. С выхода усилителя 5 мощности сигнал установленной частоты поступает на первый вход коммутатора 7, управляемого от триггера 33.

55

формирования импульсов (фиг. 5 г, д) при подаче информационного сигнала с выхода блока 12 оперативного значения на первый элемент ILTH-HE 51, а сигналов управления (фиг. 5 а) - на входы элементов И-НЕ 53, и 54 и вход синхронизации регистра 55 сдвига. Сформированные импульсы гашения незначащих нулей с выхода второго эле

колебаний. Кроме того, состояние логического нуля на стробирующем входе компаратора 17 запрещает прохождение импульсов на вход второго делителя 18.

Если значение устанавливаемой оператором частоты находится в диапазоне стабилизации уровня выходного сигнала, то триггер 33 устанавливается в единичное состояние за счет поступления на его вход импульсов с выхода второго элемента И 32 (фиг.5 и), образующихся при совпадении импульсов с выходов блока 29 формирования им- .пульсов (фиг. 5 ж, з), первого эле

мента И 38 (фиг. 5 б) и дешифратора 45 блока 15 управления (фиг. 5 в). Состояние логической единицы с выхода триггера 33 поступает на вход сумматора 27, что соответствует добавлению к значению текущего кода дополнительного адреса числа. Модифицированный таким образом код адреса поступает на вход второго дешифратоpa 28 и определяет запись значения частоты в разряды регистра 8 памяти, которое оказывается больше высвечива- емого на табло цифрового индикатора 13 в 10000 раз. Сигнал гашения незначащих нулей формируется блоком 29

g pa 28 и определяет запись значения частоты в разряды регистра 8 памяти, которое оказывается больше высвечива- емого на табло цифрового индикатора 13 в 10000 раз. Сигнал гашения незнаgQ чащих нулей формируется блоком 29

55

формирования импульсов (фиг. 5 г, д) при подаче информационного сигнала с выхода блока 12 оперативного значения на первый элемент ILTH-HE 51, а сигналов управления (фиг. 5 а) - на входы элементов И-НЕ 53, и 54 и вход синхронизации регистра 55 сдвига. Сформированные импульсы гашения незначащих нулей с выхода второго эле10

мента ИЛИ-НЕ 52 поступают на инвертор 30 и второй элемент И 32.

Разрядные выходы регистра 8 памяти управляют изменением частоты датчика 3 сетки частот и с выхода первого усилителя 5 мощности сигнал установленной частоты поступает на вход компаратора 17, преобразующего синусоидальный сигнал в прямоугольные импульсы, поступающие на вход второго делителя 18 частоты.

Таким образом, в низкочастотном диапазоне датчик 3 сетки частот вместе с усилителем 4 используется в качестве формирователя сигнала тактовой частоты. Выходной сигнал формируется методом пас- сивного синтеза, основанным на применении счетчика 1 9 как источника кода фазы и блока 20 постоянного запомина- ния в качестве функционального преобразователя кода фазы в код значений уровня выходного сигнала. Проходя через преобразователь 21 кода и Шуферньй регистр 22, сигнал преобразуется вторым ЦАП 23 в аналоговую форму и через фильтр нижних частот и второй усилитель 25 мощности поступает на вход коммутатора 7. При этом эквивалентный коэффициент деления второго делителя 18 и счетчик 19 выбирается таким, что значение синтизи- руемой частоты будет всегда совпадать со значением на табло цифрового индикатора 13.

Аналогично производится установка уровня выходного напряжения, при этом синхронизирующий сигнал через второй элемент 1ШИ 37 и второй элемент И 39 поступает на тактовый вход буферного регистра Ю. Двоично-десятичный код значения уровня сигнала на выходе буферного регистра 10 преобразуется первым ЦАП 9 в опорное напряжение, подаваемое на блок to АРУ и преобразователь 26 уровня напряжения, которое является опорным для второго ЦАП 23. Это позволяет обеспечить сопряжение обоих каналов формирования выходного сигнала по уровню выходного напряжения и получить лучшую стабильность уровня выходного напряжения в области нижних частот.

ормула

и 3

обретения 55

оп ча ле ли ре ко пе со мо п си т и 15 р д 25 р 40

1 Программно-управляемый генератор синусоидальных колебаний, содер- жаир1Й прследовательно соединенные

10

с. - -ь о

20

я 55

-

/W

опорный генерат ор, первый делитель частоты и датчик сетки частот, последовательно соединенные первый усилитель мощности, блок автоматической регулировки усиления с регулируемым коэффициентом передачи, коммутатор, первый информационный вход которого соединен с выходом первого усилителя мощности, а выход является выходом программно-управляемого генератора синусоидальных колебаний, последовательно соединенные первый дешифратор и первый регистр памяти, выход кото- 15 рого соединен с управляющим входом датчика сетки частот, последовательно соединенные второй дешифратор, второй регистр памяти и первый цифроана- логовый преобразователь, выход которого соединен с управляющим входом блока автоматической регулировки усиления, регистр сдвига, последовательно сое- диненные блок ввода информации и блок оперативного запоминания, выход кото- 25 рого соединен с информационными входами первого регистра памяти и второго регистра памяти, последовательно соединенные генератор тактовых импульсов и блок управления, управляю-, щий вход которого соединен с выходом блока ввода информации, адресньш выход блока управления соединен с входом второго дешифратора и адресным входом блока оперативного запоминания, первый, второй и третий тактовые выходы блока управления соедине- 1ны с тактовыми входами соответствен- но первого и второго регистров памяти и блока оперативного запоминания, 40 первый управляющий выход блока управления соединен с входом установки начального состояния блока оперативного запоминания, отличающийся тем, что, с целью увеличения стабильности уровня выходного напряжения, в него введены последовательно соединенные компаратор, второй делитель частоты, счетчик импульсов, блок постоянного запоминания и преобразователь кода, буферный регистр, второй цифроаналоговьш преобразователь, фильтр нижних частот и второй усилитель мощности, выход которого соеди иен с вторым информационным входом коммутатора, преобразователь уровня напряжения, выход которого соединен с опорным входом второго цифроанало- гового преобразователя, последовательно соединенные блок формирования

30

35

45

50

t4 импульсов, инвертор, первый элемент

И, триг ер и сумматор, выход которого соединен с входом первого дешифратора, второй элемент И, цифровой индикатор, второй вход сумматора соединен с адресным выходом блока управления, выход триггера соединен со стробирующим входом компаратора и управляющим входом коммутатора, управляющий вход блока формирования импульсов соединен с вторым управляющим выходом блока управления, а информационный вход блока формирования импульсов соединен с выходом блока оперативного запоминания, второй и третий входы первого элемента И соединены соответстве1шо с третьим управляющим и первым тактовым выходами блока управления, выход второго элемента И соединен с вторым входом триггера, а первый, второй и третий входы второго элемента И соединены соответственно с выходом блока формирования импульсов, третьим управляющим выходом блока управления и первым тактовым выходом блока управления, управляющий вход цифрового индикатора соединен с адресным выходом блока управления, а информационный вход цифрового индикатора соединен с выходом блока оперативного запоминания, причем второго делителя частоты соединен с тактовым входом регистра сдвига, выход старшего разряда счетчика импульсов соединен с управляющим входом преобразователя кода и с входом старшего разряда буферного регистра, выход датчика сетки частот соединен с входом усилителя с регулируемым коэффициентом передачи, выход которого соединен с входом первого усилителя мощности, информационный вход компаратора соединен с выходом первого усилителя мощности, информационный вход второго цифроаналогового преобразователя соединен с вь ходом регистра сдвига, а вход преобразователя уровня напряжения соединен с выходом первого цифроаналогового преобразователя.

5

0

5

0

5

0

5

0

чающийся тем, что блок управления содержит последовательно соединенные первьй дешифратор, триггер и первый элемент И, последовательно соединенные первый счетчик, первый инвертор, регистр сдвига и второй элемент И, последовательно соединенные второй счетчик и второй дешифратор, первый элемент ИЛИ, входы которого соединены с соответствующими выходами младших разрядов первого дешифратора, второй элемент ИЛИ, выход которого соединен с вторыми входами первого и второго элементов И, а также второй инвертор, при этом входы второго элемента ИЛИ соединены с соответствующими выходами старших разрядов первого дешифратора, выход второго инвертора соединен с информационным входом регистра сдвига, вход второго инвертора соединен с выходом старшего разряда первого счетчика, а первым, вторым и третьим тактовыми выходами блока управления являются выходы соответственно первого элемента И, второго элемента И и один из выходов старшего разряда первого дешифратора, адресными выходами блока управления являются разрядные выходы второго счетчика, а первым, вторым и третьим управляющими выходами блока управления являются выходы соответственно первого элемента- ИЛИ, старший разрядный выход первого счетчика и второй разрядньаЧ выход второго дешифратора, вход первого счетчика объединен с входом второго счетчика и черезвведеннуую RC-цепь соединен с входом первого дешифратора, которьй соединен также с синхронизирующим входом триггера и является управляющим входом блока управления, выход старшего разряда первого счетчика соединен с синхронизирующим входом второго счетчика, третьи входы первого и второго элементов И соединены соответственно с выходом регистра сдвига и инверснь М выходом триггера, а тактовым входом блока управления является тактовыр вход первого счетчика .

Фие.2

| Прибор для измерения угла наклона | 1921 |

|

SU253A1 |

| Техническое описание | |||

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Программно-управляемый генератор синусоидальных колебаний | 1984 |

|

SU1427549A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-01-15—Публикация

1985-10-15—Подача