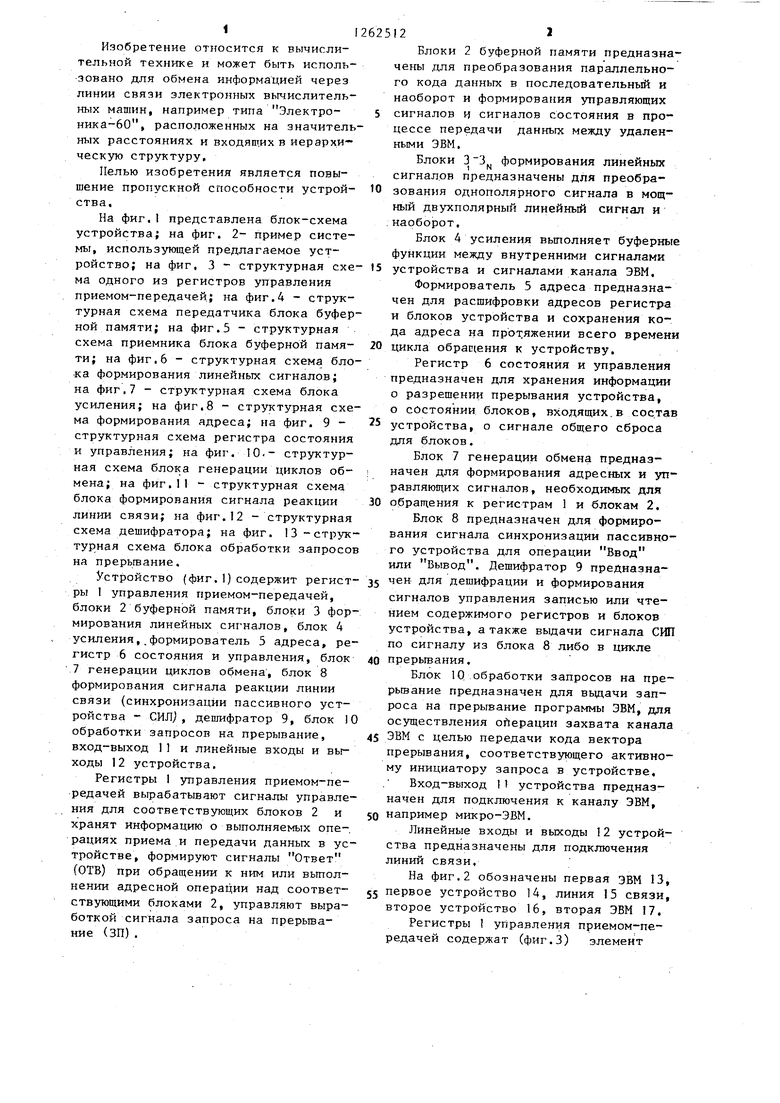

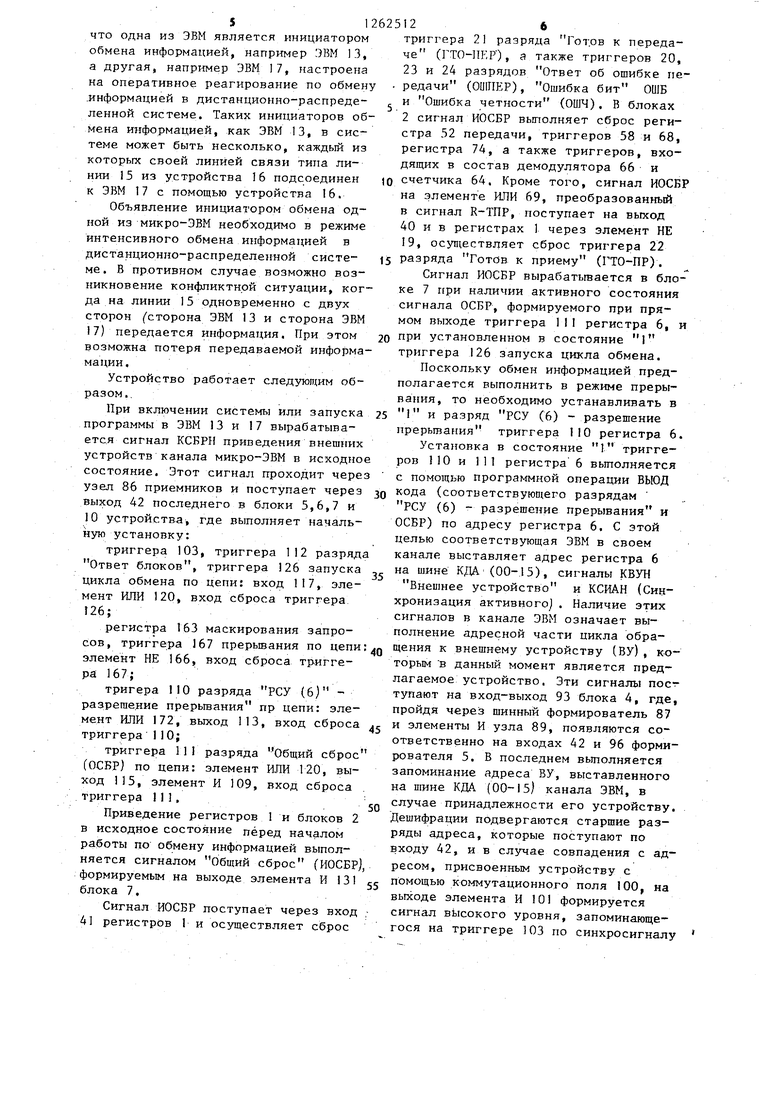

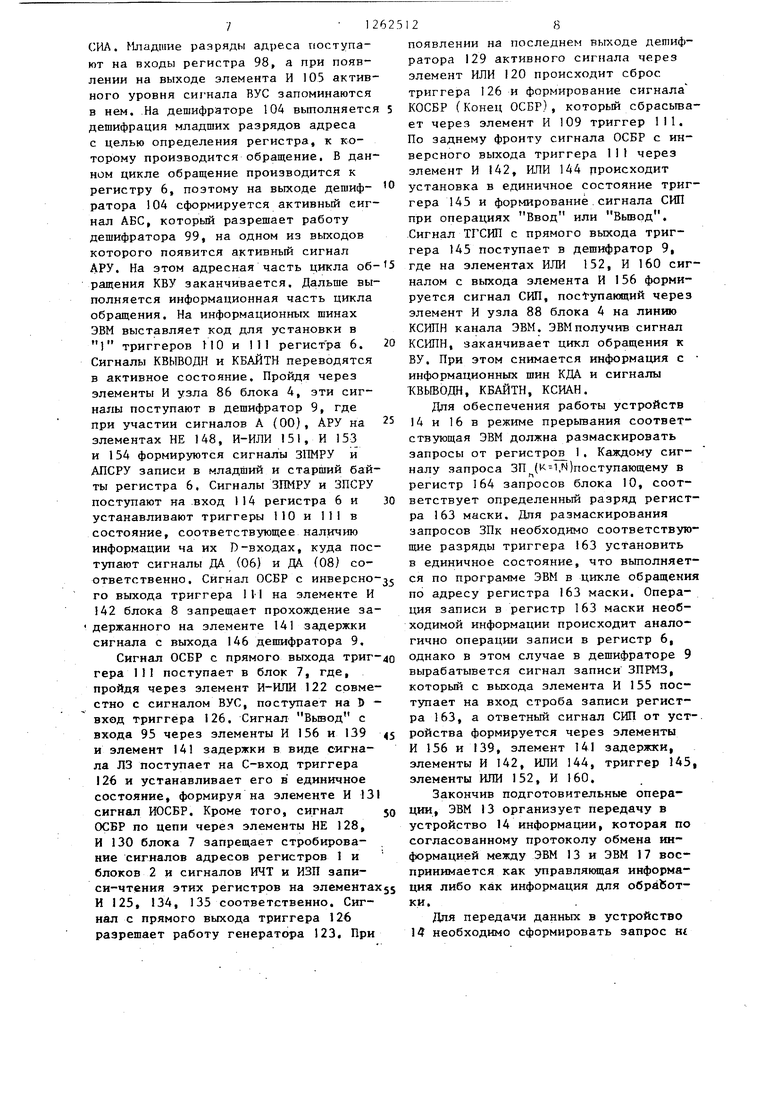

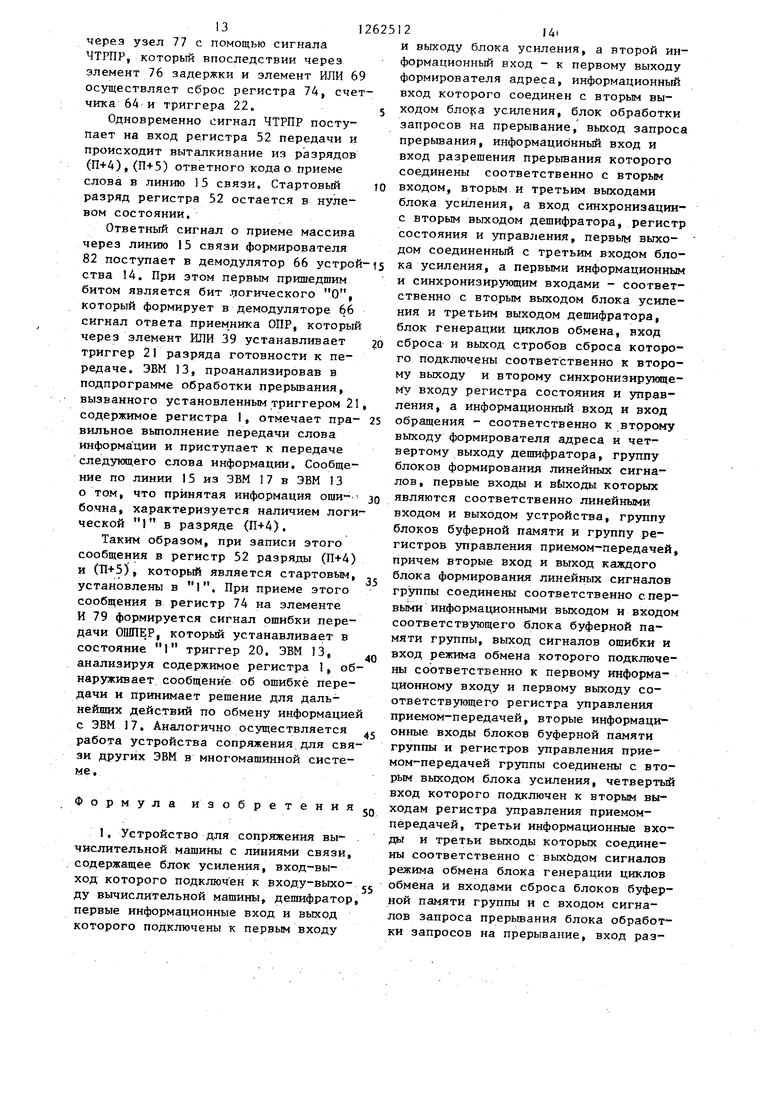

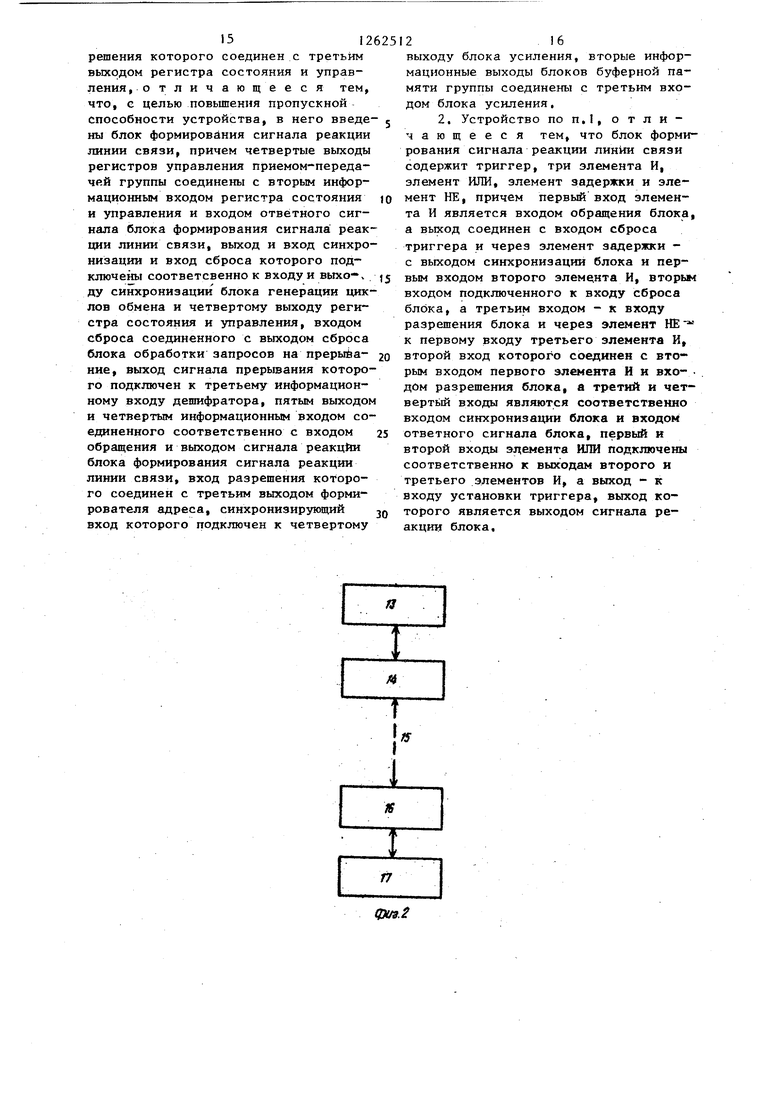

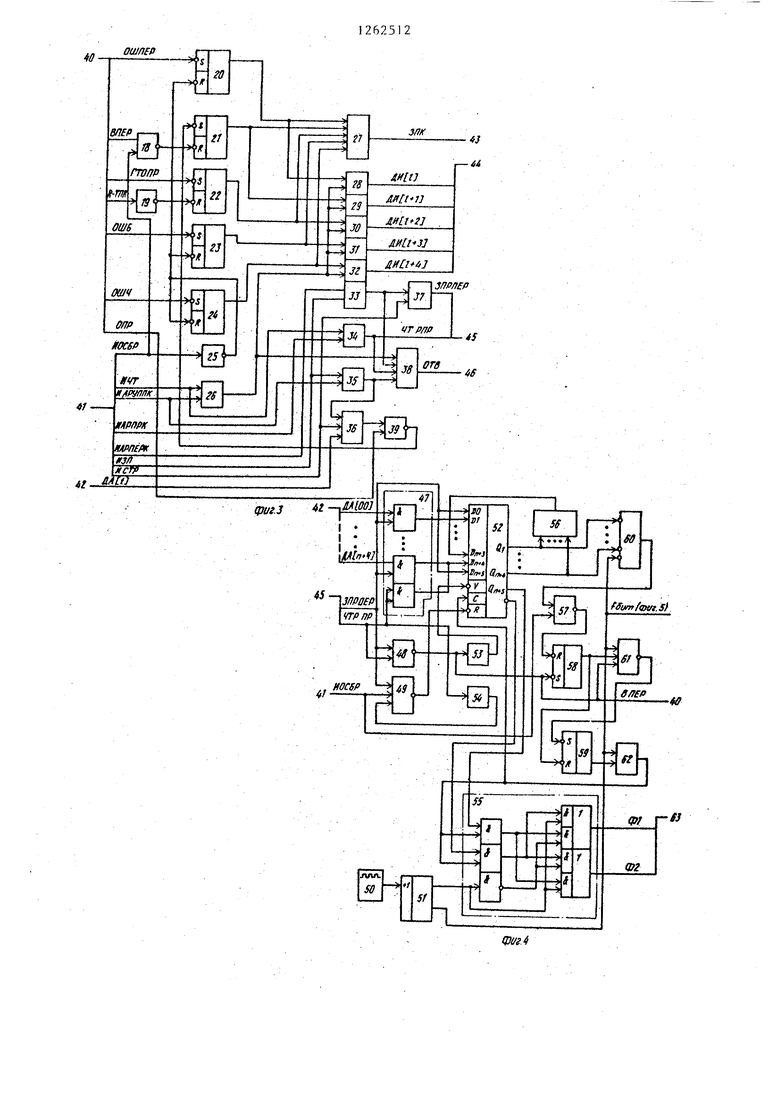

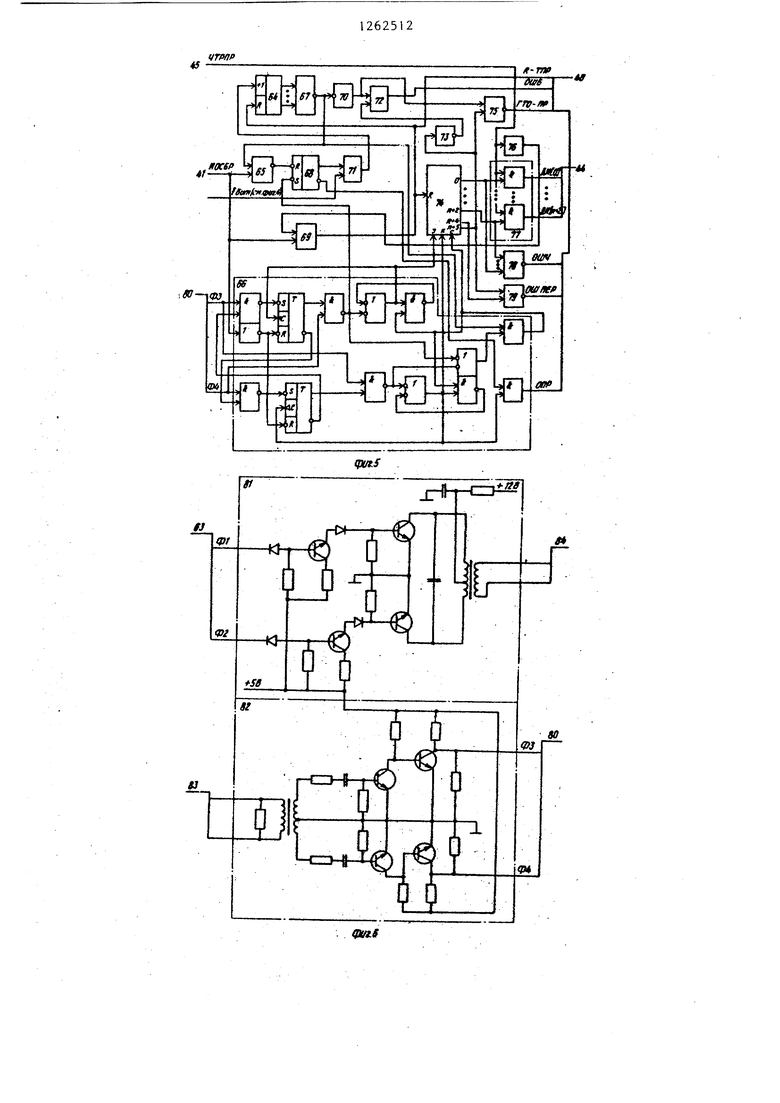

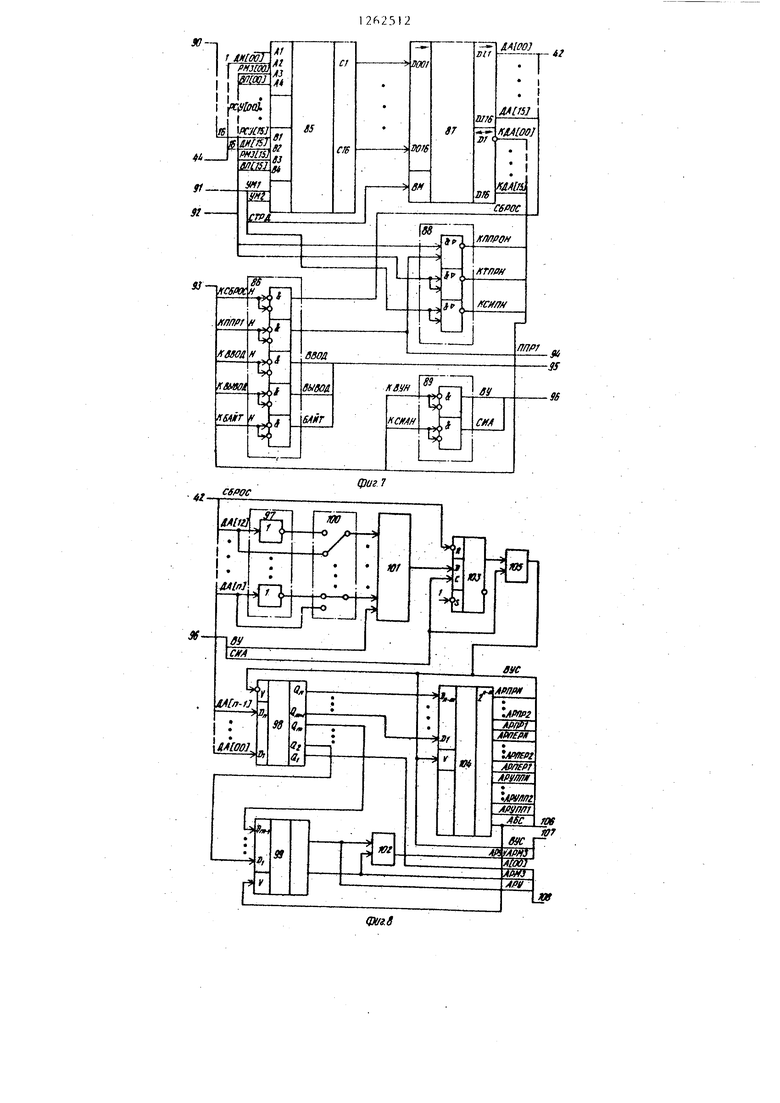

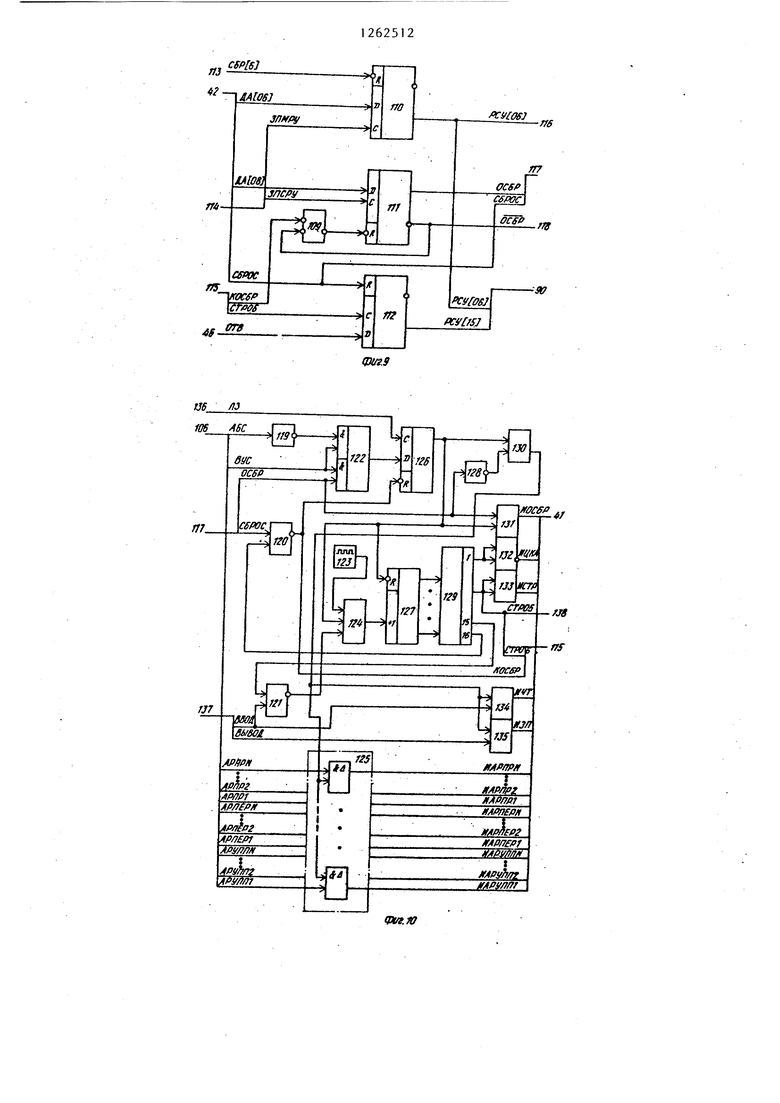

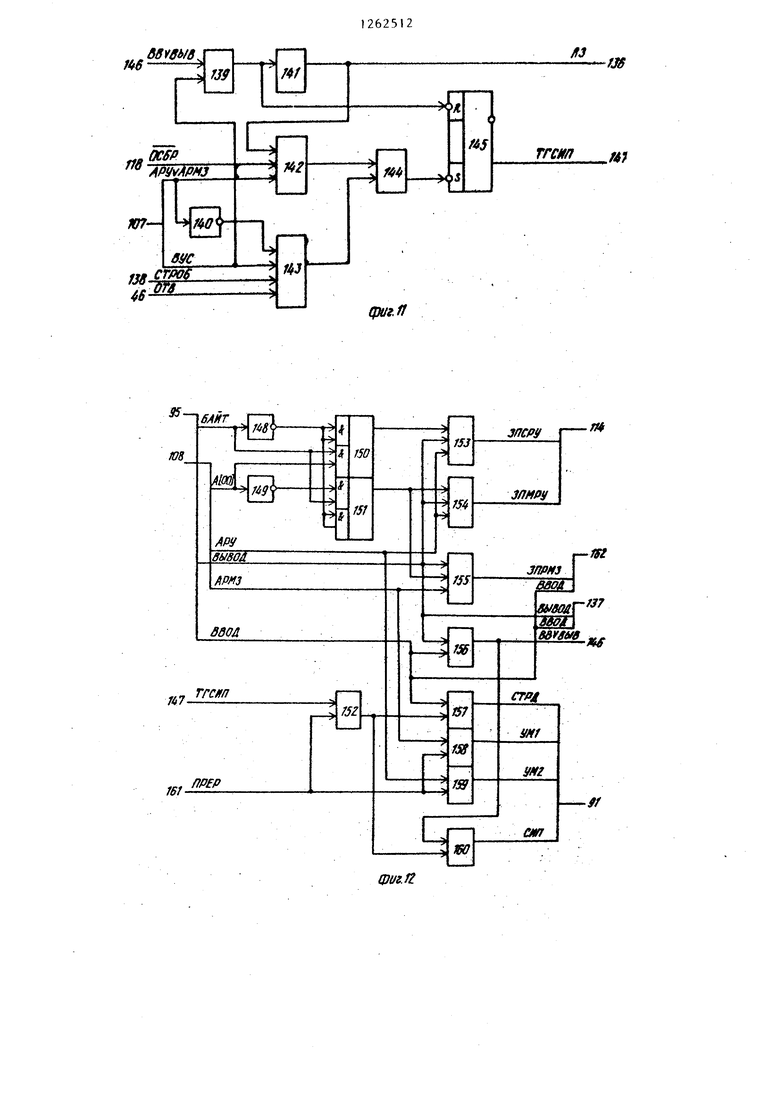

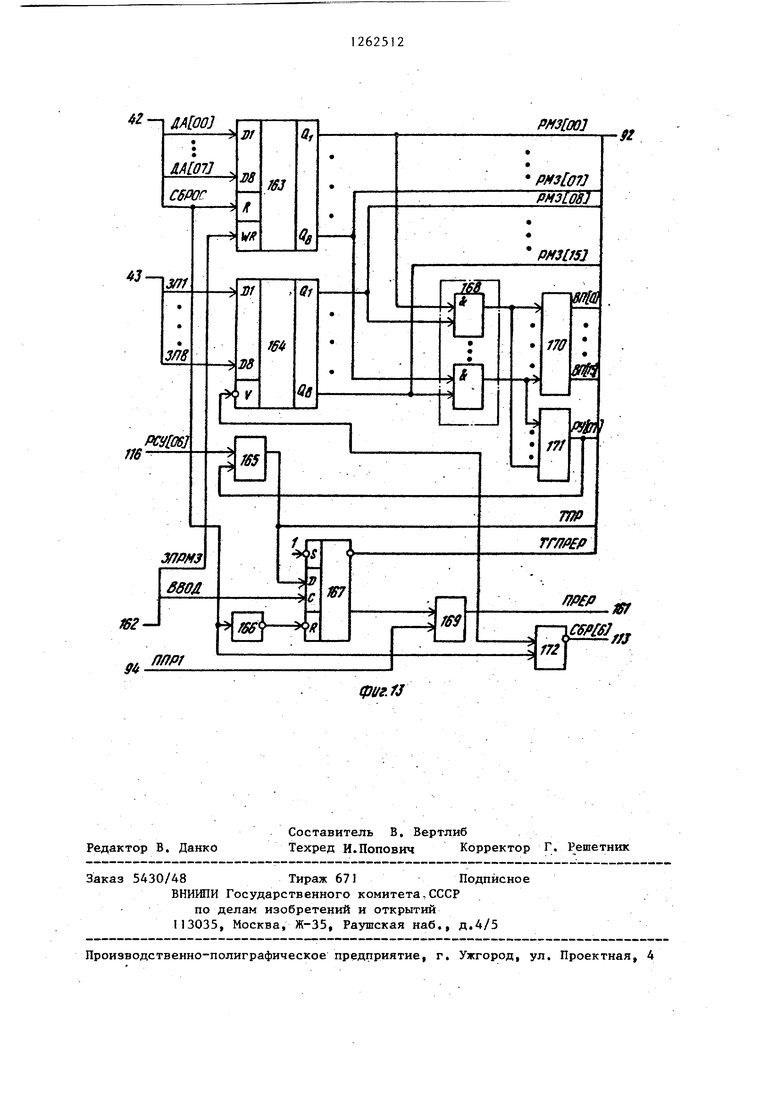

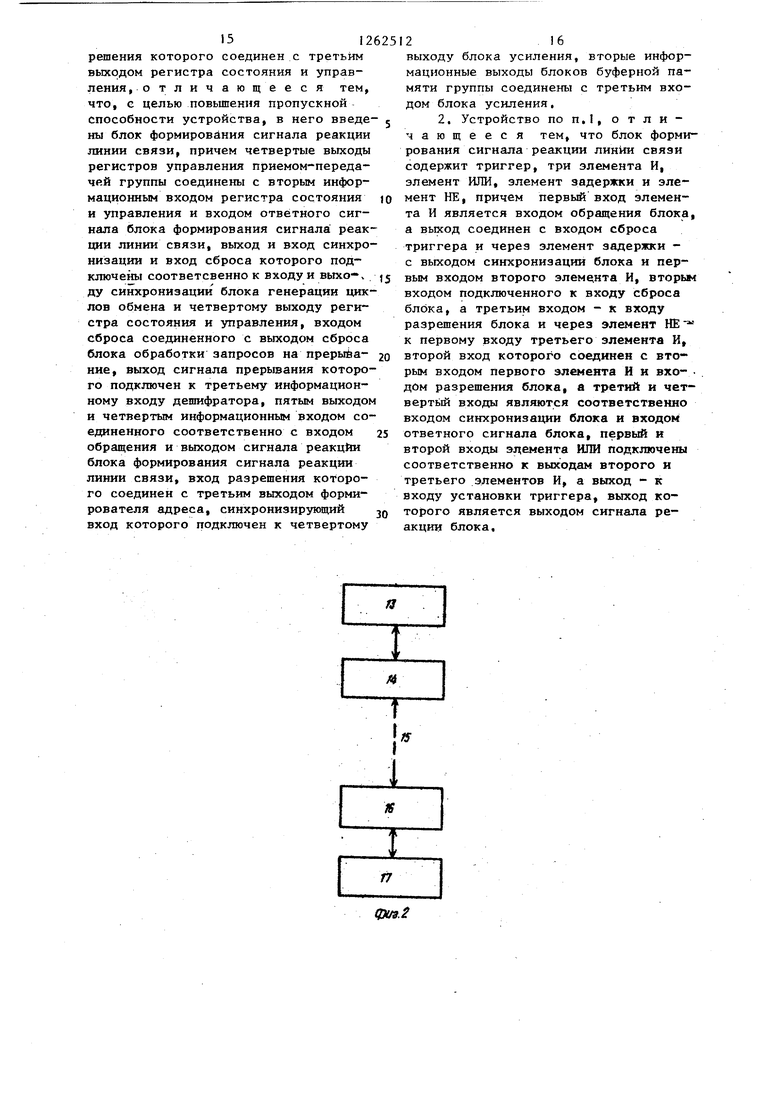

11 Изобретение относится к вычислительной технике и может быть использовано для обмена информацией через линии связи электронных вычислительных машин, например типа Электроника-60, расположенных на значитель ных расстояниях и входящих в иерархическую структуру. Целью изобретения является повышение пропускной способности устройства. На фиг.1 представлена блок-схема устройства; на фиг. 2- пример системы, использующей предлагаемое устройство; на фиг. 3 - структурная схе ма одного из регистров управле-ния приемом-передачей; на фиг.4 - структурная схема передатчика блока буфер ной памяти; на фиг.5 - структурная схема приемника блока буферной памяти; на фиг.6 - структурная схема бло ка формирования линейных сигналов; на фиг.7 - структурная схема блока усиления; на фиг.8 - структурная схе ма формирования адреса; на фиг. 9 структурная схема регистра состояния и управления; на фиг. Ю-- структурная схема блока генерации циклов обмена; на фиг.П - структурная схема блока формирования сигнала реакции линии связи; на фиг.12 - структурная схема дешифратора; на фиг. 13 -струк турная схема блока обработки запросо на прерывание. Устройство (фиг.)содержит регист ры 1 управления приемом-передачей, блоки 2 буферной памяти, блоки 3 фор мирования линейных сигналов, блок 4 усиления,.формирователь 5 адреса, ре гистр 6 состояния и управления, блок 7 генерации циклов обмена, блок 8 формирования сигнала реакции линии связи (синхронизации пассивного устройства - СИЛ, дешифратор 9, блок 1 обработки запросов на прерывание, вход-выход 11 и линейные входы и выходы 12 устройства. Регистры 1 управления приемом-передачей вырабатывают сигналы управле ния для соответствующих блоков 2 и хранят информацию о выполняемых операциях приема и передачи данных в ус тройстве, формируют сигналы Ответ (ОТВ) при обращении к ним или вьтолнении адресной операции над соответствующими блоками 2, управляют выработкой сигнала запроса на прерьшание (ЗП). 12 Блоки 2 буферной памяти предназначены для преобразования параллельного кода данных в последовательный и наоборот и формирования управляющих сигналов и сигналов состояния в про цессе передачи данных между удаленными ЭВМ. Блоки 3 3 формирования линейных сигналов предназначены для преобразования однополярного сигнала в мощный двухполярный линейный сигнал и наоборот. Блок 4 усиления вьтолняет буферные функции между внутренними сигналами устройства и сигналами канала ЭВМ. Формирователь 5 адреса предназначен для расшифровки адресов регистра и блоков устройства и сохранения кода адреса на протяжении всего времени цикла обращения к устройству. Регистр 6 состояния и управления предназначен для хранения информации о разрешении прерывания устройства, о состоянии блоков, входящих, в сос.тав устройства, о сигнале общего сброса для блоков. Блок 7 генерации обмена предназначен для формирования адресных и управляющих сигналов, необходимых для обращения к регистрам 1 и блокам 2. Блок 8 предназначен для формирования сигнала синхронизации пассивного устройства для операции Ввод или Вывод. Дешифратор 9 предназначен для дешифрации и формирования сигналов управления записью или чтением содержимого регистров и блоков устройства, а также выдачи сигнала СИП по сигналу из блока 8 либо в цикле прерьгоания. Блок 10 обработки запросов на прерывание предназначен для вьщачи запроса на прерывание программы ЭВМ, для осуществления ойерации захвата канала ЭВМ с целью передачи кода вектора прерывания, соответствующего активному инициатору запроса в устройстве. Вход-выход П устройства предназначен для подключения к каналу ЭВМ, например микро-ЭВМ. Линейные входы и выходы 12 устройства предназначены для подключения линий связи. На фиг.2 обозначены первая ЭВМ 13, первое устройство 14, линия 15 связи, второе устройство 16, вторая ЭВМ 17, Регистры I управления приемом-передачей содержат (фиг.З) элемент ИЛИ 18, элемент НЕ 19, триггеры 2024, элемент ИЛИ 25, элемент И 26, элемент ИЛИ 27, элементы И 28-37, элементы ИЛИ 38 и 39, первый, третий и второй информационные входы 40, 41 и 42 блока, третий, второй, первьШ и четвертый выходы 43, 44, 45 и 46 блока. Блок 2 буферной памяти состоит из передатчика и приемника. Передатчик блока 2 содержит (фиг.4) узел 47 эле ментов И, элементы Ш1И 48 и 49, гене ратор 50 импульсов, счетчик 51, буферный регистр 52 передачи, элементы 53 и 54 задержки, модулятор 55, узел 56 контроля четности, элемент ИЛИ 57 триггеры 58 и 59, элементы И 60-62, -первый информационный выход 63 блока 2, Приемник блока 2 содержит (фиг.5) счетчик 64, элемент ИЛИ 65, демодулятор 66, элемент И 67, триггер 68, элемент ИЛИ 69, элемент НЕ 70, элементы И 71. и 72, элемент НЕ 73, буферный регистр 74 приема, элемент И 75, элемент 76 задержки, узел 77 элементов И, узел 78 контроля нечетности, элемент И 79, первый информационный вход 80 блока 2. Блок 3 формирования линейных сигналов состоит из двух независимо работающих формирователя 81 выходных сигналов и формирователя 82 входных сигналов (фиг,6), Формирователь 81 предназначен для преобразования однополярного сигнала на входе в мощный двухполярный сигнал амплитудой 12В на выходе. Формирователь 81 представляет собой двухтактный усилитель, выполненный по трансформативной схеме. Формирователь 82 предназначен для преобразования двухполярного сигнала на входе в однополярный на выходе и представляет собой двухтактный усилитель с трансформаторной связью. Формирователь 81 имеет второй вход 63 для сигналов Ф1 и Ф2, первый вход 83 для приема информации с линии связи, первый выход 84 для передачи информации в линию связи, второй выход 80 для передачи сигналов ФЗ и Ф4, Блок 4 усиления содержит (фиг,7) мультиплексор 85, узел 86 приемников сигналов канала ЭВМ, шинный формирователь 87, узел 88 передатчиков сигналов в канал ЭВМ, узел 89 приемников сигналов канала ЭВМ, третий, первый, второй входы 90-92 блока 4, вход-выход 93 блока 4, третий, первый и четвертый выходы 94-96 блока 4, Формирователь 5 адреса содержит (фиг.8) группу элементов НЕ 97, адресный регистр 98, дешифратор 99, коммутационное поле ЮЛ, элемент И 101, элемент ИЛИ 102, триггер 103, дешифратор 104, элемент И 105, второй, третий и первый выходы 106-108 регистра 5, . Регистр 6 состояния и управления содержит фиг,9 элемент И 109, триггеры 110-112, вход 113 сброса, первый и второй входы 114 и 115 синхронизации, третий, второй и четвертый выходы 116-118 регистра 6, Блок 7 генерации циклов обмена содержит (фиг,10) элемент НЕ 119, элементы ИЛИ 120, элемент И 121, элементы И-ИЛИ 122, генератор 123 импульсов, элемент И 124, группу элементов. И 125 узла усилителей, триггер 126, счетчик 127, элемент НЕ 128, дешифратор 129, элемент И 130, элементы И 131-135 узла усилителей, входы 136 и 137 синхронизации и обращения и выход 138 синхронизации блока 7, Блок 8 формирования сигнала реакции линии связи содержит (фиг,II) элемент И 139, элемент НЕ 140, элемент 14 задержки, элементы И 142 и 143, элемент ИЛИ (44, триггер 145, вход 146 обращения и выход 147 сигнала реакции. Дешифратор 9 (фиг,12) содержит элементы НЕ 148 и. 149, элементы ИИЛИ 150 и 151, элемент ИЛИ 152, элементы и 153-160, третий информационный вход 161 и второй выход 162 дешифратора. Блок 10 обработки запросов на прерывание содержит (фиг,13) регистр 163маскирования запросов, регистр 164запросов, элемент И 165, элемент НЕ 166, триггер 167, узел 168 элементов И, элемент И 169, шифратор 170, элементы ИЛИ 171 и 172, Работа устройства рассматривается на примере системы (фиг,2), Устройство осуществляет обмен данными между блоком 2 и микро-ЭВМ под управлением программы с использованием режима прерываний, преобразование информации из параллельного кода в последовательный и вьздачу ее в линию сйязн, прием информации в последовательном коде из линии связи, преобразование ее в параллельный код,Предполагается, $1 что одна из ЭВМ является инициатором обмена информацией, например ЭВМ 13, а другая, например ЭВМ 17, настроена на оперативное реагирование по обмену .информацией в дистанционно-распределенной системе. Таких инициаторов обмена информацией, как ЭВМ 13, в системе может быть несколько, каждьй из которых своей линией связи типа линии 15 из устройства 16 подсоединен к ЭВМ 17 с помощью устройства 16, Объявление инициатором обмена одной из микро-ЭВМ необходимо в режиме интенсивного обмена информацией в дистанционно-распределенной системе. В противном случае возможно возникновение конфликтной ситуации, когда на линии 15 одновременно с двух сторон (сторона ЭВМ 13 и сторона ЭВМ 17) передается информация. При этом возможна потеря передаваемой информамации. Устройство работает следующим образом,. При включении системы или запуска программы в ЭВМ 13 и 17 вырабатывается сигнал КСБРН приведения внешних устройств канала микро-ЭВМ в исходно состояние. Этот сигнал проходит чере узел 86 приемников и поступает через выход 42 последнего в блоки 5,6,7 и 10 устройства, где выполняет начальную установку: триггера 103, триггера 112 разряда Ответ блоков, триггера 126 запуска цикла обмена по цепи: вход 117, элемент ИЛИ 120, вход сброса триггера Г26; регистра 163 маскирования запросов, триггера 167 прерьшания по цепи элемент НЕ 166, вход сброса триггера 167j тригера 110 разряда РСУ (6) разрегае.ние прерьшания пр цепи: элемент ИЛИ 172, выход 113, вход сброса триггера 110; триггера 11I разряда Общий сброс (ОСБР) по цепи: элемент ИЛИ 120, выход 115, элемент И 109, вход сброса триггера 111. Приведение регистров 1 и блоков 2 в исходное состояние перед началом работы по обмену информацией выполняется сигналом Общий сброс (ИОСБР формируемым на выходе элемента И 13 блока 7, Сигнал ИОСБР поступает через вход 41 регистров 1 и осуществляет сброс 126 триггера 21 разряда Готов к передаче (ГТО-ПЕР), а также триггеров 20, 23 и 24 разрядов Ответ об ошибке передачи (ОШПЕР), Ошибка бит ОШБ и Ошибка четности (ОШЧ), В блоках 2 сигнал ИОСБР выполняет сброс регистра 52 передачи, триггеров 58 и 68, регистра 74, а также триггеров, входящих в состав демодулятора 66 и счетчика 64, Кроме того, сигнал ИОСБР на элементе ИЛИ 69, преобразованный в сигнал R-ТПР, поступает на выход 40 и в регистрах 1 через элемент НЕ 19, осуп1ествляет сброс триггера 22 разряда Готов к приему (ГТО-ПР). Сигнал ИОСБР вырабатывается в блоке 7 при наличии активного состояния сигнала ОСБР, формируемого при прямом выходе триггера 11I регистра 6, и при установленном в состояние 1 триггера 126 запуска цикла обмена. Поскольку обмен информацией предполагается выполнить в режиме прерывания, то необходимо устанавливать в 1 и разряд РСУ (6) - разрешение прерывания триггера ПО регистра 6. Установка в состояние 1 триггеров 110 и 111 регистра 6 вьтолняется с помощью программной операции ВЬЮД кода (соответствующего разрядам РСУ (6) - разрешение прерывания и ОСБР) по адресу регистра 6, С этой целью соответствующая ЭВМ в своем канале выставляет адрес регистра 6 на шине КДА(00-15), сигналы КВУН Внешнее устройство и КСИАН (Синхронизация активного . Наличие этих сигналов в канале ЭВМ означает выполнение адресной части цикла обращения к внешнему устройству (ВУ), которым в данный момент является предлагаемое устройство. Эти сигналы пост тупают на вход-выход 93 блока 4, где, пройдя через щинный формирователь 87 и элементы И узла 89, появляются соответственно на входах 42 и 96 формирователя 5. В последнем вьтолняется запоминание адреса ВУ, выставленного на шине КДА (00-15) канала ЭВМ, в случае принадлежности его устройству. Дешифрации подвергаются старшие разряды адреса, которые поступают по входу 42, ив случае совпадения с адресом, присвоенным устройству с помощью коммутационного поля 100, на выходе элемента И 10 формируется сигнал высокого уровня, запоминающегося на триггере 103 по синхросигналу СИЛ. Младшие разряды адреса поступают на входы регистра 98, а при появлении на выходе элемента И 105 актив ного уровня сигнала ВУС запоминаются в нем. На дешифраторе 104 выполняетс дешифрация младших разрядов адреса с целью определения регистра, к которому производится обращение. В дан ном цикле обращение производится к регистру 6, поэтому на выходе дешифратора 104 сформируется активный еиг нал АБС, который разрешает работу дешифратора 99, на одном из выходов которого появится активный сигнал АРУ. На этом адресная часть цикла об ращения КВУ заканчивается. Дальше вы полняется информационная часть цикла обращения. На информационных шинах ЭВМ выставляет код для установки в 1 триггеров 0 и 111 регистра 6. Сигналы КВЫВОДН и КБАЙТН переводятся в активное состояние. Пройдя через элементы И узла 86 блока 4, эти сигналы поступают в дешифратор 9, где при участии сигналов А (00), АРУ на элементах НЕ 148, И-ИЛИ 151, И 153 и 154 формируются сигналы ЗПМРУ и АПСРУ записи в младший и старший бай ты регистра 6, Сигналы ЗПМРУ и ЗПСРУ поступают на .вход I 14 регистра 6 и устанавливают триггеры ПО и 111 в состояние, соответствующее наличию информации ча их D-входах, куда пос тупают сигналы ДА (06) и ДА (08) соответственно. Сигнал ОСБР с инверсно го выхода триггера 1 1-1 на элементе И 142 блока 8 запрещает прохождение за держанного на элементе 141 задержки сигнала с выхода 146 дешифратора 9. Сигнал ОСБР с прямого выхода триг гера 11I поступает в блок 7, где, пройдя через элемент И-ИЛИ 122 совме стно с сигналом ВУС, поступает иа 5 - вход триггера 126. Сигнал Вьшод с входа 95 через элементы И 156 и 139 и элемент 141 задержки в виде сигнала ЛЗ поступает на С-вход триггера 126 и устанавливает его в единичное состояние, формируя на элементе И 13 сигнал ИОСБР. Кроме того, сигнал ОСБР по цепи через элементы НЕ 128, И 130 блока 7 запрещает стробирование сигналов адресов регистров 1 и блоков 2 и сигналов ИЧТ и ИЗП записи-чтения этих регистров на элементах И 125, 134, 135 соответственно. Сигнал с прямого выхода триггера 126 разрешает работу генератора 123, При 128 появлении на последнем выходе дешифратора 129 активного сигнала через элемент ИЛИ 120 происходит сброс триггера 126 и формирование сигнала КОСБР (Конец ОСБР), который сбрасьгеает через элемент И 109 триггер 111. По заднему фронту сигнала ОСБР с инверсного выхода триггера 11I через элемент И 142, ИЛИ 144 происходит установка в единичное состояние триггера 145 и формирование.сигнала СИП при операциях Ввод или Вьшод. Сигнал ТГСИП с прямого выхода триггера 145 поступает в дешифратор 9, где на элементах ИЛИ 152, И 160 си1- налом с выхода элемента И 156 формируется сигнал СИП, пoctyпaющий через элемент И узла 88 блока 4 на линию КСИПН канала ЭВМ. ЭВМ получив сигнал КСИПН, заканчивает цикл обращения к ВУ. При этом снимается информация с информационных шин КДА и сигналы КВЫВОДН, КБАЙТН, КСИАН. Для обеспечения работы устройств 14 и 16 в режиме прерьшания соответствующая ЭВМ должна размаскировать запросы от регистре 1. Каждому сигналу запроса ЗП (к-1,М)поступающему в регистр 164 запросов блока 10, соответствует определенный разряд регистра 163 маски. Для размаскирования запросов ЗПк необходимо соответствующие разряды триггера 163 установить в единичное состояние, что выполняется по программе ЭВМ в цикле обращения по адресу регистра 163 маски. Операция записи в регистр 163 маски необходимой информации происходит аналогично операции записи в регистр 6, однако в этом случае в дешифраторе 9 вырабатывется сигнал записи ЗПРМЗ, который с выхода элемента И 155 поступает на вход строба записи регистра 163, а ответный сигнал СИП от уст-, ройства формируется через элементы И 156 и 139, элемент 141 задержки, элементы И 142, ИЛИ 144, триггер 145, элементы ИЛИ 152, И 160. Закончив подготовительные операции, ЭВМ 13 организует передачу в устройство 14 информации, которая по согласованному протоколу обмена информацией между ЭВМ 13 и ЭВМ 17 воспринимается как управлякщая информация либо как информация для обравотки, Для передачи данных в устройство 14 необходимо сформировать запрос Hf

912

прерьгаание в ЭВМ 13 от данного устройства, С этой целью вьтолняется . операция записи логической I в триггер 21 готовности передачи соответствующего регистра 1. Операция записи вьтолняется по адресу з-аданного per гистра 1, при этом адрес регистра 1 с соответствующего выхода дешифратог ра 104 поступает через выход 106 формирователя 5 на соответствующий. . вход элементов И 125. Триггер 126, на D -вход которого поступает логическая. по цепи элементов НЕ 119, И-ИЛИ 122 при наличии сигнала БУС и отсутствии сигнала АБС, устанавливается в состояние. сигналом ЛЗ на входе 136, Происходит запуск генерации цикла обмена, в ходе которого на элементах И 132, 133 вырабатываются сигналы ИЦКЛ, ИСТР, а на элементе И элементах И 25 сигналом с выхода элемента И 130 происходит стробирование поступившей на их входы управляющей и адресной информации. Запись 1 в триггер 21 готовности передачи происходит по цепи элементов И 35, 36 и ИЛИ 39, При выполнении операции записи в требуемый регистр на элементе ИЛИ 38 формируется сигнал ответа ОТВ, который поступает на триггера 12, а также на элемент И 143 блока 8, разрешая тем самым прохождение импульса СТРОБ через элементы И 143 и ИЛИ 144 и триггер 145 для формирования ответного сигнала СИП,

Состояние логической 1 на прямом выходе триггера 2 обуславливает формирование на элементе ИЛИ 27 запроса ЗПк от соответствующего регистра 1к, которьй поступает на один из информационных входов регистра 164 запроса, Далее на регистрах 163 и 164 и элементах И 168, ИЛИ 171 и И 165 формируется сигнал Требование прерьшания ТПР на прерывание программы в ЭВМ 13

Если этот запрос окажется более приоритетным по сравнению с выполняемой программой и другими поступившими запросами, ЭВМ 13 прекращает выподнение основной программы и переходит к обслуживанию прерьшания, С этой целью ЭВМ 13 выставляет в канал сигнал КВВОДН и далее сигнал Разрешение прерывания KlfflPlH,

Сигнал Ввод при наличии сигнала ТПР устанавливает в состояние триггер 167 прерывания. На выходе

1210

элемента И 169 при состоянии триггера 167 и сигнала Ш1Р1 формируется сигнал ПРЕР, которьй в дешифраторе 9 на элементах И 158 и 159 обеспечивает формирование сигналов УМ-, УМ-2 управления мультиплексором 85 блока 4, При этом на выходах последнего появляется код вектора прерывания наиболее приоритетного из запро-г сов ЗПк, сформированного на шифраторе 170 блока 10, По цепи элементов ИЛИ 152 и И 160 вьтолняется формирование ответного синхросигнала СИП, Одновременно через элемент ИЛИ 172 вьтолняется сброс триггера 110, ЭВМ 3, получив от устройства 14 вектор прерьшания с сигналом СИП, снимает сигналы КВВОДН, КШ1Р1 и переходит на подпрограмму обработки запросов от устройства. При этом ЭВМ 13 инициирует операцию Ввод для содержимого регистра , выставившего запрос ЗПк, Считьшание информации, содержащейся в регистре 1 к, происходит по цепи элементов И 26, 28-32 с помощью сигналов ИАРУППк и ИЧТ,

При выполнении подпрограммы обработки прерывания необходимо восстанавливать состояние 1 шестого разряда регистра 6 для обеспечения дальнейшей работы в режиме прерьшания. ЭВМ 13 анализирует содержимое регистра 1к:И, определив готовность к передаче, приступает к операциц записи в блок 2к, .

Информация в виде байта данных поступает по входу 42 через узел 47, где стробируется сигналом ЗПРПЕР записи в регистр передачи, на входе регистра 52 передачи. Сигнал ЗПРПЕР поступает на входы регистра 52, являющиеся соответственно стоповым и стартовым разрядами слова информации, через элемент ИЛИ 49 производит предварительный сброс регистра 52 передачи и через элемент ИЛИ 48 и элемент 53 задержки - последующее фиксирование информации в регистре 52, Од | овременно сигнал ЗПРПЕР поступает на вход триггера 58 и устанавливает его в состояние 1, Это обстоятельство разрешает .прохождение серии импульсов, вырабатываемой на счетчике 51, через элемент И 61 для установки в состояние 1 триггера 59, тем самым разрешая прохождение серии импульсов через элемент И 62, с выхода которого синхроимпульсы поступают на вход строба сдвига информации в регистре 52 и на вход модулятора 55. Сигнал ВПЕР с выхода элемента ИЛИ 48 через элемент ИЛИ 18 поступает на вход триггера 21. Сигнал готовности передачи снимается. На модулятор 55 поступает информация о регистре 52 в последовательном коде. После считывания из ре гистра 52 всего слова осуществляется сброс триггера 58, что в свою очередь вызьтает сброс триггера 59. Счи тьшание информации из регистра 52 в модулятор 55 прекращается. Модулятор 55 обеспечивает фазоимпульсный метод модуляции информации. Этот метод сочетает в себе принцип фазовой манипуляции на 180 и импусной модуляции. Формирователь 8 преобразует одно полярные модулированные импульсные сигналы, поступающие с выходов модулятора 55, в двуполярный сигнал. При чем код логической 1 представлен в виде сигнала положительной полярноети в первой половине периода и сигна ла отрицательной полярности во второ половине периода. А код логического О представлен в виде сигнала отрицательной полярности в первой половине периода и сигнала положительной полярности - во второй половине пери ода. Устройство 14 после завершения пе редачи слова . информации в линию 15 связи ожидает ответа от устройства 1 о результатах передачи. Информация через линию 15 связи поступает на вход устройства 16 и через формирователь 82, демодулятор 66 - на входы регистра 74. Демодулятор 66 реализует относительный метод разделения сигналов логических 1 и О на основе разделения чередования полярностей сигналов, приходящих из линии связи. Полученные на выходе демодулятора 66 прямой и инверсный коды информационного слова последовательно поступают на входы регистра 74. На входы синхронизации триггеров регистра 74 с выхода демодулятора 66 поступают синхроимпульсы, формируемые каждым битом принимаемого слова. Когда стартовый бит слова информации поступает в де модулятор 66, устанавливается в состояние 1 триггер 68, которьш разрешает прохождение серии синхроимпульсов с выхода счетчика 51 через эле-, мент И 71 на счетный вход счетЧика 64 бит слова. Схема совпадения на элементе И 67 настроена на код количества бит в принимаемом слове. Когда счетчик 64 отсчитает положенное количество импульсов, на элементе И 67 формируется импульс сброса триггера 68 через элемент ИЛИ 65, что запретит дальнейшую работу счетчика 64, Вместе с тем, через элемент НЕ 70-сигнал конца отсчета битов слова поступает на элементы И 72, 75, где происходит его сравнение с состоянием последнего разряда регистра 74, В последний разряд регистра 74 записьшается стартовый бит слова информации, который всегда является логической 1, Таким образом, если нет ошибок потери бит в слове при передаче его через линию 15 связи, то стартовый бит достигнет последнегоразряда регистра 74 в момент выработки сигнала конца отсчета битов слова, и на элементе И 75сформируется сигнал ГТО-ПР готовности приема,, а через элемент НЕ 73 на элементе И 72 запретится выработка сигг нала БИТ ОШБ ошибки потери. Если в приемном слове имеется ошибка неправильной передачи логических 1 или О, то узел 78 сформирует сигнал ОШБ ошибки четности. Любой из сигналов ГТО-ПР, ОШБ или ОШЧ поступает в регистр 1к, где устанавливает в состояние 1 соответствующий разряд (триггеры 22, 23, 20 соответственно) , Любой из этих разрядов, установленный в состояние 1 обеспечивает формирование на элементе ИЛИ 27 запроса на прерывание ЗПк, поступающего через блок 10 на шину КТПРН канала ЭВМ 17, ЭВМ,17, получив запрос на прерывание, входит в подпрограмму обработ- . ки прерывания и считьшает содержимое регистра 1к, Если в результате анализа выявились ошибки при передаче информации, ЭВМ 17 переводит устройство 16 в режим передачи и формирует сообщение в ЭВМ через линию 15 связи о том, что принятое слово информации ошибочно. Если в результате анализа содержимого регистра 1 ошибок не обнаружено, то ЭВМ 17 считывает содержимое регистра 74 блока 2к в цикле Ввод обращения к устройству 16. При этом информация из регистра 74 передается 131 через узел 77 с помощью сигнала ЧТРПР, который впоследствии через элемент 76 задержки и элемент ИЛИ 69 осуществляет сброс регистра 74, счет чика 64 и триггера 22, Одновременно сигнал ЧТРПР поступает на вход регистра 52 передачи и происходит выталкивание из разрядов (П+4),(П+5) ответного кода о приеме слова в линию 15 связи. Стартовый разряд регистра 52 остается в нулевом состоянии. Ответный сигнал о приеме массива через линию 15 связи формирователя 82 поступает в демодулятор 66 устрой ства 14, При этом первым пришедшим битом является бит .тгогического О, который формирует в демодуляторе 66 сигнал ответа приемника ОПР, который через элемент ИЛИ 39 устанавливает триггер 21 разряда готовности к передаче, ЭВМ 13, проанализировав в подпрограмме обработки прерьшания, вызванного установленным триггером 21 содержимое регистра 1, отмечает правильное выполнение передачи слова информации и приступает к передаче следующего слова информации. Сообщение по линии 15 из ЭВМ 17 в ЭВМ 13 о том, что принятая информация ошибочна, характеризуется наличием логи ческой 1 в разряде (П-1-4), Таким образом, при записи этого сообщения в регистр 52 разряды (П+4) и (Т1+5)|, который является стартовым, установлень: в 1, При приеме этого сообщения в регистр 74 на элементе И 79 формируется сигнал ошибки передачи ОШПЕР, который устанавливает в состояние 1 триггер 20, ЭВМ 13, анализируя содержимое регистра 1, об наруживает сообщение об ошибке передачи и принимает решение для дальнейших действий но обмену информацие с ЭВМ 17, Аналогично осуществляется работа устройства сопряжения для свя зи других ЭВМ в многомашинной системе. Формула изобретения 1, Устройство для сопряжения вычислительной машины с линиями связи, содержащее блок усиления, вход-выход которого подключен к входу-выходу вычислительной машины, дешифратор первые информационные вход и выход которого подключены к первым входу 12I4f и выходу блока усиления, а второй информационный вход - к первому выходу формирователя адреса, информационный вход которого соединен с вторым выходом бло|са усиления, блок обработки запросов на прерывание, выход запроса прерьшания, информационный вход и вход разрешения прерьшания которого соединены соответственно с вторым входом, вторым и третьим выходами блока усиления, а вход синхронизациис вторым выходом дешифратора, регистр состояния и управления, первым выходом соединенный с третьим входом блока усиления, а первыми информационным и синхронизируннцим входами - соответственно с вторым выходом блока усиления и третьим выходом дешифратора, блок генерации циклов обмена, вход сброса и выход стробов сброса которого подключены соответственно к второму выходу и второму синхронизируимцему входу регистра состояния и управления , а информационный вход и вход обращения - соответственно к второму выходу формирователя адреса и четвертому выходу дешифратора, группу блоков формирования линейных сигналов, первые входы и выходы которых являются соответственно линейными входом и выходом устройства, группу блоков буферной памяти и группу регистров управления приемом-передачей, причем вторые вход и выход каждого блока формирования линейных сигналов группы соединены соответственно спервьмн информационными выходом и входом соответствующего блока буферной памяти группы, выход сигналов ошибки и вход режима обмена которого подключены соответственно к первому информационному входу и первому выходу соответствующего регистра управления приемом-передачей, вторые информационные входы блоков буферной памяти группы и регистров управления приемом-передачей группы соединены с вторым выходом блока усиления, четвертый вход которого подключен к вторым выходам регистра управления приемомпередачей, третьи информационные входы и третьи выходы которых соединены соответственно с выхЬдом сигналов режима обмена блока генерации циклов обмена и входами сброса блоков буферной памяти группы и с входом сигналов запроса прерьшания блока обработки запросов на прерывание, вход раз1512решения которого соединен с третьим выходом регистра состояния и управления, о тличающееся тем, что, е целью повьшения пропускной способности устройства, в него введены блок формирования сигнала реакции линии связи, причем четвертые выходы регистров управления приемом-передачей группы соединены с вторым информационным входом регистра состояния и управления и входом ответного сигнала блока формирования сигнала реакции линии связи, выход и вход синхронизации и вход сброса которого подключены соответсвенно к входу и выхо-. ду синхронизации блока генерации циклов обмена и четвертому выходу регистра состояния и управления, входом сброса соединенного с выходом сброса блока обработки запросов на прерыйание, выход сигнала прерывания которого подключен к третьему информационному входу дешифратора, пятым выходом и четвертым информационным входом соединенного соответственно с входом обращения и выходом сигнала реакции блока формирования сигнала реакции линии связи, вход разрешения которого соединен с третьим выходом формирователя адреса, синхронизирующий вход которого подключен к четвертому 216 выходу блока усиления, вторые информационные выходы блоков буферной памяти группы соединены с третьим входом блока усиления, 2. Устройство по п,1, о т л и чающееся тем, что блок формирования сигнала реакции линии связи содержит триггер, три элемента И, элемент ИЛИ, элемент задержки и элемент НЕ, причем первый вход элемента И является входом обращения блока, а выход соединен с входом сброса триггера и через элемент задержки с выходом синхронизации блока и первым входом второго элеме нта И, вторым входом подключенного к входу сброса блока, а третьим входом - к входу разрешения блока и через элемент НЕ к первому входу третьего элемента И, второй вход которого соединен с вторым входом первого элемента И и вхо- дом разрешения блока, а третий и четвертьй входы являются соответственно входом синхронизации блока и входом ответного сигнала блока, первый и второй входы элемента ИЛИ подключены соответственно к выходам второго и третьего элементов И, а выход - к входу установки триггера, выход которого является выходом сигнала реакции блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронных вычислительных машин | 1984 |

|

SU1257653A2 |

| Устройство для сопряжения двух электронных вычислительных машин | 1985 |

|

SU1249523A2 |

| Устройство для сопряжения электронных вычислительных машин | 1980 |

|

SU962905A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1988 |

|

SU1515168A1 |

| Устройство для сопряжения ЭВМ в вычислительной системе с децентрализованным арбитром магистрали | 1984 |

|

SU1291997A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1984 |

|

SU1251093A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1987 |

|

SU1411764A1 |

| Устройство для обмена информацией двух электронно-вычислительных машин | 1984 |

|

SU1231507A1 |

| Устройство для сопряжения ЭВМ с датчиками состояния телефонных линий связи | 1984 |

|

SU1265786A1 |

Т

ownfp

(

«1

«/

40

ЧТРПР

4f

iff

1tf6

Г39

/13

fJS

QCSP

т

/

л

Ht3

fAS

ТГСИП /AJ

q)uf,ff

35SAHT

m

Ю8

f(M

1

АРУ ЗЫ80й

АРт

B80U

тгскп

Tt,7

npfp

161

.f

ЗПСРУ

т

ЗПМРУ

V4

Ш

ЗГ№НЗ ВВОЛ

r-f37

86im sssr,

serstte

f

CTPf

157

умг

rS9

-ff

41-,

Qr

UALOl

S8

JS3 С6РОС

VK

8

92

РМЗЩ}

PH3LJ51

43 -

УП

QI

т

т

ЗЛ8

S8

Qe

п

т

J65

гН-

TSJ

М

170

Pifin

/7/

Ш

У7РМЗ

--

евол

т

162- ППРГ

ff

.т

CffflfSJ

/а

172

фifг.fJ

| Устройство для сопряжения | 1982 |

|

SU1051526A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения электронных вычислительных машин | 1980 |

|

SU962905A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-07—Публикация

1985-01-09—Подача