Изобретение относится к вычислительной технике и может быть использовано для сопряжения электронно-вычислительных машин (ЭВМ) с интерфейсом Общая шина (ОШ) , в информационно-измерительных и автоматизированных системах управления. . Известно устройство для сопряжения цифровой вычислительной машины с внешними устройствами, содержащее блоки обмена, приемо-передаюисий узел, дешифратор 1.

Недостатком указанного устройства является низкая пропускная способность вследствие значительных затрат машинного времени для передачи массивов информации между ЭВМ внешними устройствами, поскольку ВМ участвует во всем цикле передали , преобразования из параллельного в последовательный код каждого слова информации.

Наиболее близким к предлагаемому по технической сущности является устройство для сопряжения периферийной системы с электронной вычислительной мгшганой, содержащее дешифратор, регистр управления, блок выполнения прерывания, блок обмена, коммутатор, пepeключiaтeль, блоки

усиления, первый из которых соединен с обшей шиной ЭВМ, первый, второй, третий и четвертый выходы первого блока усиления соединены соответственно с первыми входами, дешифратора, коммутатора, регистра управления и блока, выполнения пре1 1вания, первый, второй и третий входы первого блока усиления соединены соответственно с первыми выходами дешифратора, регистра управления и блока выполнения прерывания, второй и третий входы дешифратора соединены соответственно с первыми выходами коммутатора и блока обмена, второй и третий выходы дешифратора соединены соответственно с первым входом блока обмена, с вторым входом регистра управления, второй и тре20тий выходы которого соединены соответственно с вторыми входами блдка обмена и блока выполнения прерывания, второй выход блока обмена соединен с третьим входом регистра 25 управления, четвертый выход дешифратора соединен с третьим входом блока об1 «{ена. 2,

недостаток известного устройства - низкая пропускная способность

Цель изобретения - повышение пропускной.способности устройства.

Поставленная цель достигается тем, что в устройство, содержащее дешифратор, регистр управления, блок выполнения прерывания, блок обмена, коммутатор, блок усиления, соединенный с входом-выходом устройства, первый, второй, третий и четвертый., выходы блока усиления соединены соответственно с первыми входами дешифратора, коммутатора/ регистра управления.и блока выполнения прерывания, первый, второй и третий входы блока усиления соединены соответственно с первыми выходами дешифратора, регистра управления и блока выполнения прерывания, второй и третий входы дешифраторасоединены соответственно с выходом коммутатора и первым выходом блока обмена, второй и третий выходы дешифратора соединены соответственно с первым входом блока обмена и с. вторым входом регистра управления,, второй и третий выходы которого соединены соответственно с вторыми .входами блока обмена и блока выполнения прерывания, второй выход блока обмена соединен с третьим входом регистра управления, введены группа блоков буферной памяти, группа регистров управления приемом-передачей, группа блоков приема-передачи и группа формирователей сигналов, причем выход коммутатора соединен с третьим входом блока обмена, третий выход блока усиления соединен с первыми входами блоков буферной памяти группы и первыми входами регистров управления приемом-передачей группы, второй вход блока усиления соединен с первыми выходами блоков буферной памяти группы и первым выходами регистров управления приемом-передачё,й группы, второй и третий выходы i-ro блока буферной памяти группы (i . 1,п) соединены соответственно с четвертым входом регистра управления и с первым входом i-ro блока приема-передачи группы, второй и третий выходы i-ro регистра управления приемом-передачей группы соединены соответственно с i-M входом входов блока выполнения прерывания и .с вторым входом i-ro блока буферной п&мяти группы, а второй и третий входы соответственно с третьим выходом блока обмена и с первым выходом i-r блока приема-передачи группы, второ .третий и четвертый выходы которого соединены соответственно С третьим и четвертым входами i-ro блока буферной памяти группы и с первым входом i-ro формирователя сигналов группы, второй вход,первый и второ выходы которого соединены соответственно с 1-ми входом и выходом линейной группы входов и выходов устройства и с вторьм входом i-ro блока приема-передачи группы, четвертый выход дешифратора соединен с третьим входом блока выполнения прерывания.

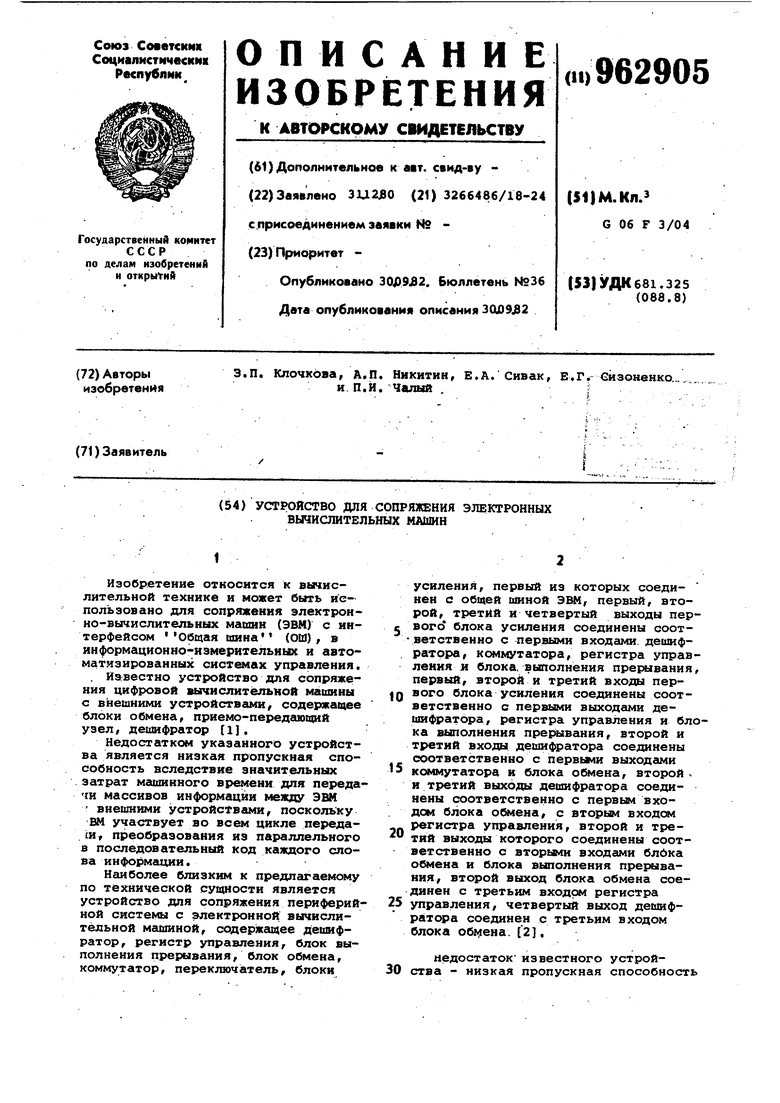

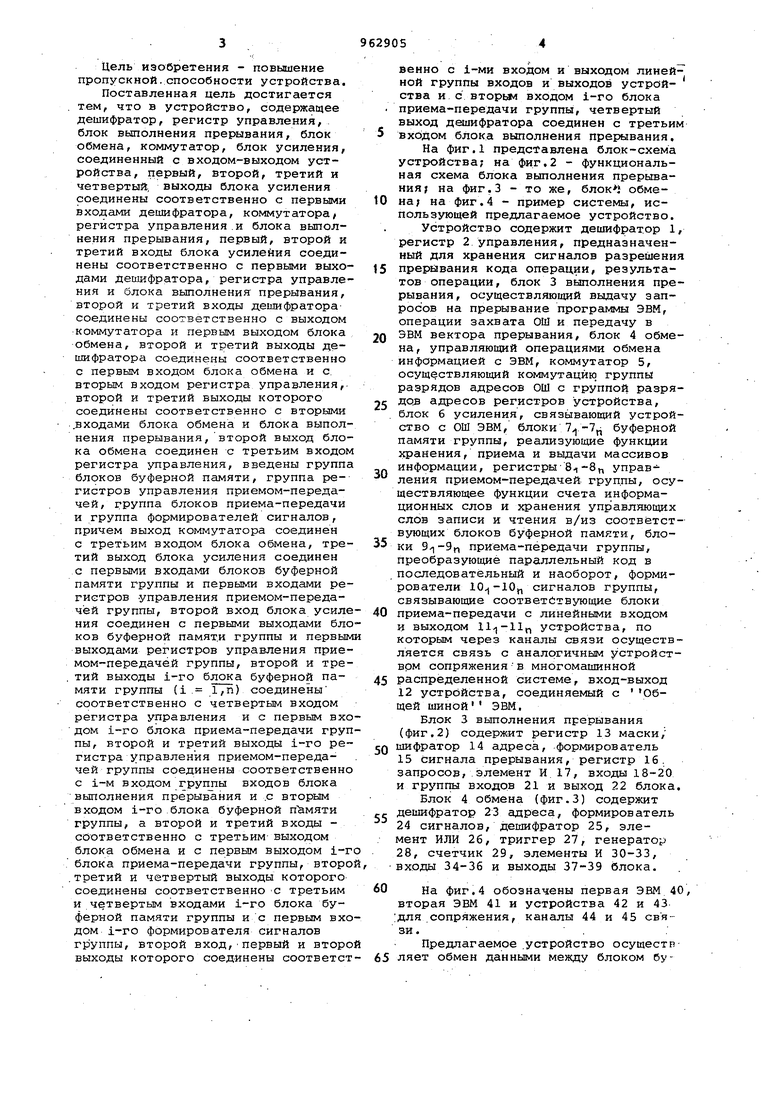

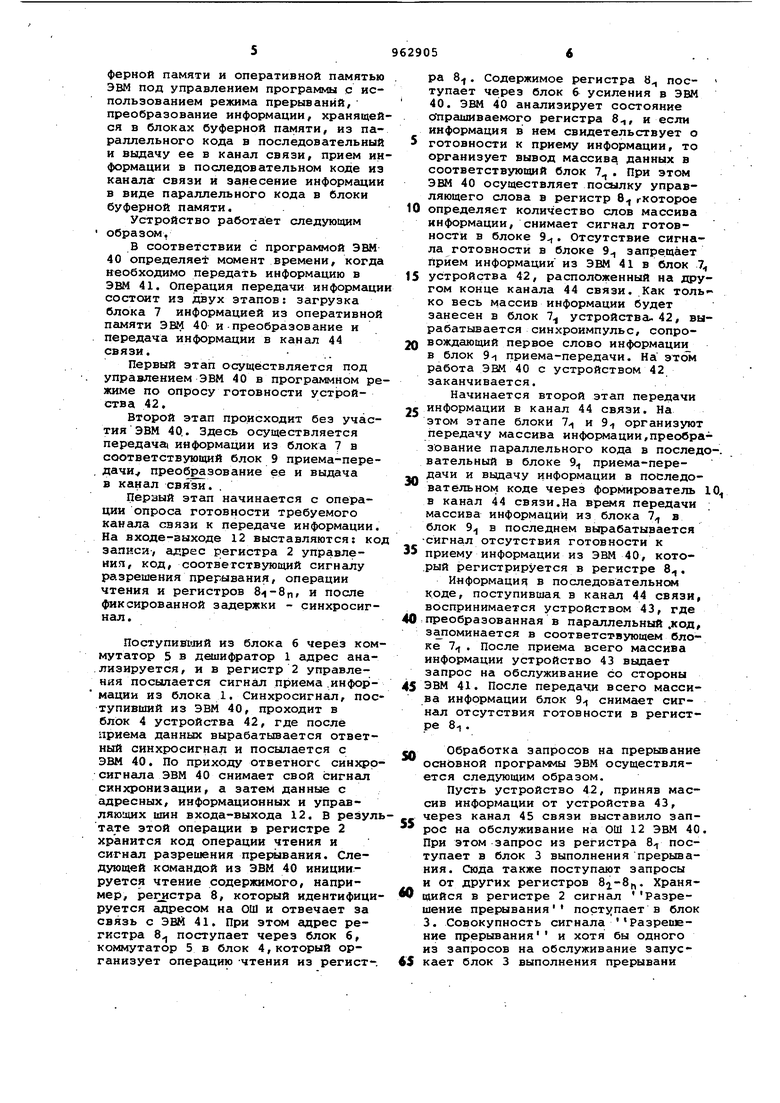

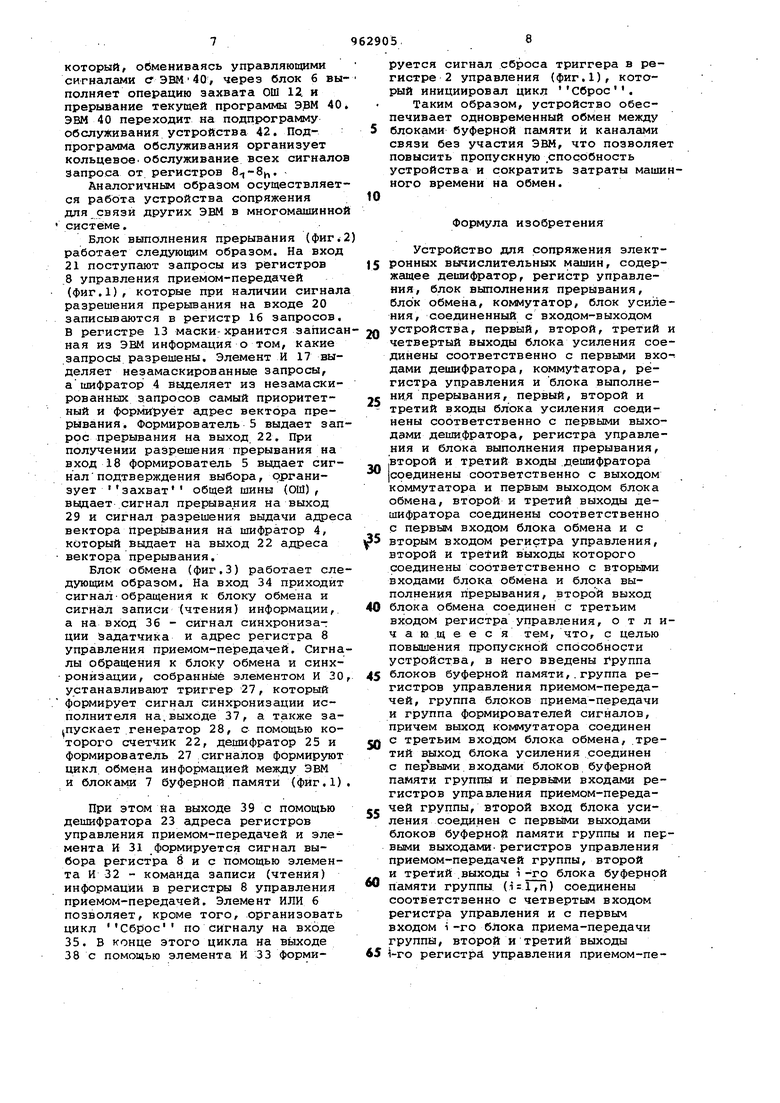

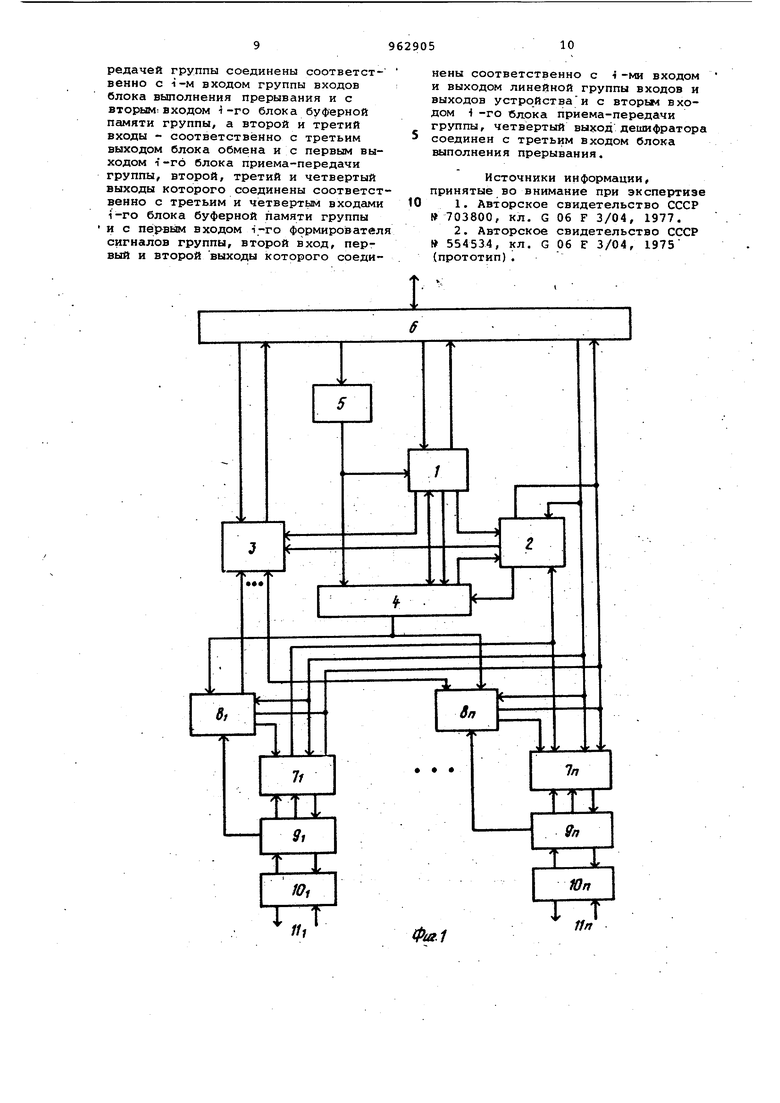

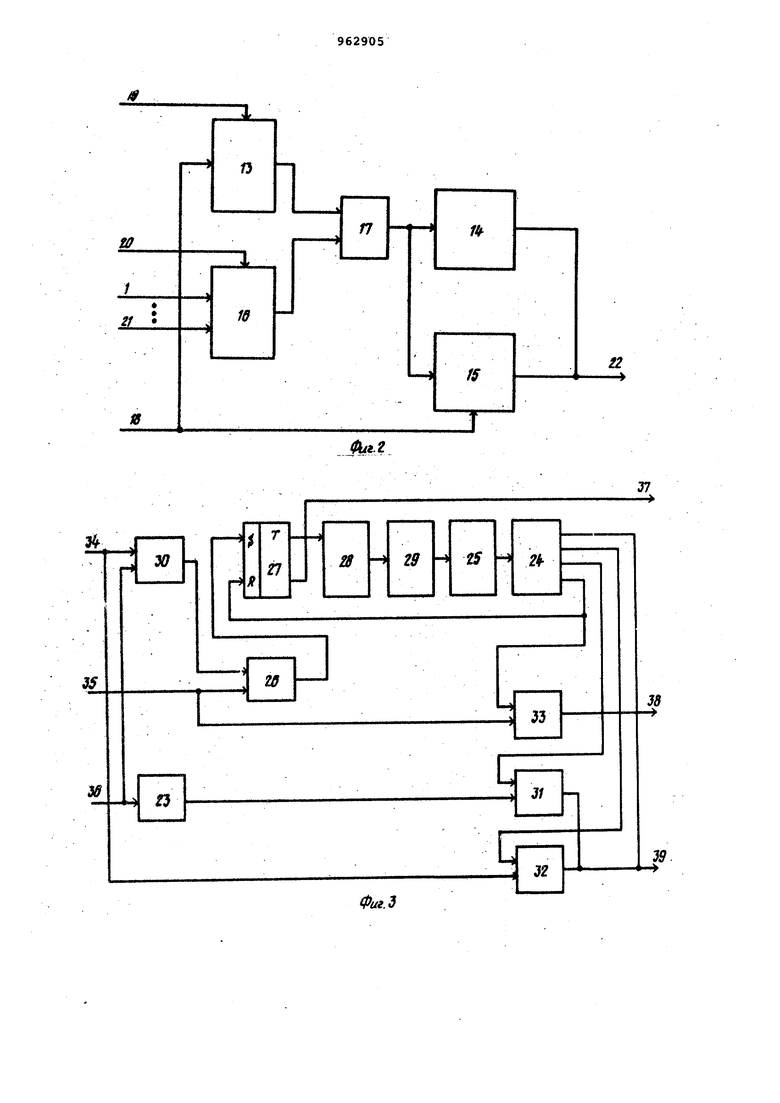

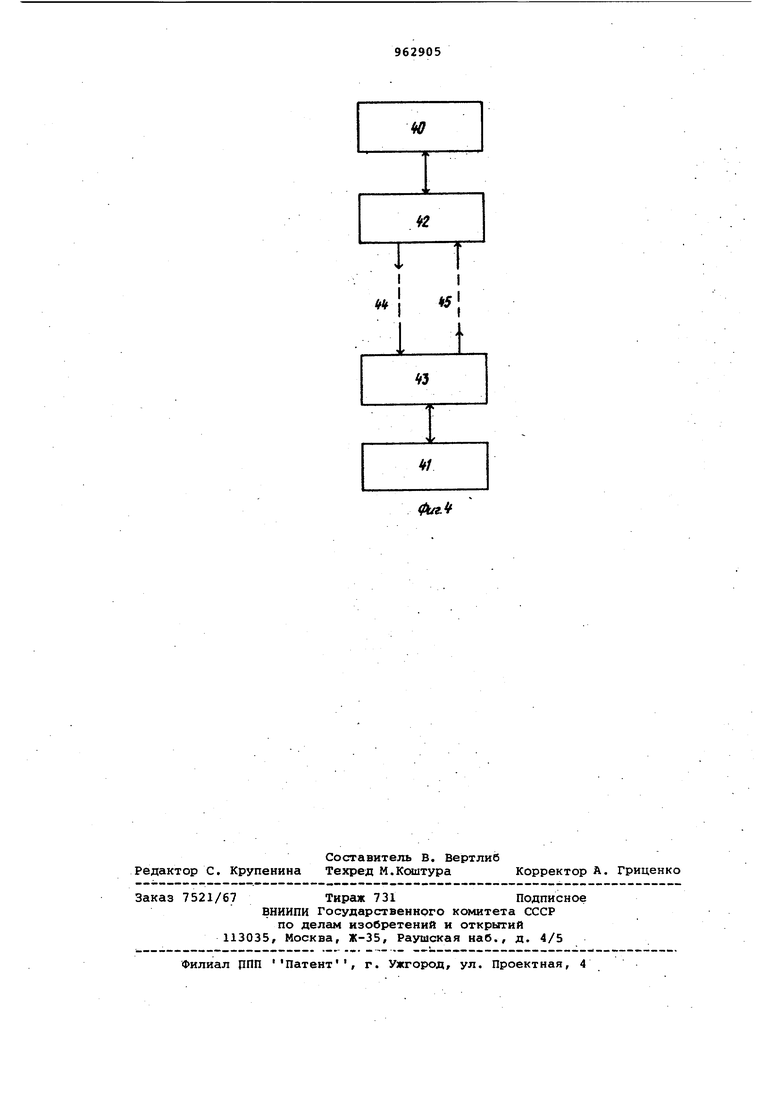

На фиг.1 представлена блок-схема устройства; на фиг.2 - функциональная схема блока выполнения прерывания; на фиг.З - то же, обмена; на фиг.4 - пример системы, использующей предлагаемое устройство.

Устройство содержит дешифратор 1, регистр 2 управления, предназначенный для хранения сигналов разрешения прерывания кода операции, результатов операции, блок 3 выполнения прерывания, осуществляющий выдачу запросов на прерывание программы ЭВМ, операции захвата ОШ и передачу в ЭВМ вектора прерывания, блок 4 обмена, управляющий операциями обмена информацией с ЭВМ, коммутатор 5, осуществляющий коммутацию группы разрядов адресов ОШ с группой разрядов адресов регистров устройства, блок б усиления, связывающий устройство с ОШ ЭВМ, блоки буферной памяти группы, реализующие функции хранения, приема и выдачи массивов информации, регистры-8 -8 управления приемом-передачей группы, осуществляющее функции счета информационных слов и хранения управляющих слов записи и чтения в/из соответствующих блоков буферной памяти, блоки 9i-9fi приема-передачи группы, преобразуюгциё параллельный код в последовательный и наоборот, формирователи , сигналов группы, связывающие соответствующие блоки приема-передачи с линейными входом и выходом устройства, по которым через каналы связи осуществляется связь с аналогичным Устройством сопряженияв многомашинной распределенной системе, вход-выход 12 устройства, соединяемый с Общей шиной ЭВМ,

Блок 3 выполнения прерывания (фиг.2) содержит регистр 13 маски, шифратор 14 адреса, формирователь 15 сигнала прерывания, регистр 16. запросов, элемент И 17, входы 18-20 и группы входов 21 и выход 22 блока.

Блок 4 обмена (фиг.З) содержит дешифратор 23 адреса, формирователь 24 сигналов, дешифратор 25, элемент ИЛИ 26, триггер 27, генератор 28, счетчик 29, элементы И 30-33, входы 34-36 и выходы 37-39 блока.

На фиг.4 обозначены первая ЭВМ 40 вторая ЭВМ 41 и устройства 42 и 43 для сопряжения, каналы 44 и 45 свяЗИ . .

Предлагаемое .устройство осуществляет обмен данными между блоком буферной памяти и оперативной . ЭВМ под управлением программы с использованием режима прерываний, преобразование информации, хранящейся в блоках буферной памяти, из параллельного кода в последовательный и выдачу ее в канал связи, прием информации в последовательном коде из канала: связи и занесение информации в виде параллельного кода в блоки буферной памяти.

Устройство работает следующим образом.

В соответствии с программой ЭВМ 40 определяет момент времени, когда необходимо передать информацию в ЭВМ 41. Операция передачи информации состоит из двух этапов: загрузка блока 7 информацией из оперативной памяти ЭВМ 40 и преобразование и передача информации в канал 44 связи.

Первый этап осуществляется под управлением ЭВМ 40 в программном режиме по опросу готовности у стройства 42.

Второй этап происходит без участия ЭВМ 40,. Здесь осуществляется передача информации из блока в соответствующий блок 9 приема-передачи преобразование ее и выдача в канал связи. .

Первый этап начинается с операции опроса готовности требуемого канала связи к передаче информации. На входе-гыходе 12 выставляются: код записи-, адрес регистра 2 управления, код, соответствующий сигналу разрешения прерывания, операции чтения и регистров 8-1-8п/ и после фиксированной задержки - синхросигнал .

Поступиврлий из блока 6 через коммутатор 5 в дешифратор 1 адрес анализируется, и в регистр 2 управления посылается сигнал приема .информации из блока 1. Синхросигнал, поступивший из ЭВМ 40, проходит в блок 4 устройства 42, где после приема данных вырабатывается ответный синхросигнал и посылается с ЭВМ 40. По приходу ответногс синхррсигнала ЭВМ 40 снимает свой сигнгш синхронизации, а затем данные с адресных, информационных и управляющих шин входа-выхода 12. В результате этой операции в регистре 2 хранится код операции чтения и сигнал разрешения пресшвания. Следующей командой из ЭВМ 40 инициируется чтение содержимого, например, регистра 8, который идентифицируется адресом на ОШ и отвечает за связь с ЭВЙ 41. При этом адрес регистра 8 поступает через блок б, коммутатор 5 в блок 4, который организует операцию -чтения из регистра 8. Содержимое регистра Й поступает через блок & усиления в ЭВМ 40. ЭВМ 40 анализирует состояние «Опрашиваемого регистра 8, и если информация в нем свидетельствует о

готовности к приему информации, то организует вывод массива данных в соответствующий блок 7. При этом ЭВМ 40 осуществляет посылку управляющего слова в регистр 8 гкоторое

0 определяет количество слов массива информации, снимает сигнал готовности в блоке 9. Отсутствие сигнала готовности в блоке 9 запрещает прием информации из ЭВМ 41 в блок 7

5 устройства 42, расположенный на другом конце канала 44 связи. Как весь массив информации будет занесен в блок 7 устройства- 42, вырабатывается синхроимпульс, сопроQ вождающий первое слово информации в блок 9i приема-передачи. На этом работа ЭВМ 40 с устройством 42 заканчивается.

Начинается второй этап передачи

5 информации в канал 44 связи. На

этом этапе блоки 7 и Э организуют передачу массива информации,преобразование параллельного кода в последе-, вательный в блоке 9 приема-передачи и вьщачу информации в последо0

вательном коде через формирователь 10 в канал 44 связи.На время передачи массива информации из блока 7 в блок 9 в последнем вырабатывается -сигнал отсутствия готовности к

5 приему информации из ЭВМ 40, который регистрируется в регистре 8, Информация в последовательном коде, поступившая в канал 44 связи, воспринимается устройством 43, где

0 преобразованная в параллельный .код, запоминается в соответствующем блоке 7 . После приема всего массива информации устройство 43 выдает запрос на обслуживание со стороны

5 ЭВМ 41. После передачи всего массива информации блок 9 снимает сигнал отсутствия готовности в регистре 8-, .

Обработка запросов на прерывание о«1(эвной программы ЭВМ осуществляется следующим образом.

Пусть устройство 42, приняв массив информации от устройства 43, через канал 45 связи выставило запрос на обслуживание на ОШ 12 ЭВМ 40. При этом запрос из регистра 8 поступает в блок 3 выполнения прерывания. Сюда также поступают запросы и от других регистров ,. Хранящийся в регистре 2 сигнал Разрешение прерывания поступает в блок 3. Совокупность сигнала Разрешение прерывания и хотя бы одного из запросов на обслуживание запускает блок 3 выполнения прерывани который, обмениваясь управляющими сигналами с ЭВМ40, через блок 6 вы полняет операцию захвата ОШ 1Z и прерывание текущей программы ЭВМ 40 ЭВМ 40 переходит на подпрограмму обслуживания устройства 42. Подпрограмма обслуживания организует кольцевое обслуживание всех сигнало запроса от регистров 8,,-8ц, Аналогичным образом осуществляет ся работа устройства сопряжения для связи других ЭВМ в многомашинно системе. Блок выполнения прерывания {фиг. работает следующим образом. На вход 21 поступают запросы из регистров 8 управления приемом-передачей (фиг.1), которые при наличии сигнал разрешения прерывания на входе 20 записываются в регистр 16 запросов. В регистре 13 маски-хранится записа ная из ЭВМ информация о том, какие запросы разрешены. Элемент И 17 выделяет незамаскированные запросы, ашифратор 4 выделяет из незамаскированных запросов самый приоритетный и форгйируёт адрес вектора прерывания. Ф эрмирователь 5 выдает зап рос прерывания на выход 22. При получении разрешения прерывания на вход 18 формирователь 5 выдает сигнал подтверждения выбора, организует захват общей шины (ОШ), вьдает сигнал прерывания на выход 29 и сигнал разрешения выдачи адрес вектора прерывания на шифратор 4, который выдает на выход 22 адреса вектора прерывания. Блок обмена (фиг.З) работает сле дующим образом. На вход 34 приходит сигналобращения к блоку обмена и сигнал записи (чтения) информации, а на вход 36 - сигнал синхрониза-: ции Задатчика и адрес регистра 8 управления приемом-передачей. Сигна лы обращения к блоку обмена и синхронйзации, собранные элементом И 30 устанавливают триггер 27, который . формирует сигнал синхронизации исполнителя на.выходе 37, а также заjnycKaeT генератор 28, с помощью которого счетчик 22, дешифратор 25 и формирователь 27 сигналов формируют цикл, обмена информацией между ЭВМ и блокаьга 7 буферной памяти (фиг.1) При этом йа выходе 39 с помощью дешифратора 23 адреса регистров управления приемом-передачей и Элемента И 31 формируется сигнал выбора регистра 8 и с помощью элемента И 32 - команда записи (чтения) информации в регистры 8 управления приемом-передачей. Элемент ИЛИ 6 позволяет, кроме того, организовать цикл Сброс по сигналу на входе 35. В конце этого цикла на выходе 38 с помощью элемента И 33 формируется сигнал сброса триггера в регистре 2 управления (фиг.1), который инициировал цикл Сброс. Таким образом, устройство обеспечивает одновременный обмен между блоками буферной памяти и каналами связи без участия ЭВМ, что позволяет повысить пропускную способность устройства и сократить затраты машинного времени на обмен. Формула изобретения Устройство для сопряжения электронных вычислительных машин, содержащее дешифратор, регистр управления, блок выполнения прерывания, блок обмена, коммутатор, блок усиления, соединенный с входом-выходом устройства, первый, второй, третий и четвертый выходы блока усиления соединены соответственно с первыми входами дешифратора, комму атора, регистра управления и блока выполнения прерывания, первый, второй и третий входы блока усиления соединены соответственно с первыми выходами дешифратора, регистра управления и блока выполнения прерывания, |второй и третий входы дешифратора Срединены соответственно с выходом коммутатора и первым выходом блока обмена, второй и третий выходы дешифратора соединены соответственно с первым входом блока обмена и с вторым входом регистра управления, второй и третий выходы которого соединены соответственно с вторыми входами блока обмена и выполнения Прерывания, второй выход блока обмена соединен с третьим входом регистра управления, о т л ич а ю .щ е е с я тем, что, с целью повышения пропускной способности устройства, в него введены i pynna блоков буферной памяти,.группа регистров управления приемом-передачей, группа блоков приема-передачи и группа формирователей сигналов, причем выход коммутатора соединен с третьим входом блока обмена, третий выход блока усиления соединен с первыми. входами блоков буферной памяти группы и первыми входами регистров управления приемом-передачей группы, второй вход блока усиления соединен с первыми выходами блоков буферной памяти группы и первыми выходами- регистров управления приемом-передачей группы, второй и третий .выходы i -го блока буферной памяти группы (,n) соединены соответственно с четвертьм входом регистра управления и с первым входом i-го блока приема-передачи группа, второй и третий выходы i-ro регистра управления приемом-передачей группы соединены соответстввнно с i-м входом группы входов блока выполнения прерывания и с вторым входом i-го блока буферной памяти группы, а второй и третий входы - соответственно с третьим выходом блока обмена и с первым выходом 1-го блока приема-передачи группы, второй, третий и четвертый выходы которого соединены соответственно с третьим и четвертьлм входами i-ro блока буферной памяти группы и с первым входом 1-го формировател сигналов группы, второй вход, первый и второй выходы которого соединены соответственно с i-ми входом и выходом линейной группы входов и выходов устройства и с вторым входом i -го блока приема-передачи группы, четвертый выход дешифратора соединен с третьим входом блока выполнения прерывания.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР №703800, кл. G 06 F 3/04, 1977.

2. Авторское свидетельство СССР 554534, кл. G 06 F 3/04, 1975 (прототип).

to

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронных вычислительных машин | 1984 |

|

SU1257653A2 |

| Устройство для сопряжения двух элект-РОННыХ ВычиСлиТЕльНыХ МАшиН | 1979 |

|

SU809147A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1985 |

|

SU1249523A2 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Устройство для сопряжения электронных вычислительных машин | 1981 |

|

SU1013938A1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

| Устройство для сопряжения двух электронных вычислительных машин (эвм) | 1984 |

|

SU1187172A1 |

| Устройство для сопряжения периферийной системы с электронной вычислительной машиной | 1975 |

|

SU554534A1 |

W

2f :

t8

tz

15

Т f

5

Авторы

Даты

1982-09-30—Публикация

1980-12-31—Подача