аяпроса прерываний устройства, выход эпемента ИЛИ соединен с третьим входом бпока прерываний, а второй вхоц-выкод регистра данных соединен с BTofttiiM информационным ВХОДОМ-БЫХОПОМ устройства. 2. Устройство по п. 1, отличают е е с я тем, что бпок управления содержит, четыре эпемента -И-НЕ, генератор тактовых импупьсов, два сдвигающих регистра, четыре триггера, два эпемента И, дешифратор, эпемент ПОИ и формирова тепь импупьса, причем первые входы первых элементов И и И-НЕ, первый вход дешифратора, информационный вход первого триггера и первый вход элемента ИЛИ образуют первый вход бпока, выход первого эпемента И соединен с синхронизирукяцим входом первого триггера и с информационным-и установочным входа™ ми второго триггера, синхронизирующий вход которого и синхронизирующие входы первого и второго сдвигающих регистров соединены с В111ходом генератора тактовых импупьсов, первый и второй выхоаы первого сдвигающе:х регистра соединены соответственно с управпяющим входом второго сдвигающего регистра и с синхро низирующим входом третьего триггера, информационный вход которого соединен с шиной нупевого потенциапа, единичный установочный вход с синхронизирующим входом четвертого триггера и с первым выходом второго сдвигаю1дего регистра, второй выход которого соединен с первым входом второго элемента И-НЕ, выход которого соединен с вторым выходом бпо ка, выхоп второго - триггера соединен с перЕ)ым входом третьего эпемента И-НЕ и с единичным установочным входом четвертого триггера, выход которого соединен с nepBfiiM входом четвертого эпе мента И-НЕ, второй вход которого соед№ нен с выходом третьего элемента И-НЕ второй вход которого соединен с: информационным входом четвертого триггера и с выходом эпемента ИЛИ, выход третьего триггера соединен с вторым входом дешифратора, третий вход которого, вход формировятепя импупьсов, второй вход второго эпемента И-НЕ, второй вход эпемента ИЛИ, выход первого триггера, первый вход и выход второго эпемента И и четвертый вход дефифратора образуют второй вход-выход бпока, выход четвертого эпемента И-НЕ. и второй вход первого элемента И образуют первый входвыход бпока, информационный вход первог сдоигающего регистра и второй вход первого эпемента И-ИЕ соединеш.г с вторым входом бпока, третий выход второтх. сав гающего регистра соединен с первым втлходом б7юка, выход 4 рмироватепя импупь(Х)в, выходы дешифратора, иш}ормац онный вход второго сдвигаст.цего регистра и инверсный вход второго эпемента И образуют третий вход-выход бпока, вы- , ход первого эпемента И-НЕ соединен с нулев1:.1М установочшлм входом третьего триппера. 3. Устройство по п, 1, о т п к ч а ю щ е е с я тем, что бпок прерываний содержит три триггера, два эпемента ИЛИ, три эпемента И, два эпемента И-НЕ и эпемент НЕ, причем вход установки в единичное состояние первого триггера соединен с вторым входом бпока, информационный вход - с шиной нупевого потенниапа, синхронизирующий вход - с перв1:.м входом бпока и с входом установ ки в нулевое состояние Bjoporcj триггера, прямой выход - с первым входом первого эпемента ИЛИ и инверсный выход с первым входом первого эпемента И, второй вход которого соединен с вторым входом первого эпемента ИЛИ и с третьим входом бпока, выход первого эпемента ИЛИ соединен с первыми входами втс рого элемента И и первого элемента И-НЕ и с входом установки в нупевое состояние третьего триггера, информационный вход которого соединен с выходом второго эпемента И-НЕ, инверсный выход - с первым входом второго эпемента И-НЕ, а прямой выход - с первым входом треть-, его эпемента И и с информационным входом второго триггера, синхронизирующий вход которого соединен с и-.1хоаом первого эпемента И-НЕ, прямой выход с вторыми входами третьего эпемента И, второго эпемента И-НЕ, а инверсный выход - с вторым входом первогх) эпемента И-НЕ, третий вход которого соединен с выходом BTopoix) эпемента ИЛИ, выход третьего эпемента И соединен через эпемент НЕ с первым входом второго эпемента ИЛИ, выходы первого и третьего элементов И образуют выход, бпока второй вход второго эпемента ИЛИ, выход эпемента НЕ, второй вход и. выход второго эпемента И и сиш(.ронизирую1ций вход третьего триггера образуют входвыход блока. 4. Устройство по п. 1, о т п и ч 9 ю щ е е с я тем, что Опок захвата магистрали содержит тряггчэр, два коммутатора и два эпемента И, причем cинxpзн V зирующий вход тригге{.та соединен с гсер

вым входом бпока, вход установки в единичное состояние - с четвертым входом блока, информационный вход - с шиной нулевого потенциала, а выход - с первым входом первого эпемеита И, второй вход которого соединен с вторым входом бпока, а выход -. с входом первого коммутатора

НС первым вводом второгоэпеменгаИ.вто- рой вхои которого соединен с выходом ВТ коммутатора, выход второго элемента И сое аи иен с вторым выходом блока,входы вто рого коммутатора соединены с третьим вхо Дом бпокв,а выходы первого коммутатора соединены с первым выходом бпока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

| Устройство для согласования системных магистралей | 1989 |

|

SU1674143A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения вычислительной машины с периферийными устройствами | 1981 |

|

SU960787A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

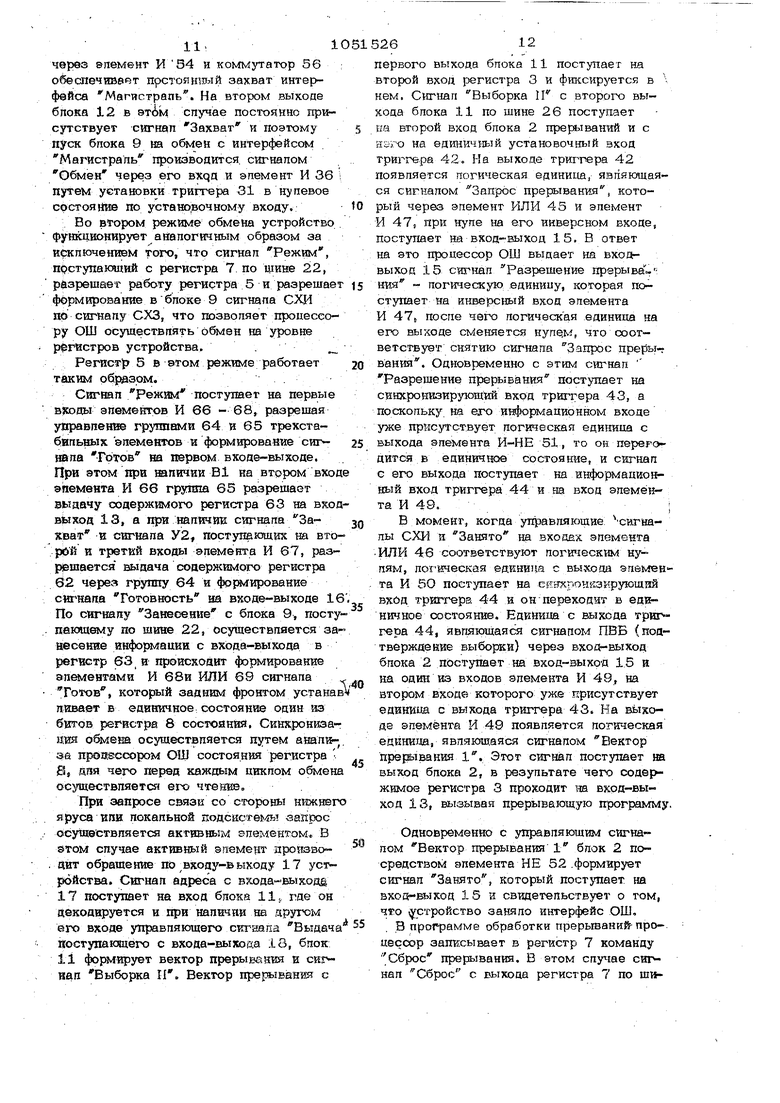

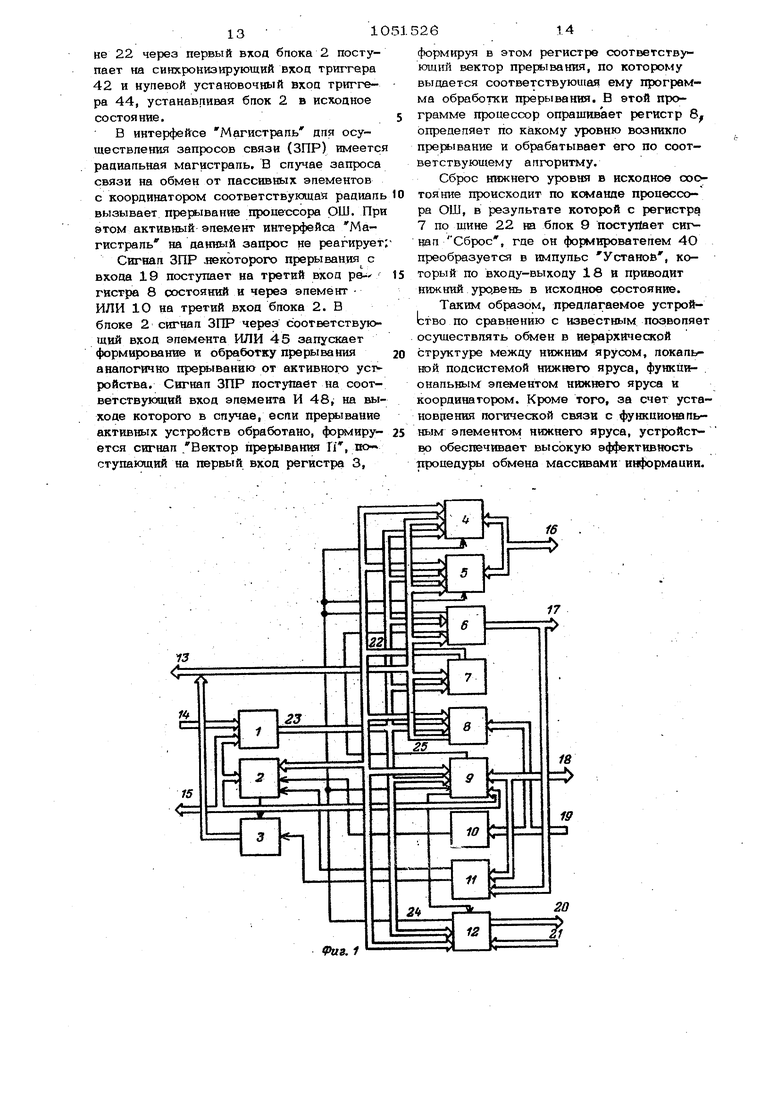

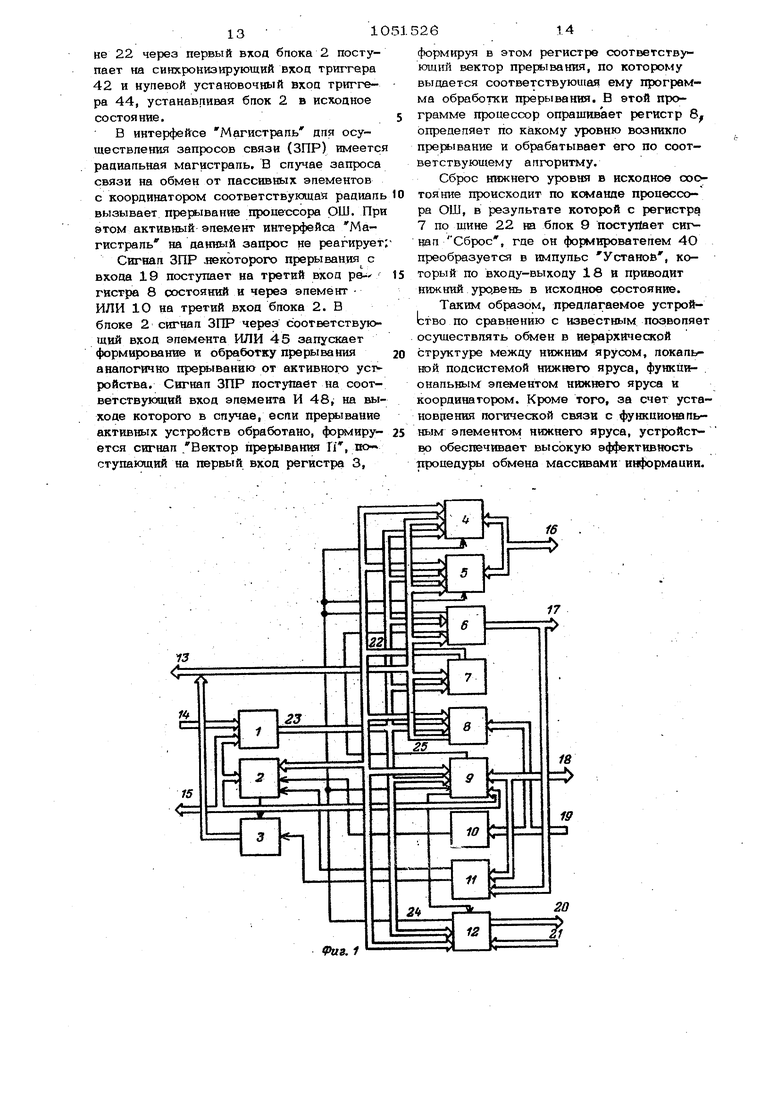

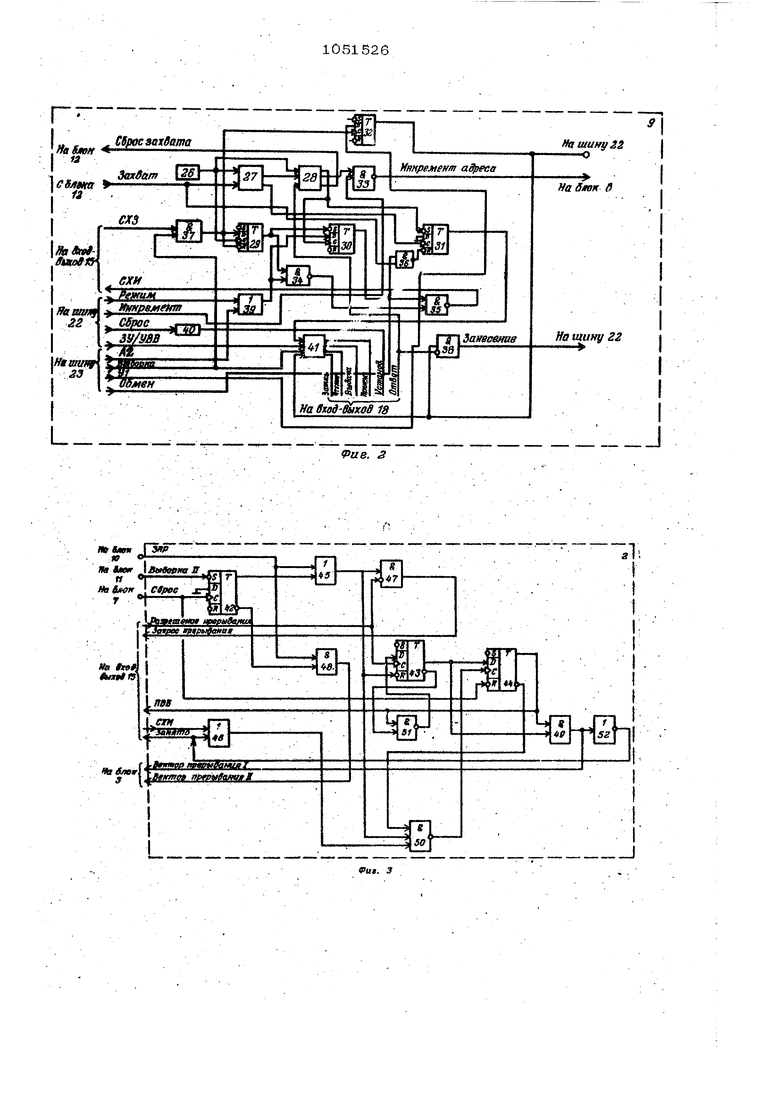

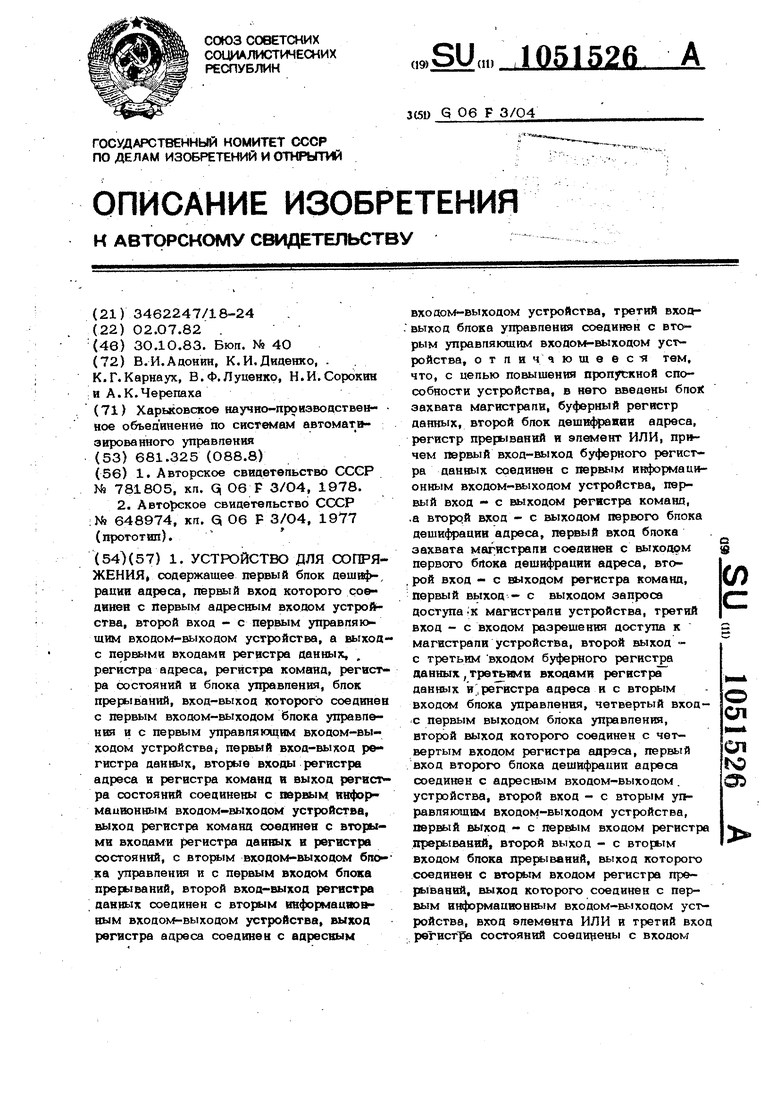

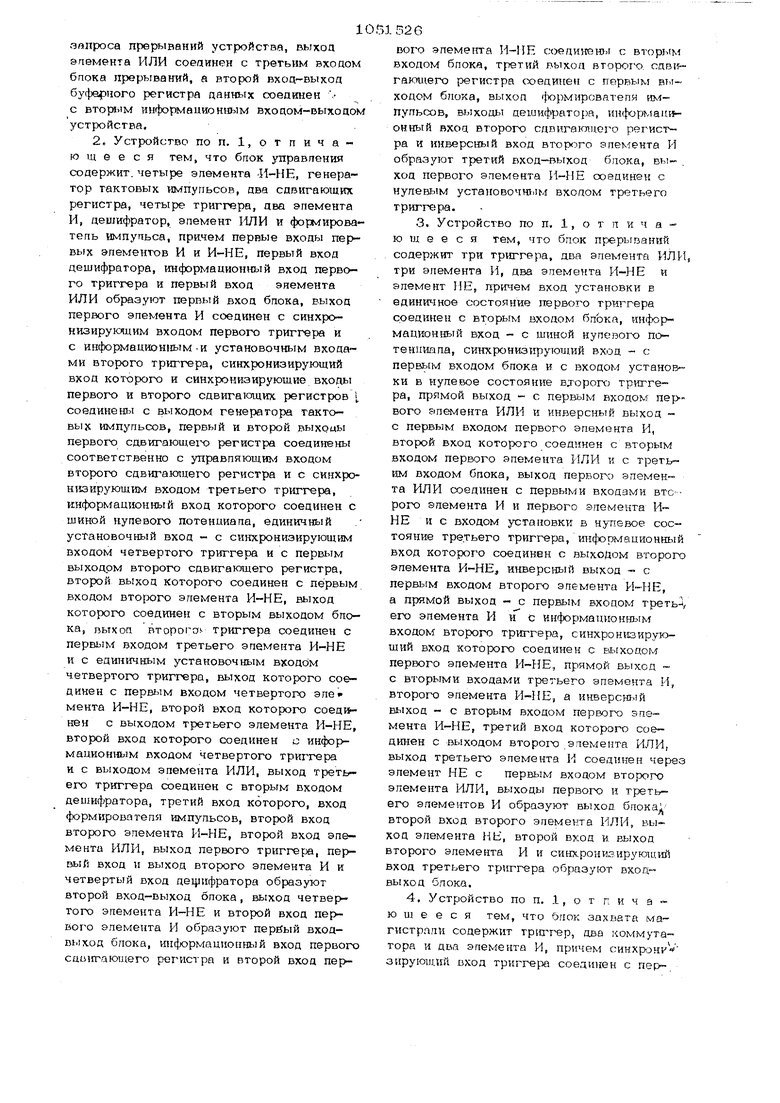

1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ г содержащее первый бпок дешй|| раиии адреса, первый вход которого соединен с первым адресным вхопом устройства, второй вход - с первым управляющим входом-выходом устройства, а выходс nepBbfMH входами регистра данных, регистра адреса, регистра команд, регистра состояний и бпока управпения, бпок прерываний, вход-выход которого соединен с первым входом-выходом блока управления и с первым управпяихцим входом-выходом устройства первый вход-выход регистра данных, вторые входы регистра адреса и регистра команд и выход регистра состояний соединены с первым информационным входом-выходом устройства, регистра команд соединен с вторыми входами регнстра данных и регистра состояний, с входом-выходом бпо-ка управпения и с первым входом бпока прерываний, второй вход-выход регистра данных соединен с вторым информаиаовным входок -выходом устройства, выход регистра адреса соединен с адресным входом-выходом устройства, третий вхоо. выход бпока управпения соединен с вто рым управпяющим входом-выходом устройства, отпиччющеес тем, что, с цепью повышения пропускной способности устройства, в него введены бпоК захвата магистрали, буферный регистр данных, второй бпок дешифравви адреса, регистр прерываний и эпемент ИЛИ, причем первый вход-выход буферного регистра данных соединен с информационным входом-и 1 ходом устройства, первый вход - с .ходом регистра команд, .а вторрй вход - с выходом первого бпока дешифрации адреса, первый вход бпока захвата магистрали соеди1юн с выходом первого бпока дешифрации адреса, вто(Л , рой вход - с выходом регистра команд, первый - с выходом запроса Доступа;к магнстрапи устройства, третий вход - с входом разрешения доступа к магистрали устройства, второй выход с третьим входом буферного регистра данных, третьнмв входами регистра данных и.регНстра адреса и с вторым входом бпока управления, четвёртый входел с первым выходом блока управпения, второй выход которого соединен с четел вертым входом регистра адреса, первый ГчЭ вход второго блока дешифрации адреса 05 соединен с адресным входом-выходом устройства, второй вход - с вторым управляющим входом-выходом устройства, первый выход - с первым входом регистра прерываний, второй выход - с вторым входом бпока прерываний, выход которого соединен с входом регистра прерываний, выход которого соединен с первым информационным входом-выходом устройства, вход элемента ИЛИ и третий вход регистр состояний соединены с входом

.. : . 1 . : . .

Изобретение отвосигся k вычнспитепьной технике и может быть использовано дпя сопряжения вычислительных систем, имеющих интерфейс типа рбшая шина (ОШ), с вычислительными системами,

имеющими интерфейс типа Магистраль и вкпючеиными по иерарх№1еской структуре. ;-;;. .-: , :

Известно устройство для сопряжения, содержащее дешифратор, блок управления прерыванием, блок управления вводом и блокуправления выводом lj

. Недостаток этого устройства заключается в ограниченных функциональных возможностях, так как оно позволяет осушествлять.обмен только между ярусак1И, поскольку со стороны интерфейса Магистраль участие в обмеве: предоставлен но лишь одному активному элементу, и и фррмашюнные потоки -от локаоьных поясистем и функдвк налью 1х 8пементов покальных подсистем всегда замыкаются на нем.

Наиболее блвзким к щюдлагаемому по техническому решению является устройство для сопряжения, соаеркашее первый блок дешифрации адреса, первый вкоа которого соединен с первым адресным BjconoKJ устройства, второй вход - с первым управляющим входом-выходом устрой ства, а выход - с первыми входами регистра дан1&1Хэ регистра адреса, регистра команды, регистра состояний и блока упрЕшления, блок прерываний, входгвыход которого соединен с цервым управляк щим входомг-выходом устройства, пе{шый вход-выход регистра данных, вторые вхоДЬ1 регистра адреса и регистра команд и выход регистра состояний соединены с первым информационным входом устрой ства, выход регистра команд соедвяен с вторыми входами регистра данных в регистра состояний, с вторым входом-выхо дом блока- управления и с першм входом

блока прерываний, второй вход-выход регистра данных соединен с вторым информационным входом-выходом устройства, выхоЬ регистра адреса соединен с вторым адресным входом-выходом устройства, первый и третий входы-выходы блока управления соединены соответственно с и вторым управляющими входамивыходами устройства ..

Недостаток этого устройства состоит в низкой скорости из-за ограниченных функциональных возможностей, поскольку 01Ю не позволяет осуществлять обмен при оргаН10ации на нижнем уровне локальных подсистем путем включения в интерфейс Магистраль активных элементов, а также вести обмен в режиме П1К1МОЙ логической связи.

Цель изобретения повышение пропусй ной способности устройства.

Поставленная цель достигается тем, что в устройство для сопряжения, содер-: жащее первый блсж дешифрации адреса, первый вход которого соединен с первым адресным входом устройства, второй входс первыми управляющим входом-выходом устройства, а выход - с первыми вхоцами регистра данных, регистра адреса, регист ра команд, регистра состояний и блока управления, блок прерываний вхоф-выход которого соединен с перюым входом-выходом блока управления и с первым упра ляющим вхоДс -выходом устройства, первый вход-выход регистра данных, вто рые входы регистра адреса и регистра и выход регистра состояний соединены с первым информационным входо| ь выкоаом устройства, выход регистра команд соединен с BTOJMJMH входами регистра данных и регистра состояний, с вто{ялм входом-ш 1ходсм бпока управления и с первым входом блока прерываний, второй вкоп-выход регистра данных соединен с вторым информационным входом31выкодом. устройства, регистра адреса- соеднвен с ацрескым входом-вы-ходом устройсгва, третий вхоо-выход бло ка управпения, Соединен с вторым управляющим входом- выходом устройства, видены блок захвата магистрапи, буфер.ный регистр данных, второй -бпок дешифрации адреса, регистр прерываний и .элементИЛИ, причем первый вход-выход буфернсгго регистра данных соецинен с пер.вым информационным входом-выходом 5 стройства, первый вход с .выходом регистра команд, -а второй вход - с выходом первого бпока .дешифрации адреса, первый вк.оц бпока захвата магистрали соединен с выходом первого блока дешифрации адреса, второй вход - с выходо регистра командГ .первый выход - .С вы, ходом эа.проса доступа к Магистрали уст ройства, .третий вход - с входом разре; . шеш-ы aocTjTia к магистрали устройства, второй выход .с третьим вх:одом буфер юго регистра данных, .третьими входами . регистра данньдх .и регистра адреса и С вторым входом блока управления, четвертый вход - с. первым выходом бпока управления, второй .выход которого соединен с четвертым входом регистра,адре се, первый вход второго, бдока.дешифрации адреса соединен с адресным входомвыходом устройства, второй .вход - с вторым, управляющим входом-выходом устройства, первый выход - с первым входом регистра прерываний, второй выход/ свторым -входом, блока прерываний выход которого соединен с вторым входом регистра прерываний, вых:од которог соединен с первым информационным входом-выходом устройства,. вход элемента ИЛИ третий вход регистра состояний сое дщень/ с входом запроса -прерываний устройства, выход элемента ИЛИ соедиН8.Н с третьим входом блока лрерываний а второй вход-выход буферного регистра данных -соеаинен с вторым информационным вкоаом-вы сояом устройства. - Блок управления содержит четыре эле мента И-НЕ, генератор тактовых сов, два сдвигающих регистра, четыре тригте-ра, два эпемент-з И дэшйфратор, элемент ИЛИ и формирователь импупьса, причем первые входы злемецтов И и И-НЕ, первый вход дашйфрагора, информационныйвход первого тр гггера к первый вход элементе ИЛИ образуют первый вход бпока, выход первого sneмента И соединен с синхронизирующим входом гюрвого триггера и с информашшкным и установочным вхог-ами второ264го тр г-гера, синхронизирующий вход ко .торого и синхронизирующие входы первого и вгорогю сдвигающих pervtcTtx B соеЦ1и1е.ны с выходом генератора тактовых та ш-ульсов, первый и второй выходы nef аого с.а..ющего регистра соединены соответсгвенно с- управпяющшч входом второго сдБИгающаго регистра и ссинхро низируюшю ВХОДОМ- третьего триггера, ккфорМБдионный вход которого с шиной ну-яевого ттотекциапа, единичный установочный вход - с синхронизирующим входом чет.верто1Х) триггера и с первьгм выходом второго сдвигающего регистра второй выход которого соединен с первым входом второго элемента И-НЕ, выход которого соединен с вторым выходом блока, выход второго трштера соединенс первым входом третьего элемента И-НЕ и с единичдаш установочным входом четвертого триггера, выход которого сое дивен с пер1зым входом четвертого элемента И-НЕ, второй вход которого соединен с выходом третьего элемента И-НЕ, второй вход которого соединен с инфорЯЛа- ционным входом четвертого тригг-ера и с выходом элемента ИЛИ, выход третьего триггера соединен с вторым входом де41 шифратор-а,, третий вход которого, вхоц формирователя импульсов, второй вход второгхэ элемента И-НЕ, второй вход элемента ИЛИ, выход гюрвого триггера, первый .вход и выход второго элемента И и четвертый .вход дешифратора образуют второй вход-выход блока, выход четвертого элемента И-НЕ и второй вход первого элемента И образуют первый входвыход б.пока, инфорщационный вход первог-о сдвигающего регистра и вторэй вход первогю элемента И-НЕ соединешэ с вторым входом блока, третий выход второго сдвигаклде го регистра соединен с первым выходом блока, зыход форугироватепя импульсов, выходы дешифратора, информационный вход второго сдвигающего регистра и инверсный вход второго элемента И образуют третий вхоц-выхоа блока выход первого элемента соединен с нулевым установочным входом третьего триггера. Бпок прерываний содержит три трш гера, два элемента ИЛИ, три элемента И, два элемента И-НЕ и элемент НЕ, причем вход установки в единичное состояние перво1Х) триггера соединен с вторым входом блока, информационный вход « с нулевого потенциапа, синхронизир ло-Щий вход - с первым входом блока и с вяоаом установки в нулевое состояние второго триггера, прямой выхоа - с прр вым входом первого эпемента ИЛИ, а. инверсный выход - с первым входом перч вого эпемента И, второй вход которого соединен с вторым входом первого впе- мента ИЛИ и с третьим входом бпока, ВЫХ9Д первого эпемента ИЛИ соединен с первыми входами второго элемента И ,и первого эпемента И-НЕ и с вхоДом установки в нулевое состояние третьего триггера, информаииондай вход которого соединен с выходом второго , инверснь1й выход - с первым входом второго эпемента И-НЕ, а прямой выход - с первым входом третьего эпемента И и с информационным входом вто рого триггера, синхронвзв5 У«яций вход которого соединен с выходом первого эпемекта И-НЕ, прямой выход - с вторы ми входами третьего эпемевта И и вторрго эпемента И-НЕ, а инверсный выход «5 BivpbiM входом первого эпемевта ИНЕ, третий вход которого сбеаинен с выходом второго эпемента ИЛИ, выход третьего эпемента И соединен через эяемент НЕ с первым входом второго эпемента ИЛИ, выходы первого и третьего элементов И образуют выход бпока, вто рой вход второго эпемента ИЛИ, выход элемента НЕ, второй вход и выход второго эпемента И и сннхронизируюптй вход третьего триггера образуют вх:оавыход бпока. Бпок захвата магистрали содержит триггер, два коммутатора и . два элемеата И, причем синхронизирующий вход триггера соединен с первым входом блок вя:од установки в едтавяшё состоянве .с четвертым ; чходом блока, пвонный вход - с ШИВОЙ нулевого потевцшла, а выход - с 1юрБЫм входом пе{ вого эпемента И, второй вход которого соединен с вторым входом блока, а вы ход - с входом первого коммутатора и с первым Входом второго элемента И, второй вход которого соединен с выхопом второго коммутатора, выход второго эпемента И соединен с вторым &ыхоп№ м блока, входы второго коммутатора динены с третьим вкойом блока, а выходы первого коммутатора соединены .с первым выходом блока. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - 6 - фушшионавьг ные схемы бпока управления, блока арерываний, бпока захвата магистрали, бу ферного регистра данных и регистра оав ных соответственно, Устройство (фиг. 1) содержит первый блок 1 дешифрации адреса, блок 2 прерьь ваний, регистр 3 прерываний, буферный регистр 4 данных, регистр 5 данных, регистр 6 адреса, регистр 7 команд, рв.гистр 8 состояний, блок 9 управления, элемент ИЛИ 1О, второй блок 11 дешифрации адреса, бпок 12 захвата магистрали, первый информационный вход-выход 13, адресный эход 14, первый управлякущий вход-выход 15, второй инфо{л ацио(ный вход-выход 16, адресный вход-выход 17, второй упрввпяющий вход-выход 18, вход 19 запроса прерываний, выход 2О запроса доступа к магистрали, йход 21 разрешения доступа к магистрапн, шины 22-25 внутренних связей устройства. Блок 9 управпенйя {фиг. 2). содержит генератор 26 тактовых импульсов, сдвигают го регистры 27 и 28, второй, четвертый, третий и первый триггеры 2932, второй, третий,четвертый и первый элетленты И-НЕ 33-36, элементы И 37 к 38, элемент ИЛИ 39, формнроватепь 40 импульсов и дешифратор 41. Блок 2 прерываний (фиг. 3) содержит первый, третий к второй триггеры 4244j элементы ИЛИ 45 и 46, второй, первый в третий элементы И 47-49, элементы H-4iE 50 и 51 и элемент НЕ 52. Бпок зах&ата магвстрапи (фвг.4) : содержит триггер 53, элементы И 54 и 55 и коммутаторы 56 в 57. Буферный регистр (буфер) 4 (фиг.5) содержит элементы И 58 и 59, первую 60 н вторую 61 грушы трехстабильных впементов И.. Регистр 5 дашалх (фиг. 6) регистры 62 в 63, первую 64 в вторую 65 группы трехстабвпьных эпёментов И, эг ленты И 66-68 в элемент ИЛИ б. Устройство работает следующим образе. Прооессор ОШ выставляет на вход 14 адрес , в котором А18-АЗ определяют базовый адрес устройства, А2 обращенве к внутренним регистрам устройства впв обмен дан1а 1ми, А1-АО код внутреннего регистра, на вход-выход .13 - .«гные при выводе информации, а Еа1;;:4вхо1 -выход 15 - сигнал У1, определякпций 1ФВ логической единице Ввод, а при нуле Вывод, сопровождая указанные сигналы сигналом СХЗ (синхрон1{зацш задатчшса) по входу-выходу 15. Блок 1 по сигналам А18-АЗ формирует сигнал Выборка 1, определяющий 71 обращение к устройству. Кроме того, бпо 1 по совокупности сигнапов СХЗ, У1, А2, А1 и АО вырабатывает сигнапы управнения регистрами 5-8 и буфером 4 данных, обеспечивая занесение данных с входа-выхода 13 в указанные регистры ипи выдачу их содержимого на него, а также обеспечивает обмен данными межд входами-выходами 13 и 16. В спучае обращения процессора ОШ к регистрам выполнение операции ввода-вывода определяется временем их срабатывания и поэтому выработка сигнала СХИ (синхронизации исполнитепя), являющегося известите ль ным сигналом о том, что уст ройство произвело действия по- операции ввода-вывода, блоком 9 осуществляется по сигналу СХЗ с задержкой на время, определяемое срабатыванием регистров. Работа блока 9 происходит следующим 66pa3oMi Сигнал СХЗ с входа-вы юда 15 и сиг нал Выборка 1 с блока 1 по шине 23 поступают на входы элемента И 37, выходным сигналом которого триггер 32 устанавливается е..состояние, соответств ющее значению сигнала У1, а триггер 29 - в единичное. Затем на выходе элемента И-НЕ 34 появляется логический нуль, так как на входах этого элемента присутствуютединичные сигналы с выход триггера 29 и с выхода элемента ИЛИ 39, на входе которого присутствует сигнал А2 или сигнал Режим. Логический нуль с выхода элемента И-НЕ 34 поступает на элемент И-НЕ 35, который формирует на своем выходе логическую единицу, являющуюся сигналом СХИ. На этом цикл обращения процессора ОШ к устройству завершается. Обмен данными между процессором ОШ и интерфейсом Магистраль осущест ляется Б двух режимах. В первом режиме обмен данными про ИСХОДИТ путем установления логической связи проце,ссора ОШ с интерфейсом .Ма гистраль через буфер 4, Во втором режиме процессор ОШ обме данными осуществляет на уровне регистр 5j а пересылка данных устройство И интерфейсом Магистраль происходит без участия процессора ОШ. Дпя управление работой устройства по обмену данными пропессхэр ОШ засьтает в регистр 6 адрес устройства интерфейса Магистраль, к.которому будет провзво питься обращение, а в регистр 7 команду ухфавпения, определяющую с какт устро 26 .Р ством будет производиться обмен (устройством ВБода-вывода ипи запоми 1аюи1им устройством), в каком режиме (первом ипи втором) будет работать устройство, захват интер4 ейса Магистраль на постоянно (запрос) или на время передачи одногослова и др. Для выполнения обмена по интерфейсу Магистраль выполняется следующая последовательность действий: захват магистрали, т.е. посылка на выход 2О сиг нала запроса доступа к магистрали (ЗДМ) и получение по входу 21 сигнала разре- шения доступа к магистрали (РДЛ), выдача на вхоц-выход 17 адреса: устройства, выдача на вход-выход 18 соответствующего сигнала управления (рапись, чтение, выдача, прием) и ожидание выполнения обмена -с адресуемым устройством, т.е, получение по входу-выходу 18 сигнала Ответ. Если в команде определен первый режим обмена - то процессор ОШ не отключается от устройства до окончания прог- цесса обмена по интерфейсу Магистраль. Сигнал СХИ в этом случае формируется после получения сигнала Ответ. В первом режиме по сигналу Режим, поступающему из регистра 7 по шине 22, разрешается работа буфера 4 и запрещается работа регистру 5, а блок 9 переводится в соответствующий режим функционирования. Для осуществления обмена процессор ОШ выставляет на вход 14 адрес устройства с признаком обмена по интерфейсу Магистраль, сопровождая его по входу-выходу 15 сигналом СХЗ и выставляет на вход-выход 15 сигнал У1. В случае вывода с инте)фейса ОШ данные выдаются на входг-выход 13. При поступлении сигнала СХЗ блок 1 вырабатывает сигнал Обмен и сигнал В1, определяющий юправление обмена, знгачевие которого при выводе данных равно логи-, ческой единице, а при вводе - логическому нулю. Обмен по шине 23 поступает на вход блока 12 и устанавливает триггер 53 в нулевое состояние. Логический нуль с выхода триггера 53 поступает на элемент И 54 и с eix) выхо-. да через ко:шу1утатор 56 поступает на выход 20, как сигнал ЗДМ. Сигнал РДМ, представленный логической единицей на входе 21, через коммутатор 57 поступает на прямой вход элемента И 55, на инвррсшм входе которого приходит нулевой ситна л с выхода элемента И 54, В результате на выходе элемента И 55 будет погическая еаиница, явпяющаяся , извесгитепьным сигнапом Захват магистрапи. Сигнап Захват через второй выход бпока 12 по шине 24 поступает на входы буфера 4, регистра 6 иблока 9. По этому сигналу регистр 6 выдает адрес на вход-выход 17, буфер 4 пропускает дан ные с входа-выхода 13 на вход-выход 16 при наличии на втором его входе сиг нала В1, равного логической единице, и наоборот - при наличии на этом входе сигнала В1, равного логическому нулю, так как комбинация входных сигналов (режим, захват и В1) на входах элеменгов И 58 и 59 обеспечивает открывание групп 6О или 61 трехстабильных элементов.. В блоке 9 сигнал Захват через информационный вход регистра 27 тактовым импульсом генератора 26 продвигается к его выходам, затем с первого из них поступает наинформационный вход сдвига ющего регистра 28, а с второго - на синхронизирующий вход триггера 31 и переводит его в нулевое состояние. Сиг нал с выхода триггера 31 -поступает на первый вход дешифратора 41. В этх. время на остальных его входах присутствуют сигналы ЗУ/УВВ, выборка 1 и У1. Дешифратор 41 по комбинации входных снг налов выраЬатывает сигналы Запись либо Чтение, если обмен происходит с ЗУ или сигналы Прием пибо Выдаче если происходит с устройством ввода-вывода, и выдает их на вход-выход 18. Устройство, с которым осуществляется обмен, выполнив операцию обмена, вырабатывает управляющий сигнал Ответ представленный логическим нулем, кото, рый с входа-выхода 18 постухюет иа инверсный вход элемента И 38. В случае осуществления ввода информации триггер 32 установлен в единичное состояние и поэтому логическая едиквиа с его выхода поступает на прямой вход элемента И 38 На выходе элемента И 38 в этом случае будет сформирован сигнал Занесение, который по шине 22 поступает на регист 5 для приема данных с входа-выхода 16. Кроме того, сигнал Ответ поступает на информационный вход сдвигающего регистра 28 и под действием импульсов с тактового генератора 26 появляется на , первом, втором и третьем его выходах с запаздыванием на один, два и три.такта соответственно. Сигнал с первого выхода регистра 28 устанавливает триггер 31 в единичное состояние, а триггер 30 в нулевое. При этом логическая едикиЦБ с выхода триггера 31 блокирует работу дешифратора 41, а логический нуль с выхода триггера 30 приводит к появлению на выходе элемента И-НЕ 35 погической единиш 1, которая поступает на вход-выход 15 и является сигналом СХН, свидетельствующим о том, что обмен с адресуемым устройством завершен. По этому сигналу процессор снимает данные с входа-выхода 13, адрес - с входа 14 и управляющие сигналы - с входа-выхода 15. Снятие сигнала СХЗ приводит к .тому, что триггер 29 устанавливается в нулевое состояние, а триггер ЗО - в единичное. При этом на выходе элемента И-НЕ 35 появляется логический нуль, что соответствует снятию управляющего сигнала СХИ. Сигнал - логическая единица с второго выхода регистра 28 поступает на вход элемента И-НЕ 33. На другой вход этого элемента с регистра 7 по шине 22 поступает сигнал Инкремент, которыК при обмене массивами информации представлен логической единицей, а при обмене словом - логическим нулем. При наличии логической единицы на другом входе элемента И-НЕ 33 на его выходе формируется сигнал Инкремент адреса, который с выхода блока 9 по цепи 25 поступает на вход регистра 6 адреса и увеличивает его содержимое на единицу. При наличии логического нуля на другом входе элемента И-НЕ 33 на его выходе формироватш указанного сигнала не произойдет и содержимое регистра 6 адреса не изменится. Сигнал с третьего выхода регистра 28 через первый выход блока 9 поступает на блок 12 и является исполнительной командой Сброс захвата магистрали. По нему триггер 53 устанавливается в единичное состояние, а на выходе элемента И 54 появляется логическая единица, в результате чего на выходе элегмента И 55 появляется логический нуль, по которому снимаются сигналы Захват и ЗДМ. После этого буфер 4 и регистр 6 отключаются от интерфейса Магистраль и сигнал Разрешение доступа к магист) снимается. Наэтом процедура обмена словом в первом режиме завершается. В случае массивом из регисгра 7 по шине 22 на вход блока 12 может быть передана команда Запрос постоянный - логический нуль, которая 11,1 через впембнт И 54 и коммутатор 56 овеся1ечивеет прстояншлй захват интерфейса Магистрапь. На втором выкоае бпока 12 в эт()М случае постоянно присутствует сигнап Захват и поэтому пуск бпока 9 на обмен с интерфейсом Магистраль производится, сигналом Обмен через его Bxqa и элемент И 36 путем установки триггера 31 в нулевое срстояйие по установочному входу. Во втором режиме обмена устройство функционирует аналогичным образом за исключением того, что сигнал Режим, поступающий с регистра 7 по щине 22, разрешает работу регистра 5 и разрешае формирование вблоке 9 сигнала СХИ по сигналу СХЗ, что позволяет процессору ОШ осуществл:ять обмен на уровне регистров устройства.. Регистр 5 и этом режиме работает таким образом.. Сигнап Режим поступает на первые в|соды эпементов И 66 - 68, разрешая увравпение группами 64 и 65 трехстабнпьных элементов и формирование сигнала Готов на первом входе-выходе. При этом при тапичии В1 на втором вхо эпемента И 66 группа 65 разрешает выдачу содержимого регистра 63 на вхо выход 13, а щж наличии Захват и сигнала У2 поступающих m вго и третий входы элемента И 67, разрнвшается выдача соцержимотх регистра 62 черечЧ группу 64 и формирование сда-капа Готовность на входе-выходе 1 По сигналу Занесение с бпока 9, пост пающему по шине 22, осуществляется за аесение анфоралаиии с входа-выхода в регистр 63 и происходит формирование anoiieHTaMH И 68и ИЛИ 69 сигнала Готов, который задним фронтом устана лйвает в единичное:состояние один из битов регистра 8 состояния. Синхрониза ция обмена осуществпяется путем ашпи а (Х)ром ОЩ состояния регистра &f цйя чего перед каждым циклом обмен осуществпяется его чтение. При запросе связи со стороны ншкдаг яруса ипи локальной яоасЕСге5-гы запрос осушвствпяется активкь м эпементоме В 8ТОМ случае активный эпемерт произзо. аит обращение по входу-выходу 17 устройства. Сигнал адреса с вкода-выхода 17 поступает на вход блока 11., где он декодируется и при наличии на другом его входе управляющего СЕг-нака Выдач Яоступакяцёго с входа-выхода 18, блок 11 формирует вектор прерывания и скгнап Выборка И. Вектор прерьшаг® с 26 первого выхода бпока 11 поступает на второй вход 5эегистра 3 и фшссируется в нем. CvcTHan Выборка И с второго выкоца блока 11 по шине 26 поступает ка второй вход блока 2 прерываний и с нэгчэ на eaHiiK4Hfcift установочный вход триггера 42. На выходе триггера 42 появляется погическая единица, являющаяся сигналом Запрос прерывания , который через элемент ИЛИ 45 и элемент И 47, при нупе на его инверсном входе, поступает на вход-выход 15. В ответ на это процессор ОШ выдает на вхоовыхой 15 сигнап Разрешение прерыва ния - логическую единицу, которая поступает ма инверсный вход элемента И 47s после чего логическая .единица на его сменяется нупем, что соответствует снятию сигнала Запрос прерывания. Одновременно с этим сигнал Разрешение прерывания поступает на синхронизирующий вход триггера 43, а поскольку, на его информационном входе уже присутствует логическая единица с выхода элемента И-НЕ 51, то он перегодится в единичдае состояние, и сигнал с его выхода поступает на информационный вход триггера 44 и на вход элемента И 49.; В моменг, когда управляющие: сигналы СХИ и Занято на ВХОНЕХ элеменга ИЛИ 46 соответствуют логическим нулям, погическая едкнипа с выхоша aneMeH та И 50 поступает на c 5:нxpoнлэ фyющий вход триггера 44 и онпереходит в единичное состояние. Единица с вьш5да триг гера 44, явгшюЩаяся сигналом ПВБ (подтверждекие выборки) через вход-выход блока 2 поступает на вход-выход 15 и на один из входов эпемента И 49, на втором входе которого уже присутствует единиш с выхода триггера 43. На вьтходе элемента И 49 появляется логическая единица, являющаяся сигналом Вектор прере1ваЕИя 1. Этот сигнал поступает иа выход блока 2, в результате чего содержимое регистра 3 проходит m вход-выход 13, вызывая прерывающую программу. Одновременно с управляющим сигналом Вектор прерывания 1 блок 2 посредством эпемента НЕ 52 .формирует сигнал Занято, который поступает на вход-в ход 15 и сввдетепьствует о том, что (устройство заняло интерфейс ОШ, В программе обработки прерьюани про-, цессор записывает в регистр 7 команду Сброс пр«эрывания. В этом случае сиг нал Сброс с выхода регистра 7 по щиь ие 22 через первый вход бпока 2 поступает на синхронизирующий вход триггера 42 и нупевой установочный вход триггера 44, устанавливая блок 2 в исходное состояние. В интерфейсе Магистрапь дпя осуществления запросов связи (ЗПР) имеетс радиальная магистраль, В случае запроса связи на обмен от пассивных элементов с координатором соответствующан радиаль вызывает прерывание процессора рШ. При этом активный элемент интерфейса Магистраль на данный запрос не реагирует Сигнал ЗПР .некоторого прерывания с входа 19 поступает на третий вход / гистра 8 состояний н через элемент ИЛИ 1О на третий вход блока 2. В бпоке 2 сигнал ЗПР через соответствующий вход элемента ИЛИ 45 запускает формирование и обработку прерывания аналогично прерыванию от активного устройства. Сигнал ЗПР поступает на соответствующий вход элемента И 48j на выходе которого в случае, еспи пре{а 1вание активных устройств обработано, формируется сигнал .Вектор пре1%шания П, по- ступающий на первый вход регистра 3, формируя в этом регистре соответствующий вектор прерывания, по которому выцает-ся соответствующа$ ему программа обработки прерывания. В этой программе процессор опрашивает регистр 8. определяет по какому уровню возникло прерывание и обрабатывает его по соответствующему алгоритму. Сброс нижнего уровня в исходное состояние происходит по команде процессера ОШ, в результате которой с регистра 7 по шине 22 на блок 9 постутйет Сброс, где он формирователем 4О преобразуется в импульс Устаноб, который по входу-выходу 18 и приводит нижний уровень в исходное состояние. Таким образом, предлагаемое устройство по сравнению с известным позволяет осуществлять обмен в иерархической структуре между нижним ярусом, локальной подсистемой нижнего яруса, функциональным элементом нижнего яруса и координатором. Кроме того, за счет установцения логической связи с функциошпьным элементхэм нижнего яруса, устройство обеспечивает высокую эффективность процедуры обмена массивами информации. ,fg Сброс захвата I С9лвка «

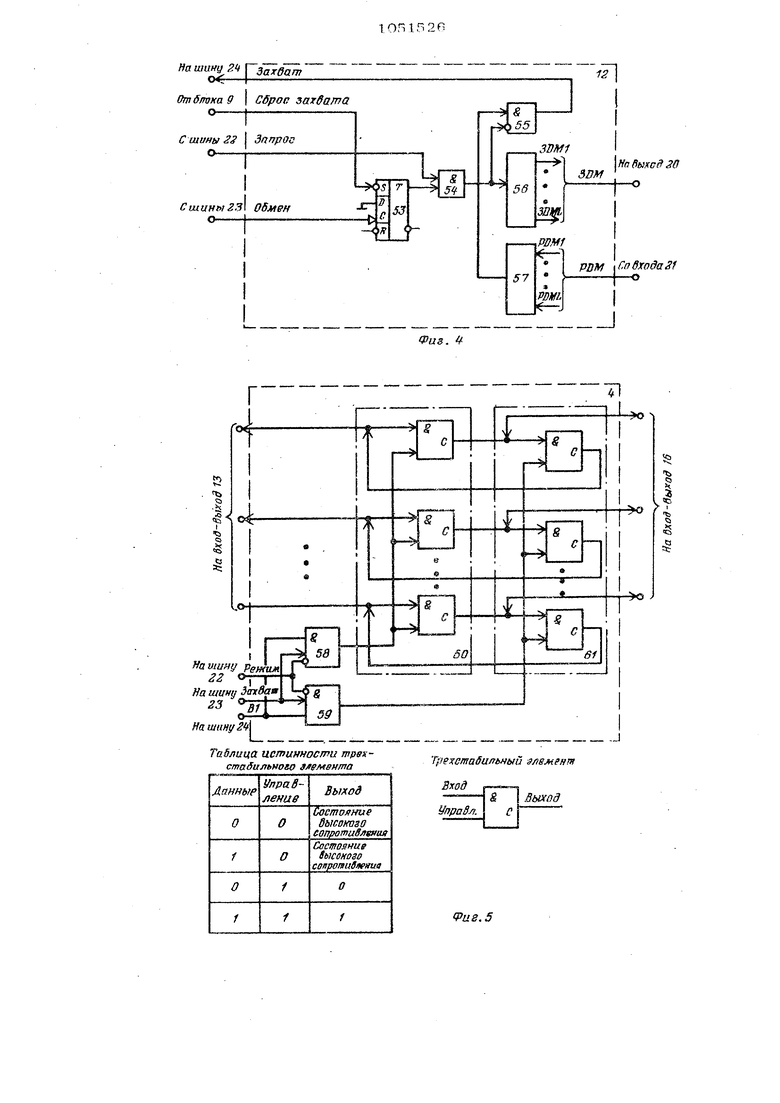

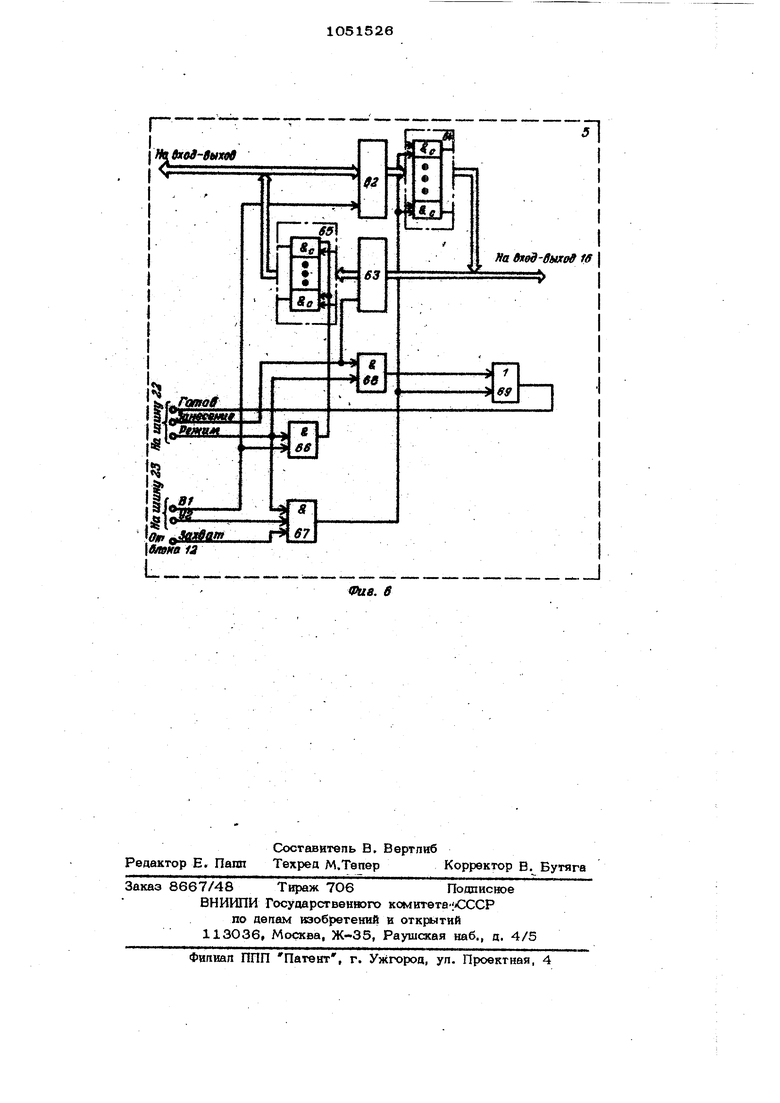

Фие. 3 На шику 22 На бмя 8 На шину 22 I

Машину 2ir-3a;rffaf7

O4ih-

Таблица истинности траастабильноео злемвнта

F1

NapKKccf20

POM Co8xoda31

З

fuB. 4

Tl

Трежс/паби/гмый мвмент Вход

Выход

УпраЗл

Pus. 5

Фив, в

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Моторная установка для автомобилей | 1925 |

|

SU7818A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сопряжения | 1977 |

|

SU648974A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-10-30—Публикация

1982-07-02—Подача