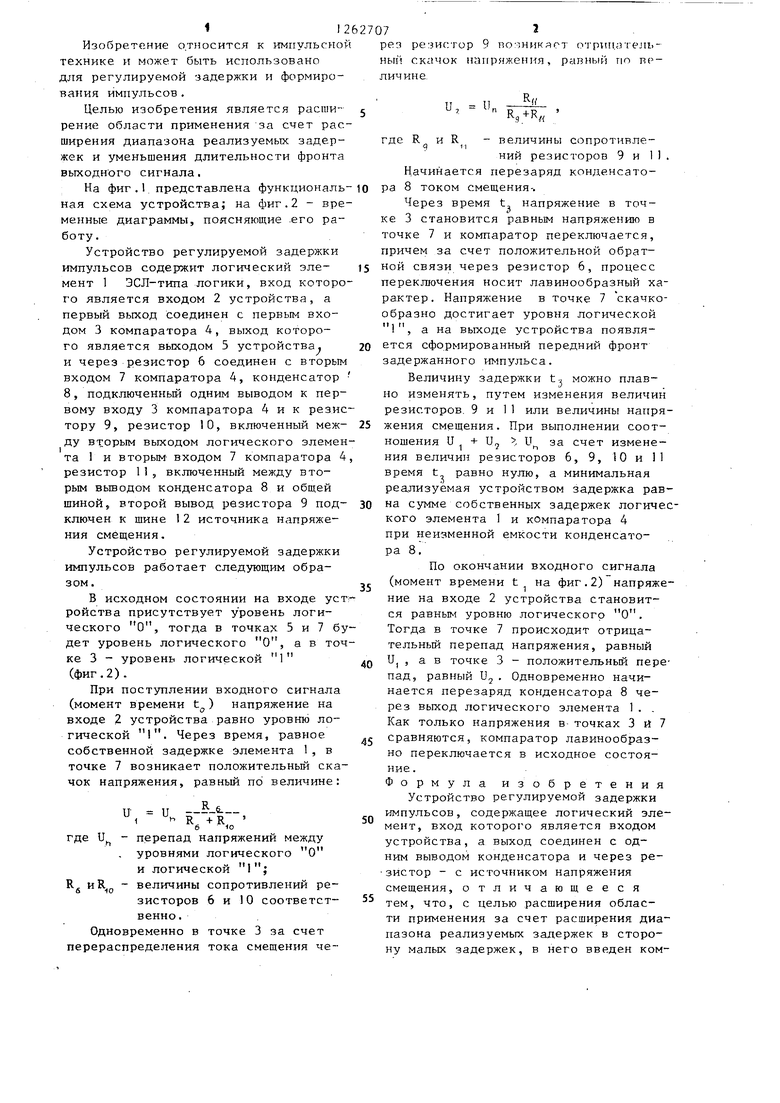

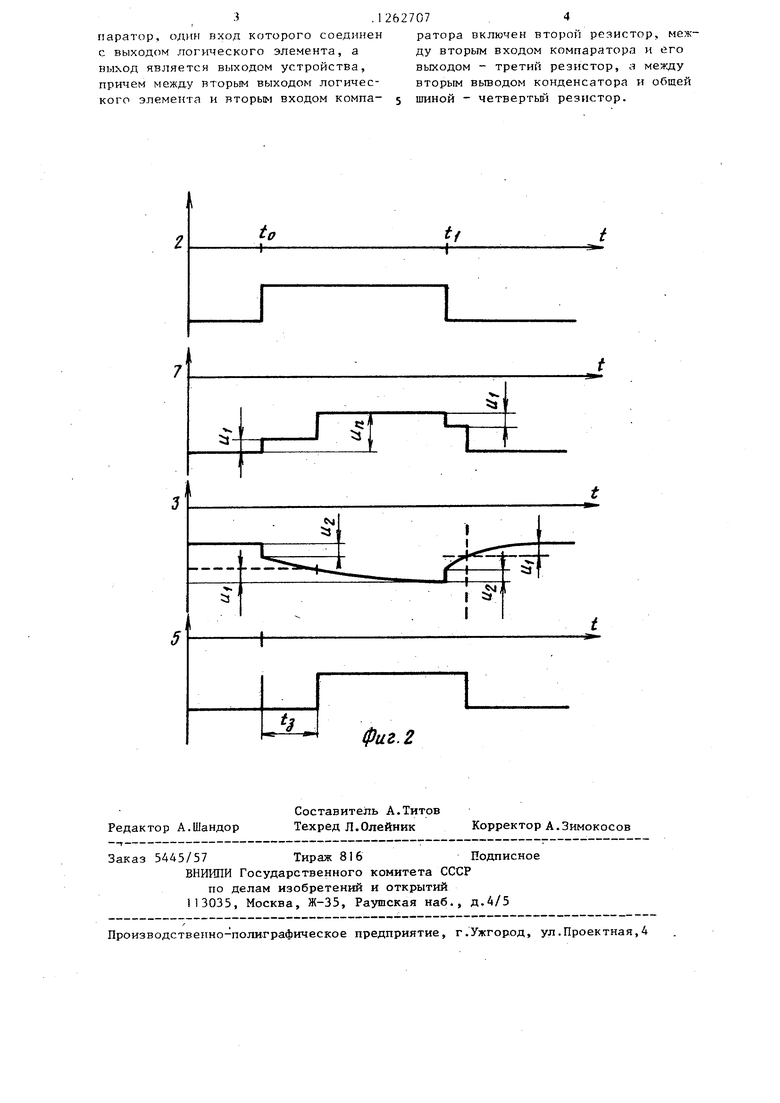

технике и может быть использовано для регулируемой задержки и формирования импульсов. Целью изобретения является расширение области применения за счет рас ширения диапазона реализуемых задержек и уменьшения длительности фронта выходного сигнала. На фиг . 1 представлена функциональная схема устройства; на фиг.2 - вр менные диаграммы, поясняющие .его ра боту. Устройство регулируемой задержки импульсов содержит логический элемент 1 ЭСЛ-типа логики, вход котор го является входом 2 устройства, а первый выход соединен с первым входом 3 компаратора 4, выход которого является выходом 5 устройства. и через резистор 6 соединен с вторы входом 7 компаратора 4, конденсатор 8, подключенный одним выводом к пер вому входу 3 компаратора 4 и к рези тору 9, резистор 0, включенный меж ду вторым выходом логического элеме та и вторым входом 7 компаратора резистор 115 включенный между вторым вьшодом конденсатора 8 и общей шиной5 второй вывод резистора 9 под ключен к шине 12 источника напряжения смещения. Устройство регулируемой задержки импульсов работает следующим образом. В исходном состоянии на входе yc ройства присутствует Уровень логического О, тогда в точках 5 и 7 б дет уровень логического О, а в то ке 3 - уровень логической 1 (фиг.2). При поступлении входного сигнала (момент времени t) напряжение на входе 2 устройства равно уровню логической I. Через время, равное собственной задержке элемента 1, в точке 7 возникает положительный ска чок напряжения, равный по величине: и- и где и - перепад напряжений между уровнями логического О и логической Rg иК, - величины сопротивлений резисторов 6 и 10 соответственно. Одновременно в точке 3 за счет перераспределения тока смещения черавный по прНЫ11 скачок напряжения, личине. где R - величины сопротивлений резисторов 9 и 1). Начинается перезаряд конденсатора 8 током смещения-. Через время t напряжение в точе 3 становится равным напряжению в очке 7 и компаратор переключается, ричем за счет положительной обратой связи через резистор 6, процесс ереключения носит лавинообразный хаактер. Напряжение в точке 7 скачкобразно достигает уровня логической 1 , а на выходе устройства появляется сформированный передний фронт задержанного импульса. Величину задержки t можно плавно изменять, путем изменения величин резисторов. 9 и П или величины напряжения смещения. При выполнении соотношения и + U,j , и счет изменения величин резисторов 6, 9, 10 и 1 время t равно нулю, а минимальная реализуемая устройством задержка равна сумме собственных задержек логического элемента 1 и компаратора 4 при неизменной емкости конденсатора 8 Г По окончании входного сигнала (момент времени t на фиг.2) напряжение на входе 2 устройства становится равным уровню логического О. Тогда в точке 7 происходит отрицательньш перепад напряжения, равный Uj , а в точке 3 - положительный перепад, равный Uj. Одновременно начинается перезаряд конденсато.ра 8 через выход логического элемента 1. Как только напряжения в- точках 3 и 7 сравняются, компаратор лавинообразно переключается в исходное состояние. Формула изобретения Устройство регулируемой задержки импульсов, содержащее логический элемент, вход которого является входом устройства, а выход соединен с одним выводом конденсатора и через резистор - с источником напряжения смещения, отличающееся тем, что, с целью .расщирения области применения за счет расширения диапазона реализуемых задержек в сторону малых задержек, в него введен компаратор, один вход которого соединен с выходом логического элемента, а выход является выходом устройства, причем между вторым выходом логического элемента и вторым входом компаратора включен второй резистор, между вторым входом компаратора и его выходом - третий резистор, а между вторым вьтодом конденсатора и общей шиной - четвертый резистор.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задержки импульсов | 1984 |

|

SU1295511A1 |

| Устройство для измерения коэффициента нелинейности пилообразного напряжения | 1981 |

|

SU978077A1 |

| Генератор импульсов | 1991 |

|

SU1835597A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Преобразователь тока в частоту | 1986 |

|

SU1392617A1 |

| Устройство для задержки импульсов | 1985 |

|

SU1529424A1 |

| Формирователь задержки импульсов | 1984 |

|

SU1236599A1 |

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| Устройство для задержки импульсов | 1981 |

|

SU1046924A1 |

| ЦИФРОВОЙ ЭЛЕКТРОПРИВОД ПОСТОЯННОГО ТОКА С ДВОЙНОЙ ШИРОТНО-ИМПУЛЬСНОЙ МОДУЛЯЦИЕЙ | 1992 |

|

RU2037263C1 |

Изобретение может быть использовано для формирования и регулируемой задержки импульсов. Цель изобретения - расширение области применения. Достигается она путем расширения диапазона регулируемых задержек в сторону малых задержек и уменьшения длительности фронта выходного сигнала. Для этого в устройство дополнительно введен компаратор 4. Устройство также содержит логический элемент I ЭСЛ-типа логики, вход которого является входом 2 устройства, первый вход 3 компаратора 4, выход которого является выходом 5 устройства, резисторы 9, 10 и П, второй вход 7 компаратора 4, конденсатор 8, тину I2 источника напряжения смещения. Величина регулируемой задержки может плавно изменяться путем изменения величин резисторов 9 и I1 или величины напряжения смещения. 2 ил. 1.

to

tf

| Устройство для задержки импульсов | 1981 |

|

SU1046924A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Мелешко Е.А | |||

| Интегральные схемы в наносекундной ядерной электронике. | |||

| М;: Атомиздат, 1977, с | |||

| Способ приготовления сернистого красителя защитного цвета | 1915 |

|

SU63A1 |

Авторы

Даты

1986-10-07—Публикация

1984-12-25—Подача