ND

05

сл

со 00

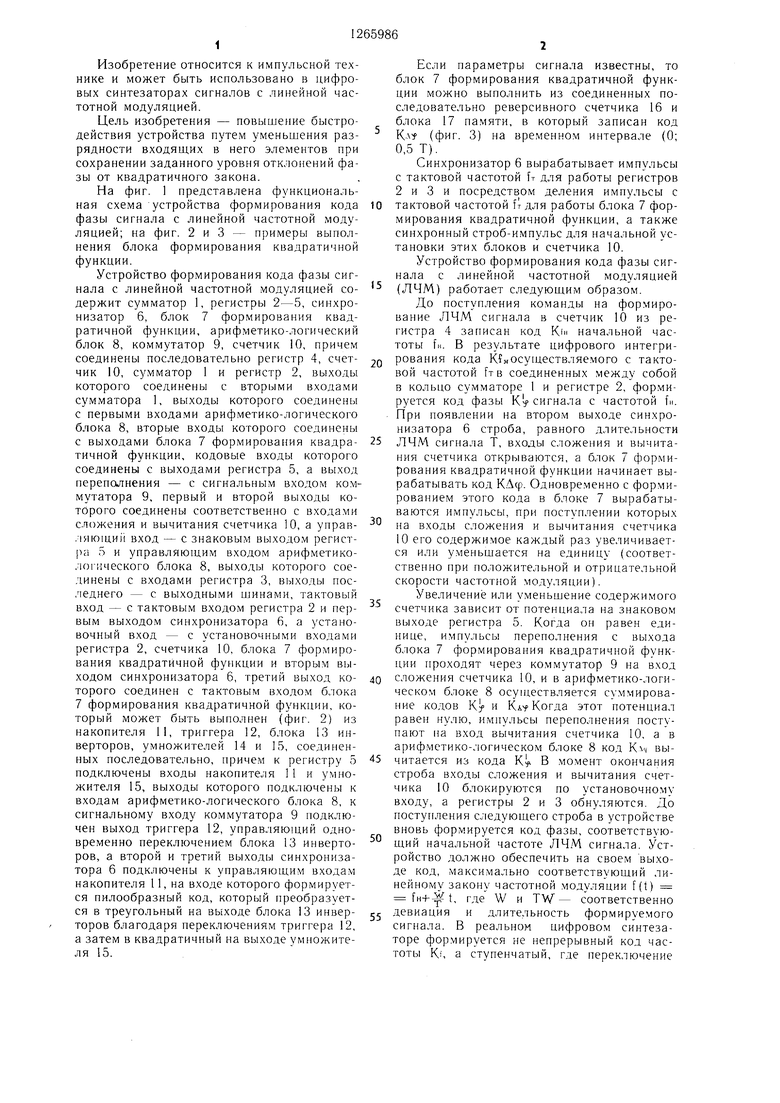

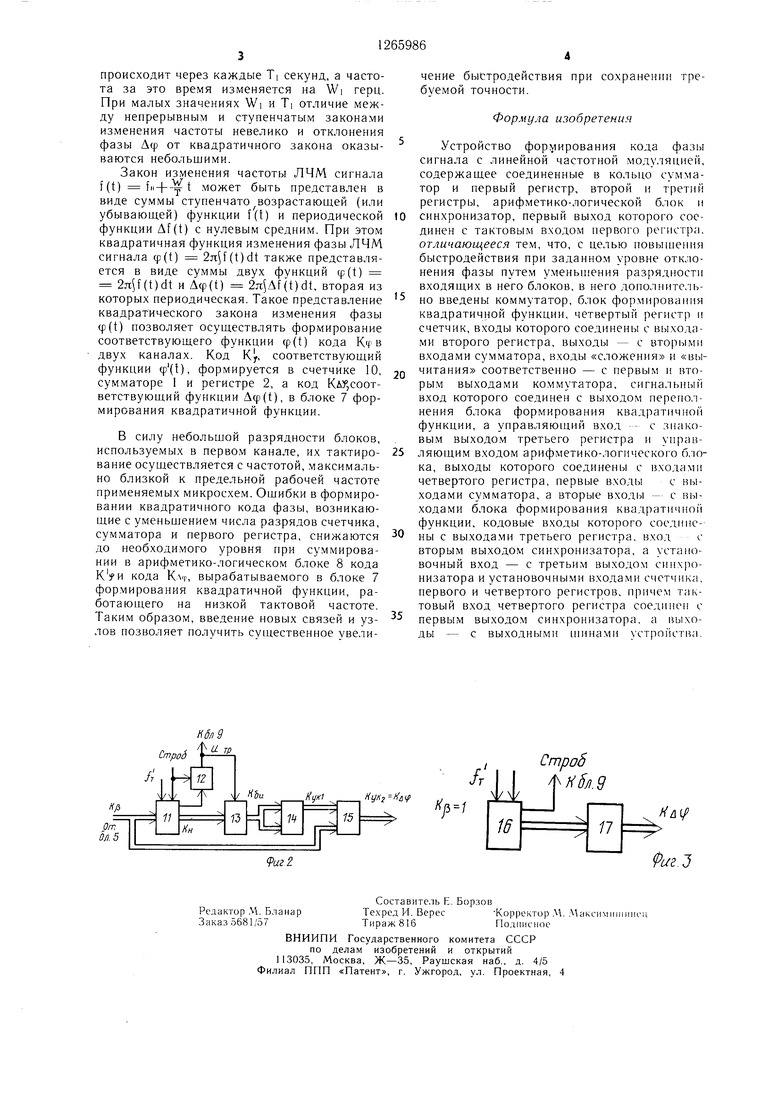

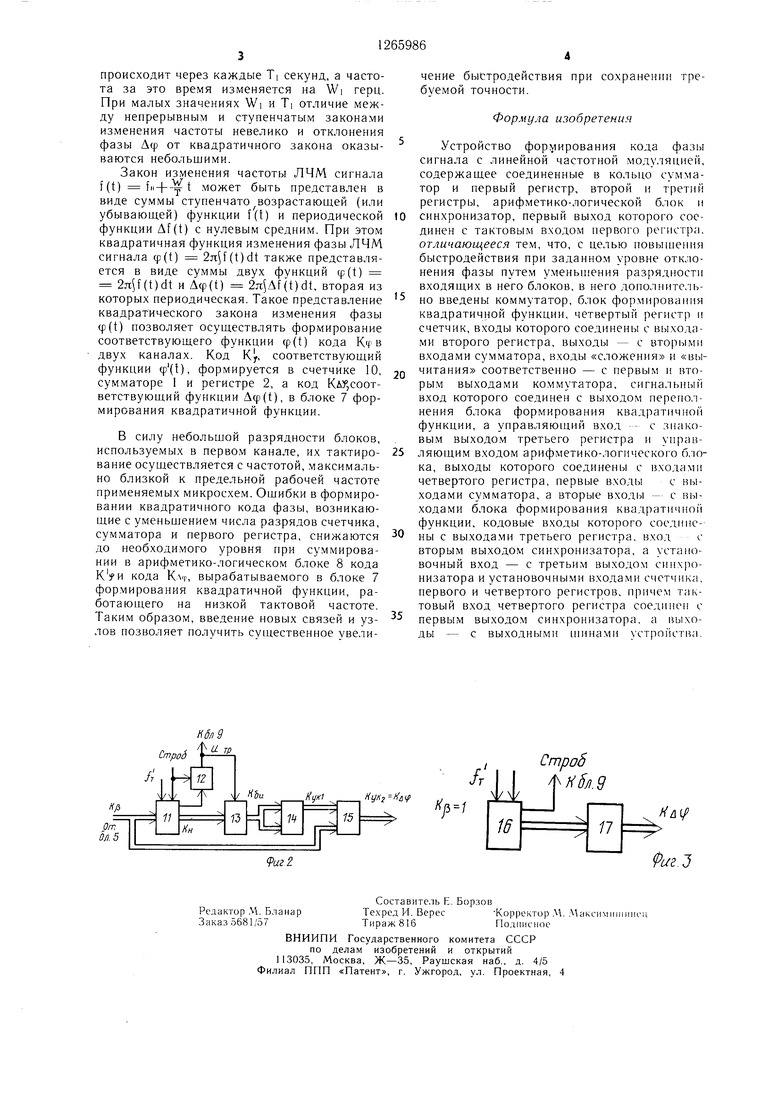

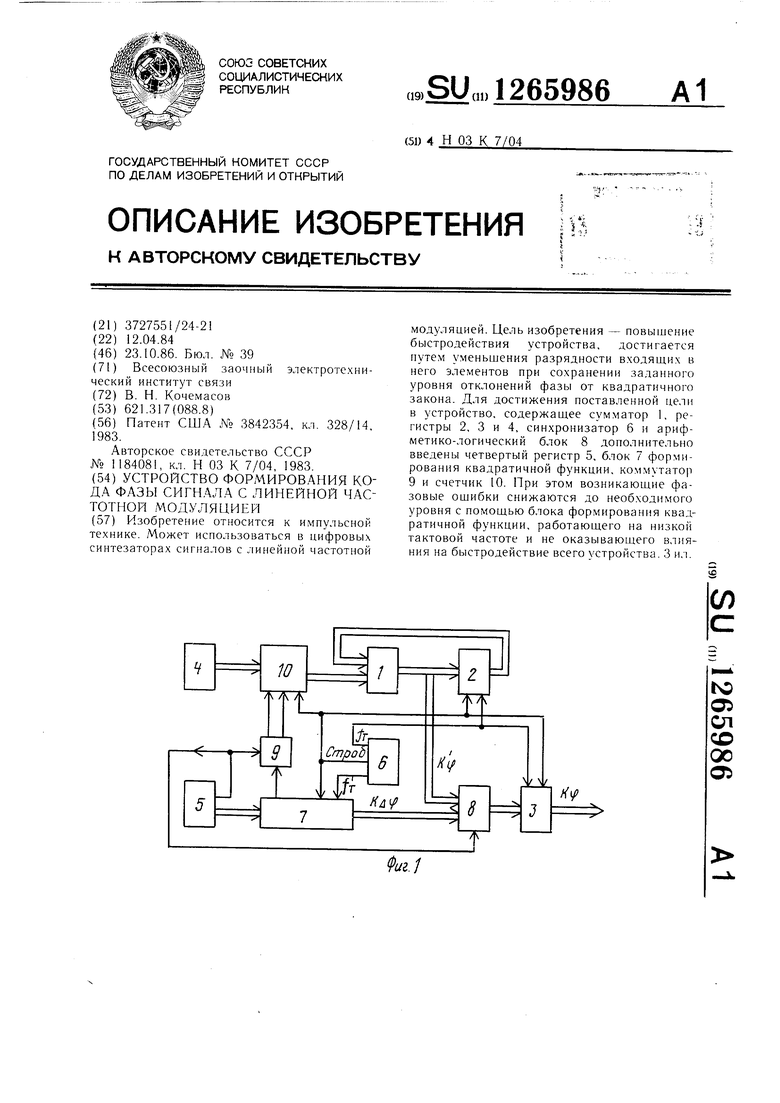

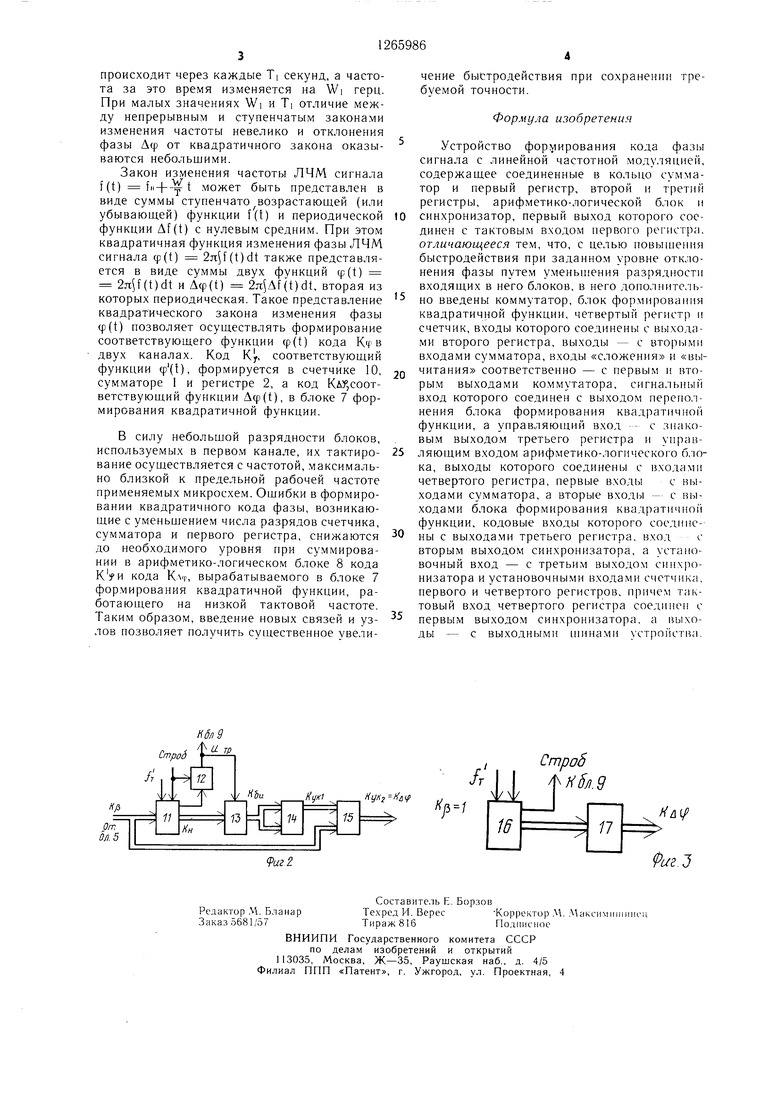

05 Изобретение относится к импульсной технике и может быть использовано в цифровых синтезаторах сигналов с линейной частотной модуляцией. Цель изобретения - повышение быстродействия устройства путем уменьшения разрядности входящих в него элементов при сохранении заданного уровня отклонений фазы от квадратичного закона. На фиг. 1 представлена функциональТ I 1 , ная схема устройства формирования кода фазы сигнала с линейной частотной модуляцией; на фиг. 2 и 3 - примеры выполнения блока формирования квадратичной функции. Устройство формирования кода фазы сигнала с линейной частотной модуляцией содержит сумматор 1, регистры 2-5, синхронизатор 6, блок 7 формирования квадратичной функции, арифметико-логический блок 8, коммутатор 9, счетчик 10, причем соединены последовательно регистр 4, счетчик 10, сумматор 1 и регистр 2, выходы которого соединены с вторыми входами сумматора 1, выходы которого соединены с первыми входа.ми арифметико-логического блока 8, вторые входы которого соединены с выходами блока 7 формирования квадратичной функции, кодовые входы которого соединены с выходами регистра 5, а выход переполнения - с сигнальным входом коммутатора 9, первый и второй выходы которого соединены соответственно с входами сложения и вычитания счетчика 10, а управ.|ЯЮ1ци)1 вход - с знаковым выходом регист ia 5 и управляющим входом арифметико.югического блока 8, которого соединены с входами регистра 3, выходы последнего - с выходными шинами, тактовый вход - с тактовым входом регистра 2 и первым выходом синхронизатора 6, а установочный вход - с установочными входами регистра 2, счетчика 10, блока 7 формирования квадратичной функции и вторым выходом синхронизатора 6, третий выход которого соединен с тактовым входом блока 7 формирования квадратичной функции, который может быть выполнен (фиг. 2) из накопителя 11, триггера 12, блока 13 инверторов, умножителей 14 и 15, соединенных последовательно, причем к регистру 5 подключены входы накопителя 1 1 и умножителя 15, выходы которого подключены к входам арифметико-логического блока 8, к сигнальному входу коммутатора 9 подключен выход триггера 12, управляющий одновременно переключением блока 13 инверторов, а второй и третий выходы синхронизатора 6 подключены к управляющим входам накопителя 11, на входе которого формируется пилообразный код, который преобразуется в треугольный на выходе блока 13 инверторов благодаря переключениям триггера 12, а затем в квадратичный на выходе умножителя 15. Если параметры сигнала известны, то блок 7 формирования квадратичной функции можно выполнить из соединенных последовательно реверсивного счетчика 16 и блока 17 памяти, в который записан код К (фиг. 3) на временном интервале (0; 0,5 Т). Синхронизатор 6 вырабатывает импульсы с тактовой частотой т для работы регистров 2 и 3 и посредством деления импульсы с я( тактовой частотой fr для работы блока 7 формирования квадратичной функции, а также синхронный строб-и.мпульс для начальной установки этих блоков и счетчика 10. Устройство формирования кода фазы сигнала с линейной частотной модуляцией (ЛЧМ) работает следующим образом. До поступления команды на формирование ЛЧМ сигнала в счетчик 10 из регистра 4 записан код Kf начальной частоты и. В результате цифрового интегрирования кода К носуществляемого с тактовой частотой fr в соединенных между собой в кольцо сумматоре 1 и регистре 2, формируется код фазы сигнала с частотой fn. При появлении на втором выходе синхронизатора 6 строба, равного длительности ЛЧЛ1 сигнала Т, входы сложения и вычитания счетчика открываются, а блок 7 формирования квадратичной функции начинает вырабатывать код КАср. Одновременно с формированием этого кода в блоке 7 вырабатываются импульсы, при поступлении которых на входы сложения и вычитания счетчика 10 его содержимое каждый раз увеличивается или у.меньшается на единицу (соответственно при положительной и отрицательной скорости частотной модуляции). Увеличение или уменьшение содержимого счетчика зависит от потенциала на знаковом выходе регистра 5. Когда он равен единице, импульсы переполнения с выхода блока 7 формирования квадратичной функции проходят через коммутатор 9 на вход сложения счетчика 10, и в арифметико-логическом блоке 8 осу1цествляется суммирование кодов Kf и Когда этот потенциал равен нулю, и.мпульсы переполнения поступают на вход вычитания счетчика 10, а в арифметико-логическом блоке 8 код вычитается из кода KV В момент окончания строба входы сложения и вычитания счетчика 10 блокируются по установочному входу, а регистры 2 и 3 обнуляются. До поступления следующего строба в устройстве вновь формируется код фазы, соответствующий начальной частоте ЛЧМ сигнала. Устройство должно обеспечить на своем выходе код, максимально соответствующий линейному закону частотной модуляции f (t) fH-f- t, где W и соответственно девиация и длительность формируемого сигнала. В реальном цифровом синтезаторе формируется не непрерывный код частоты Ki, а ступенчатый, где переключение происходит через каждые Т| секунд, а частота за это время изменяется на Wi герц. При малых значениях Wi и Ti отличие между непрерывным и ступенчатым законами изменения частоть невелико и отклонения фазы Дф от квадратичного закона оказываются небольшими. Закон изменения частоты ЛЧМ сигнала f(t) fH-|-- t может быть представлен в виде суммы ступенчато возрастающей (или убывающей) функции f(t) и периодической функции Af(t) с нулевым средним. При этом квадратичная функция изменения фазы ЛЧМ сигнала ф(1) (i)di также представляется в виде суммы двух функций ф(1) )й{ и Аф{1) (i}di, вторая из которых периодическая. Такое представление квадратического закона изменения фазы ф(1) позволяет осуществлять формирование соответствующего функции ф(1) кода Кф в двух каналах. Код К, соответствующий функции ф(1), формируется в счетчике 10, сумматоре 1 и регистре 2, а код КдУ,соответствующий функции 4ф(1), в блоке 7 формирования квадратичной функции. В силу небольшой разрядности блоков, используемых в первом канале, их тактирование осуществляется с частотой, максимально близкой к предельной рабочей частоте применяемых микросхем. Ошибки в формировании квадратичного кода фазы, возникающие с уменьшением числа разрядов счетчика, сумматора и первого регистра, снижаются до необходимого уровня при суммировании в арифметико-логическом блоке 8 кода Куи кода Клф, вырабатываемого в блоке 7 формирования квадратичной функции, работающего на низкой тактовой частоте. Таким образом, введение новых связей и узлов позволяет получить существенное увеличение быстродействия при сохранении требуемой точности. Формула изобретения Устройство формирования кода фазы сигнала с линейной частотной модуляцией, содержащее соединенные в кольцо сумматор и первый регистр, второй и третий регистры, арифметико-логической блок и синхронизатор, первый выход которого соединен с тактовым входом первого регистра. отличающееся тем, что, с целью повышения быстродействия при заданном уровне отклонения фазы путем уменьшения разрядности входящих в него блоков, в него дополнительно введены коммутатор, блок формирования квадратичной функции, четвертый регистр и счетчик, входы которого соединены с выходами второго регистра, выходы - с вторыми входами сумматора, входы «сложения и «вычитания соответственно - с первым и вторым выходами коммутатора, сигнальный вход которого соединен с выходом nepeno.iнения блока формирования квадратичной функции, а управляющий вход с знаковым выходо.м третьего регистра и управляющим входом арифметико-логического блока, выходы которого соединены с входами четвертого регистра, первые входы с выходами сумматора, а вторые входы - с выходами блока формирования квадратичной функции, кодовые входы которого соединены с выходами третьего регистра, вход с вторым выходом синхронизатора, а установочный вход - с третьим выходом синх 1онизатора и установочными входами счетчика, первого и четвертого регистров, причем тактовый вход четвертого регистра соединен с первым выходом синхронизатора, а выходы - с выходными Нинами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Индикаторное устройство | 1990 |

|

SU1779936A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1327267A1 |

| Измеритель частотных ошибок | 1984 |

|

SU1291890A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА МОДУЛИРОВАННЫХ ПО ФАЗЕ И ЧАСТОТЕ СИГНАЛОВ | 2005 |

|

RU2288539C1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385238A2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА МОДУЛИРОВАННЫХ ПО ФАЗЕ И ЧАСТОТЕ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2004 |

|

RU2262802C1 |

| Формирователь линейно-частотно-модулированных колебаний | 1982 |

|

SU1072247A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1978 |

|

SU873418A1 |

Изобретение относится к импульсной технике. Может использоваться в цифровых синтезаторах сигналов с линейной частотной модуляцией. Цель изобретения - повышение быстродействия устройства, достигается путем у.меньшения разрядности в.чодящих в него элементов при сохранении заданного уровня отклонений фазы от квадратичного закона. Для достижения поставленной цели в устройство, содержащее сумматор I, регистры 2, 3 и 4, синхронизатор 6 и арифметико-логический блок 8 дополнительно введены четвертый регистр 5, блок 7 формирования квадратичной функции, коммутатор 9 и счетчик 10. При этом возникающие фазовые ошибки снижаются до необходимого уровня с помощью блока формирования квадратичной функции, работающего на низкой тактовой частоте и не оказывающего влияния на быстродействие всего устройства. 3 ил.

НуК;

Kjb-1

| Патент США 3842354, кл | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

| Цифровой фазовый модулятор | 1983 |

|

SU1184081A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-10-23—Публикация

1984-04-12—Подача