ю

о -4j

О5

4;iii

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарное устройство | 1983 |

|

SU1119196A1 |

| Резервированное пересчетное устройство | 1982 |

|

SU1064475A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1335920A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| ТЕЛЕВИЗИОННОЕ УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ПЕРЕМЕЩЕНИЙ ОБЪЕКТОВ | 1984 |

|

RU2140721C1 |

| Реверсивный счетчик | 1983 |

|

SU1145477A1 |

| Устройство для разделения входных импульсов | 1984 |

|

SU1287282A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1984 |

|

SU1218503A1 |

| Преобразователь двоичного кода во временной интервал | 1983 |

|

SU1115223A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

Мажоритарное устройство относится к измерительной технике и может быть использовано в многоканальных хранителях времени. Цель изобретения - повышение надежности работы и расширение области применения. Мажоритарное устройство - изобретение. дополнительное к авт. св. № 1119196. Новым является включение в устройство четвертого, пятого и шестого Dтриггеров и четвертого, пятого, шестого элементов И, выходы которых соединены соответственно с D-входами четвертого, пятого и шестого D-триггеров, С-входы которых соединены с выходами первого, второго и третьего элементов И соответственно, а выходы этих D-триггеров соединены с пятыми входами первого, второго и третьего элементов И соответственно, при этом входы четвертого, пятого и шестого элементов И соединены с выходами i пороговых элементов по мажоритарной трехканальной логике. 2 ил. (Л

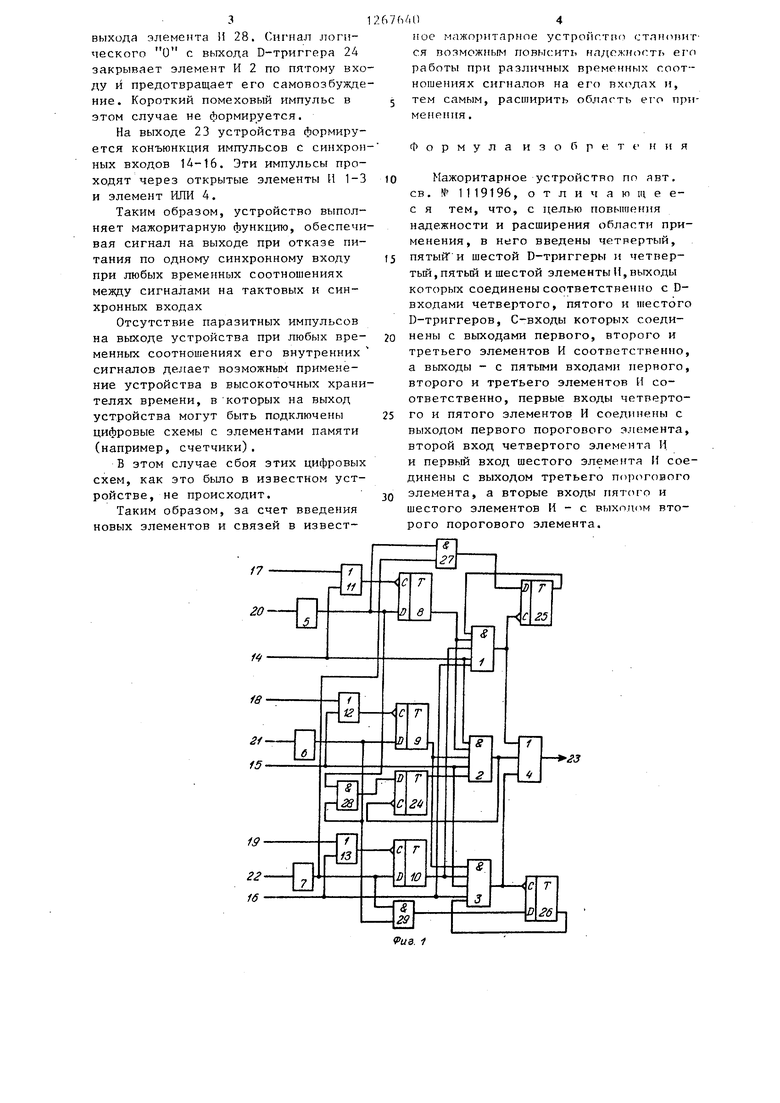

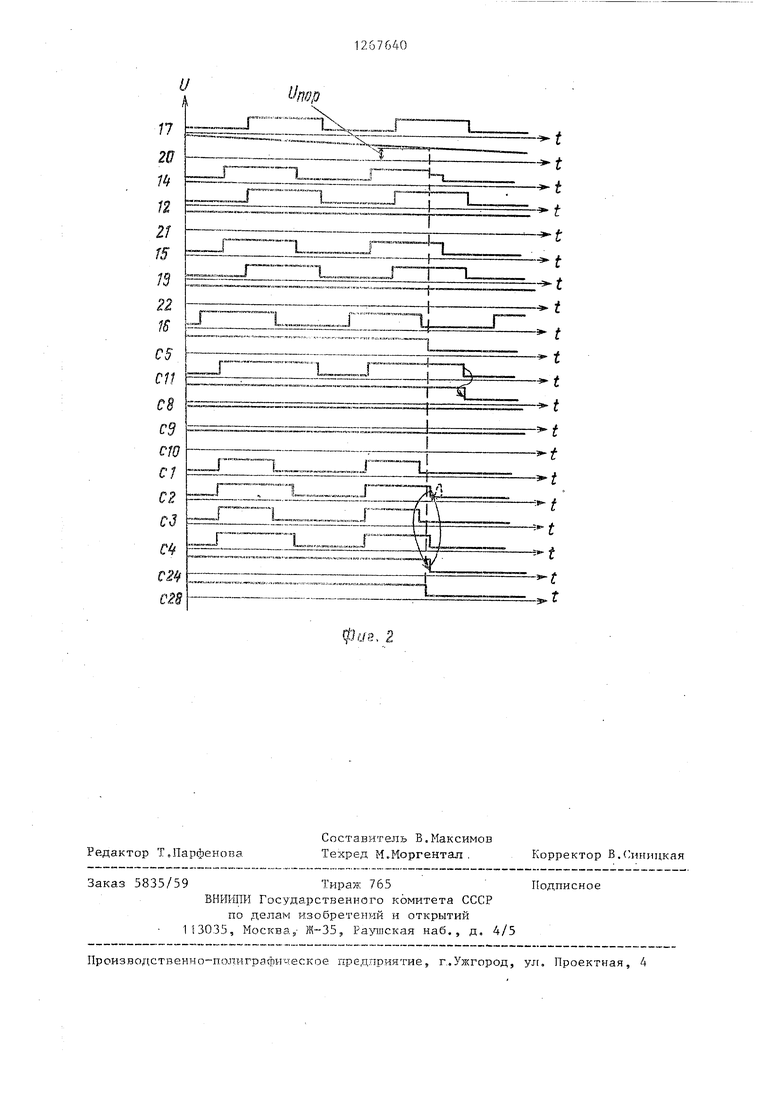

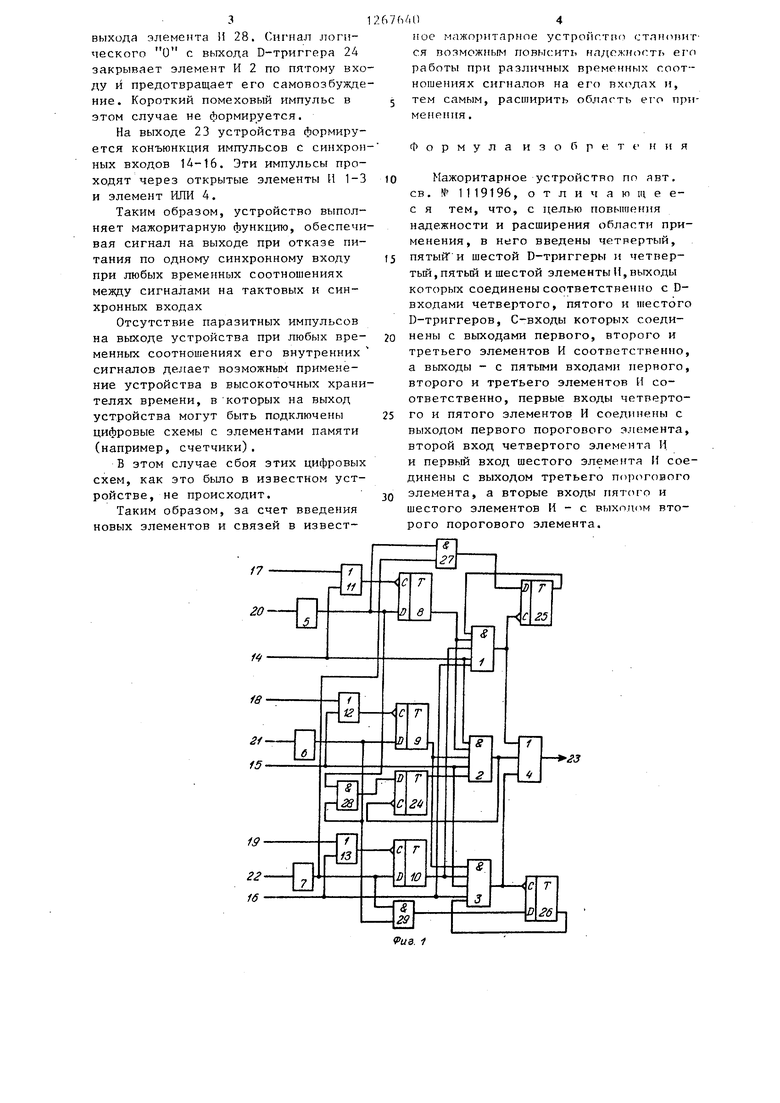

14) Изобретение относится к измерительной технике и предназтгачерю для построения мажоритарных устройств мно1Ч)канальньтх хранителей времени и является усовершенствованием устройства по авт.св. № 1119196/24, Целью изобретения явлйется повышение надежности работы и расширени области применения. На фиг.1 приведена функциональна схема устройства; на фиг.2 - времен ные диаграмм. работы устройства. Устройство содержит (фиг.1) первые элементы И 1-3, первый элемент ИЛИ 4, пороговые элементы 5-7., первые D-триггеры 8-10, вторые элементы ШИ 11-13, синхронные входы 14-1 тактовые входы 17-19, шины 20-22 пи тания соответственно первого, второ го и третьего каналов, выход устрой ства 23, вторые D-триггеры 24-26, вторые элементы И 27-29. Мажоритарное устройство работает следующим образом. При исправной работе трех канало на шинах питания 20-22 присутствует высокий уровень напряжения, поэтому ,на выходах пороговых элементов 5-7 постоянно присутствует потенциал логической 1. Импульсы поступающие с тактовых входов 17-19 через соответствующие элементы ИЛИ 11-13 устанавливают D-триггеры 8-10 в сос тояние 1, благодаря чему элементы И 1-3 постоянно открыты по третьим четвертым входам. На выходе 23 устройства о-казывается сигнал, получен ный в результате мажоритарной обработки сигналов синхронных входов 14-16 с помощью элементов И 1-3 и элемента ИЛИ 4. Вновь введенные эле менты и связи в этом случае не влияют на работу устройства, так как на первые и вторые входы элементов И 27-29 поступает потенциал уровня логической 1 с выходов пороговых элементов 5-7, что приводит к появлению на выходах элементов И 27-29 также потенциалов логической 1, которые поступают на D-входы тригге ров 24-26. Данные триггеры под воздействием задних фронтов импульсов выходов элементов И 1-3 на их С-вхо удерживаются в 1 по выходам и раз решают прохождение импульсов через элементы И 1-3, открывая их потенциалом логической 1 по их пятым входам и абсолютно не вмешиваясь в работу устройства. IaccMOTpPiM cjiyqafi, когда импульсные последовательтюсти на тактовых входах 17-19 задержаны по времени относительно импульсных последовательностей на синхронных входах 14-16 так, что фронт тактовых импульсов приходит во время наличия импульсов на синхронных входах. В этом случае также существует временное рассогласование между импульсами на синхронном входе 16 и на синхронных входах 14 и 15 (импульсы на входе 16 опережают импульсы на входах 14 и 15) из-за различного времени срабатывания элементов каналов. При уменьшении напряжения питания на одной из шин питания 20-22, например на шине 20 первого канала, на синхронный вход первого канала 14 устройства начинают поступать импульсы уменьшающейся амплитуды. Эти импульсы идут на nepBF-ie входы элементов И 1 и 2. В рассмотренном случае амплитуда импульсов на синхронном входе 14 достигает порогового значения, при котором может начаться возбуждение элементов И 1 и 2 в момент времени, когда импульс на синхронном входе третьего канала 16 уже закончился. В тот же момент времени на выходе порогового элемента 5 устанавливается потенциал логического О, так как уровень напряжения питания на шине 20 снизился до .порога срабатывания порогового элемента (/jof ) .Логический О с выхода порогового элемента 5 формируется логический О на выходе элементов И 27 и 28, которьй. поступает на D-входы триггеров 25 и 24 соответственно. Элемент И 1 оказьшается закрытым по второму входу потенциалом логического О с синхронного входа 16 и поэтому не возбу кдается. В тоже время элемент И 2 открыт по второму, третьему и четвертому входам потенциалом логической 1 с выходов триггеров 8 и 9 и с синхронного входа 15 и может войти в режим возбуждения ПОД действием импульсов пониженной амплитуды, поступ ;ющих на его первый вход с синхронного входа 14. Но этого не происходит, так как задний фронт первого (основного) импульса с выхода элемента И 2, поступающий на С-вход триггера 24, устанавливает этот D-триггер в состояние логического О по выходу, потому что на Dвходе триггера 24 логический О с

3

выхода элемента И 28. Сигнал логического О с выхода D-триггера 24 закрывает элемент И 2 по пятому входу и предотвращает его самовозбужде ние. Короткий помеховый импульс в этом случае не формируется.

На выходе 23 устройства формируется конъюнкция импульсов с синхрон ных входов 1Д-16. Эти импульсы проходят через открытые элементы И 1-3 и элемент ИЛИ 4.

Таким образом, устройство выполняет мажоритарную функцию, обеспечи вал сигнал на выходе при отказе питания по одному синхронному входу при любых временных соотношениях мевду сигналами на тактовых и синхронных входах

Отсутствие паразитных импульсов на выходе устройства при любых временных соотношениях его внутренних сигналов делает возможным применение устройства в высокоточных храни телях времени, в которых на выход устройства могут быть подключены цифровые схемы с элементами памяти (например, счетчики).

В этом случае сбоя этих цифровых схем, как это было в известном устройстве, не происходит.

Таким образом, за счет введения новых элементов и связей в извест267Ь/.П4

псе мажоритарное устройг/пи) стлионится возможным повысить р{лдежнпг.ть его работы при различных временных соотношениях сигналов на его входах и, 5 тем самым, расширить область ето применения.

Ф о р м у л а и 3 о б р е т f н и я

Мажоритарное устройство по явт. св. № 1119196, отличающеес я тем, что, с целью повышения надежности и расширения области применения, в него введены четвертый, пятый и шестой D-триггеры и четвертый, пятый и шестой элементы И, выходы которых соединены соответственно с Dвходами четвертого, пятого и шестого D-триггеров, С-входы которых соединены с выходами первого, второго и третьего элементов И соответственно, а выходы - с пятыми входами первого, второго и третьего элементов И соответственно, первые входы четвертого и пятого элементов И соединены с выходом первого порогового эле.мента, второй вход четвертого элемента И. и первый вход шестого элемента И соединены с выходом третьего порогового элемента, а вторые входы пятого и шестого элементов И - с выходом второго порогового элемента.

фаз. 2

| Мажоритарное устройство | 1983 |

|

SU1119196A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-10-30—Публикация

1985-01-07—Подача