ственно с выходом, с первым, вторым и третьим входами блока- управления счетными и корректирующими импульсами, четвертый вход которого соединен с вторыми входами первых

.структур И второго элемента И-ИЛИ-Н и элемента И-ИЛИ, второй вход второ структуры И которого соединен с пятым входом блока управления счетным корректирующими импульсами, шестой

. аход которого соединен с тактовым входом первого D-триггера и счетным входом счетчика.

3. Устройство по п.1, о т л ичающееся тем, что блок сравнения колов содержит мультиплексор, два элемента И-ИЛИ-НЕ, два элемента НЕ, элемент И-НЕ и два D-триггера, выход мультиплексора соединен с входами первой структуры И первого элемента И-ИЛИ-НЕ и с первым входом первой структуры И второго элемента И-ИЛИ-НЕ, выход которого соединён с входом установки в ноль первого D-триггера, прямой выход которого соединен с первым входом элемента И-НЕ, второй вход которого соединен с выходом первого элемента И-ИЛИ-НЕ и с входом первого элемента НЕ, выход которого соединен с тактовым входом первого D-триггера, вход D которого соединен с шиной потенциала логической единицы, выход элемента И-НЕ соединен с входом установки в ноль второго D-триггера, D-вход и тактовый вход которого соединены соответственно с шиной потенциала логического нуля и с выходом второго элемента НЕ, вход которого соединен с входами второй структуры И второго элемента И-ИЛИ-НЕ и соединен с управляющим входом блока сравнения кодов, выход, второй и третий входы которого соединены соответственно с инверсньам выходом второго D-триггера и с первым, вторым управляющими входами мультиплексора, первый, второй и третий информационные входы которого соединены с шиной потенциала логической единицы, четвертый и пятый информационные входы мультиплексора соединены соответственно с шинами потенциалов логических нуля и единицы, первая из которых соединена с шестым, седьмым и восьмым информационными входами мультиплексора третий управляющий вход которого соединен с входа:ми второй структуры И первого элемента И-ИЛИ-НЕ, с вторым входом первой структуры И второго элемента И-ИЛИ-НЕ и соединена с первым входом блока сравнения, кодов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ СИТУАЦИЙ | 2000 |

|

RU2195703C2 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1506570A1 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| УПРАВЛЯЮЩАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2520350C2 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2011 |

|

RU2494006C2 |

| СИСТЕМА УПРАВЛЕНИЯ | 2011 |

|

RU2527570C2 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

РЕЗЕРВИРОВАННОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО, содержащее генератор счетных импульсов, генератор сдвиговых импульсов и каналы, каждый из которых содержит элемент НЕ, счет.чик, мажоритарный элемент, преобразователь параллельного кода в последовательный и блок сравнения кодов, в каждом канале разрядные выходы счетчика соединены с информационными входами преобразователя параллельного кода в последовательный, выход которого соединен с первым входом блока сравнения кодов, остальные входы которого соединены соответственно с выходами преобразователей параллельного кода в последовательный других каналов, в каждом канале первый и второй входы преобразователя параллельного кода в последовательный соединены соответственно с выходом генератора - сдвиговых импульсов и с выходом элемента НЕ, выход последнего разряда счетчика- соединен с первым входом мажоритарного элемента, остальные входы которого соединены соответственно с выходами псЗследн х разрядов счетчиков других каналов, о т л и ч а ю ы е ё с я тем, что, с целью повышения-надеж.ности, в него введены генератор кор-; ректирующих и myльcoв, два элемента управления, а в каждый канал - блок управления счетными и корректирукяци-ми импульсами, с первого по шестой входы и выход которого соединены соответственно с выходом блока сравнения кодов, с выходами первого, второго элементов управления, с выходом генератора корректирующих импульсов, сдвиговых импульсов, счетных импульсов и счетным входом счетчика, вход элемента .НЕ соединен с управляющим входом блока сравнения кодов и с выходом генератора корректируют щих импульсов. 2. Устройство по П.1, о т л и..чающееся тем, что блок упраВ с ления счетными и корректирующими ® импульсами содержит счетчик, два (Л D-триггера, два элемента И-ИЛИ-НЕ и элемент И-ИЛИ, первый вход первой, структуры И которого соединен с прямым выходом первого D-триггера и с входом установки в ноль второго ,Ь-триггера, инверсный выход которого соединен с первыми входами первых структур И первого и второго элементов И-ИЛИ-НЕ, с входом уста-, а новки нуля счетчика и с D-входом 4 4 второго D-триггера, тактовый вход и прямой выход которого соединены соответственно с выходом и с первым входом второй структуры и второго сл элемента И-ИЛИ-НЕ, второй вход второй структуры И которого соединен с одним из выходов счетчика, выход первого элемента И-ИЛИ-НЕ соединен с входом D-первого D-триггера,инверсный выход которого соединен с первыми входами вторых структур И элемента И-ИЛИ и перврго элемента И-ЙЛИ-НЕ/ выход элемента И-ИЛИ, второй вход первой структуры И первого элемента И-ИЛИ-НЕ, вход установки в единицу первого D-триггера и второй вход второй структуры И первого ИГ-ИЛИ-НЕ соединены соответ

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых устройств повышенной надежности. Известно резервированное пересчетное устройс-тво с мажоритарным элементом и схемой восстановления информации в сбившемся счетчикеtl3. Недостатком такого резервированного устройства является п-крат. ное увеличение объема элементов сравнения при увеличении числа раз рядов счетчика на один разряд (п 2,3...}. Известно резервированное перёсчетное устройство, содержащее гене ратор счетных импульсов, генератор сдвиговых импульсов и каналы, кажда0й из которых содержит элемент НЕ счетчик, мажоритарный элемент,преобразователь параллельного кода в последовательный и блок сравнения кодов, в каждом канале разрядные вЛходы счётчика соединены с информационными входами преобразователя параллельного кода в последователь ный, выход которого соединен с первым входом блока сравнения кодо остальные входы которого соединены соответственно с выходами преобразователей параллельного кода в последовательный других каналов, в каждом канале первый и второй входы преобразователя параллельного кода в последовательный соединены соответственно с выходом генератора сдвиговых импульсов и с выходом элемента НЕ, выход последнего разряда счетчика соединен с первым входом мажоритар- . ного элемента, остальные входа которого соединены соответственно с выходами последниз разрядов счетчиков других каналов, вход элемента НЕ соединен с. генератором счетных импульсов и со счетным входом счетчика, установочные входы которого соединены с выходами блока перекоса, управляющий вход которого соединен с выходом блока сравнения кодов, информационные входы блоков переноса первого, второго и третьего каналов соединены соответственно с выходами счетчиков второго, третьего и первого каналов С2. Недостаток известного устройства состоит в том, что при большом числе разрядов счетчика количество связей между каналами также большоэ что снижает надежность устройства.

Цель изобретения - повышение надежности за счет уменьшения количества связей между каналами.

Поставленная, цель достигается тем, что в резервированное пересчетное устройство, содержащее генератор счетных импульсов, генератор сдвиговых импульсов и каналы, каждый из которых содержит элемент НЕ, счетчик, мажоритарный элемент, преобразователь параллельного кода впоследовательный и блок сравнения кодов, в каждом канале разрядные выходы счетчика соединены с информационными входами преобразователя параллельного кода в последовательный, выход которого соединен с первым входом блока сравнения кодов остальные входы которого соединешл соответственно с выходами преобразователей параллельного кода в послдовательный других каналов, в каждом канале первый и второй входы преобразователя параллельного кода в последовательный соединены соответственно с выходом генератора сдвиговых импульсов и с выходом элемента НЕ, выход последнего разряда счетчика соединен с первым входом мажоритарного элемента, остальные входы которого соединены соответственно с выходами последнихразрядов счетчиков других каналов, введены генератор.корректирующих импульсов, два элемента управления, а в каждЕлй канал - блок управления счетными и корректиру ющими импульсами, с первого по шестой входы и выход которого соединены соответственно с выходом блока сравнения кодов, с вы- . ходами первого, второго элементов управления,„ с. выходом генератора корректирующих импульсов, сдвиговых импульсов, счетных импульсов и счетным входом счетчика, вход элемента: НЕ соединен с управляющим входом блока сравнения, кодов и с выходом генератора корректирующих импульсов.

В резервированном пересчетном устройстве блок управления -счетными и корректирующими импульсами содержит счетчик, два D-триггера, два элемента И-ИЛИ-НЕ и элемент И-ИЛИ, первый вход первой структуры И которого соединен с прямым входом первого D-триггера и со входом установки в ноль второго D-триггераj инверсный выход которого соединен с первыми входами первых структур И первого; и второго элементов И-ИЛИ-Н со входом установки нуля счетчикаи с D-входом второго D-триггера,. тактовый вход и прямой выход которого соединены соответственно с выходом и с первым входом второй структуры И второго элемента И-ИЛИ-НЕ, второй вход второй структуры И которого соединен с одним из выходов счетчика, выход первого элемента И-ИЛИ-НЕ соединен со входом р -первого D-триггера., инверсный выход которого соединен с первыми входами вторых структур И элемента И-ИЛИ и первого элемента И-ИЛИ-НЕ,

выход элемента И-ИЛИ, второй вход первой структуры И первого элемента И-ИЛИ-НЕ, вход установки в единицу первого D-триггера и второй вход второй структуры И первого элемента И-ИЛИ-ЙЕ соединены соответственно с выходом, с первым, вторым и третьим входами блока управления -счетными и корректирующими импульсами, четвертый вход которого соединен со вторыми входами первых структур И второго элемента И-ИЛИ-НЕ и элемента.И-ИЛИ, второй вход второй структуры И которого соединен с пятым входом блока управления счетными и корректирующими импульсакш, шестой вход которого соединен с тактовьм входом первого D-трИггера и

.счетным входом счетчика.

В резервирование пересчетном устройстве блок сравнения кодов содержит мультиплексор, два элемента И-ИЛИ-НЕ, два элемента НЕ, эле мент и два D-триггера. Выход мультиплексора соединен со входами первой структуры И первого элемента И-ИЛИ-НЕ и с первым входом первой структуры И второго элемента И ИЛИ-НЕ, выход которого соединен со входом установки в ноль первого D-триггера, прямой выход KdTOрого соединён с первым входом элемента И-НЕ, второй вход которого .соединен с выходом первого элемента И-ИЛИ-НЕ и со входом первого элемента НЕ, выход которого соединен с тактовым входом первого D-триггера, вход D которого соединен с шиной потенциала логической единицы. Выход элемента И-НЕ соединен с, входом установки в ноль второго р-триггера, D-вход и тактовый вход которого соединены соответственно с шиной потенциала логического нуля и с выходом второго элемента НЕ, вход которого соединен со входами второй

.структуры И второго элемента И-ИЛИ-НЕ и соединён с управляющим входом блока сравнения кодов, выход, второй-и третий входы которого соединены сортветственно с инверсным выходом второго D-триггера и с первым, вторым управляющими входами мультиплек-. сора, первый, второй и третий информационные входы которого соединены с шиной потенцисша логической единицы. Четвертый и пятый информационные входы мультиплексора соединены

соответственно с шинами потенциало логических нуля и единицы, первая из которых соединена с шестым,седьмым и восьмым информационными входами мультиплексора третий управляющий вход которого соединен со входами второй структуры И первого элемента И-ИЛИ-НЕ, со вторым входо первой структуры И второго элемента И-ИЛИ-НЕ и соединена с первым входом блока сравнения кодов.

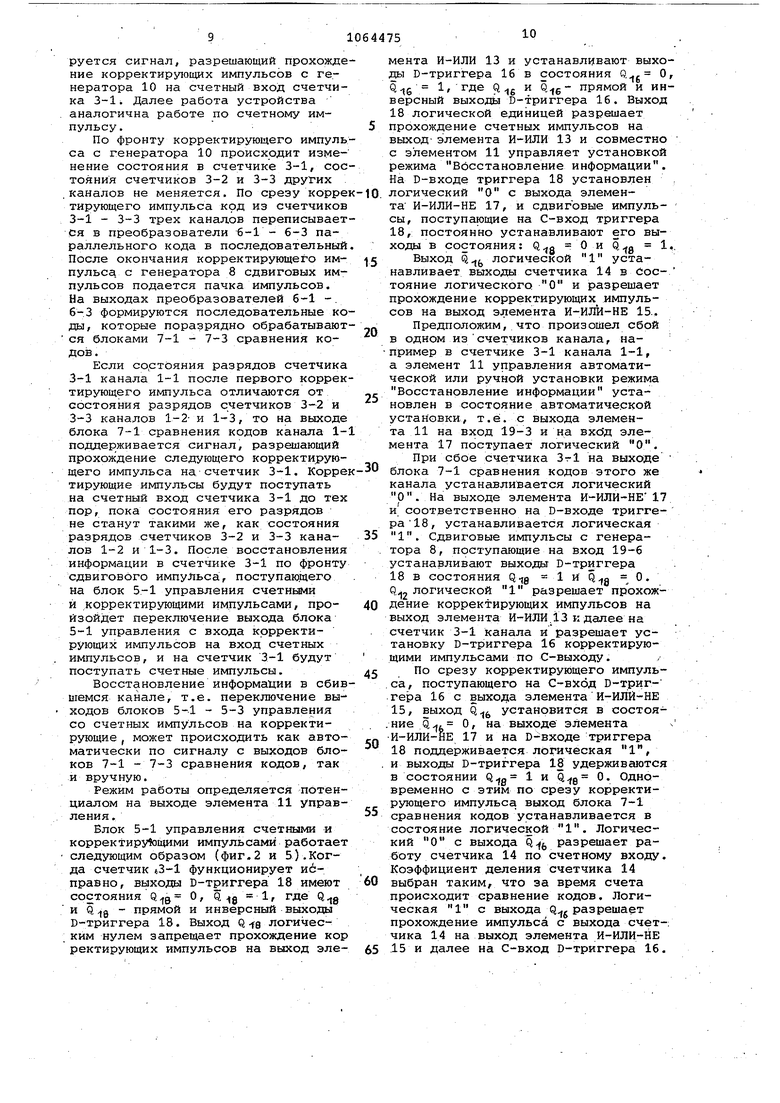

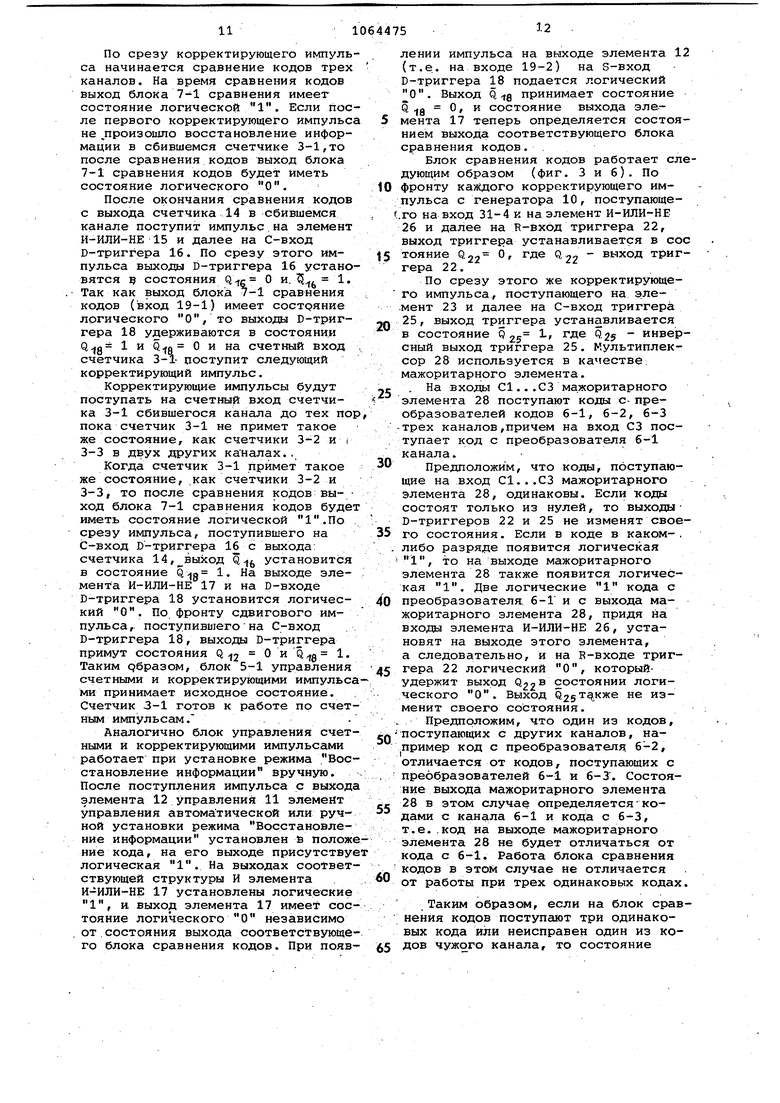

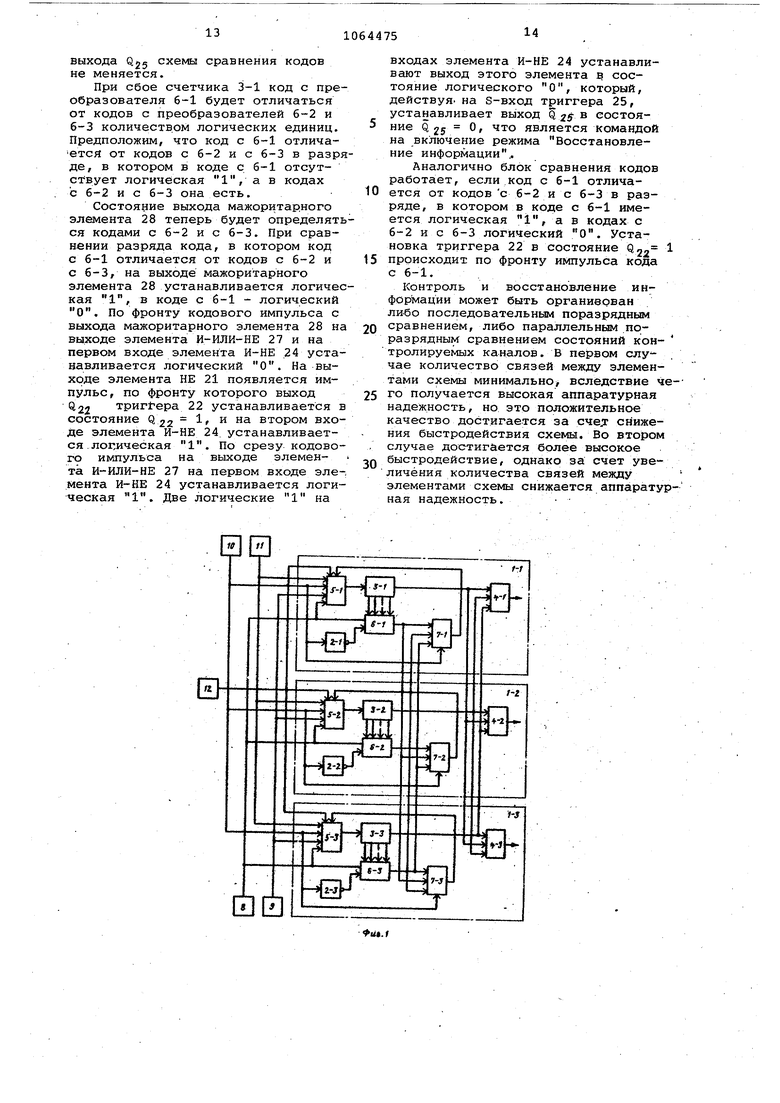

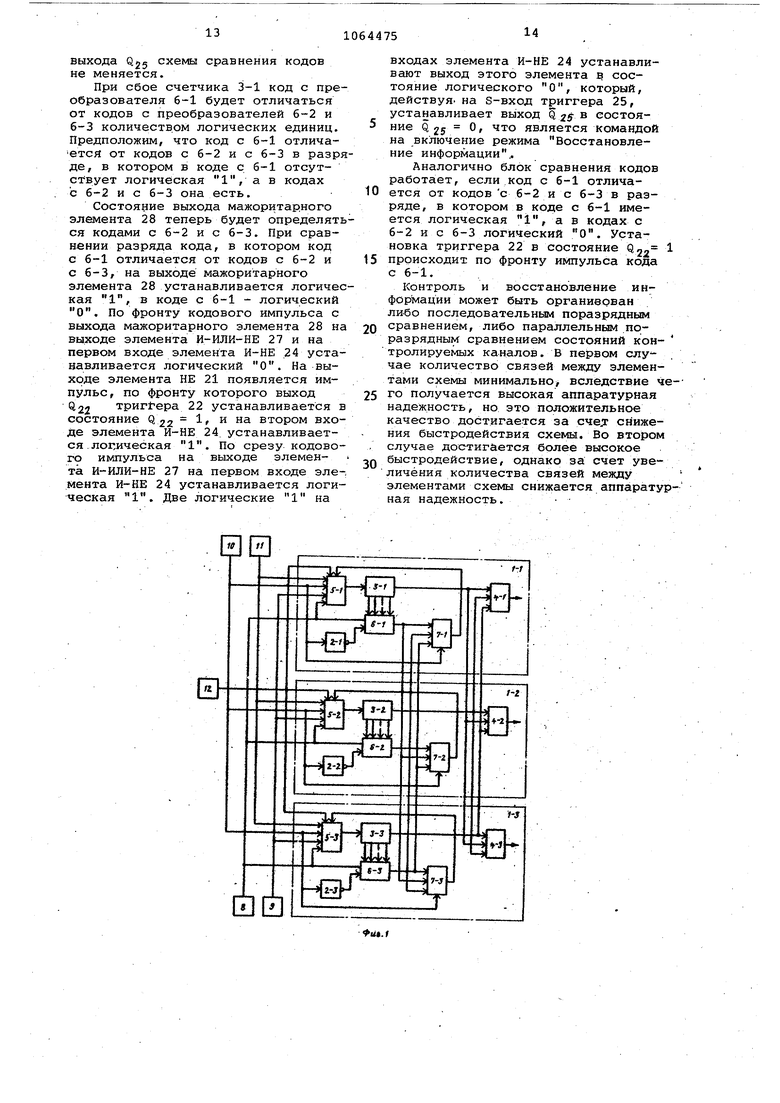

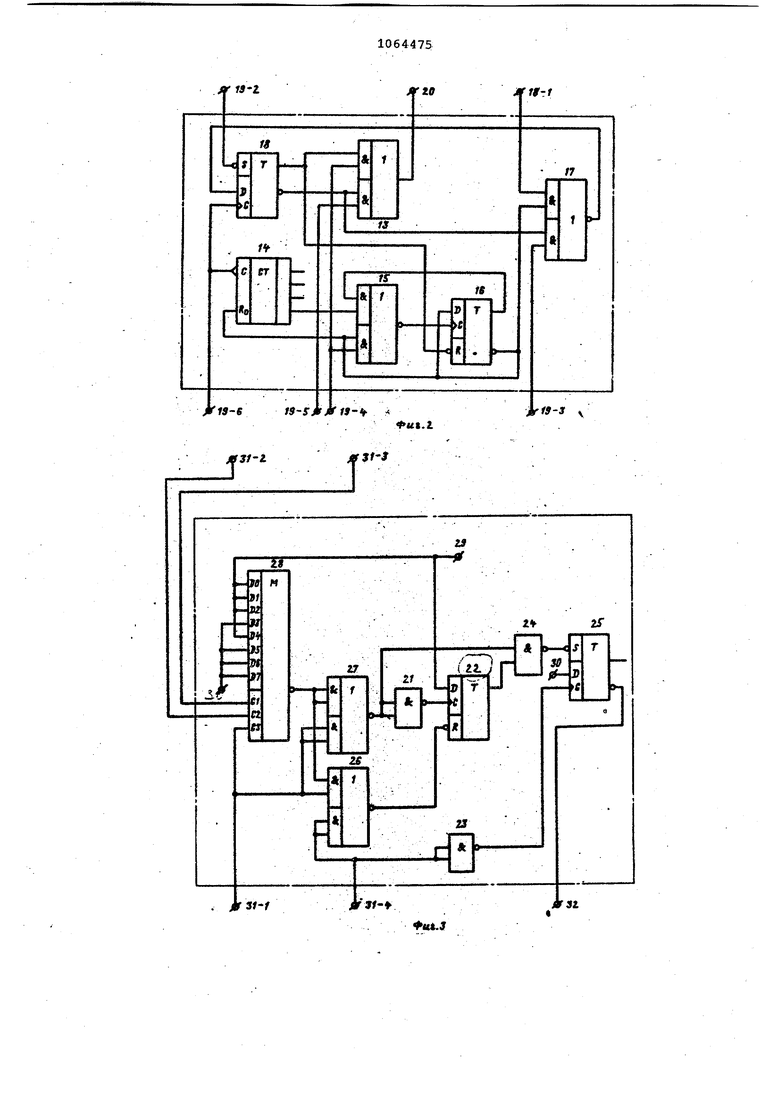

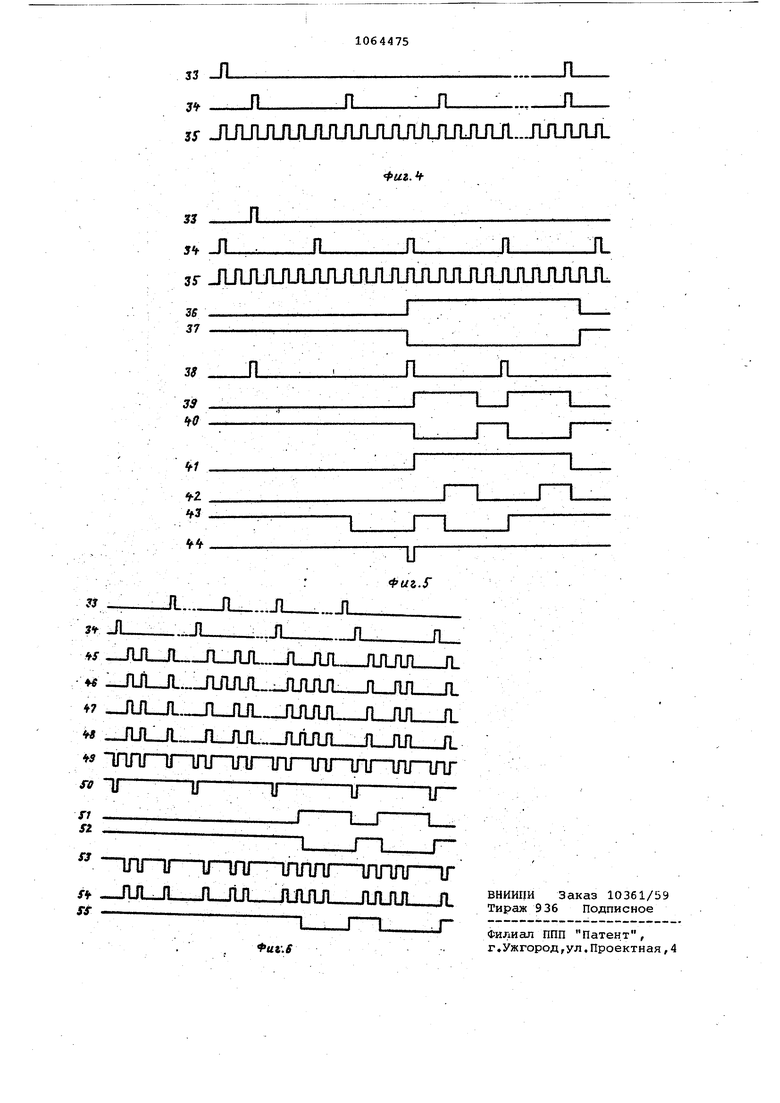

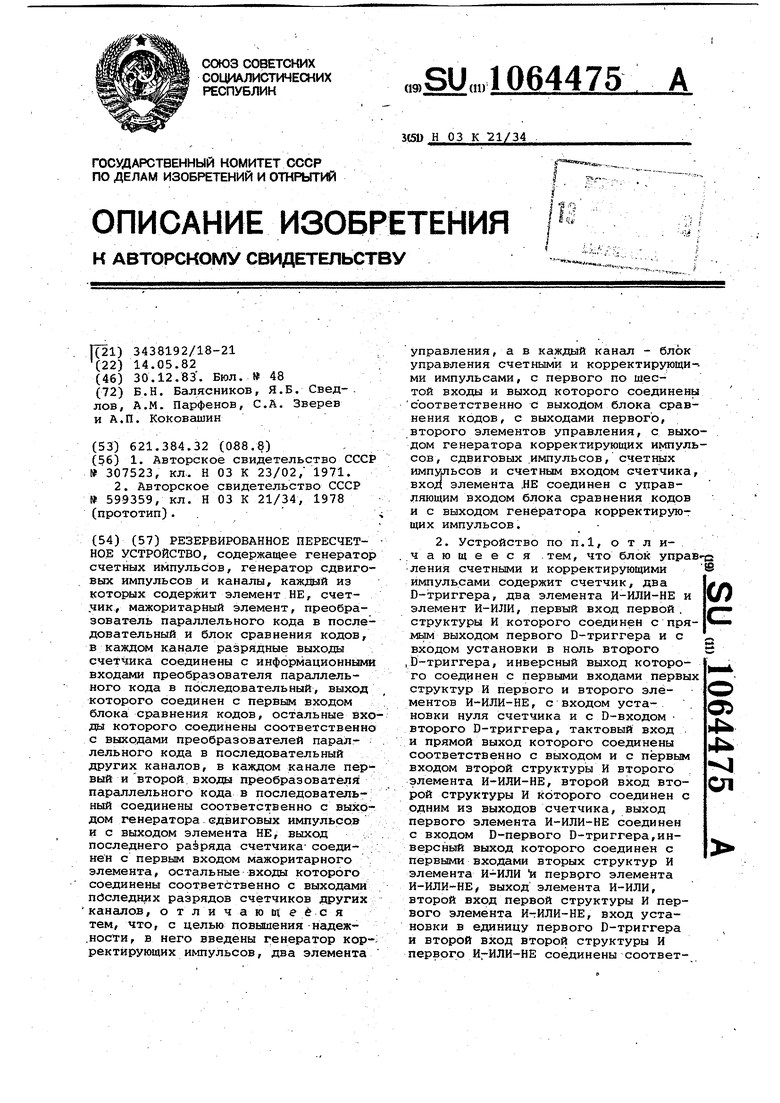

На фиг.1 приведена блок-схема резервированного пересчетного устройства/ на фиг.2 - схема блока управления счетными и корректирующими импульсами/.на фиг.З - схема блока сравнения кодов, на фиг. 4-6 временные диаграммы работы соответственно генераторов счетных, корректирующих, сдвиговых импульсов, блока управления счетными и корректирующими импульсами и блока сравнния кодов.

Устройство содержит (фиг.1) каналы 1-1 - 1-3, элементы НЕ 2-1 2-3, счетчики 3-1 - 3-3, мажоритарные элементы 4-1 - 4-3/ блоки 5-1 - ,5-3 управления счетнЕлми и корректирующими импульсами, преобрзователи 6-1 - б-З параллельного кода в последовательный, блоки 7-1 - 7-3 сравнения кодов, генератор 8 сдвиговых импульсов, генератор 9 счетных импульсов, генератор 10 корректирующих импульсов и элементы 11 и 12 управления.

, Разрядные выхЪды счетчиков 3-1 - 3-3 соединены соответственно q информационными входами преобразователей 6-1 - б-З, выходы которы соединены соответственно с первыми входами блоков 7-1 - 7-3 сравнения кодов, с вторыми входами блоков 7-2, 7-3, 7-1 сравнения кодов и с третьими входами блоков 7-3, 7-1, 7-2 сравнения кодов, выходы которы соединены соответственно с первыми входами блоков 5-3, 5-1, 5-2 управления счетными и корректирующими импульсами, вторые входы которых соединены с выходом элемента 12 управления. Выход элемента 11 управления соединен с третьими входами блоков 5-1 - 5-3 управления счеными и корректирующими импульсами, четвертые входы которых соединены с выходом генератора 10 корректирующих импульсов, с управляющими входами блоков 7-1 - 7-3 сравнения кодов и с входами элементов 2-1 2-3 НЕ, .выходы которых соединены соответственно с первыми входами преобразователей 6-1 - б-З параллельного кода в последовательный, вторые входы которых соединены с выходом генератора 8 с двиговых импульсов. Выход генератора 9 счетных импульсов соединен с пятыми входами блоков 5-1 - 5-3 управления счетными и корректирующими импульсами, выходы которых соединены соответственно со счетными входами счетчиков 3-1 3-3. Входы каждого из мажоритарных элементов 4-1 - 4-3 соединены с выходами последнего разряда счетчиков 3-1 - 3-3. Шестые входы блоков 5-1 - 5-3 управ0 ления счетными и корректирующими

импульсами соединены с выходом генератора 8 сдвиговых импульсов.

Схема блока управления счетными и корректирующими импульсами содер5 жит (фиг.2) элемент И-ИЛИ 13, счетчик 14, элемент И-ИЛИ-НЕ 15, D-триггер 16, элемент И-ИЛИ-НЕ 17, D-триггер 18, входы 19-1 -. 19-6 (соответственно входа с первого по

0 шестой блоков 5-1 - 5-3 управления счетными и корректирующими импульсами), выход 20 блоков 5-1 - 5-3 управления счетными и корректирующими импульсами.

5 Прямой выход D-триггера 18 соединен с. первым входом первой структуры И элемента И-ИЛИ 13 и с входом установки в ноль D-триггера 16, инверсный выход которого соединен с

0 первым входом первой структуры И элемента И-ИЛИ-НЕ 17, с D-входом D-триггера 16, с первым входом первой структуры И элемента И-ИЛИ-НЕ 15 и с входом установки, в ноль счетчи5 ка 14, выход одного из разрядов которого соединен с первым входом второй структуры И элемента И-ИЛИ-НЕ 15, выход которого соединен с тактовым входом D триггера 16, прямой

выход которого соединен с вторым

входом второй структуры и элемента И-ИЛИ-НЕ 15, второй вход первой структуры И которого соединен с входом 19-4 и с вторым входом первой структуры И элемента И-ИЛИ 13, первый вход второй структуры И которого соединен с инверсным выхсЛчом D-триггера 18 и с первым входом второй структуры И элемента И-ИЛИ-НЕ 17, вторые входы первой/ второй структур И и выход которого соединены

соответственно с входами 19-1, 19-3 и с входом D триггера 18, вход установки в единицу которого соединен с входом 19-2. Тактовый вход D-триггера 18 и счетный вход счетчика 14 соединены с входом 19-6. Второй вход второй, структуры И и выход элемента И-ИЛИ 13 соединены соответственно с входом 19-5 и выходом 20.

Схема блока сравнения кодов содержит элемент НЕ 21, D-триггер 22, элемент НЕ 23, Jэлeмeнт И-НЕ 24, В-Триггер 25, элементы И-ИЛИ-НЕ 26 и 27, мультиплексор 28, шину 29

потенциала логической единицы, шину 30 потенциала логического нуля, вх ды 31-1 - 31-3 (соответственно вхо с первого по третий блоков 7-1 7-3 сравнения кодов), управляющий вход 31-4 и выход 32 блоков 7-1 ,7-3 сравнения кодов. Шина 29 потенциала логической единицы соединена с D-входом триггера 22 и с .первыми тремя информационными входами мультиплексора 28, выход которого соединен с первым входом первой структуры И элемента И-ИЛИ-НЕ 26 и с входами первой структуры И элемента И-ИЛИ27,выход которого соединен через элемент НЕ 21 с тактовым входом В-триггера 22 и С первым входом эл мента И-НЕ 24, второй вход и выход которого.соединены соответственно прямым выходом D-триггера 22 -и с входом установки в ноль D-триггера 25,тактовый вход которого соедине с выходом элемента НЕ 23, вход которого соединен с входом 31-4 j с входами второй структуры И элемента И-ИЛИ-НЕ 26, выход которого соединен с входом установки в ноль D-триггера 22. Шина 30 потенциала логического нуля соединена с D-вхо дом D-триггера 25 и с четвертым ин формационным вхрдом мультиплексора 28,пятый информационный вход кото рого соединен с шиной 29 потенциала логической единицы. Шестой,седь мой и восьмой информационные входы мультиплексора 28 соединены с шиной 30 потенциала логического, нуля Входа 31-3, 31-2 соединены соответ ственно с пёрвьм и вторым управляю щими входами мультиплексора 28, третий управляющий вход которого соединен с входами второй структуры И элемента .И-ИЛИ-НЕ 27, с вторым, входом первой структуры И элемента И-ИЛИ-НЕ 26 и с входом 31-1. Выход 32 соединен с инверсным выхо дом D-триггера 25. На фиг.4 обозначены диаграммы 33-35 сигналов на выходах соответственно генератора 9 счетных импульсов, генератора 10 корректирую щих импульсов и генератора 8 сдвиговых импульсов. На фиг.5 обозначены диаграммы 36-44 сигналов соответственно на прямом, инверсном выходах триггера 18, на выходе элемента И-ИЛИ 13, на прямом, инверсном выходах триггера 16, на выходе элемента И-ИЛИ17, на выходе счетчика 14, на вход 19-1 и на входе 19-2. На фиг. 6 обозначены диаграммы 45-55 соответственно на входах 31-1 - 31-3, на выходе мультиплексора 28, на выходе элемента И-ИЛИ26,на выходе элемента НЕ 23, на в ходе триггера 22, на инверсном выходе триггера 25, на выходе элемента И-ИЛИ -НЕ 27, на выходе элемента НЕ 21 и на выходе элемента И-НЕ 24.- В качестве элементов 11 и 12 управления могут быть использованы соответственно переключатель и кнопка.. Резервированное пересчетное устройство работает следующим образом (фиг.1,4). На входы блоков 5-1 - 5-3 управления счетными и корректирующими импульсами трех каналов синхронно поступают счетные импульсы от генератора 9 счетных импульсов и корректирующие импульсы от генератора 10 корректирующих импульсов. Предположим, что счетчики 3-1 - 3-3 всех трех каналов функционируют исправно. В этом случае выходы блоков 7-1 - 7-3 сравнения кодов имеют такие состояния, что на вьаходы блоков 5-1 - 5-3 управления счетными и корректирующими импульсами проходят счетные импульсы, .которые поступают на счетные входы счетчиков 3-1 - 3-3. По фронту с.четного импульса происходит изменение состояния в счетчиках 3-1 - 3-3. По срезу корректирующего импульса, поступающего на входы преобразователей 6-1 - 6-3 через, элементы .НЕ 2-1 - 2-3,; код из счетчиков 3-1 - 3-3 переписываемся соответственно в преобразователи 6-1 - 6-3 параллельного кода в пос- ; ледовательный.После окончания корректирующего импульса на другие входы преобразователей 6-1 - 6-3 поступает пачка импульсов с генератора 8 сдвиговых импульсов. На выходах преобразователей 6-1 6-3 формируются последовательные коды, которыепоразрядно обрабатываются блоками 7-1 - 7-3 сравнения кодов. На блоках 7-1 - 7-3 формируются сигналы, разрешающие прохождение на счетный вход счетчиков 3-1 - 3-3 счетных или корректирующих импульсов. Если все разряды последовательных кодов с выходов преобразователей 6-1 - 6-3 совпадают, то на выходах блоков 7-1 - 7-3 сравнения кодов поддерживается сигнал, разре1аающий прохождение на счетные входы счетчиков 3-1-3-3 счетных импульсов и запрещающий прохождение корректирующих импульсов, Если в каком-либо разряде кода в одном из каналов, например в канале 1-1, имеется сигнал, отличный от сигналов в двух других каналах, например, в каналах 1-2 и 1-3, что свидетельствует о сбое в счетчике 3-1, то на выходе блока 7-1 сравнения кодов кана:ла 1-1 сформируется сигнал, разрешающий прохожде ние корректирующих импульсов с генератора 10 на счетный вход счетчика 3-1i Далее работа устройства аналогична работе по счетному импульсу. По фронту корректирующего импуль са с генератора 10 происходит изменение состояния в счетчике 3-1, сос тояния счетчиков 3-2 и 3-3 других .каналов не меня.ется. По срезу корре тирующего импульса крд из счетчиков 3-1 - 3-3 трех каналов переписывает ся в преобразователи 6-1 - б-З параллельного кода в последовательный После окончания корректирующего импульса с генератора 8 сдвиговых импульсов подается пачка импульсов. На выходах преобразователей 6-1 -. 6-3 формируются последовательные ко ды, которые поразрядно обрабатывают ся блоками 7-1 - 7-3 сравнения кодов. Если состояния разрядов счетчика 3-1 канала 1-1 после первого коррек тирующего импульса отличаются от состояния разрядов счетчиков 3-2 и 3-3 каналов 1-2- и 1-3, то на выходе блока 7-1 сравнения кодов канала 1поддерживается сигнал, разрешающий прохождение следующего корректирующего импульса на счетчик 3-1. Корре тирующие импульсы будут поступать на счетный вход счетчика 3-1 до тех пор, пока состояния его разрядов не станут такими же, как состояния разрядов счетчиков 3-2 и 3-3 каналов 1-2 и 1-3. После восстановления информации в счетчике 3-1 по фронту сдвигового импульса, поступающего на блок 5-1 управления счетными и корректирующими импульсами, произойдет переключение выхода блока 5-1 управления с входа корректирующих импульсов на вход счетных импульсов, и на счетчик 3-1 будут поступать счетные импульсы. Восстановление информации в сбив шемся канале, т.е. переключение выходов блоков 5-1 - 5-3 управления со счетных импульсов на корректирующие , может происходить как автоматически по сигналу с выходов блоков 7-1 - 7-3 сравнения кодов, так и вручную. Режим работы определяется потенциалом на выходе элемента 11 управления. Блок 5-1 управления счетными и корректирующими импульсами работает следующим образом (фиг.2 и 5).Когда счетчик 3-1 функционирует исправно, выходы D-триггера 18 имеют состояния О, 1, где и - прямой и инверсный выходы D-триггера 18. Выход Q а логическим нулем запрещает прохождение кор ректирующих импульсов на выход элемента И-ИЛИ 13 и устанавливают выходы D-триггера 16 в состояния 0.5 О, 1,тде Q 6 и 0.6 - прямой и инверсный выходы D-триггера 16. Выход 18 логической единицей разрешает прохождение счетных импульсов на выход-элемента И-ИЛИ 13 и совместно с элементом 11 управляет установкой режима Восстановление информации. На D-входе триггера 18 установлен логический О с выхода элемента И-ИЛИ-НЕ 17, и сдвиговые импульсы, поступающие на С-вход триггера 18, постоянно устанавливают его выходы в состояния: 0 и 1,. Выход Q(j логической 1 устанавливает выходы счетчика 14 в Соетояние логического О и разрешает прохождение корректирующих импульсов на выход элемента И-ИЛИ-НЕ 15.. Предположим, что произошел сбой в одном изсчетчиков канала, например в счетчике 3-1 канала 1-1, а элемент 11 управления автоматической или ручной установки режима Восстановление информации установлен в состояние автоматической установки, т.е. с выхода элемента 11 на вход 19-3 и на вхсЗд элемента 17 поступает логический О. При сбое счетчика Зт-1 на выходе блока 7-1 сравнения кодов этого же канала устанавливается логический О. На выходе элемента И-ИЛИ-НЕ17 и соответственно на D-входе триггера 18, устанавливается логическая 1. Сдвиговые импульсы с генератора 8, поступающие на вход 19-6 устанавливают выхо№1 D-триггера 18 в состояния 1 и 0. 0,2 логической 1 разрешает прохождение корректирующих импульсов на выход элемента И-ИЛИ.13 к далее на счетчик 3-1 канала и разрешает установку D-триггера 16 корректирующими импульсами по С-выходу. По срезу корректирующего импульса, поступающего на С-вхбд D-триггера 16 с выхода элемента И-ИЛЙ-НЕ 15, выход Q установится в состояние О, на выходе элемента И-ИЛИ-НЕ 17 и на D-входе триггера 18 поддерживается логическая 1, и выходы D-триггера 18 удерживаются в состоянии 1 и 0. Одновременно с этим по срезу корректирующего импульса выход блока 7-1 сравнения кодов устанавливается в состояние логической 1. Логический О с выхода Q(, разрешает работу счетчика 14 по счетному входу. Коэффициент деления счетчика 14 выбран таким, что за время счета происходит сравнение кодов. Логическая 1 с выхода Q gразрешает прохождение импульса с выхода счет-; чика 14 на выход элемента И-ИЛИ-НЕ .15 и далее на С-вход D-триггера 16. По срезу корректирующего импуль са начинается сравнение кодов трех каналов. На время сравнения кодов выход блока 7-1 сравнения имеет состояние логической 1, Если пос ле первого корректирующего импульс не .произошло восстановление информации в сбившемся счетчике 3-1,то после сравнения кодов выход блока 7-1 сравнения кодов будет иметь состояние логического О. После окончания сравнения кодов с выхода счетчика 14 в сбившемся канале поступит импульс.на элемент И-ИЛИ-НЕ 15 и далее на С-вход D-триггера 16. По срезу этого импульса выходы Ь-триггера 16 устано вятся э состояния Q-i6 О и. , 1. Так как выход блока 7-1 сравнения кодов (вход 19-1) имеет состояние логического О, то выходы В триггера 18 удерживаются в состоянии 1 и О и на счетный вход счетчика 3-1- поступит следующий корректирующий импульс. Корректирующие импульсы будут поступать на счетный вход счетчика 3-1 сбившегося канала до тех по пока счетчик 3-1 не примет такое же состояние, как счетчики 3-2 иг 3-3 в двух других каналах. . Когда счетчик 3-1 примет такое же состояние, как счетчики 3-2 и 3-3, то после сравнения кодов выход блока 7-1 сравнения кодов буде иметь состояние логической 1.По срезу импульса, поступившего на С-вход D-триггера 16 с выхода; счетчика 14,выход Q. установится 1. На выходе элев состояние мента И-ИЛИ-НЕ 17 и на D-входе D-триггера 18 установится логический О. По фронту сдвигового импульса,, поступившегона С-вход D-триггера 18, выходы D-триггера примут состояния Q 2 Таким рбразом, блок 5-1 управления счетными и корректирующими импульс ми принимает исходное состояние. Счетчик 3-1 готов к работе по счет ным импульсам. . Аналогично блок управления счет ными и корректирующими импульсами работает при установке режима Вос становление информации вручную. После поступления импульса с выход элемента 12 управления 11 элемент управления автоматической или ручной установки режима Восстановление информации установлен и полож ние кода, на его выходе присутству логическая 1. На выходах соответ ствующей структуры И элемента И-ИЛИ-НЕ 17 установлены логические 1, н выход элемента 17 имеет сос тояние логического О независимо от.состояния выхода соответствующе го блока сравнения кодов. При появ лении импульса на выходе элемента 12 (т.е,. на входе 19-2) на S-вход D-триггера 18 подается логический О. Выход Q-fg принимает состояние Q д О, и состояние выхода эле.мента 17 теперь определяется состоянием выхода соответствующего блока сравнения кодов. . Блок сравнения кодов работает следующим образом (фиг. 3 и 6). По фронту каждого корректирующего импульса с генератора 10, поступающего на вход 31-4 и на элемент И-ИЛИ-НЕ 26 и далее на В-вход триггера 22, выход триггера устанавливается в сое тояние Q,o, 6, где Q ,,„ - выход триггера 22. По срезу этого же корректирующего импульса, поступающего на эпе .мент 23 и далее на С-вход триггера 25, выход триггера устанавливается в состояние Q 25 25 инверсный выход триггера 25. Мультиплексор 28 используется в качестве, мажоритарного элемента. . На входы С1...СЗ мажоритарного элемента 28 поступают коды с- преобразователей кодов 6-1, 6-2, 6-3 трех каналов,причем на вход СЗ поступает код с преобразователя 6-1 канала. Предположим, что коды, поступающие на вход С1...СЗ мажоритарного элемента 28, одинаковы. Если коды состоят только из нулей, то выходыD-триггеррв 22 и 25 не изменят своего состояния. Если в коде в каком-, либо разряде появится логическая 1, то на выходе мажоритарного элемента 28 также появится логическая 1. Две логические 1 кода с преобразователя, 6-Г и с выхода мажоритарного элемента 28, придя на входы элемента И-ИЛИ-НЕ 26, установят на выходе этого элемента, а следовательно, и на R-входе триггера 22 логический О, которыйудержит выход Q22в состоянии логического О. Выход 9,25тд.кже не иэменит своего состояния. Предположим, что один из кодов, поступающих с других каналов, например код с преобразователя 6-2, отличается от кодов, поступающих с преобразователей 6-1 и 6-3. Состояние выхода мажоритарного элемента 28 в этом случае определяется-кодами с кана.ла 6-1 и кода с 6-3, т.е..код на выходе мажоритарного элемента 28 не будет отличаться от кода с 6-1. Работа блока сравнения кодов в этом случае не отличается от работы при трех одинаковых кодах. Таким образом, если на блок сравнения кодов поступают три одинаковых кода или неисправен один из коДов чужого канала, то состояние

выхода Qjg схемы сравнения кодов не меняется.

При сбое счетчика 3-1 код с преобразователя 6-1 будет отличаться от кодов с преобразователей 6-2 и 6-3 количеством логических единиц. Предположим, что код с 6-1 отличается от кодов с 6-2 и с 6-3 в разряде, в котором в коде с 6-1 отсутс-Гвует логическая 1, а в кодах с 6-2 и с 6-3 она есть.

Состояние выхода мажоритарного элемента 28 теперь будет определяться кодами с 6-2 и с 6-3. При сравнении разряда кода, в котором код с 6-1 отличается от кодов с 6-2 и с 6-3, на выходе мажоритарного элемента 28 устанавливается логическая 1, в коде с 6-1 - логический О. По фронту кодового импульса с выхода мажоритарного элемента 28 на выходе элемента И-ИЛИ-НЕ 27 и на первом входе элемента И-НЕ 24 устанавливается логический О. На выходе элемента НЕ 21 появляется импульс, по фронту которого выход 22 триггера 22 устанавливается в состояние 0.22 втором входе элемента И-НЕ 24 устанавливается лог,ическая 1. По срезу кодового импульса на выходе элемента И-ИЛИ-НЕ 27 на первом входе эле-, мента И-НЕ 24 устанавливается логическая 1. Две логические 1 на

входах элемента И-НЕ 24 устанавливают выход этого элемента в состояние логического О, который, действуя, на S-вход триггера 25, устанавливает выход Q гj в состояние Q 25 является командой на включение режима Восстановление информации..

Аналогично блок сравнения кодов работает, если код с 6-1 отличается от кодовс 6-2 и с 6-3 в разряде, в котором в коде с 6-1 имеется логическая 1, а в кодах с

6-2 и с 6-3 логический О. Установка триггера 22 в состояние 2

5 ПРОИСХОДИТ по фронту импульса кода с 6-1.

Контроль и восстановление информации может быть органиеован ли-бо последовательным поразрядным сравнением, либо параллельным поразрядным сравнением состояний контролируемых каналов. В первом слу- , чае количество связей между элементами схемы минимально/ вследствие че5 го получается высокая аппаратурная надежность, но это положительное качество достигается за снижения быстродействия схемы. Во втором , случае достигается более высокое быстродействие, однако за счет увеличения количества связей между элементами схемы снижается аппаратурная надежность. .

JT м-г

JTw

й(19-1

Ггт

Uft г

Jtfl$-SW-5-jlrjfrw-V

nt-i

.i

31-3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПЁРЁСЧЁТНОЁ УСТРОЙСТВО | 0 |

|

SU307523A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Резервированное пересчетное устройство | 1976 |

|

SU599359A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| , | |||

Авторы

Даты

1983-12-30—Публикация

1982-05-14—Подача