Изобретение относится к области вычислительной техники и может быть использовано о резервированных системах для приема двоичной информации, представленной последовательными кодами, с нескольких направлений.

Целью изобретения является расширение области применения и повышение живучести устройства.

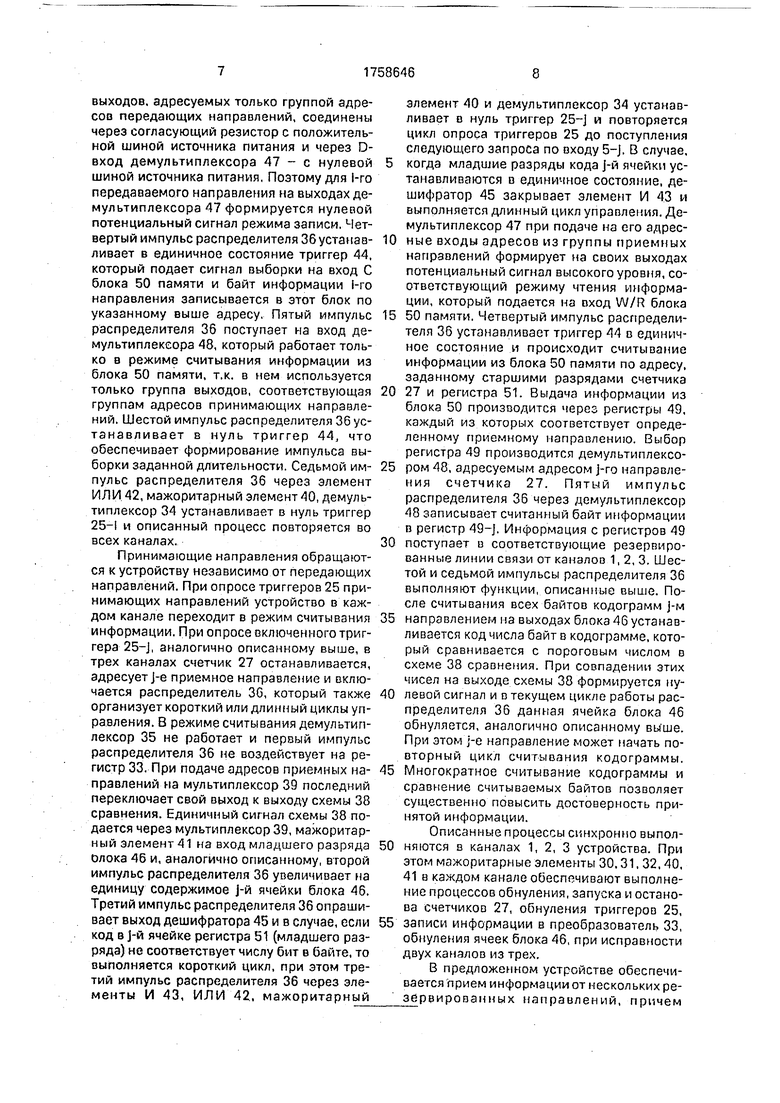

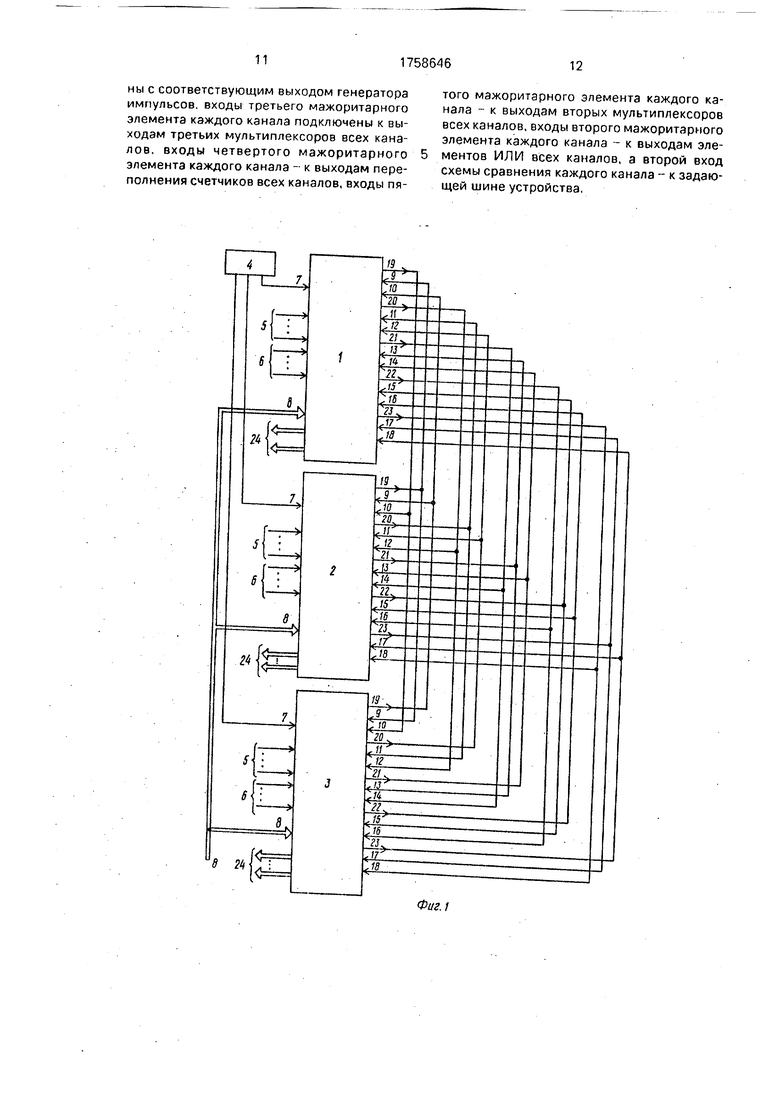

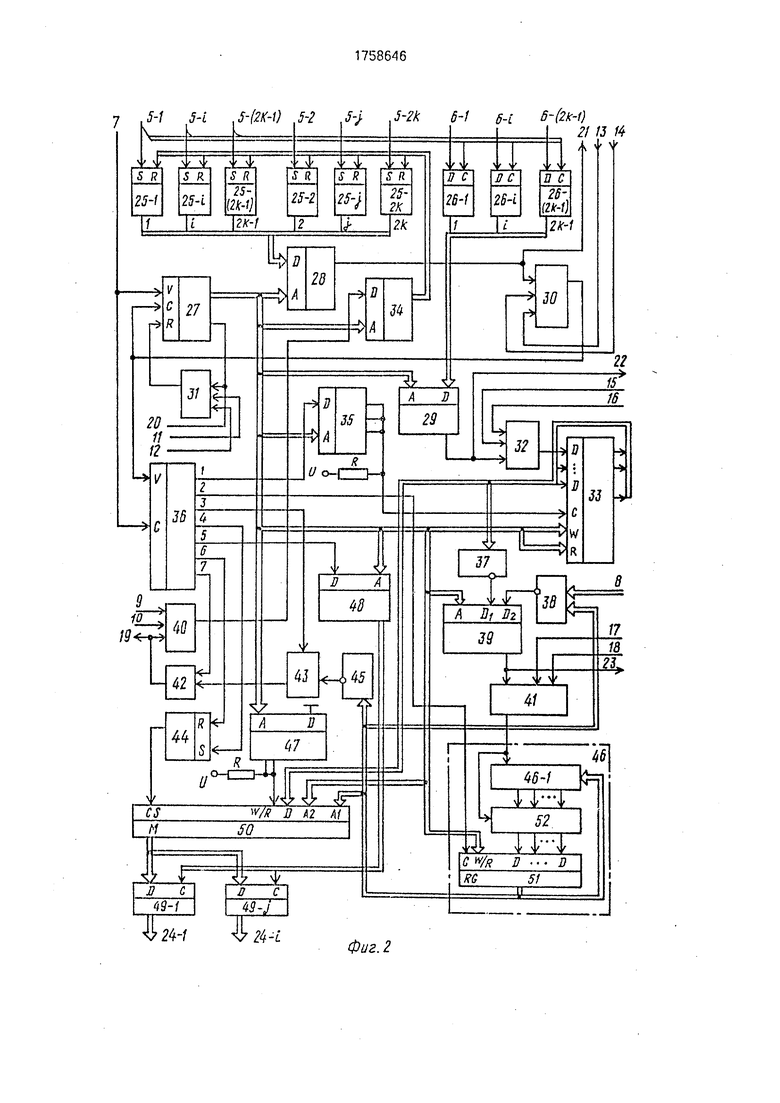

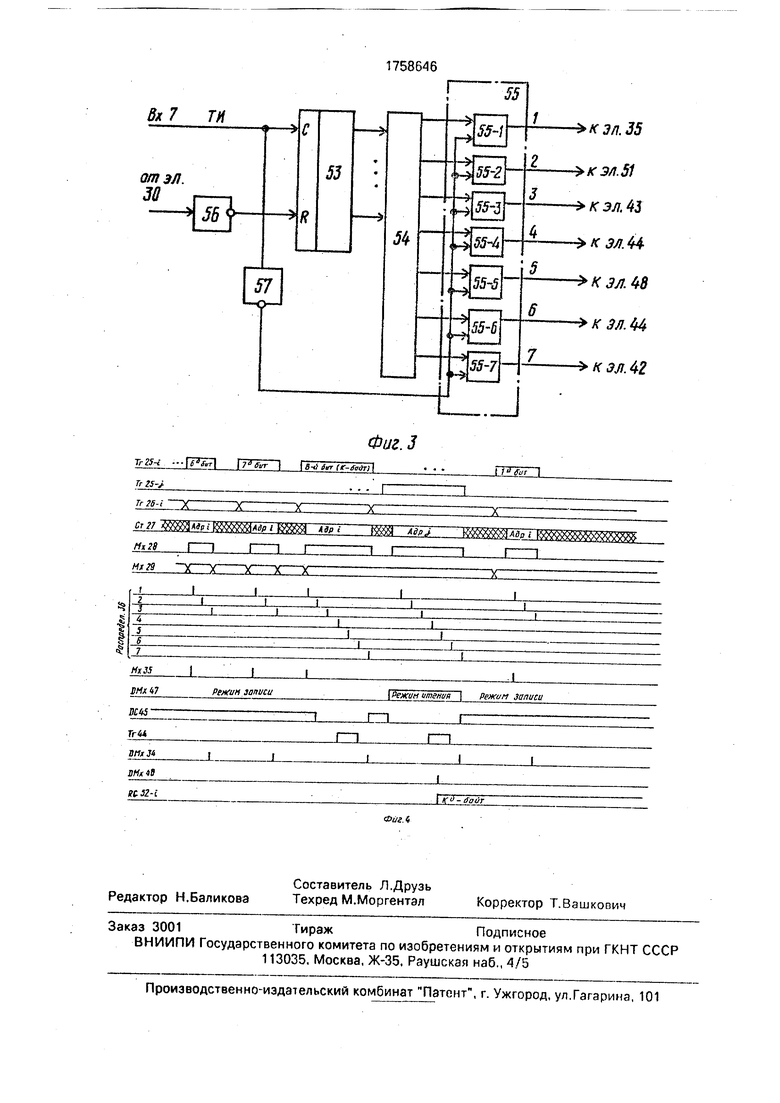

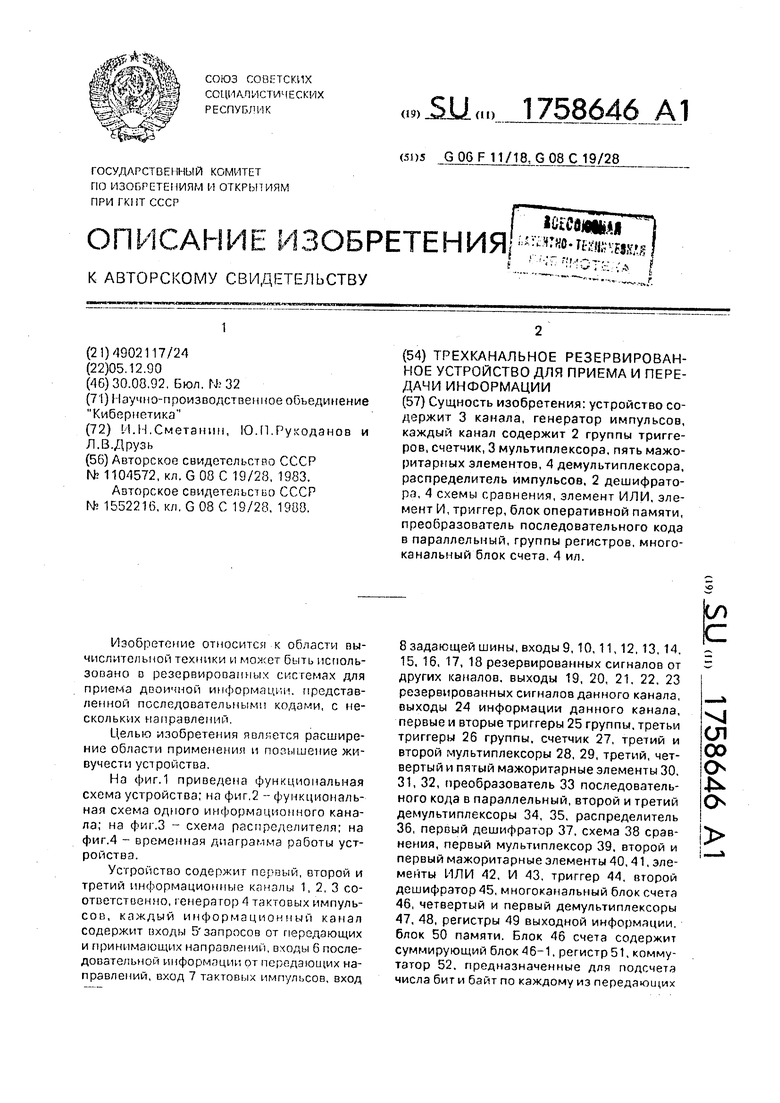

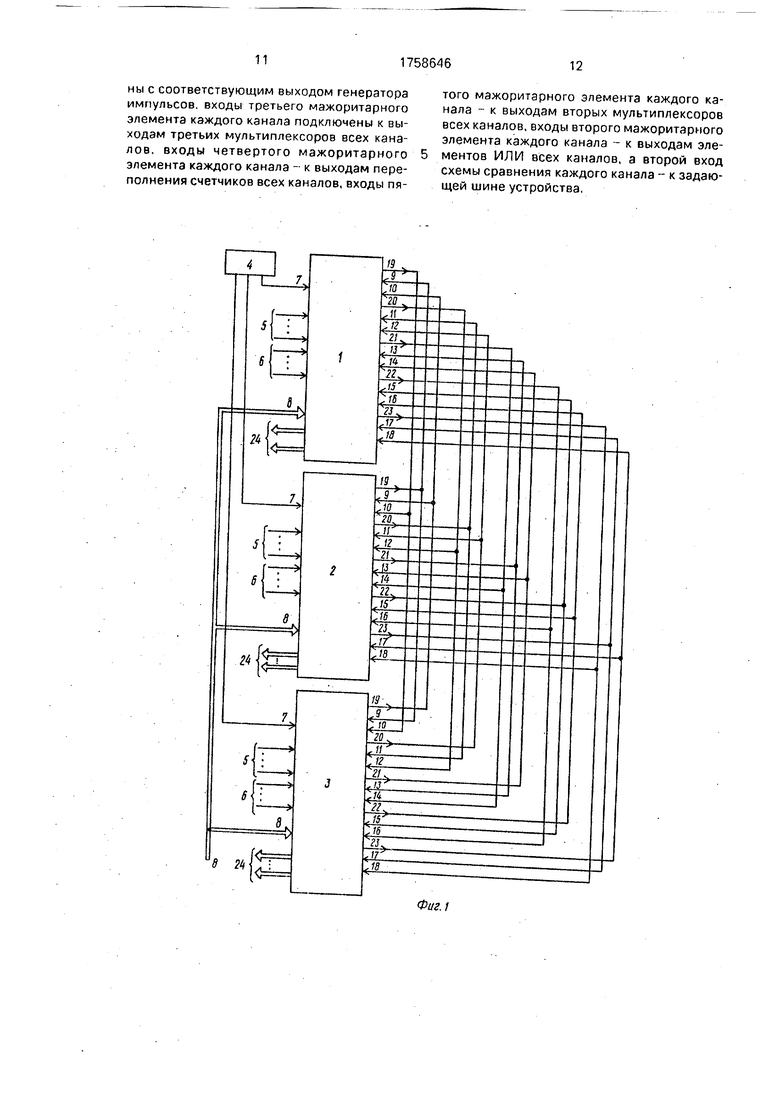

На фиг.1 приведена функциональная схема устройства; на фиг.2 -- функциональная схема одного информационного канала; на фиг.З - схема распределителя; на фиг.4 - временная диаграмма работы устройства.

Устройство содержит первый, второй и третий информационные каналы 1, 2, 3 соответственно, leneparop 4 тактовых импульсов, каждый информационный канал содержит входы 5 запросов от передающих и принимающих направлении, входы 6 последовательной информации от передающих направлений, вход 7 тактовых импульсов, вход

8 задающей шины, входы 9,10,11,12,13, 14. 15, 16, 17, 18 резервированных сигналов от других каналов, выходы 19, 20, 21, 22. 23 резервированных сигналов данного канала, выходы 24 информации данного канала, первые и вторые триггеры 25 группы, третьи триггеры 26 группы, счетчик 27, третий и второй мультиплексоры 28, 29, третий, четвертый и пятый мажоритарные элементы 30. 31, 32, преобразователь 33 последовательного кода в параллельный, второй и третий демультиплексоры 34, 35. распределитель 36, первый дешифратор 37. схема 38 сравнения, первый мультиплексор 39, второй и первый мажоритарные элементы 40,41, элементы ИЛИ 42, И 43, триггер 44, второй дешифратор 45, многоканальный блок счета

46,четвертый и первый демультиплексоры

47,48, регистры 49 выходной информации, блок 50 памяти. Блок 46 счета содержит суммирующий блок 46-1. регистр 51, коммутатор 52, предназначенные для подсчета числа бит и байт по каждому из передающих

сл

С

(Я 00 О 4 О

и принимающих направлений. Распределитель 36 (фиг.З) содержит счетчик 53, дешифратор 54, коммутатор 55. элементы НЕ 56, 57. Генератор А выполнен в виде резервированного генератора. Блоки и элементы устройства выполнены на микросхемах серий 564, 541, Преобразователь 33 выполнен на групповом регистре 564 ИР11 накопления последовательных бит и преобразования их в параллельные байты по каждому из передающих направлений, адреса направлений подаются на входы W записи и входы R считывания, управление записью бит (байт) в регистр производится сигналом по входу С. Регистры 49 предназначены для хранения считываемой из блока 50 памяти параллельной информации каждого направления.

Устройство работает следующим образом. Направления, обслуживаемые каналами 1, 2. 3 выставляют требования на прием или выдачу в эти каналы информации по входам 5 каналов, причем одноименные направления - синхронно в каналы 1, 2, 3. Передающие направления по нечетным входам 5 устанавливают в единичное состояние соответствующие им нечетные триггеры 25-1, 25-325-(2k-1), приемные

направления по четным входам 5 - четные

триггеры 25-2, 25-425-2R. Информация

от направлений в каналы в последовательных кодах подается по входам 6 на D-триг- геры 26, Информация поступает в каналы 1, 2, 3 от одноименных направлений синхронно в виде кодограмм, число байт в которых определено заранее и задается по входам 8 каналов 1, 2, 3. Начало кодограммы определяется специальным признаком - маркером. Передающие и принимающие направления и соответствующие им нечетные и четные триггеры 25 описываются группами передающих и принимающих адресов, которые отличаются значениями младшего разряда в коде адреса. При взаимодействии с направлениями устройство работает в режиме накопления и записи информации от передающих направлений и в режиме считывания информации соответствующими принимающими направлениями.

В исходном положении счетчик 27, триггеры 25, 26, преобразователь 33, регистры 49, 51, установлены в нуль (цепи начальной установки на схеме не показаны). При отсутствии сигналов на выходах мультиплексоров 28 каналов 1, 2, 3 отсутствуют сигналы на входах мажоритарных элементов 30 этих каналов. В каждом канале нулевой сигнал с выхода мажоритарного элемента 30 подается на управляющий вход счетчика 27 и разрешает счет тактовых импульсов, а через элемент НЕ 56 удерживает в нулевое состоянии счетчик 53 распределителя 36. Генера- тор4 импульсовформируеттри синхронные последовательности тактовых импульсов, которые через входы 7 подаются на тактовые входы счетчиков 27 каждого канала. В каждом канале счетчик 27- через мультиплексоры 28, 29 опрашивает выходы триггеров 25,26, суммарное время опроса которых с учетом времени обработки требований на0 правлений при записи или считывании информации (время цикла распределителя 36) меньше длительности периода между требованиями, которые выставляют направления по входам 5, что исключает воз5 можность потери информации, В режиме накопления и записи информации передающее i-e направление устанавливает, например по входу 5-I в единичное состояние триггер 25-i и одновременно подает бит ин0 формации на D-вход триггера 26-i и устанавливает его в соответствии со значением бита - в единичное или нулевое состояние - по фронту сигнала с входа 5-I. Описанные включения происходят синхронно в каналах

5 1,2,3. В каждом канале при опросе триггера 25 - на выходе мультиплексора 28 формируется единичный сигнал, который запрещает счет импульсов в счетчике 27 и снимает сигнал сброса со счегчика, 53 распределителя

0 36. На выходах счетчика 27 устанавливается адрес данного передающего направления. Выход триггера 26-I через мультиплексор 29 подключается к выходу мажоритарного элемента 32 и через выход 22 - к входам 15, 16

5 мажоритарных элементов 32 других каналов. При исправной работе каналов выход мультиплексора 29 через мажоритарный элемент 32 подключается к информационному входу преобразователя 33 кодов. По0 еле снятия в распределителе каждого канала сигнала сброса со счегчика 53 последний включается п режим счета тактовых импульсов генератора 4. Состояние счетчика 53 декодируется дешифратором 54, сигналы

5 которого стробируютсл через коммутатор 55 инверсными тактовыми импульсами с элемента НЕ 57. Распределитель 36 формирует цикл распределенных импульсных сигналов. В зависимости оттого, накоплен или не

0 накоплен байт информации по данному направлению, распределитель 36 выполняет длинный или короткий цикл управления. В рассматриваемом случае, пока байт информации не накоплен, выполняется короткий

5 цикл из трех сигналов. Первый импульс распределителя 36 подается на демультиплек- сор 35, группа выходов которого, соответствующая адресам передающих направлений, подключена через согласующий резистор к шине источника питания. Поэтому для адреса 1-го направлений на выходах демультиплексора 35 формируется импульс, который обеспечивает запись первого бита информации в ячейку преобразователя 33, адресуемую по входу счетчиком 27. Второй импульс распределителя 36 подается на тактовый вход многоканального блока 46 счета, который определяет число бит каждого направления. Подсчет числа бит и байт, принятых от передающего направления, производится следующим образом. До момента принятия маркера кодограммы на инверсном выходе дешифратора 37 установлен единичный сигнал. Для группы адресов передающих направлений, задан- ных счетчиком 27, мультиплексор 39 подключает выход дешифратора 37 к входу мажоритарного элемента 39 и через выход 23 к входам 17,18 мажоритарных элементов 39 других каналов. При исправной работе каналов сигнал дешифратора 37 через мультиплексор 39, мажоритарный элсмент41 поступает в блок 46 на вход младшего разряда суммирующего блока 46-1 и открывает коммутатор 52. Блок 46-1 прибавляет единицу к числу, накапливаемому для данного направления в соответствующий ячейке регистра 51. которое подается на входы старших разрядов суммирующего блока 46-1. Сумма с выходов блока 46-1 срез коммутатор 52 подается на информационные входы регистра 51 и фиксируется в ячейке по адресу i. Импульс записи подается на ОБХОД регистра 51 с распределителя 35. При подаче ад- оеса счетчика 27 на R-входы регистра 51 указанная сумма считывается из данной ячейки и снова поступает нл входы суммирующего блока 46-1 для суммирования с единицей в следующем цикле и т д. Запись новой суммы в данную ячейку регистра 51 производится в следующем цикле работы распределителя 36, который включается при поступлении следующих бит информации данного направления. Управление мультиплексором 39 от 27 осуще- ствляется таким образом, что в зоне адресов передающих направлений вход мультиплексора 39 подключается к выходу дешифратора 37, а в зоне адресов принимаемых каналов-к выходу схемы 38 сравнения. который определяет длину считываемой кодограммы. После накопления бит маркера в преобразователе 33 на выходе дешифратора 37 устанавливается нулевой сигнал. При этом закрывается коммутатор 52. через мн- формациоиные входы регистра 51 о ячейку, адресуемую счетчиком 27, записывается нулевое число, т.е. происходит обнуление ячейки, хранящей число бит данного направления. Третий импульс распределителя

36 через элементы И 43, ИЛИ 42 поступает, на мажоритарный элемент 40 и через выход 19 данного канала на входы 9, 10 мажоритарного элемента 40 даух других каналов. При исправной работе каналов импульс с выхода элемента ИЛИ 42 через мажоритарный элемент 40, демультиплексор 3-4, адресуемый счетчиком 27, поступает на вход сброса в нуль триггера 25-I и устанавливает его в нулевое состояние. При этом, снимается сигнал с выхода мультиплексора 28, распределитель 36 снова устанавливается в нулевое состояние, а счетчик 27 включается в режим счета тактовых импульсов и продолжает опрос триггеров 25, 26 для приема информации с других направлений. После опроса всех триггеров 25, 26 и заполнения счетчика 27 сигнал с выхода его старшего разряда поступает на вход мажоритарного элемента 31 и через выход 20 на выходы 11, 12 мажоритарных элементов 31 других каналов. При исправной работе каналов на выходах мажоритарных элементов 31 формируются импульсные сигналы, синхронно устанавливающие счетчики 27 в нулевое положение. Таким образом, обеспечивается синхронизация работы С етчиков 27 в каналах 1, 2, 3. Аналогично обслуживаются запросы других направлений. Накопление бит данного направления в соответствующей ячейке преобразователя 33, адресуемой счетчиком 27, обеспечивается за счет подачи кодов с выходов преобразователя 33 на группу его информационных входов, сдвинутых на один разряд. При этом, каждый последующий бит сдвигает предыдущий бит по разрядам этой ячейки до накопления в ней байта информации с данного направления. После накопления байта информации в ячейке преобразователя 3 для данного направления на выходе дешифратора 45 байтов устанавливается нулевой сигнал, который закрывает элемент И 43. В этом случае распределитель 36 выполняет длинный цикл управления из семи импульсных сигналов. Причем третий импульс распределителя 36 не устанавливает в нуль триггер 25-i. Так как счетчик 27 в данном цикле адресует i-e направление, на выходах преобразователя 33 сформирован параллельный код принятого байта i-ro направления, который подается на информационные входы блока 50 памяти. На адресные входы блока 50 памяти подается адресная часть с выходов старших разрядов счетчика 27 (номер направления) и адресная часть с выходов старших разрядов блока 46 (число байт, принятых с этого направления). Режим запись/чтение на блок 50 задается демультиплексором 47, в котором группа

выходов, адресуемых только группой адресов передающих направлений, соединены через согласующий резистор с положительной шиной источника питания и через D- вход демультиплексора 47 - с нулевой шиной источника питания, Поэтому для 1-го передаваемого направления на выходах демультиплексора 47 формируется нулевой потенциальный сигнал режима записи, Четвертый импульс распределителя 36 устанавливает в единичное состояние триггер 44, который подает сигнал выборки на вход С блока 50 памяти и байт информации i-ro направления записывается в этот блок по указанному выше адресу. Пятый импульс распределителя 36 поступает на вход де- мультиплекеора 48, который работает только в режиме считывания информации из блока 50 памяти, т.к. в нем используется только группа выходов, соответствующая группам адресов принимающих направлений. Шестой импульс распределителя 36 ус- танавливает в нуль триггер 44, что обеспечивает формирование импульса выборки заданной длительности. Седьмой импульс распределителя 36 через элемент ИЛИ 42, мажоритарный элемент 40, демуль- типлексор 34 устанавливает в нуль триггер 25-1 и описанный процесс повторяется во всех каналах.

Принимающие направления обращаются к устройству независимо от передающих направлений. При опросе триггеров 25 принимающих направлений устройство в каждом канале переходит в режим считывания информации. При опросе о ключе ни о го триггера 25-J, аналогично описанному выше, в трех каналах счетчик 27 останавливается, адресует j-e приемное направление и включается распределитель 30, который также организует короткий или длинный циклы управления. В режиме считывания демультип- лексор 35 не работает и первый импульс распределителя 36 не воздействует на регистр 33. При подаче адресов приемных направлений на мультиплексор 39 последний переключает свой выход к выходу схемы 38 сравнения. Единичный сигнал схемы 38 подается через мультиплексор 39, мажоритарный элемент 41 на вход младшего разряда олока 46 и, аналогично описанному, второй импульс распределителя 36 увеличивает на единицу содержимое j-й ячейки блока 46. Третий импульс распределителя 36 опрашивает выход дешифратора 45 и в случае, если код в j-й ячейке регистра 51 (младшего разряда) не соответствует числу бит в байте, то выполняется короткий цикл, при этом третий импульс распределителя 36 через элементы И 43, ИЛИ 42, мажоритарный

элемент 40 и демультиплексор 34 устанавливает в нуль триггер 25-J и повторяется цикл опроса триггеров 25 до поступления следующего запроса по входу 5-J. В случае,

когда младшие разряды кода j-й ячейки устанавливаются в единичное состояние, дешифратор 45 закрывает элемент И 43 и выполняется длинный цикл управления. Демультиплексор 47 при подаче на его адрес0 ные входы адресов из группы приемных направлений формирует на своих выходах потенциальный сигнал высокого уровня, соответствующий режиму чтения информации, который подается на вход W/R блока

5 50 памяти. Четвертый импульс распределителя 36 устанавливает триггер 44 в единичное состояние и происходит считывание информации из блока 50 памяти по адресу, заданному старшими разрядами счетчика

0 27 и регистра 51. Выдача информации из блока 50 производится через регистры 49, каждый из которых соответствует определенному приемному направлению. Выбор регистра 49 производится демультиплексо5 ром 48, адресуемым адресом j-ro направления счетчика 27. Пятый импульс распределителя 36 через демультиплексор 48 записывает считанный байт информации в регистр 49-J. Информация с регистров 49

0 поступает в соответствующие резервированные линии связи от каналов 1, 2, 3. Шестой и седьмой импульсы распределителя 36 выполняют функции, описанные выше. После считывания всех байтов кодограмм j-м

5 направлением на выходах блока 46 устанавливается код числа байт в кодограмме, который сравнивается с пороговым числом в схеме 38 сравнения. При совпадении этих чисел на выходе схемы 38 формируется ну0 левой сигнал и в текущем цикле работы распределителя 36 данная ячейка блока 46 обнуляется, аналогично описанному вы ше. При этом j-e направление может начать повторный цикл считывания кодограммы.

5 Многократное считывание кодограммы и сравнение считываемых байтов позволяет существенно повысить достоверность принятой информации.

Описанные процессы синхронно выпол0 няются в каналах 1, 2, 3 устройства. При этом мажоритарные элементы 30.31, 32,40, 41 в каждом канале обеспечивают выполнение процессов обнуления, запуска и останова счетчиков 27, обнуления триггеров 25,

5 записи информации в преобразователь 33, обнуления ячеек блока 46, при исправности двух каналов из трех.

В предложенном устройстве обеспечивается прием информации от нескольких резервированных направлений, причем

чередование режимов приема и выдачи информации определяется последовательностью соответствующих требований от этих направления, что расширяет область применения устройства. В устройстве три идентичных канала работают в горячем резерве и при отказе некоторой части элементов в каналах с помощью мажоритарных элементов обеспечивается дальнейшее функционирование каналов, что повышает живучесть устройства.

Формула изобретения Трехканальное резервированное устройство для приема и передачи информации, содержащее генератор импульсов и в каждом канале - первый и второй мажоритарные элементы, с первого по третий мультиплексоры, преобразователь последовательного кода в параллельный, схему сравнения, счетчик, два дешифратора, триггер, элемент И, элемент ИЛИ, первый де- мультиплексор и группу регистров, выходы которых являются группой информационных выходов данного канала, причем в каждом канале группа выходов счетчика соединена с группой адресных входов первого мультиплексора и с группой адресных входов первого демультиплексора, группа выходов которого подключена к синхровхо- ду соответствующего регистра группы, выход первого мультиплексора соединен с первым входом первого мажоритарного элемента, второй и третий входы которого подключены к выходам первых мультиплексоров двух других каналов соответственно, отличающееся тем, что, с целью расширения области применения устройства и повышения его живучести, преобразо- ватель последовательного кода в параллельный каждого канала выполнен многоканальным, а в каждый канал устройства введены с первой по третью группы триггеров, распределитель импульсов, с второго по четвертый демультиплексоры, блок оперативной памяти, с третьего по пятый мажоритарные элементы и многоканальный блок счета, счетный вход которого подключен к выходу первого мажоритарного элемента, а группа выходов - к первой группе адресных входов блока оперативной памяти, к группе входов второго дешифратора и к первой группе входов схемы сравнения данного канала, причем в каждом канале первая группа адресных входов соединена с установочными входами триггеров первой группы и с синхровходами триггеров третьей группы, вторая группа адресных входов - с установочными входами триггеров второй группы, а группа информационных входов - с информационными входами триггеров третьей группы, подключенных выходами к группе информационных входов второго мультиплексора, группы выходов

триггеров первой и второй групп соединены с группой информационных входов третьего мультиплексора, а входы сброса - с соответствующим выходом группы выходов второго демультиплексора, подсоединенного груп0 пой адресных входов к группе выходов счетчика, к группам адресных входов второго и третьего мультиплексоров, преобразователя последовательного кода в параллельный, третьего и четвертого демультиплексоров и

5 многоканального блока счета и к второй группе адресных входов блока оперативной памяти, выход третьего мажоритарного элемента соединен со счетным входом счетчика и с входом блокировки распределителя им0 пульсов, выход четвертого мажоритарного элемента соединен с входом сброса счетчика, а выход второго и пятого мажоритарных элементов подключены соответственно к информационному входу второго демуль5 типлексора и к младшему разряду группы информационных входов преобразователя последовательного кода в параллельный, соединенного синхровходом с выходом третьего демультиплексора, а группой выхо0 дов - со старшими разрядами собственной группы информационных входов и с группами информационных входов блока оперативной памяти и первого дешифратора, связанного выходом с первым информаци5 онным входом первого мультиплексора, второй информационный вход которого подключен к выходу схемы сравнения, выход второго дешифратора соединен с первым входом элемента И, подключенного

0 выходом к первому входу элемента ИЛИ. информационный вход четвертого демультиплексора соединен с нулевой шиной устройства, а выход - с входом управления записью-считывания блока оперативной па5 мяти, подсоединенного синхровходом к выходу триггера, а группой выходов - к группам информационных входов регистров группы, первый выход распределителя импульсов подключен к информационному

0 входу третьего демультиплексора, второй выход - к синхровходу многоканального блока счета, третий выход - к второму входу элемента И, четвертый и пятый выходы - к установочному входу и входу сброса

5 соответственно триггера,.шестой выход - к информационному входу первого демультиплексора, а седьмой выход - к второму входу элемента ИЛИ, кроме того, в каждом канале вход блокировки счетчика и синх- ровхол, распределителя импульсов соединены с соответствующим выходом генератора импульсов, входы третьего мажоритарного элемента каждого канала подключены к выходам третьих мультиплексоров всех каналов, входы четвертого мажоритарного элемента каждого канала - к выходам переполнения счетчиков всех каналов, входы пятого мажоритарного элемента каждого канала - к выходам вторых мультиплексоров всех каналов, входы второго мажоритарного элемента каждого канала - к выходам элементов ИЛИ всех каналов, а второй вход схемы сравнения каждого канала - к задающей шине устройства.

N Ґ

s

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для индикации | 1990 |

|

SU1795511A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Многоканальный преобразователь последовательного кода в параллельный | 1990 |

|

SU1751859A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Устройство для сопряжения абонента с каналом связи | 1987 |

|

SU1499358A1 |

| Устройство для управления ленточным перфоратором | 1990 |

|

SU1837333A1 |

| Устройство для приема и обработки информации | 1989 |

|

SU1603418A1 |

| Устройство для индикации | 1989 |

|

SU1686474A1 |

| Устройство для ввода и вывода информации | 1990 |

|

SU1709295A1 |

| Многоканальное устройство для сравнения кодов | 1990 |

|

SU1795446A1 |

Сущность изобретения: устройство содержит 3 канала, генератор импульсов, каждый канал содержит 2 группы триггеров, счетчик, 3 мультиплексора, пять мажоритарных элементов, 4 демультиплексора, распределитель импульсов, 2 дешифратора, 4 схемы сравнения, элемент ИЛИ, элемент И, триггер, блок оперативной памяти, преобразователь последовательного кода в параллельный, группы регистров, многоканальный блок счета, 4 ил.

H

в

С:

г°

t

J Jt со

O5

.с o

Tr25-i | 7 far 1 | в-й itr dC-fmfrl}

Tris-i-xcr г $SSftMri №$&$MpT.

Kip i

Hit

x x x x у

HxM

tMxtf

Режин записи

VW

BllxJt

J.

gt-tt-i

Фиг.З

2C

MPJ Ґ№Щ&мя1 УШШШЬУЩь

JL

±

Режим итгнс/я Режин записи

X

L

i t(u-ffauT

| Устройство для приема информации | 1983 |

|

SU1104572A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для приема информации | 1988 |

|

SU1552216A1 |

Авторы

Даты

1992-08-30—Публикация

1990-12-05—Подача