113359822

Изобретение относится к ньмисли- 7 - 9 - 2,5 , так как они реализу- телькой технике и может быть испогп.- ют соответстненио предикаты . зовано при построении арифметических устройств.,

Цель изобретения - увеличение быстродействия сумматора-вычитателя.

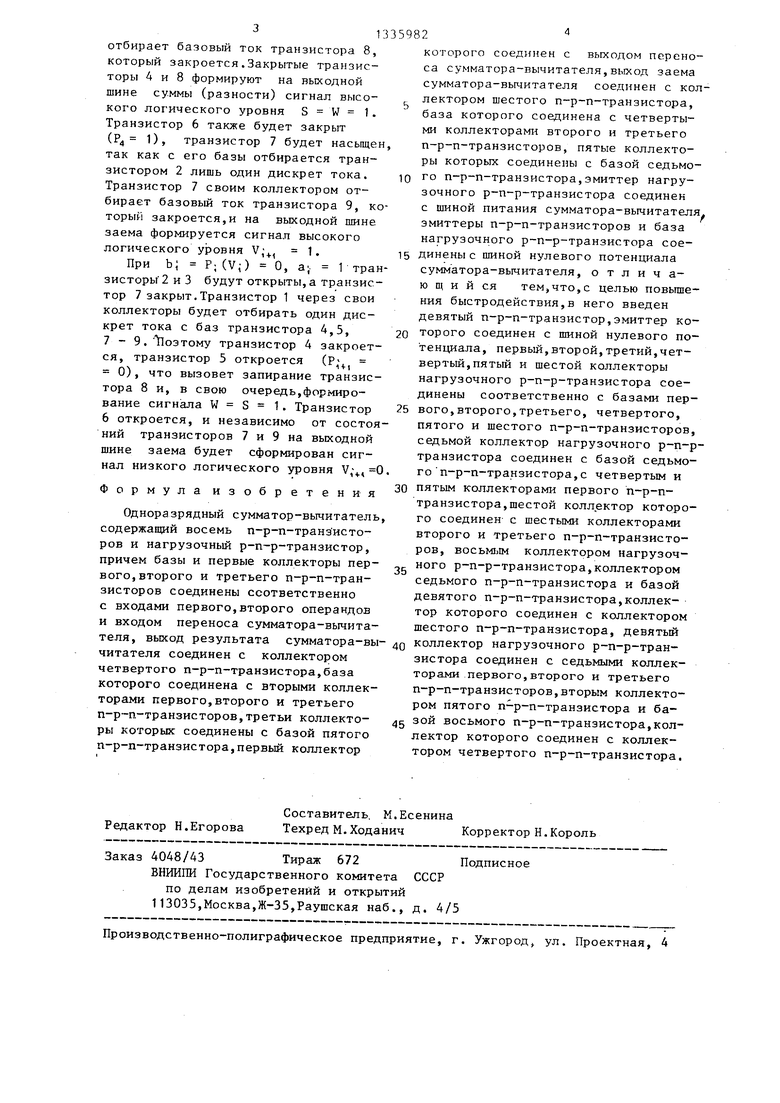

На чертеже представлена функциональная схема одноразрядного сумматора-вычитателя.10

Одноразрядный сумматор-вычитатель содержит девять п-р-п-транзисторов 1-9, нагрузочный р-п-р-транзистор 10, шину 11 питания,входы 12 и 13 первого и второго операндов,вход 14 15 ному кванту (коэффициент передачи переноса,выход 15 суммы,выход 16 пе- по току транзисторов 1- 3 равен единице - токовые повторители). Следовательно,с баз транзисторов 4,5,8,9 будет отбираться три дискрета тока

Указанные соотношения токов задаются путем изменения геометрических размеров инжектирующих и базовых областей.

Устройство работает следующим образом.

Предположим,на вход устройства подается следующая комбинация входных сигналов: а; Ь; Р; 1.В этом случае транзисторы 1 - 3 открыты и их коллекторные токи равны одреноса,выход 17 заема.

Известно,что функции суммы,разности переноса и заема имеют следующий вид в булевой алгебре

W S а; Р;Ь; V а; Р,Ь; v V а; P;b; V а; P;b; ,

PU, a,-b; V а;Р; V Ь; , ,

Vj,, a;b; V a;V; v b;V;.

В арифметическом базисе указанные функции будут иметь вид:

20 (3 1) а так как их базовые токи меньше указанных значений,то эти транзисторы закроются.Закроются также транзисторы 6 (с его базы отбирается два дискрета тока) и 7 (с его ба- 25 зы отбирается четыре дискрета тока PC) Таким образом, все пороговые детекторы будут закрыты, т.е.

W S Р, (aj + Р; Ь; ь 1) - W S 1; Р ;„ 1; V;,, 1. - Р (а-, + р. + Ь; 2) + + Р; + Предположим,что а; Ь; 1; + Ь; 5 3); .30 P;(V;) 0. В этом случае транзисто Р,(а; + р.; Ь; 2); V ,, Р(Ь; + V; i 1) - Ру(2а; +

+ Ь; + V; i 3) + Р,, (а 1 + V; + b;i 3).

Как видно из последних соотношений, для реализации функций Р, ; P,j ; Р I Ру используются одни и те же аргументы по различным порогам (одни, и те же многоколлекторные тран35

ры 4 и 5 будут закрыты (так как с их баз отбирается два дискрета тока), т.е. Р;, 1. Запирание транзистора 5 не будет- влиять на состояние транзистора 8, который откроется так как с его базы отбирается 2 1 (его базовый ток равен 2,5 Ij,) . Отпирание транзистора 8 шунтирует выход транзистора 4 и на

зисторы для образования суммы).Это 40 выходной шине суммы (разности) пояпозволяет реализовать искомые функции с минимальными аппаратурными и временными затратами.Причем в базы транзисторов 1- 3 инжектируется

вится сигнал S W 0. С базы транзистора 6 будет отбираться один дискрет тока, поэтому он закроется (Р 1), транзистор 7 будет также

один квант тока (IQ) , а в базы тран- 45 Р ° базы отбирается ток, равный 3 1д (2 а,; + Ь,; ). Закрытый транзистор 7 не будет оказывать влияние на состояние транзистора 9, поэтому он откроется ,так

50 как с его базы отбирается ток,равный (а; + bj) двум дискретам.Открытый транзистор 9 приводит к появлению выходного сигнала заема V,, 0, т.е. при а; Ь; 1; Р; (V;) 0;

55 W S 0; Р,.„ 1, V;,, 0.

При а; P;(V;) 0; Ь; 1 транзистор 4 закроется, транзистор 5 будет насыщен (Р;, 0), открытый

зисторов 4-9, выполняющих функции пороговых детекторов, задаются токи, значения которых указаны в арифметическом представлении реализуемых функций и их предикатов: Р, ; Р, ; Р . Для определенности срабатывания пороговых детекторов токи берутся на 0,5 кванта меньше, чем это указано в рассматриваемых выражениях. В соответствии со сказанным в базу транзистора 4 из транзистора 10 инжектируется ток-, равный 0,5 1о (транзистор 4 реализует функцию Р, ), в базу транзисторов

транзистор 5 через свой коллектор

7 - 9 - 2,5 , так как они реализу- ют соответстненио предикаты .

ному кванту (коэффициент передачи по току транзисторов 1- 3 равен единице - токовые повторители). Следовательно,с баз транзисторов 4,5,8,9 будет отбираться три дискрета тока

Указанные соотношения токов задаются путем изменения геометрических размеров инжектирующих и базовых областей.

Устройство работает следующим образом.

Предположим,на вход устройства подается следующая комбинация входных сигналов: а; Ь; Р; 1.В этом случае транзисторы 1 - 3 открыты и их коллекторные токи равны одW S 1; Р ;„ 1; V;,, 1. Предположим,что а; Ь; 1; P;(V;) 0. В этом случае транзисто

ры 4 и 5 будут закрыты (так как с их баз отбирается два дискрета тока), т.е. Р;, 1. Запирание транзистора 5 не будет- влиять на состояние транзистора 8, который откроется так как с его базы отбирается 2 1 (его базовый ток равен 2,5 Ij,) . Отпирание транзистора 8 шунтирует выход транзистора 4 и на

вится сигнал S W 0. С базы транзистора 6 будет отбираться один дискрет тока, поэтому он закроется (Р 1), транзистор 7 будет также

Р ° базы отбирается ток, равный 3 1д (2 а,; + Ь,; ). Закрытый транзистор 7 не будет оказывать влияние на состояние транзистора 9, поэтому он откроется ,так

транзистор 5 через свой коллектор

313

отбирает базовый ток транзистора 8, который закроется.Закрытые транзисторы 4 и 8 формируют на выходной шине суммы (разности) сигнал высокого логического уровня S W 1. Транзистор 6 также будет закрыт (Р 1), транзистор 7 будет насыщен так как с его базы отбирается транзистором 2 лишь один дискрет тока. Транзистор 7 своим коллектором отбирает базовый ток транзистора 9, который закроется,и на выходной шине заема формируется сигнал высокого логического уровня V; 1.

При Ь; P;(Vj) о, а;. 1 транзисторы 2 и 3 будут открыты, а транзистор 7 закрыт.Транзистор 1 через свои коллекторы будет отбирать один дискрет тока с баз транзистора 4,5, 7-9. YlosTOMy транзистор 4 закроется, транзистор 5 откроется (Р,Ч| 0), что вызовет запирание транзистора 8 и, в свою очередь,формирование сигнала W S 1. Транзистор 6 откроется, и независимо от состояний транзисторов 7 и 9 на выходной шине заема будет сформирован сигнал низкого логического уровня V,-., 0

Формула изобретения

Одноразрядный сумматор-вычитатель содержащий восемь п-р-п-транз исто- ров и нагрузочный р-п-р-транзистор, причем базы и первые коллекторы первого, второго и третьего п-р-п-транзисторов соединены ссответственно с входами первого,второго операндов и входом переноса сумматора-вычита- теля, выход результата сумматора-вы читателя соединен с коллектором четвертого п-р-п-транзистора,база которого соединена с вторыми коллекторами первого,второго и третьего п-р п-транзисторов,третьи коллекторы которых соединены с базой пятого п-р-п-транзистора,первый коллектор

Редактор Н.Егорова

Составитель. М.Есенина

Техред М.Ходанич Корректор Н.Король

Заказ 4048/43 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035,Москва,Ж-35,Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

2

которого соединен с выходом переноса сумматора-вычитателя,выход заема сумматора-вычитателя соединен с коллектором шестого п-р-п-транзистора, база которого соединена с четвертыми коллекторами второго и третьего п-р-п-транзисторов, пятые коллекторы которых соединены с базой седьмого п-р-п-транзистора,эмиттер нагрузочного р-п-р-транзистора соединен с шиной питания сумматора-вычитателя. змиттеры п-р-п-транзисторов и база нагрузочного р-п-р-транзистора соединеныс шиной нулевого потенциала сумматора-вычитателя, о т л и ч а- ю щ и и ся тем,что,с целью повьше- ния быстродействия,в него введен девятый п-р-п-транзистор,эмиттер которого соединен с шиной нулевого потенциала, первый,второй,третий,четвертый, пятый и шестой коллекторы нагрузочного р-п-р-транзистора соединены соответственно с базами первого,второго,третьего, четвертого, пятого и шестого п-р-п-транзисторов, седьмой коллектор нагрузочного р-п-р- транзистора соединен с базой седьмого п-р-п-транзистора,с четвертым и

пятым коллекторами первого п-р-п- транзистора, шестой коллектор которого соединен с шестыми коллекторами второго и третьего п-р-п-транзисторов, BocbMijiM коллектором нагрузочного р-п-р-транзистора,коллектором седьмого п-р-п-транзистора и базой девятого п-р-п-транзистора,коллектор которого соединен с коллектором шестого п-р-п-транзистора, девятый

коллектор нагрузочного р-п-р-транзистора соединен с седьмыми коллекторами первого, второго и третьего п-р-п-транзисторов,вторым коллектором пятого п-р-п-транзистора и баЗОЙ восьмого п-р-п-транзистора,коллектор которого соединен с коллектором четвертого п-р-п-транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный сумматор-вычитатель | 1987 |

|

SU1424013A1 |

| Одноразрядный сумматор | 1988 |

|

SU1599854A1 |

| Схема контроля на четность И @ Л типа | 1985 |

|

SU1269253A1 |

| Интегральный четырехзначный D-триггер | 1986 |

|

SU1338012A1 |

| Схема контроля на четность И @ Л-типа | 1988 |

|

SU1525906A1 |

| Четырехуровневый сумматор-вычитатель | 1987 |

|

SU1422396A1 |

| Тактируемый @ -триггер в интегральной инжекционной логике | 1982 |

|

SU1051692A1 |

| Инжекционный сумматор-вычитатель | 1987 |

|

SU1471305A1 |

| Тактируемый JK-триггер И @ Л-типа | 1987 |

|

SU1422367A1 |

| Одноразрядный сумматор | 1982 |

|

SU1043641A2 |

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств. Цель изобретения - повышение быстродействия. Одноразрядный сумматор-вычитатель содержит девять п-р-п-транзисторов 1 - 9, нагрузочный р-п-р-транзистор 10,шину 11 питания,входы 12,13 первого и второго операндов,вход 14 переноса,выход 15 суммы,выход 16 переноса,выход 17 заема. Устройство выполняет операции суммирования и вычитания с прямыми кодами переменных,т.е. нет необходимости при смене выполнения операции производить инвертирование входных переменных.1 ил. с (Л С

Авторы

Даты

1987-09-07—Публикация

1986-04-14—Подача