(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Тактируемый @ -триггер @ -типа | 1985 |

|

SU1275738A1 |

| Интегральный четырехзначный D-триггер | 1986 |

|

SU1338012A1 |

| Двоичный делитель частоты @ типа | 1983 |

|

SU1112533A1 |

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1335982A1 |

| Тактируемый @ -триггер в интегральной инжекционной логике | 1982 |

|

SU1051692A1 |

| Преобразователь двоичного кода в код Грея | 1986 |

|

SU1444960A1 |

| Схема контроля на четность И @ Л типа | 1985 |

|

SU1269253A1 |

| Динамический логический элемент | 1979 |

|

SU822370A1 |

| Ячейка памяти | 1983 |

|

SU1132344A1 |

| Ячейка памяти | 1982 |

|

SU1140165A1 |

Изобретение относится к импульс- ной технике, а именно к устройствам с двумя устойчивыми состояниями. Цель изобретения - упрощение триггера. Тактируемый JK-триггер И Л-типа содержит семь транзисторов с инжекционным питанием. Работоспособность триггера обеспечивается подключением третьих дополнительных коллекторов первого и второго транзисторов соответственно в J- и К-входам, а также подачей в базу первого транзистора 1,5 дискретов тока, а в базы остальных транзисторов 1,0 дискрета тока. 2 ил.

4 го ю

ОО

а

; Изобретение относнтся к импульс- технике, а именно к устройствам 4 двумя устойчивыми состояниями.

Цель изобретения - упрощение триггера.

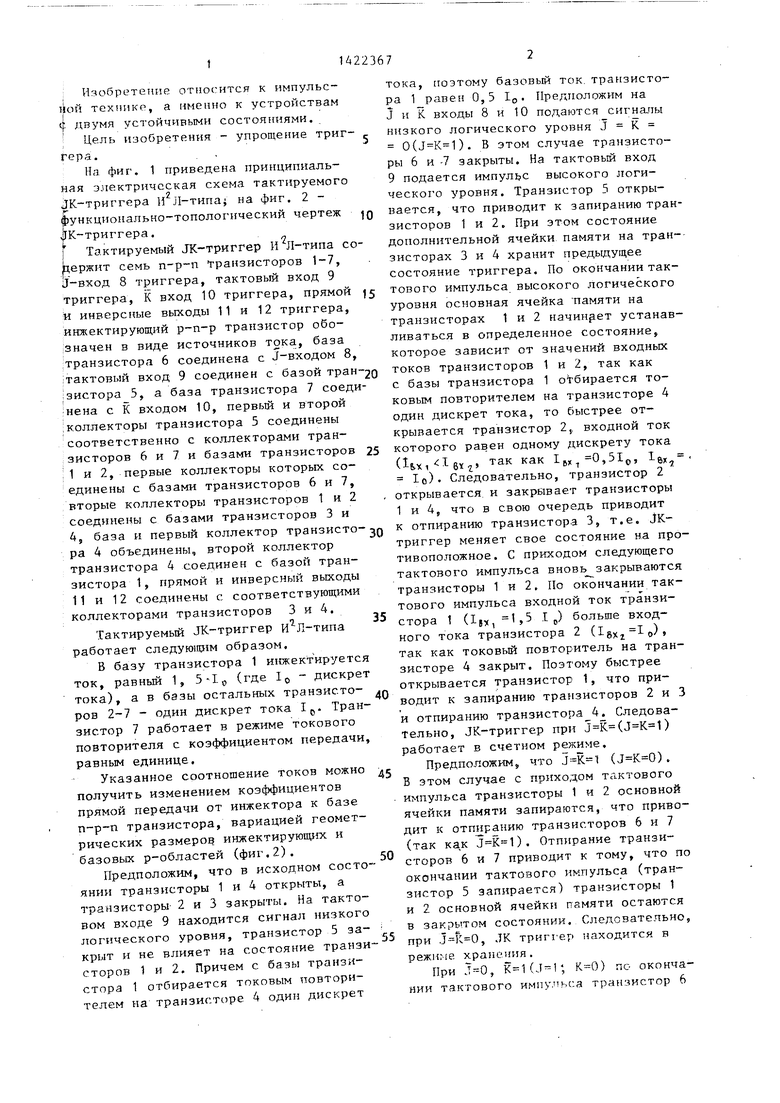

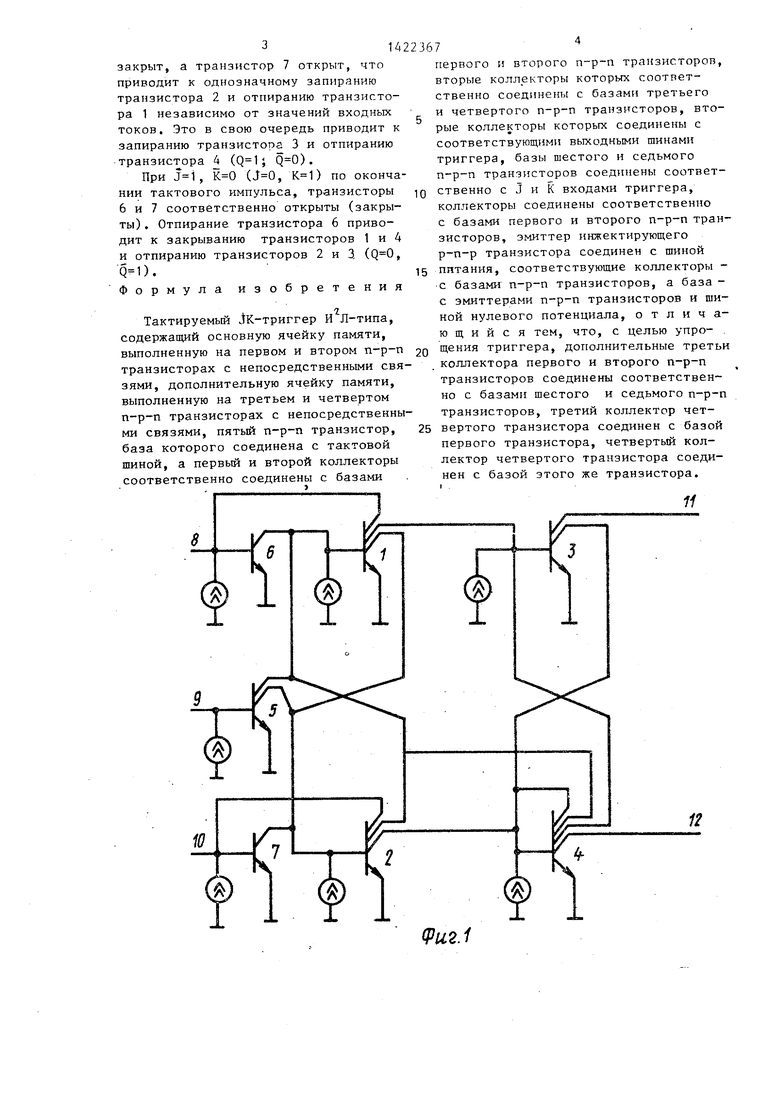

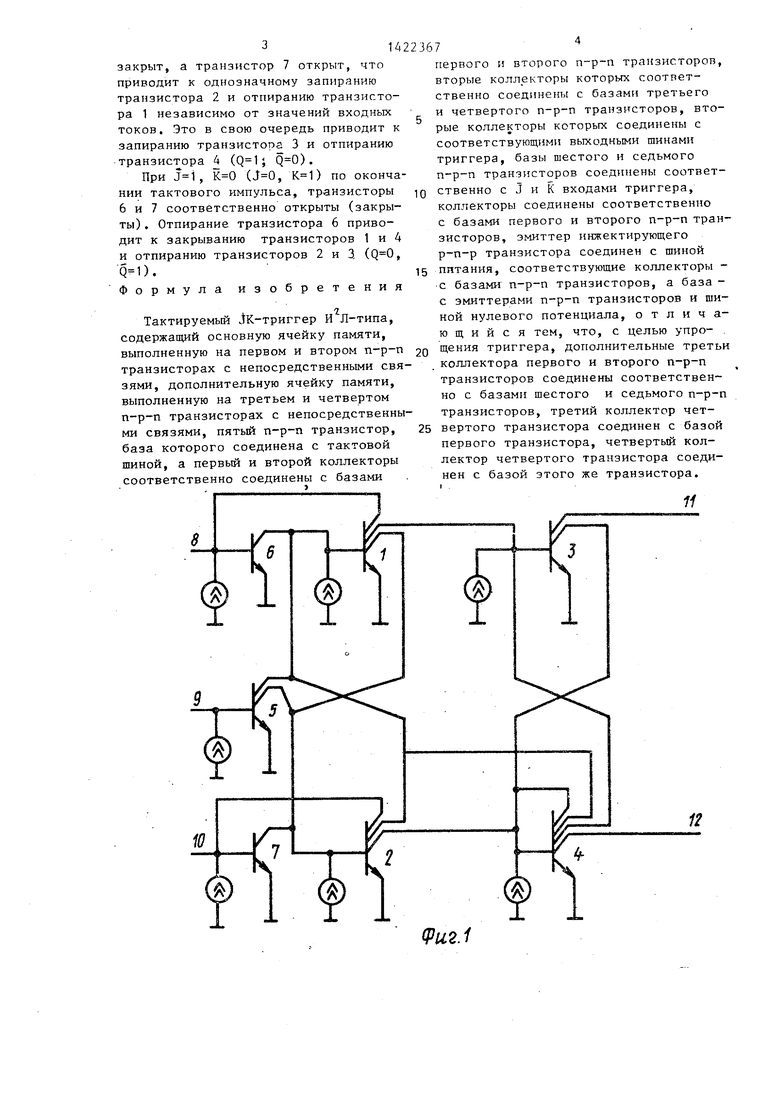

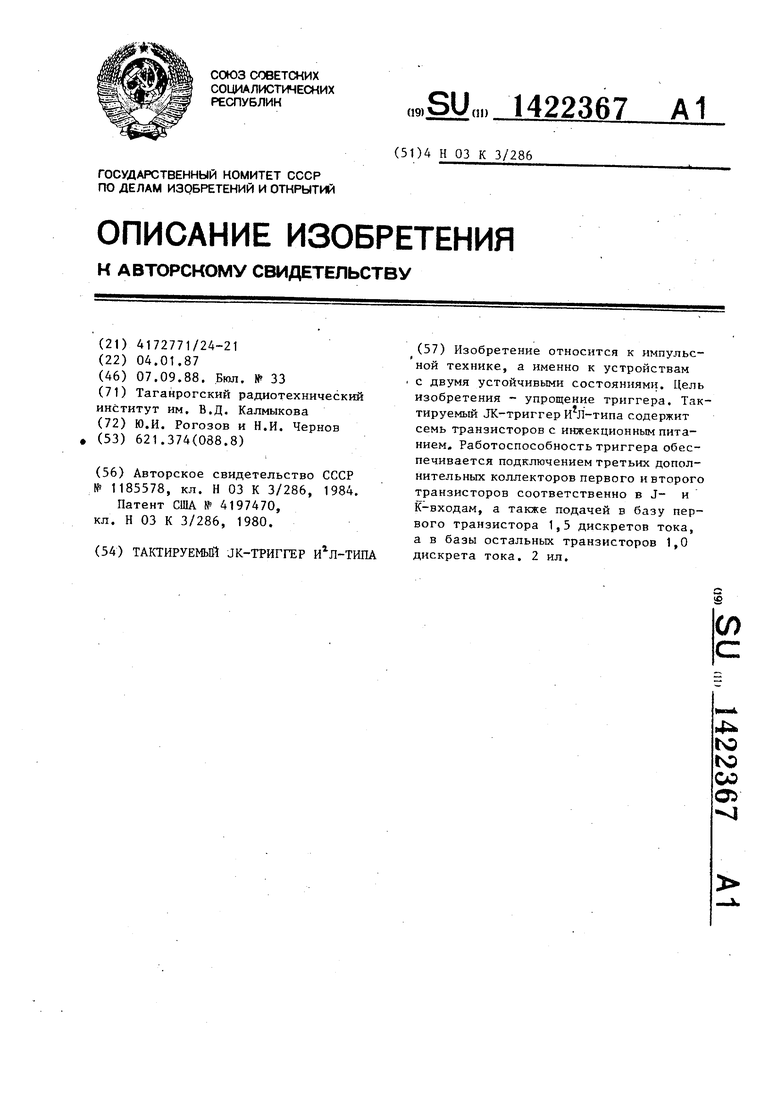

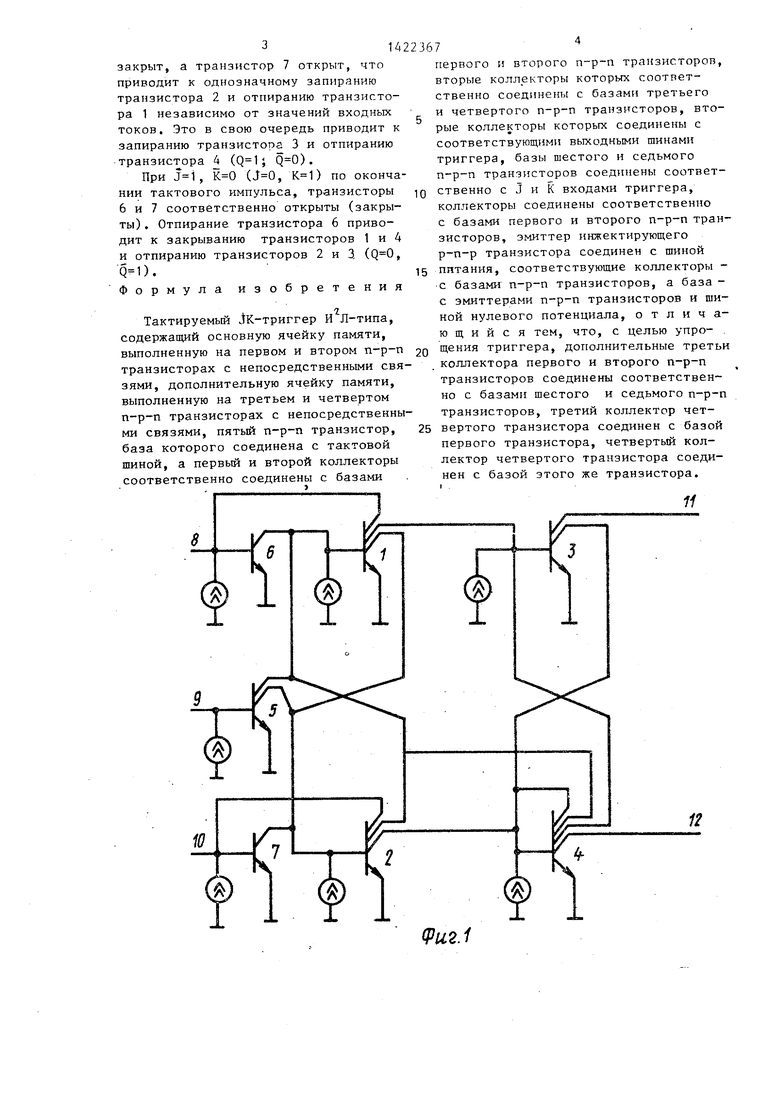

На фиг. 1 приведена принципиальная электрическая схема тактируемого jK-триггера И JI-типai на фиг. 2 - функционально-топологический чертеж

jJK-триггера.

t п

Тактируемый JK-триггер И Л-типа содержит семь п-р-п транзисторов 1-7, &-вход 8 триггера, тактовый вход 9 триггера, К вход 10 триггера, прямой и инверсные выходы 11 и 12 триггера, инжектирующий р-п-р транзистор обо- ;3начен в виде источников тока., база транзистора 6 соединена с J-входом 8, ;тактовый вход 9 соединен с базой тран ;зистора 5, а база транзистора 7 соеди нена с К входом 10, первый и второй :коллекторы транзистора 5 соединены соответственно с коллекторами транзисторов 6 и 7 и базами транзисторов :1 и 2, первые коллекторы которых соединены с базами транзисторов 6 и 7, вторые коллекторы транзисторов 1 и 2 соединены с базами транзисторов 3 и 4, база и первый коллектор транзистоpa 4 объединены, второй коллектор транзистора 4 соединен с базой транзистора 1, прямой и инверсный выходы 11 и 12 соединены с соответствующими коллекторами транзисторов 3 и 4.

Тактируемый JK-триггер и Л-типа работает следующим образом.

В базу транзистора 1 инжект ируется ток, равньй 1, 5-1,, (где 1с, дискрет тока), а в базы остальных транзисто- ров 2-7 - один дискрет тока I. Транзистор 7 работает в режиме токового повторителя с коэффициентом передачи, равным единице.

Указанное соотношение токов можно получить изменением коэффициентов прямой передачи от инжектора к базе п-р-п транзистора, вариацией геометрических размеров инжектирующих и базовых р-областей (фиг,2).

Предположим, что в исходном состоянии транзисторы 1 и 4 открыты, а транзисторы- 2 и 3 закрыты. На тактовом входе 9 находится сигнал низкого

логического уровня, транзистор 5 за- крыт и не влияет на состояние транзисторов 1 и 2. Причем с базы транзистора 1 отбирается токовым повторителем на транзисторе 4 один дискрет

д

д 5 Q

Q

п

5

тока, поэтому базовый ток. транзистора 1 равен 0,5 Го- Предположим на J и К входы 8 и 10 подаются сигналы низкого логического уровня vT К 0(). В этом случае транзисторы 6 и -7 закрыты. На тактовый вход 9 подается импул1 с высокого логического уровня. Транзистор 5 открывается, что приводит к запиранию транзисторов 1 и 2. При этом состояние дополнительной ячейки памяти на тран-- зисторах 3 и 4 хранит предыдущее состояние триггера. По окончании тактового импульса высокого логического уровня основная ячейка памяти на транзисторах 1 и 2 начинает устанавливаться в определенное состояние, которое зависит от значений входных токов транзисторов 1 и 2, так как с базы транзистора 1 отбирается токовым повторителем на транзисторе 4 один дискрет тока, то быстрее открывается транзистор 2,, входной ток которого равен одному дискрету тока

(1ьх1 1бкг ,51р, 1вх, TO) Следовательно, транзистор 2 открывается и закрывает транзисторы 1 и 4, что в свою очередь приводит к отпиранию транзистора 3, т.е. JK- триггер меняет свое состояние на противоположное. С приходом следующего тактового импульса вновь закрываются транзисторы 1 и 2, По окончании тактового импульса входной ток транзистора 1 (Ijx, Ij .1 д) больше входного тока транзистора 2 (Ig,, 1 (,) , так как токовьй повторитель на транзисторе 4 закрыт. Поэтому быстрее открывается транзистор 1, что приводит к запиранию транзисторов 2 и 3 и отпиранию транзистора 4. Следовательно, JK-триггер при () работает в счетном режиме.

Предположим, что (). В этом случае с приходом тактового импульса транзисторы 1 и 2 основной ячейки памяти запираются, что приводит к отпиранию транзисторов 6 и 7 (так ка,к ). Отпирание транзисторов 6 и 7 приводит к тому, что по окончании тактового импульса (транзистор 5 зап1фается) транзисторы 1 и 2 основной ячейки памяти остаются в закрь том состоянии. Следовательно, при , JK триггер находится в режиме хранения.

При J-0, К 1(, ) по окончании тактового импульса тран.чистор 6

закрыт, а транзистор 7 открыт, что приводит к однозначному запиранию транзистора 2 и отпиранию транзистора 1 независимо от значений входньк токов. Это в свою очередь приводит к запиранию транзистора 3 и отпиранию транзистора 4 ( ).

При , (, ) по окончании тактового импульса, транзисторы 6 и 7 соответственно открыты (закрыты) . Отпирание транзистора 6 приводит к закрыванию транзисторов 1 и 4 и отпиранию транзисторов 2 и 3, (, ). Формула изобретения

л

Тактируемый vtK-триггер И Л-типа, содержащий основную ячейку памяти, выполненную на первом и втором п-р-п транзисторах с непосредственными связями, дополнительную ячейку памяти, выполненную на третьем и четвертом п-р-п транзисторах с непосредственными связями, пятый п-р-п транзистор, база которого соединена с тактовой шиной, а первый и второй коллекторы

соответственно соединены с

базами

5

0

5

первого и второго п-р-п транзисторов, вторые коллекторы которых соответственно соединень с базами третьего и четвертого п-р-п транзисторов, вторые коллекторы которых соединены с соответствующими выходными шинами триггера, базы шестого и седьмого п-р-п транзисторов соедт1нены соответственно с J и К входами триггера, коллекторы соединены соответственно с базами первого и второго п-р-п транзисторов, эмиттер инжектирующего р-п-р транзистора соединен с шиной пптания, соответствующие коллекторы - с базами п-р-п транзисторов, а база - с эмиттерами п-р-п транзисторов и шиной нулевого потенциала, отличающийся тем, что, с целью упро- . щения триггера, дополнительные третьи коллектора первого и второго п-р-п транзисторов соединены соответственно с базами шестого и седьмого п-р-п транзисторов, третий коллектор четвертого транзистора соединен с базой первого транзистора, четвертый коллектор четвертого транзистора соединен с базой этого же транзистора.

Tf

(Pu2.i

10

fPuz.2

Авторы

Даты

1988-09-07—Публикация

1987-01-04—Подача