12

(Я

S

tc

оа

i sTI 11 I

6664

±г:I

9ив. i

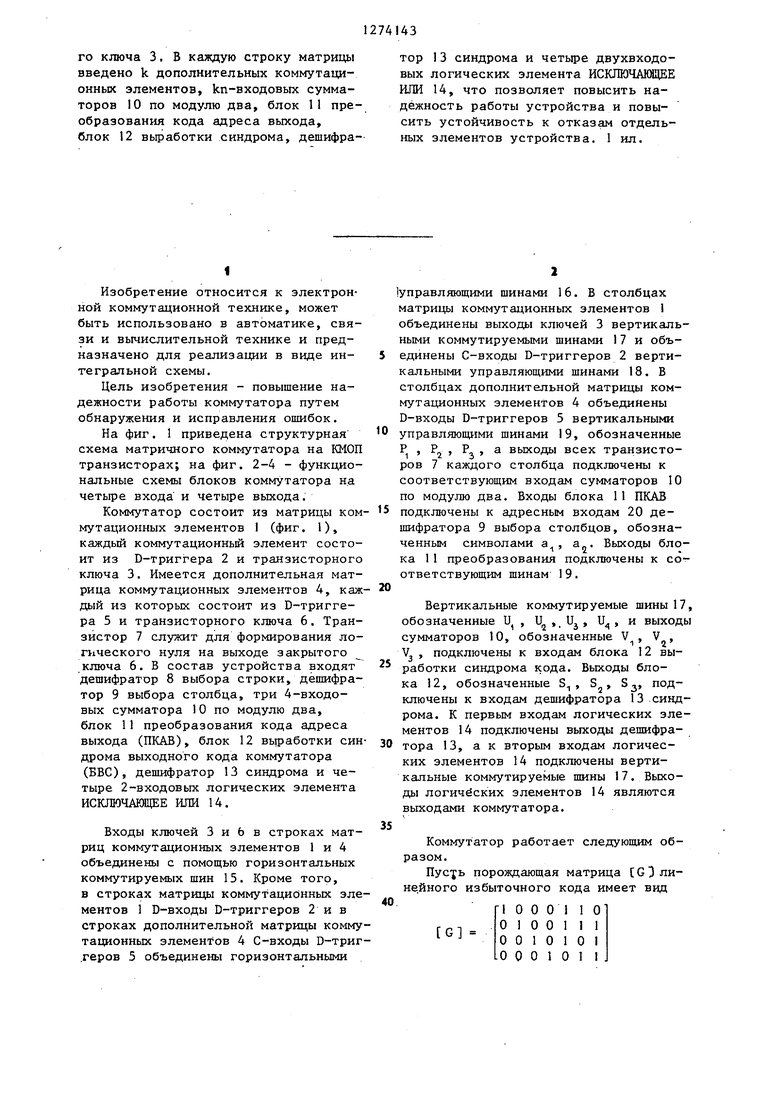

го ключа 3, В каждую строку матрицы введено k дополнительных коммутационных элементов, kn-входовых сумматоров 10 по модулю два, блок 11 преобразования кода адреса выхода, блок 12 выработки синдрома, дешифратор 13 синдрома и четыре двухвходовых логических элемента ИСКЛЮЧАНШЩЕ ИЛИ 14, что позволяет повысить надёжность работы устройства и повысить устойчивость к отказам отдельных элементов устройства. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное вычислительное устройство | 1990 |

|

SU1833890A1 |

| Коммутационное устройство | 1985 |

|

SU1307573A1 |

| СИСТЕМА ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК | 1991 |

|

RU2007042C1 |

| Коммутационное устройство | 1985 |

|

SU1307572A1 |

| Матричный коммутатор | 1987 |

|

SU1429308A1 |

| Устройство для обмена информацией | 1979 |

|

SU842773A1 |

| Матричное коммутационное устройство | 1988 |

|

SU1569965A1 |

| Матричный коммутатор | 1985 |

|

SU1275753A1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОГО СООБЩЕНИЯ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2179365C1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

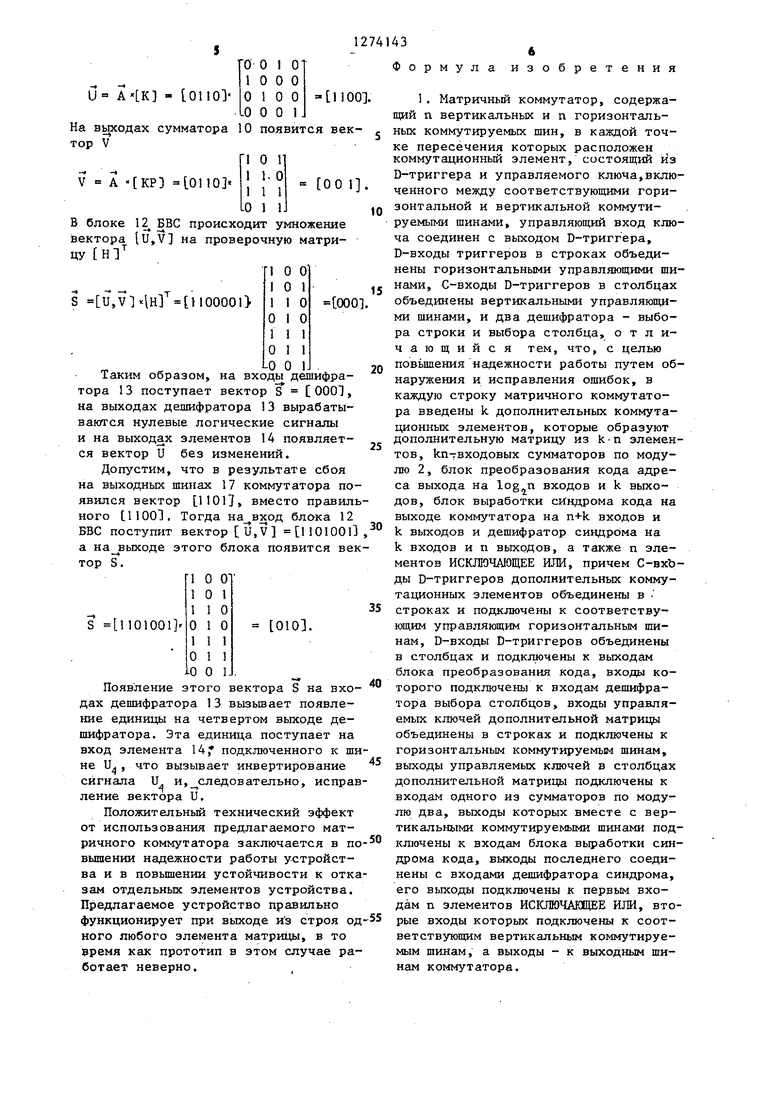

Изобретение относится к области электронной коммутационной техники, может быть использовано в автоматике, связи и вычислительной технике. Цель изобретения - повышение надежности работы путем обнаружения и исправления ошибок. Устройство содержит m вертикальных 17 и п горизонтальных 16 коммутируемых шин, в каждой точке пересечения которых расположен коммутационный элемент,- состоящий из D-триггера 2 и транзисторно

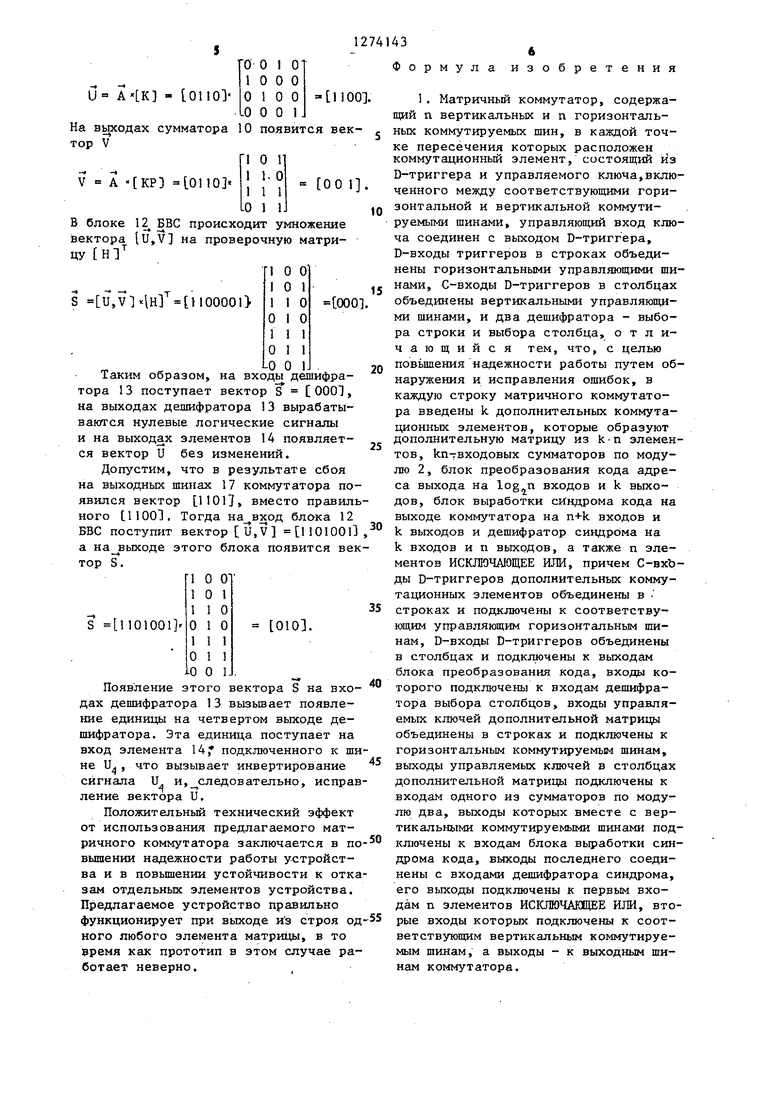

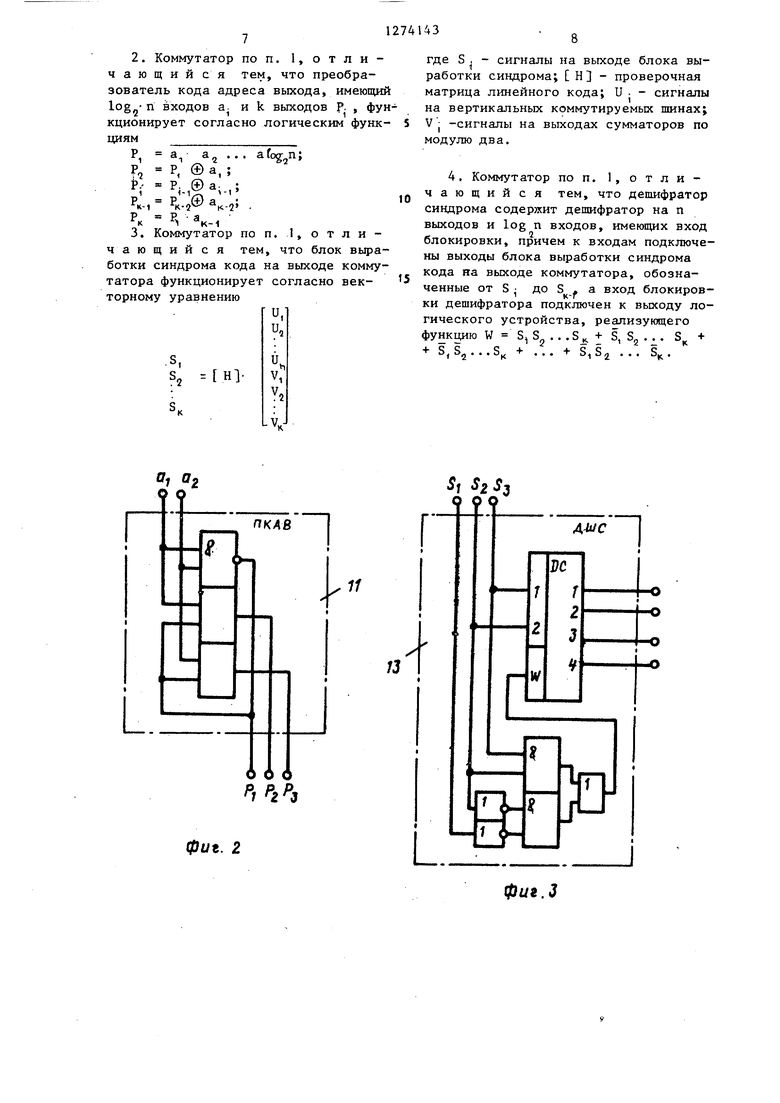

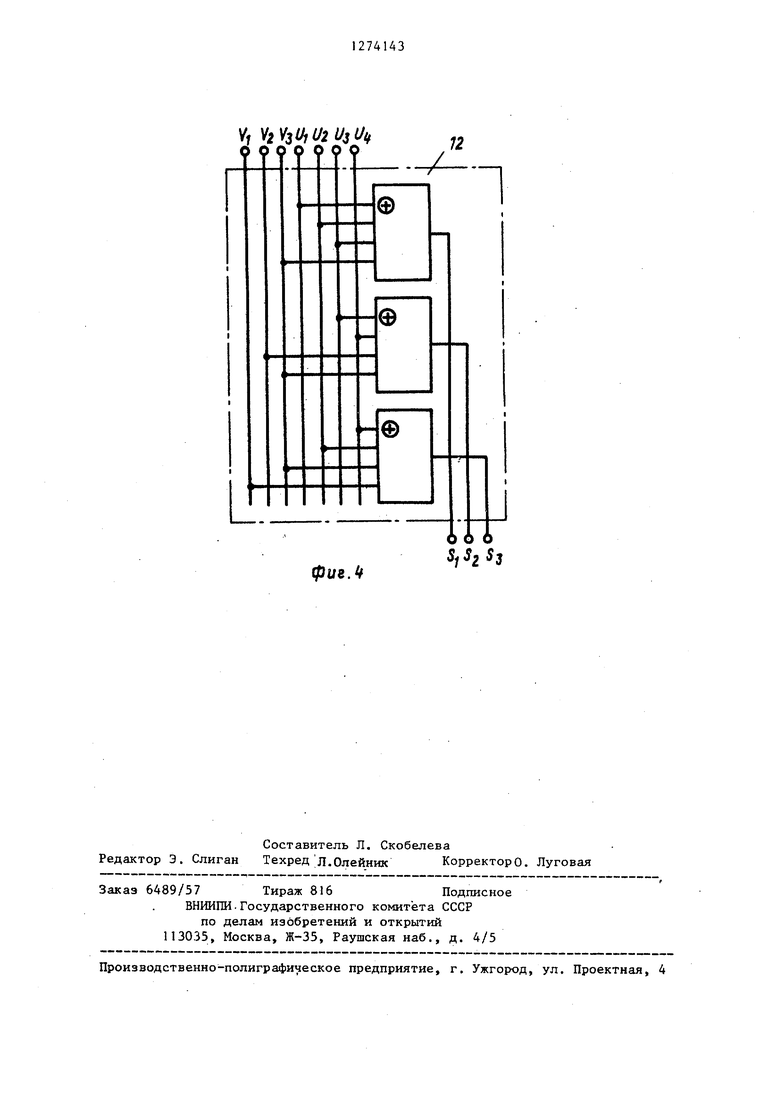

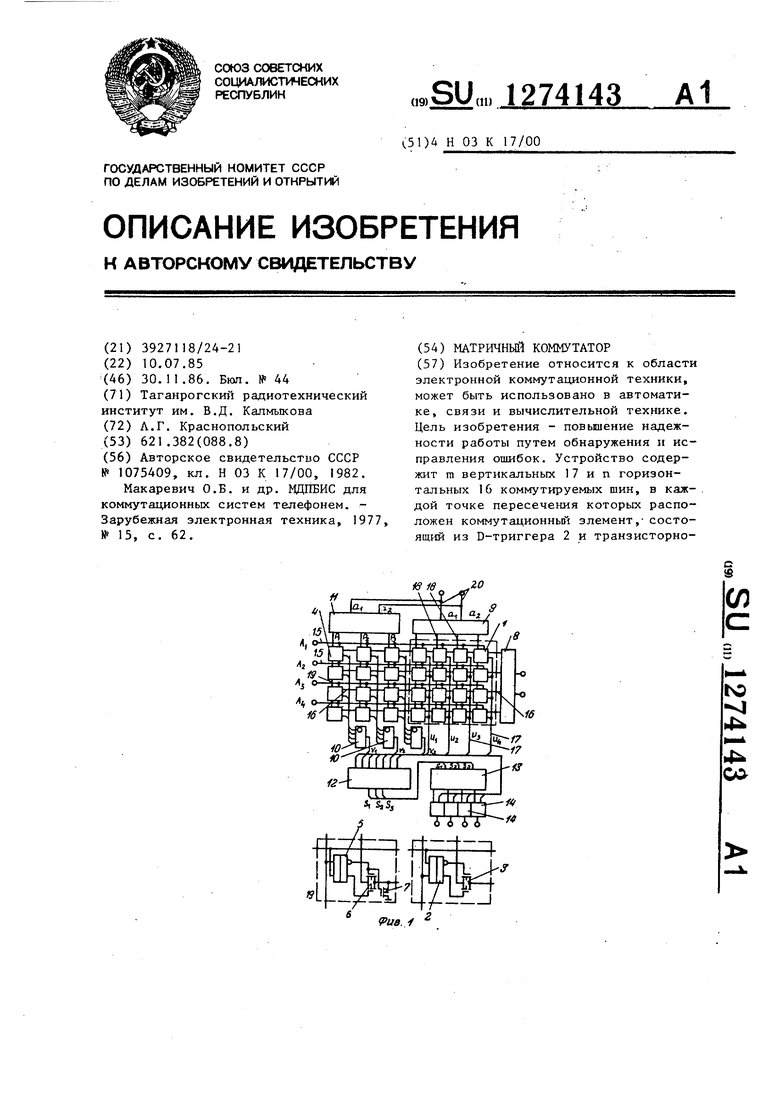

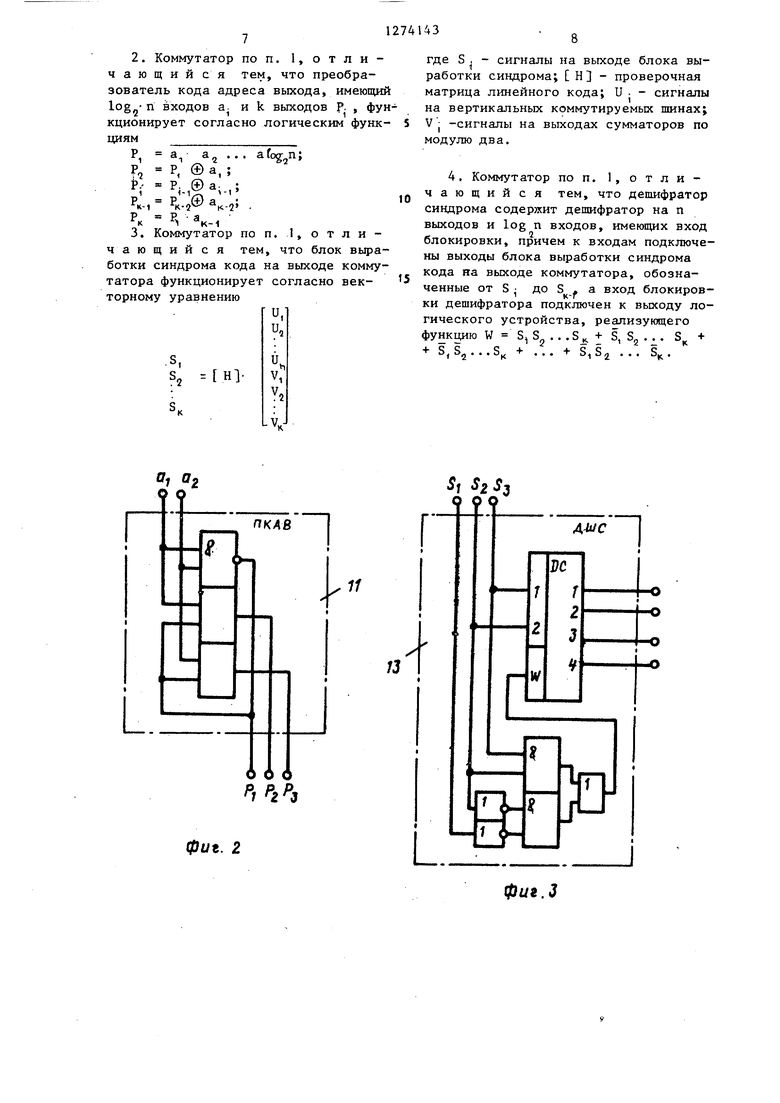

Изобретение относится к электронной коммутационной технике, может быть использовано в автоматике, связи и вычислительной технике и предназначено для реализации в виде интегральной схемы. Цель изобретения - повышение надежности работы коммутатора путем обнаружения и исправления ошибок. На фиг. 1 приведена структурная схема матричного коммутатора на КМОП транзисторах; на фиг. 2-4 - функциональные схемы блоков коммутатора на четьфе входа и четыре выхода. Коммутатор состоит из матрицы ком мутационных элементов 1 (фиг. 1), каждый коммутационньй элемент состоит из D-триггера 2 и транзисторного ключа 3. Имеется дополнительная матрица коммутационных элементов 4, каж дый из которых состоит из D-триггера 5 и транзисторного ключа 6. Транзистор 7 служит для формирования логического нуля на выходе закрытого ключа 6. В состав устройства входят дешифратор 8 выбора строки, дешифратор 9 выбора столбца, три 4-входовых сумматора 10 по модулю два, блок 11 преобразования кода адреса выхода (ПКАВ), блок 12 выработки син дрома выходного кода коммутатора (ВВС), дешифратор 13 синдрома и четыре 2-входовьгх логических элемента ИСКЛЮЧАЩЕЕ ИЛИ 14. Входы ключей 3 и 6 в строках матриц коммутационных элементов 1 и 4 объединены с помощью горизонтальных коммутируемых шин 15. Кроме того, в строках матрицы коммутационных эле ментов 1 D-входы D-триггеров 2 и в строках дополнительной матрицы комму тационных элементов 4 С-входы D-триг .геров 5 объединены горизонтальными управляющими шинами 16. В столбцах матрицы коммутационных элементов 1 объединены выходы ключей 3 вертикальными коммутируемыми шинами 17 и объединены С-входы D-триггеров 2 вертикальными управляющими шинами 18. В столбцах дополнительной матрицы коммутационных элементов 4 объединены D-входы D-триггеров 5 вертикальными управляющими шинами 19, обозначенные Р , Pj , Р, , а выходы всех транзисторов 7 каждого столбца подключены к соответствующим входам сумматоров 10 по модулю два. Входы блока 11 ПКАВ подключены к адресньм входам 20 дешифратора 9 выбора столбцов, обозначенным символами а, а„. Выходы блока 11 преобразования подключены к соответствующим шинам 19. Вертикальные коммутируемые шины 17, обозначенные U , U ., Uj , U , и выходы сумматоров 10, обозначенные V, V , V, , подключены к входам блока 12 выработки синдрома кода. Выходы блока 12, обозначенные S , S , S.j, подключены к входам дешифратора 13 синдрома. К первым входам логических элементов 14 подключены выходы дешифратора 13, а к вторым входам логических элементов 14 подключены вертикальные коммутируемые шины 17. Выходы логических элементов 14 являются выходами коммутатора. Коммутатор работает следующим образом. Ilycfb порождающая матрица GO линейного избыточного кода имеет вид 10001 10 0100111 0010101 000101 1 а проверочная матрица НТ Г1 1 1 О 1 О О Н 0011110 LG 1 О О I I 1. А-,, А, Входной двоичный вектор А У на горизонтальных шинах А (фиг. 1) преобразуется коммута1щонной матрицей в выходной двоичный ве тор и на вертикальных шинах 17. Это преобразование можно представить оп ратором коммутации К1, который име ет в каждом столбце и в каждой стро ке только одну единицу, например ГО О 1 О 1000 0100 О О О 1. Тогда выходной вектор U можно представитьи А « К. (2) Чтобы выходное слово избыточного ко да I ,2 2 3 - удовлетворяло проверочному соотношению U.V . {Н О, необходимо, чтобы оно удовлетворяло следующему уравнению U,V и- G, (3) Но для того, чтобы обнаружить ошибки, произошедшие в коммутаторе, нужно, чтобы проверочные разряды избыточного кода з ависели только от вход ного вектора А. Подставив (2) в (3) получим . u,v АЧк LG (4) Учитьшая, что матрицу G можно пред ставить в виде единичной матрицы I и матрицы Р1 /Pi, уравнение (4) распаивается на два соотношения и А СК (5) и А С К АЧКР (6) Умножение матрицы Р на матрицу К эквивалентно перестановке строк матрицы LP следующим образом: i строка IP попадает на место j строки в матрице КР, если в i строке СКТ единица стоит в j столбце. Необходимо, чтобы устройству, реализующее умножение вектора А на матрицу КР , функционировало независиМО от коммутационной матрицы. В зтом случае ошибка, появившаяся в векторе и, будет обнаружена после умножения на проверочную матрицу ТН S U,V. а синдром S укажет на позицию ошибочного бита и. Исправление ошибочного бита производится инвертирова15нием с помощью логического элемента ИСКЛЮЧАЩЕЕ ИЛИ 14 (фиг. 1). Пример установления соединений и передачи коммутируемой информации без ошибки и с ошибкой. Допустим, необходимо соединить входы под номерами 1, 2, 3 и 4 с выходами соответственно под номерами 3, 1, 2 и 4, т.е. оператор коммутации имеет вид (О. Установление соединений происходит следующим Образом.На входы дешифратора 8 (фиг. 1) после,довательно поступают коды номеров . входоэ и последовательно выбираются шины 16 (с верхней по нижнюю}. Одновременно на адресные входы 20 поступают соответствующие коды номеров выходов. При этом выбирается одна из шин 18, а на шины Р , Р и Р из блока 11 ПКАВ поступают коды, соответствующие i строке матрицы Pi, где i номер выхода, соединяемого в данный такт настройки переключателя. Таким образом, в каждый такт настройки информация записывается в выбранный столбец основной матрицы коммутаг гонных элементов I и в выбранную строку дополнительной матрицы коммутационных элементов 4. После установления всех соединений, содержание ячеек памяти коммутационных элементов 1 и 4 соответствует произведению матриц К1-iGl, или, что то же самое, матрице К/КР, причем основная матрица коммутационных элементов 1 соответствует К, а дополнительная матрица коммутационных элементов 4 соответствует КР. Для рассматриваемого случая КР имеет вид 1 О Л Если переключатель не имеет неисправностей и сбоев, то при передаче информации блок 12 ВВС вьщает на шины S , Sj, нулевой вектор (S S Sj О), дешифратор 13 заблокируется, на его входе W (фиг. 3) находится логическая единица, и элементы 14 (фиг. 1) передают выходные сигналы основной матрицы U - U с шин 17 на выходы коммутатора. Например, если входной вектор Л коммутатора имеет вид 0110, то шинах 17 появится двоичный вектор U О О I О 1000 и - оно tnoo0100 LO О О 1 На выходах сумматора 10 появится вектор V V А 001 В блоке 12 ВВС происходит умножение вектора lU,V на проверочную матрицу Hi s и,У14нГ иоооо1 000 001. Таким образом, на входы дешифратора 13 поступает вектор S 0001, на выходах дешифратора 13 вырабатываются нулевые логические сигналы и на выходах элементов 14 появляется вектор и без изменений. Допустим, что в результате сбоя на выходных шинах 17 коммутатора появился вектор ПОП, вместо правиль ного til001, Тогда на вход блока 12 ВВС поступит вектор и,V П0100П а на выходе этого блока появится век тор S. S 1101001 0101. Появление этого вектора S на вхо дах дешифратора 13 вызьшает появление единицы на четвертом выходе дешифратора. Эта единица поступает на вход элемента 14, подключенного к ш не и что вызывает инвертирование сигнала U и,следовательно, испра ление вектора U. Положительный технический эффект от использования предлагаемого матричного коммутатора заключается в п вышении надежности работы устройства и в повьш1ении устойчивости к отк зам отдельных элементов устройства. Предлагаемое устройство правильно функционирует при выходе из строя од кого любого элемента матрицы, в то время как прототип в этом случае ра ботает неверно. Формула изобретения 1. Матричный коммутатор, содержащий п вертикальных и п горизонтальных коммутируемых шин, в каждой точке пересечения которых расположен коммутационньй элемент, состоящий из D-триггера и управляемого ключа,включенного между соответствующими горизонтальной и вертикальной коммутируемыми шинами, управляющий вход ключа соединен с выходом D-триггера, D-входы триггеров в строках объединены горизонтальными управляющими шинами, С-входы D-триггеров в столбцах объединены вертикальными управляющими шинами, и два дешифратора - выбора строки и выбора столбца, отличающийся тем, что, с целью повьш1ения надежности работы путем обнаружения и исправления ошибок, в каждую строку матричного коммутатора введены k дополнительных коммутац;ионных элементов, которые образуют дополнительную матрицу из элементов, kn7вxoдoвыx сумматоров по модулю 2, блок преобразования кода адреса выхода на log п входов и k выходов, блок выработки синдрома кода на выходе коммутатора на n+k входов и k выходов и дешифратор синдрома на k входов и п выходов, а также п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем С-вхЪды D-триггеров дополнительных коммутационных элементов объединены в . строках и подключены к соответствующим управляющим горизонтальным шинам, D-входы D-триггеров объединены в столбцах и подключены к выходам блока преобразования кода, входы которого подключены к входам дешифратора выбора столбцов, входы управляемых ключей дополнительной матрицы объединены в строках и подключены к горизонтальным коммутируемым шинам, выходы управляемых ключей в столбцах дополнительной матрицы подключены к входам одного из сумматоров по модулю два, выходы которых вместе с вертикальными коммутируемыми шинами подключены к входам блока выработки синдрома кода, выходы последнего соединены с входами дешифратора синдрома, его выходы подключены к первым входам п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых подключены к соответствуюшим вертикальным коммутируемым шинам, а выходы - к выходным шинам коммутатора.

V, 2

0, 02 Q О

П г

ПКАВ

f

где S , - сигналы на выходе блока выработки синдрома; С Н - проверочная

Sj S2 О

п

DC матрица линейного кода; U - сигналы на вертикальных коммутируемых шинах; V j -сигналы на выходах сумматоров по модулю два. 4. Коммутатор по п. 1, о т л и чающийся тем, что дешифратор синдрома содержит дешифратор на п выходов и log п входов, имеющих вход блокировки, причем к входам подключены выходы блока выработки синдрома кода на выходе коммутатора, обозначенные от S до S , а вход блокировки дешифратора подключен к выходу логического устройства, реализующего функцию W S, S . . .Sj. + S, Sj ... + S, S,j. ..S + ... + . .

о 0

Piflfj

фиг. 2

X

w

фиг.З

| Матричное коммутационное устройство | 1982 |

|

SU1075409A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Макаревич О.Б | |||

| и др | |||

| МДПБИС для коммутационных систем телефонем | |||

| Зарубежная электронная техника, 1977, № 15, с | |||

| Способ крашения тканей | 1922 |

|

SU62A1 |

Авторы

Даты

1986-11-30—Публикация

1985-07-10—Подача