to

СП

ел

со

тикальные коммутируемые шины, в каждой точке пересечения которых расположены D-триггер 2 и первый транзисторный аналоговый ключ 3. В устройство введены дополнительные аналоговые ключи 4,5,6, управляемые входы которых соединены с управляющей шиной разрешения настройки. Уменьшение числа шин позволяет уменьшить внутренние паразитные емкости, что обеспечивает большую помехоустойчивость и чистоту диапазона коммутируемых сигналов, 1 ил,

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный коммутатор | 1985 |

|

SU1274143A1 |

| Матричный коммутатор | 1983 |

|

SU1102038A1 |

| Коммутационное устройство | 1985 |

|

SU1307572A1 |

| Матричный коммутатор | 1987 |

|

SU1439614A1 |

| Коммутационное устройство | 1985 |

|

SU1307573A1 |

| УСТРОЙСГВО для РАСКРЫТИЯ ОПРЕДЕЛИТЕЛЕЙ МАТРИЦ | 1968 |

|

SU218538A1 |

| Матричный распределитель | 1987 |

|

SU1580377A1 |

| Матричное коммутационное устройство | 1988 |

|

SU1569965A1 |

| УСТРОЙСТВО для ОПРЕДЕЛЕНИЯ ЗНАКА ЧЛЕНОВ ОПРЕДЕЛИТЕЛЯ МАТРИЦЫ | 1972 |

|

SU336664A1 |

| Модуль многокаскадной коммутационной системы | 1990 |

|

SU1793443A1 |

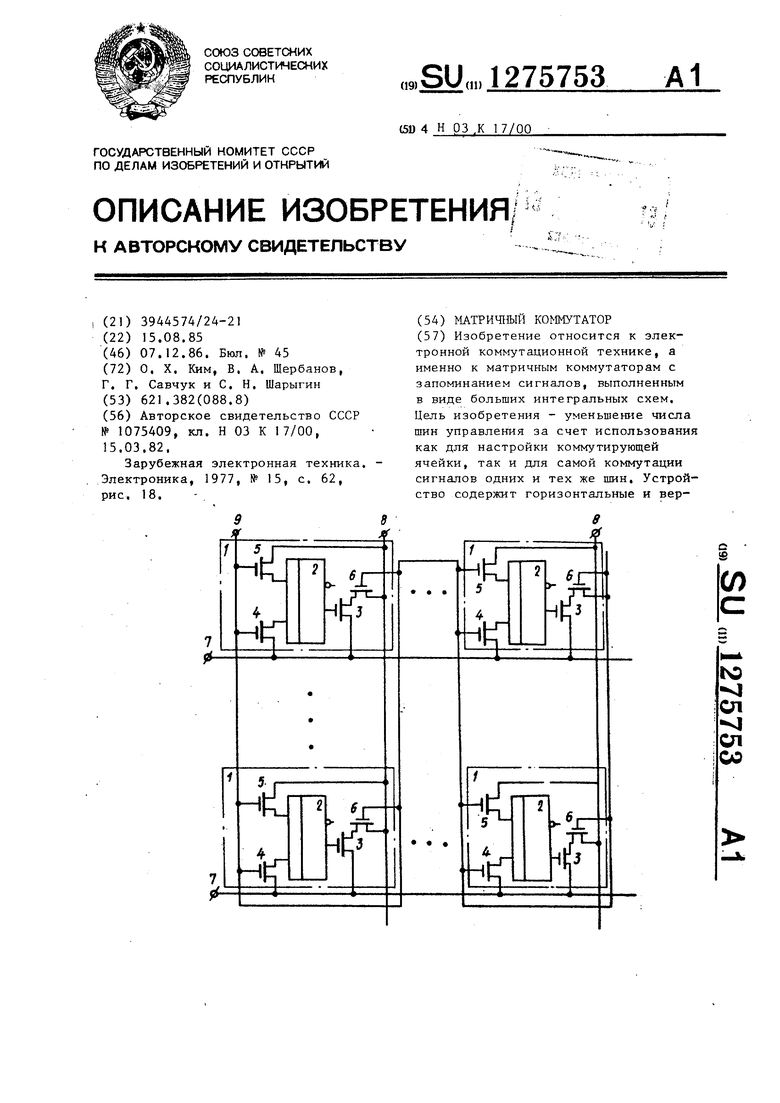

Изобретение относится к электронной коммутационной технике, а именно к матричным коммутаторам с запоминанием сигналов, выполненным в виде больших интегральных схем. Цель изобретения - уменьшение числа шин управления за счет использования как для настройки коммутирующей ячейки, так и для самой коммутации сигналов одних и тех же шин. Устройство содержит горизонтальные и вер

Изобретение относится к электронной коммутационной технике и может быть использовано для создания коммутационных полей на основе больших интегральных схем, , Цель изобретения - уменьшение чис ла внешних шин управления коммутатором за счет использования как для настройки коммутирующей ячейки, так и для самой коммутации сигналов одни и тех же горизонтальных и вертикальных коммутируемых шин путем введения двух дополнительных ключей для настройки и одного нормально замкнутого аналогового ключа в цепь коммутации , На чертеже показана принципиальная схема коммутатора при использовании в качестве ключей МДП-транзисторов, Устройство содержит коммутирующие ячейки 1, расположенные в матричном порядке. Каждая ячейка состоит из D-триггера 2, аналогового ключа 3, первого 4 и второго 5 дополнительных ключей и нормально замкнутого ключа 6, Управляющими входами ключей явля ются затворы МДПтранзисторов, Комм тирующие ячейки 1 объединены односменнь1Ми выводами по строкам и стол цам соответственно горизонталыш ми 7 и вертикальньтми 8 коммутируе1 1ыми шинами. Прямой выход D-триггера 2 соединен с управляющим входом анало гового ключа 3, который включен пос ледовательно с нормально замкнутым аналоговым ключом 6 между горизонтальной 7 и вертикальной 8 коммутируемьтми шинами о Дополнительные ключи 4 и 5 включены соответственно между 1)-входом D-триггера 2 и горизонтальной коммутируемой шиной 7, С-входом того же триггера и вертикальной коммутируемой шиной 8, Управляющие входы нормально замкнутого аналогового ключа 6 и дополнительных ключей 4 и 5 подключены к шине 9 настройки матрицы. Устройство работает следующим образом. Состояние коммутирующей ячейки 1 определяется D-триггером 2. В режиме настройки на шину 9 настройки матрицы подается единичный сигнал. Нормально замкнутый аналоговый ключ 6при этом закрыт, а дополнительные ключи 4 и 5 открыты. От устройства управления последовательно на каждую из горизонтальных коммутируемых шин 7подаются единичные сигналы, которые обеспечивают запись логической 1 в D-триггер выбранного столбца. Выбор столбца производится одновременно подачей единичного сигнала на вертикальшле коммутируемые шины 8. После соответствующего числа тактов настройки аналоговые ключи 3 всех коммутирующих ячеек 1 принимают состояния, соответствующие кодам настройки, и коммутатор готов к работе. Коммутируемые сигналы передаются между соответствующими горизонтальными 7 и вертикальными 8 коммутируемыми шинами только через аналоговые ключи 3 тех коммутирукщих ячеек 1, D-триггеры 2 которых установлены в единичное состояние. При этом сигнал шины 9 настройки матрицы приоб-. ретает нулевое значение и нормально замкнутьй аналоговый ключ 6 переходит в проводящее состояние, а дополнительные ключи 4 закрываются. Благодаря минимальному числу шин управления коммутатором может быть

обеспечена высокая интеграция в БИС матричных коммутаторов на основе интегральной технологии.

Формула изобретения

«

Матричный коммутатор, содержащий матрицу коммутирующих ячеек, объединенных одноименными выводами по строкам и столбцам соответственно горизонтальными и вертикальными коммутируемыми шинами, каждая из которых состоит из D-триггера и аналогового ключа, управляющий вход которого подключен к выходу D-триггера, а один из аналоговых выводов - к горизонтальной коммутируемой шине, о т л и чающийся тем, что, с целью уменьшения числа внешних шин управления , в каждую коммутирующую ячейку введены нормально замкнутый аналоговый ключ и два дополнительных ключа, управляюпще входы которых подключены к шине настройки матрицы, D-вход D-триггера через первый дополнительный ключ подключен к горизонтальной коммутируемой шине соответствующей строки, а С-вход того же триггера подключен к вертикальной коммутируемой шине соответствующего столбца, нормально замкнутый аналоговый ключ включен между вторым вьшодом аналогового ключа и соответствующей вертикальной коммутируемой шиной .

| Матричное коммутационное устройство | 1982 |

|

SU1075409A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Зарубежная электронная техника | |||

| Электроника, 1977, № 15, с | |||

| Способ крашения тканей | 1922 |

|

SU62A1 |

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

Авторы

Даты

1986-12-07—Публикация

1985-08-15—Подача