112

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля: цифровых интегральных схем и логических блоков ЭВМ.

Цель изобретения - повышение достоверности контроля.

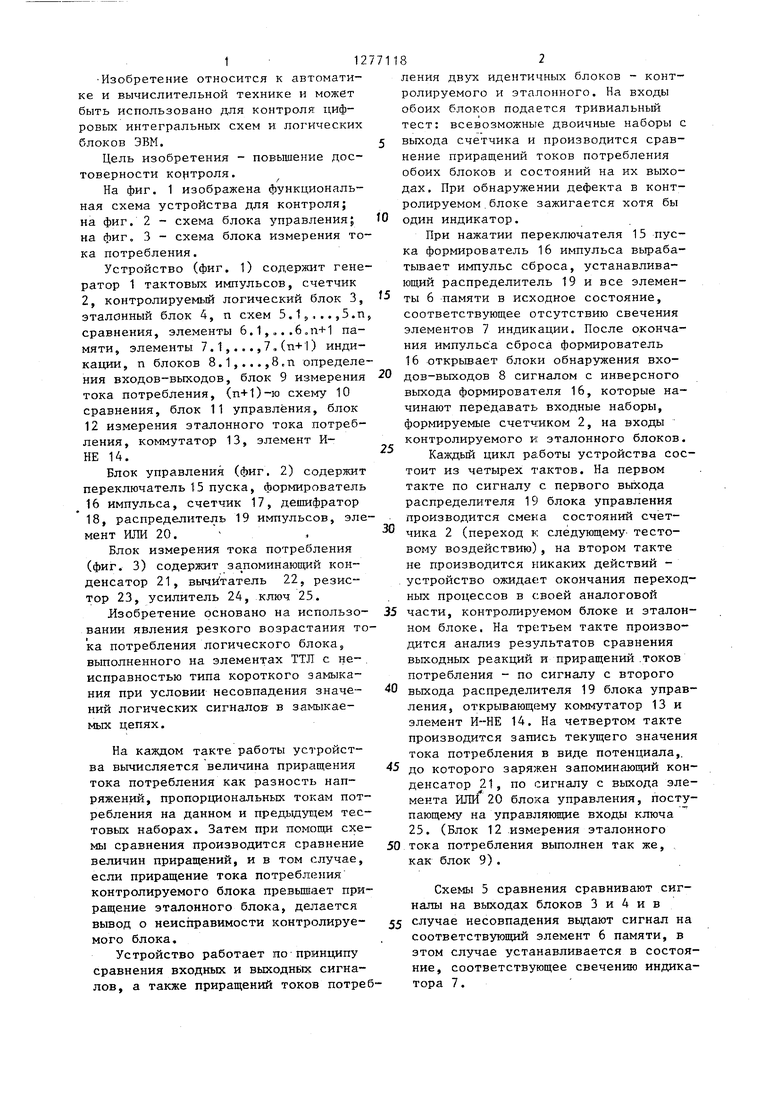

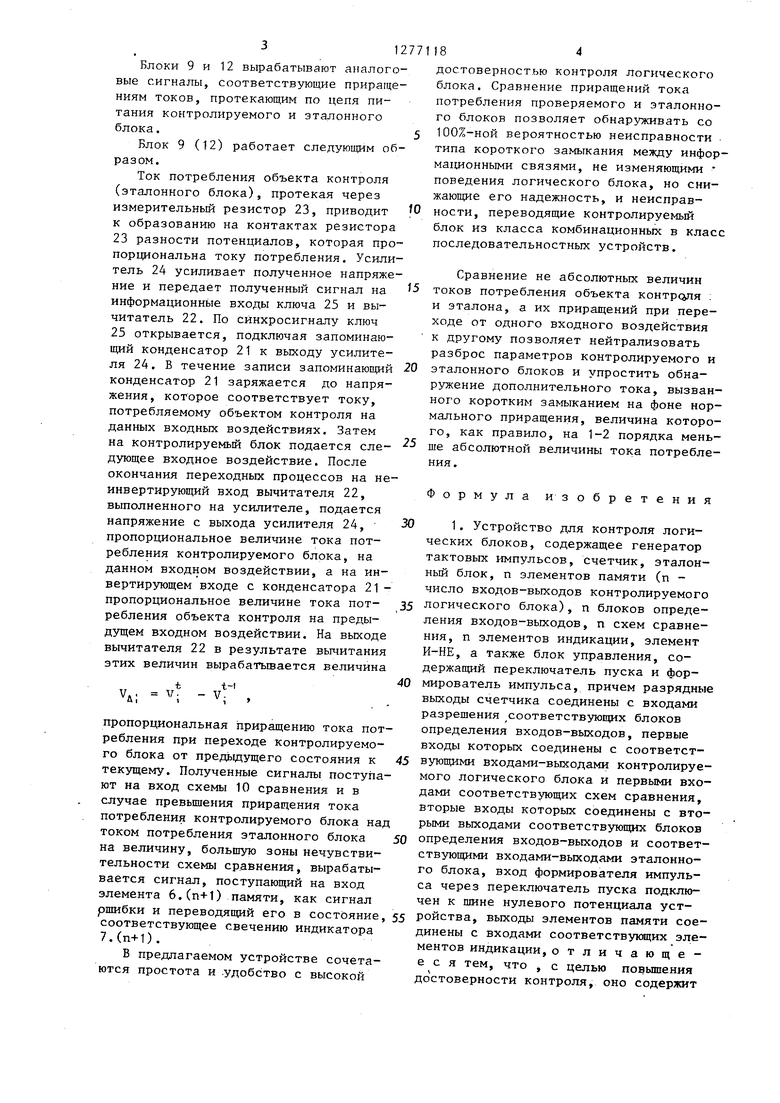

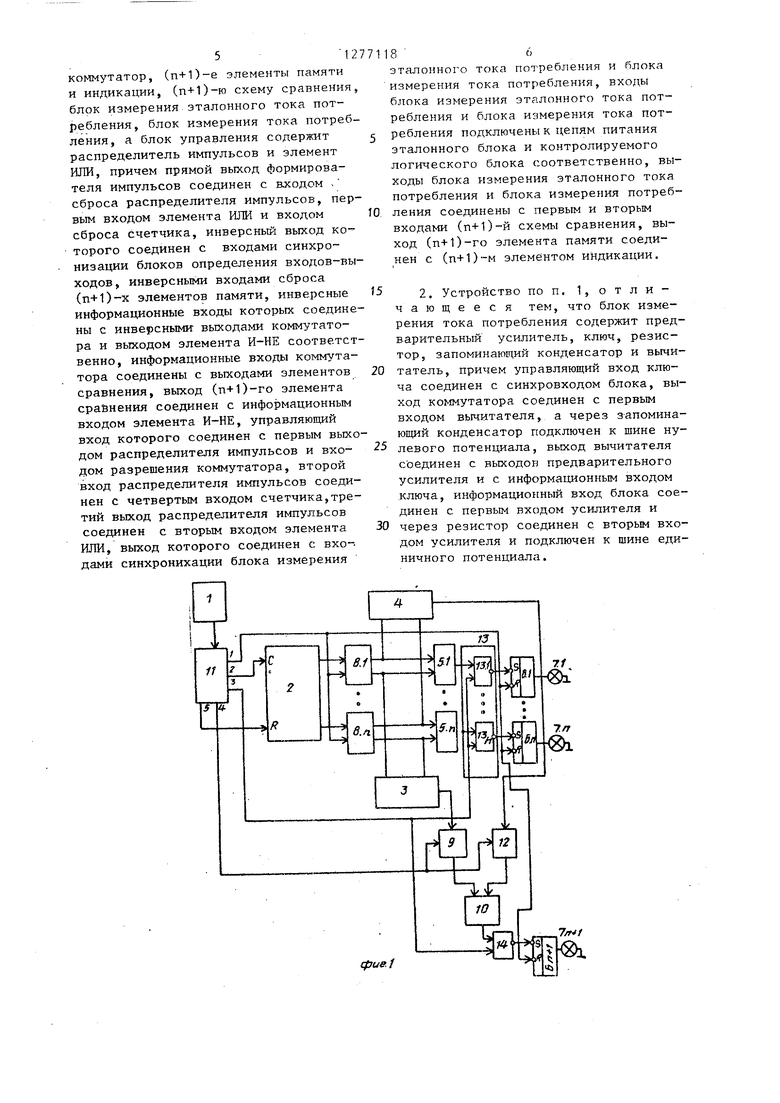

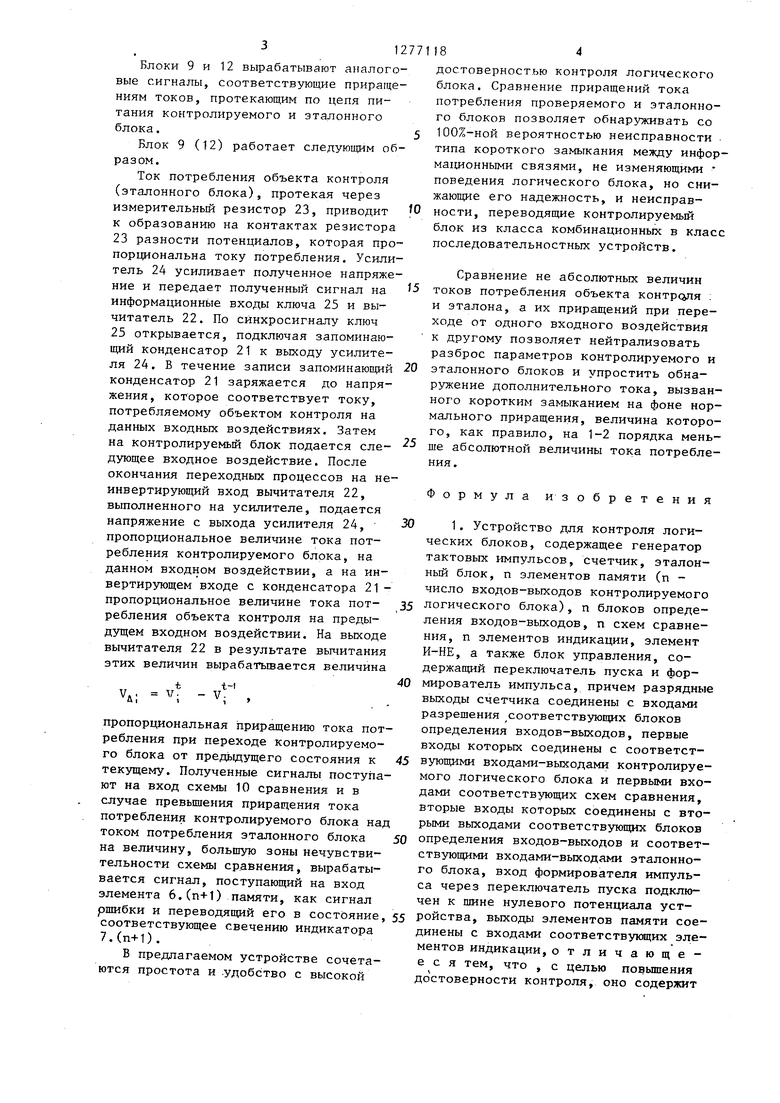

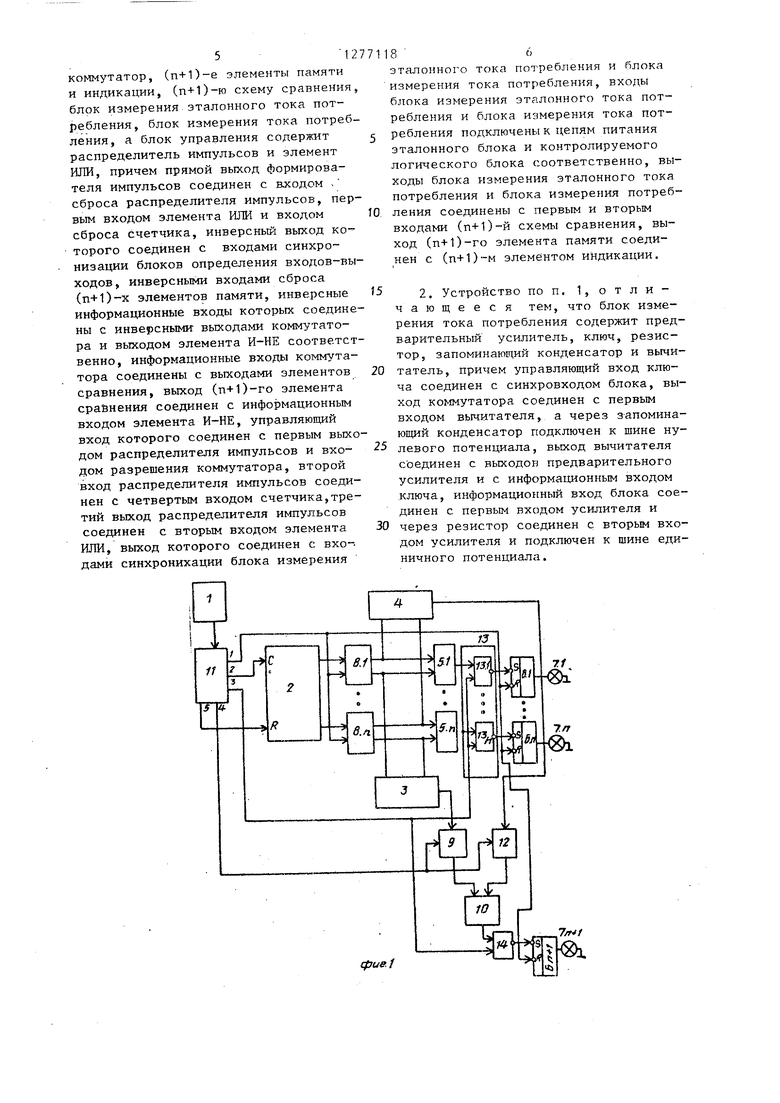

На фиг. 1 изображена функциональная схема устройства для контроля; на фиг. 2 - схема блока управления; на фиг, 3 - схема блока измерения тока потребления.

Устройство (фиг, 1) содержит генератор 1 тактовых импульсов, счетчик 2, контролируемый логический блок 3, эталонный блок 4, п схем 5.1р,.,,5.П сравнения, элементы 6.1,„..6«п+1 памяти, элементы 7.1,..., 7, (n+ l) индикации, п блоков 8.1,...,8.п определения входов-выходов, блок 9 измерения тока потребления, (п+1)-ю cxeiviy 10 сравнения, блок 11 управления, блок 12 измерения эталонного тока потребления, коммутатор 13, элемент И- НЕ 14.

Блок управления (фиг. 2) содержит переключатель 15 пуска, формирователь 16 импульса, счетчик 17, дешифратор 18, распределитель 19 импульсов, элемент ИЛИ 20.

Блок измерения тока потребления (фиг. 3) содержит за поминающий конденсатор 21, вьгч1 татель 22, резистор 23, усилитель 24, ключ 25.

Изобретение основано на использовании явления резкого возрастания тока потребления логического блока, выполненного на элементах ТТЛ с не- , исправностью типа короткого замыкания при условии несовпадения значений логических сигналов в замыкаемых цепях.

На каждом такте работы устройства вычисляется величина приращения тока потребления как разность напряжений, пропорциональных токам потребления на данном и предьщущем тестовых наборах. Затем при помощи схемы сравнения производится сравнение величин приращений, и в том случае, если приращение тока потребления контролируемого блока превьш ает приращение эталонного блока, делается вывод о неисправимости контролируемого блока.

Устройство работает по принципу сравнения входных и выходных сигналов, а также приращений токов потреб25

71182

ления двух идентичных блоков - контролируемого и эталонного. На входы обоих блоков подается тривиальный тест: всевозможные двоичные наборы с

5 выхода счетчика и производится сравнение приращений токов потребления обоих блоков и состояний на их выходах. При обнаружении дефекта в контролируемом .блоке зажигается хотя бы 10 один индикатор.

При нажатии переключателя 15 пуска формирователь 16 импульса вырабатывает импульс сброса, устанавливающий распределитель 19 и все элемен- 5 ты 6 памяти в исходное состояние, соответствующее отсутствию свечения элементов 7 индикации. После окончания импульса сброса формирователь 16 открьшает блоки обнаружения вхо- 20 дов-выходов 8 сигналом с инверсного выхода формирователя 16, которые начинают передавать входные наборы, формируемые счетчиком 2, на входы контролируемого и эталонного блоков.

Каждьш цикл работы устройства состоит из четырех тактов. На первом такте по сигналу с первого выхода распределителя 19 блока управления производится смена состояний счет чика 2 (переход к следующему- тестовому воздействию), на втором такте не производится никаких действий - устройство ожидает окончания переходных процессов в своей аналоговой

35 части, контролируемом блоке и эталонном блоке. На третьем такте производится анализ результатов сравнения выходных реакций и приращений .токов потребления - по сигналу с второго

выхода распределителя 19 блока управления, открывающб му коммутатор 13 и элемент И-НЕ 14. На четвертом такте производится запись текущего значения тока потребления в виде потенциала,.

45 до которого заряжен запоминающий конденсатор 21, по сигналу с выхода элемента ИЛИ 20 блоха управления, поступающему на управляющие входы ключа 25. (Блок 12 измерения эталонного

50 тока потребления выполнен так же, как блок 9).

Схемы 5 сравнения сравнивают сигналы на выходах блоков 3 и 4 и в 55 случае несовпадения выдают сигнал на соответствующий элемент 6 памяти, в этом случае устанавливается в состояние, соответствующее свечению индикатора 7.

312

Блоки 9 и 12 вырабатывают аналоговые сигналы, соответств5пощие приращениям токов, протекающим по цепя питания контролируемого и эталонного блока.

Блок 9 (12) работает следующим образом.

Ток потребления объекта контроля (эталонного блока), протекая через измерительный резистор 23, приводит к образованию на контактах резистора 23 разности потенциалов, которая пропорциональна току потребления. Усилитель 24 усиливает полученное напряже

ние и передает полученный сигнал на

информационные входы ключа 25 и вы- читатель 22. По синхросигналу ключ 25 открывается, подключая запоминающий конденсатор 21 к выходу усилителя 24. В течение записи запоминающий конденсатор 21 заряжается до напряжения, которое соответствует току, потребляемому объектом контроля на данных входных воздействиях. Затем на контролируемый блок подается еле- дующее входное воздействие. После окончания переходных процессов на неинвертирующий вход вычитателя 22, выполненного на усилителе, подается напряжение с выхода усилителя 24, пропорциональное величине тока потребления контролируемого блока, на данном входном воздействии, а на инвертирующем входе с конденсатора 21 - пропорциональное величине тока пот- ребления объекта контроля на предыдущем входном воздействии. На выходе вычитателя 22 в результате вычитания этих величин вырабатывается величина

ь t-i

V.

А;

t t-l

V. - V.

пропорциональная приращению тока потребления при переходе контролируемого блока от предьщущего состояния к текущему. Полученные сигналы поступают на вход схемы 10 сравнения и в случае превьшгения приращения тока потребления контролируемого блока над током потребления эталонного блока на величину, большую зоны нечувствительности схемы сравнения, вырабатывается сигнал, поступающий на вход элемента 6.(п+1) памяти, как сигнал ршибки и переводящий его в состояние, соответствующее свечению индикатора 7.(п+1).

В предлагаемом устройстве сочетаются простота и .удобство с высокой

0

5

0 0 5

0

5 0 5

достоверностью контроля логического блока. Сравнение приращений тока потребления проверяемого и эталонного блоков позволяет обнарзокивать со 100%-ной вероятностью неисправности . типа короткого замыкания между инфор- мационньши связями, не изменяющими поведения логического блока, но снижающие его надежность, и неисправности, переводящие контролируемый блок из класса комбинационных в класс последовательностных устройств.

Сравнение не абсолютных величин токов потребления объекта контропя : и эталона, а их приращений при переходе от одного входного воздействия к другому позволяет нейтрализовать разброс параметров контролируемого и эталонного блоков и упростить обнаружение дополнительного тока, вызванного коротким замыканием на фоне нормального приращения, величина которого, как правило, на 1-2 порядка меньше абсолютной величины тока потребления.

Формула изобретения

1. Устройство для контроля логических блоков, содержащее генератор тактовых импульсов, счетчик, эталонный блок, п элементов памяти (п - число входов-выходов контролируемого логического блока), п блоков определения входов-выходов, п схем сравнения, п элементов индикации, элемент И-НЕ, а также блок управления, содержащий переключатель пуска и формирователь импульса, причем разрядные выходы счетчика соединены с входами разрешения соответствующих блоков определения входов-выходов, первые входы которых соединены с соответствующими входами-выходами контролируемого логического блока и первыми входами соответствующих схем сравнения, вторые входы которых соединены с вторыми выходами соответствующих блоков определения входов-выходов и соответствующими входами-выходами эталонного блока, вход формирователя импульса через переключатель пуска подключен к шине нулевого потенциала устройства, выходы элементов памяти соединены с входами соотватствуклцих элементов индикации,отличающееся тем, что , с целью повышения до стоверности контроля, оно содержит

коммутатор, (n+1)-e элементы памяти и индикации, (п+1)-ю схему сравнения блок измерения эталонного тока потребления, блок измерения тока потребления, а блок управления содержит распределитель импульсов и элемент ИЛИ, причем прямой выход формирователя импульсов соединен с входом - сброса распределителя импульсов, первым входом элемента ИЛИ и входом сброса счетчика, инверсны выход ко- торого соединен с входами синхронизации блоков определения входов-выходов, инверсными входами сброса (п+1)-х элементов памяти, инверсные информационные входы которых соединены с инверсными- выходами коммутатора и выходом элемента И-НЕ соответственно, информационные входы KoisiMyTa- тора соединены с выходами элементов сравнения, выход (п+1)-го элемента сравнения соединен с информационным входом элемента И-НЕ, управляющий вход которого соединен с первым выходом распределителя импульсов и входом разрешения коммутатора, второй вход распределителя импульсов соединен с четвертым входом счетчика,третий выход распределителя импульсов соединен с вторым входом элемента ИЛИ, выход которого соединен с вхо-. дами синхронихации блока измерения

8 6

эталонного тока потребления и блока измерения тока потребления, входы блока измерения эталонного тока потребления и блока измерения тока потребления подключены к цепям питания эталонного блока и контролируемого логического блока соответственно, выходы блока измерения эталонного тока потребления и блока измерения потребления соединены с первым и вторым входами (п+1)-й схемы сравнения, выход (п+1)-го элемента памяти соединен с (п+1)--м элементом индикации.

2. Устройство по п. 1, о т л и - чающееся тем, что блок измерения тока потребления содержит предварительный усилитель, ключ, резистор, запоминающий конденсатор и вычи- татель, причем управляющий вход ключа соединен с синхровходом блока, выход коммутатора соединен с первым входом вычитателя, а через запоминающий конденсатор подключен к шине нулевого потенциала, выход вычитателя соединен с выходов предварительного усилителя и с информационным входом ключа, информационный вход блока соединен с первым входом усилителя и через резистор соединен с вторым входом усилителя и подключен к шине единичного потенциала.

А / /«;

.

f/ Su6)

Си /fffjfff y )

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматизированного контроля параметров реле | 1985 |

|

SU1265704A1 |

| Устройство для цетрализованного контроля | 1976 |

|

SU661515A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| УСТРОЙСТВО ДЛЯ ДИАГНОСТИРОВАНИЯ ТЕЛЕВИЗИОННОЙ АППАРАТУРЫ | 1989 |

|

RU2050700C1 |

| Устройство для измерения температуры | 1980 |

|

SU907402A1 |

| Устройство для диагностирования троированных дискретных схем автоматики | 1990 |

|

SU1772783A1 |

| Устройство для контроля запоминающих матриц | 1979 |

|

SU875468A1 |

| Устройство для контроля автоматической телефонной станции | 1984 |

|

SU1218495A1 |

| Устройство для измерения температуры | 1985 |

|

SU1315831A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при контроле ТЭЗов. Цель изобретения - повышение достоверности контроля. Устройство содержит генератор тактовых импульсов, блок управления, эталонный блок, блоки определения входов - выходов, счетчик, элементы индикации, блоки измерения потребления. В устройстве измеряют приращение токов потребления в эталонном блоке и в контролируемом. В случае их несовпадения формируют дополнительный сигнал ошибки. 1 з.п. ф-лы, 3 ил. ю ч 00

г

Z3

21

22

Составитель A. Сиротская- Редактор Е. Копча Техред И.Попович Корректор А. Ильин

Заказ 6668/43 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

qfre/ffS

| Устройство для обнаружения неисправностей в логических схемах | 1971 |

|

SU441532A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля логических блоков цвм | 1976 |

|

SU633019A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-15—Публикация

1985-04-22—Подача