(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ ЦВМ

1)ый вход блока соединен с первыми входами первого и второго эпементов И-НЕ, второй вход блока соединен со счетным входом триггера и со вторыми входами первого и второго элементов И-НЕ, инверсный выход триггера соединен с третьими входами первого и второго элементов И-МЕ, выходы которых ясвпяются выхода ми блока, выход первого элемента И-НЕ соединен с первым входом третьего элемента И-НЕ и со входом эмиттерного повторителя, выход которого соединен через элемент НЕ со вторым входом третьего элемента И-НЕ, выход третьего элемента И-НЕ соединен с Д-«ходом триггера,

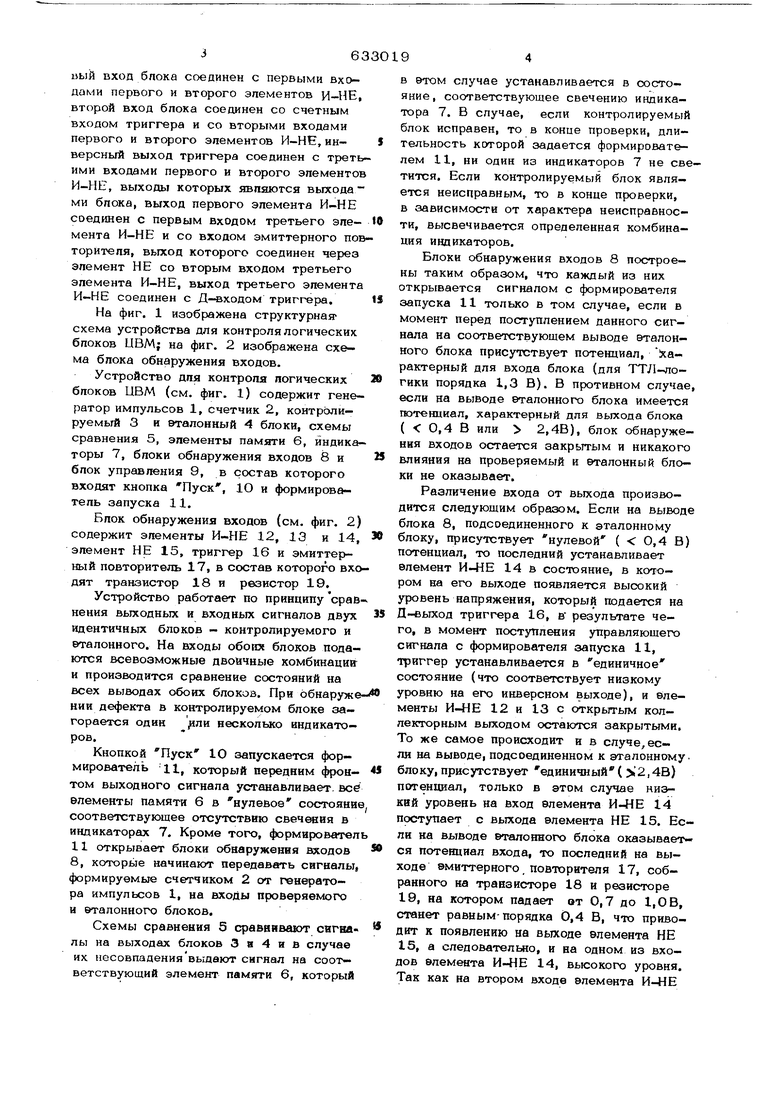

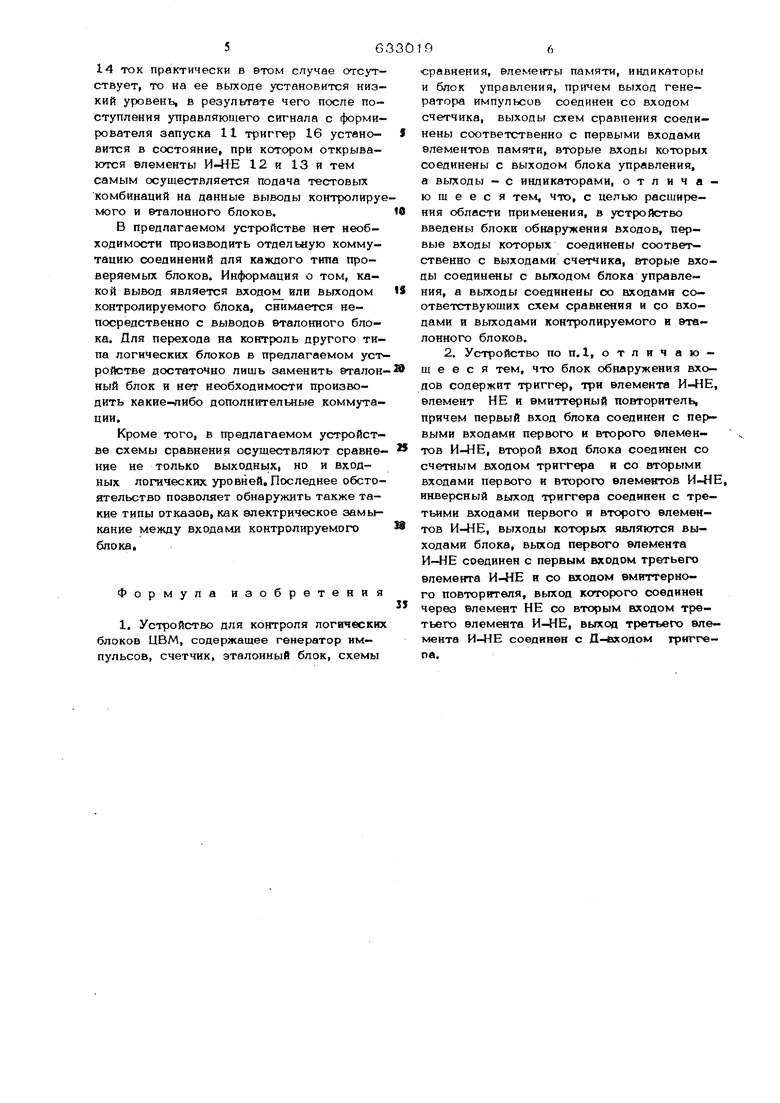

На фиг. 1 изображена структурнаясхема устройства для контроля логических блоков ЦВМ; на фиг. 2 изображена схема блока обнаружения входов.

Устройство для контроля логических блоков ЦВМ (см. фиг. 1) содержит генератор импульсов 1, счетчик 2, контролируемый 3 и эталонный 4 блоки, схемы сравнения 5, элементы памяти 6, индикаторы 7, блоки обнаружения входов 8 и блок управления 9, в состав которого входят кнопка Пуск, Ю и формирователь запуска 11.

Блок обнаружения входов {см. фиг. 2) содержит элементы И-НЕ 12, 13 и 14, элемент НЕ 15, триггер 16 и эмиттерный повторитель 17, в состав которого входят транзистор 18 и резистор 19.

Устройство работает по принципу сравнения выходных и входных сигналов двух идентичных блоков - контролируемого и эталонного. На входы o6otix блоков подаются всевозможные двойчвые комбинаций и производится сравнение состояний на всех выводах обоих блоков. При обнаружеНИИ дефекта в контролируемом блоке загорается один /1ЛИ несколько индикаторов.

Кнопкой Пуск 10 запускается формирователь 11, который передним фронтом выходного сигнала устанавливает.веб элементы памяти 6 в нулевое состояние соответствующее отсутствию свечения в индикаторах 7. Кроме того, формировател 11 открывает блоки обнаружения входов 8, которые начинают передавать сигналы, формируемые счетчиком 2 от генератора импульсов 1, на входы проверяемого и эталонного блоков.

Схемы сравнения 5 сравнивают сигналы на выходах блоков 3 а 4 и в случае их несовпадениявыдают сигнал на соответствующий элемент памяти 6, который

в этом случае устанавливается в состояние , соответствующее свечению индикатора 7. В случае, если контролируемый блок исправен, то в конце проверки, длительность которой задается формирователем 11, ни один из индикаторов 7 не светится. Если контролируемый блок является неисправным, то в конце проверки, в зависимости от характера неисправности, высвечивается определенная комбинация индикаторов.

Блоки обнаружения входов 8 построены таким образом, что каждый из них открывается сигналом с формирователя запуска 11 только в том случае, если в момент перед поступлением данного сигнала на соответствующем выводе эталонного блока присутствует потенциал, Характерный для входа блока (для ТТЛ-логики порядка 1,3 В). В противном случае если на выводе эталонного блока имеется потенциал, характерный для выхода блока ( 0,4 В или 2,4В), блок обнаружения входов остается закрытым и никакого влияния на проверяемый и эталонный блоки не оказывает.

Различение входа от выхода производится следующим образом. Если на вывод блока 8, подсоединенного к эталонному блоку, присутствует нулевой ( 0,4 В) потенциал, то последний устанавливает элемент И-НЕ 14 в состояние, в котором на его выходе появляется высокий уровень напряжения, который подается на Д-«ыход триггера 16, в результате чего, в момент поступления управляющего сигнала с формирователя запуска 11, триггер устанавливается в единичное состояние (что соответствует низкому уровню на его инверсном выходе), и влементы И-НЕ 12 и 13 с открытьп коллекторным выходом остаются закрытыми. То же самое происходит и в случе, если на выводе, подсоединенном к эталонному блоку, присутствует единичный( 2,4В) потенциал, только в этом случае ниэкий уровень на вход элемента И-НЕ 14 поступает с выхода элемента НЕ 15. Если на выводе эталонного блока оказывается потенциал входа, то последний на выходе вмиттерного, повторителя 17, собранного на транзисторе 18 и резисторе 19, на котором падает от 0,7 до 1,ОВ, станет равным-порядка 0,4 В, что приводит к появлению на выходе элемента НЕ 15, а следовательно, и на одном из входов элемента И-НЕ 14, вьюокого уровня. Так как на втором входе элемента И-НЕ 56 14 ток практически в этом случае отсутствует, то на ее вьгходе установится низкий уровень, в результате чего после поступления управляющего сигнала с формирователя запуска 11 триггер 16 установится в состояние, при котором открываются элементы И-НЕ 12 и 13 и тем самым осуществляется подача тестовых комбинаций на данные выводы контролируе мого и эталонного блоков. В предлагаемом устройстве нет необходимости производить отдельную коммутацию соединений для каждого типа проверяемых блоков. Информация о том, какой вывод является входом или выходом контролируемого блока, снимается непосредственно с выводов эталонного блока. Для перехода на контроль другого типа логических блоков в предлагаемом устройстве достаточно лищь заменить эталон- ный блок и нет необходимости производить какие-либо дополнительные коммутации. Кроме того, в предлагаемом устройстве схемы сравнения осуществляют сравнение не только выходных, но и входных логических уровней. Последнее обстоятельство позволяет обнаружить также такие типы отказов, как электрическое замыкание между входами контролируемого блока. Формула изобретения 1. Устройство для контроля логических блоков ЦВМ, содержащее генератор импульсов, счетчик, эталонный блок, схемы 96 сравнения, элементы памяти, инпикаторы и блок управления, причем выход генератора импульсов соединен со входом счетчика, выходы схем сравнения соединены соответственно с первыми входами элементов памяти, вторые входы которых соединены с выходом блока управления, а выходы - с индикаторами, отличающееся тем, что, с целью расщире- ния области применения, в устройство введены блоки обнаружения входов, первые входы которых соединены соответственно с выходами счетчика, вторые входы соединены с выходом блока управления, а выходы соединены со входами соответствующих схем сравнения и со входами и выходами контролируемого и эталонного блоков. 2, Устройство по п. 1, о т л и ч а ю - щ е а с я тем, что блок обнаружения входов содержит триггер, три элемента И-НЕ, элемент НЕ и эмиттерный повторитель, причем первый вход блока соединен с первыми входами первого и второго элементов И-НЕ, второй вход блока соединен со счетным входом триггера и со вторыми входами первого и второго элементов И-ЛЕ, инверсный выход триггера соединен с третьими входами первого и второго элементов И-НЕ, выходы которых являются выходами блока, выход первого элемента И-НЕ соединен с первым входом третьего элемента И-НЕ и со входом эмиттерного повторителя, выход которого соединен через элемент НЕ со вторым вяодом третьего элемента И-НЕ, выход третьего элемента И-НЕ соединен с Д-еходом триггера.

96

г

RS

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических узлов | 1980 |

|

SU868764A1 |

| Многоканальное устройство для контроля логических блоков | 1982 |

|

SU1038947A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1180901A1 |

| Устройство для контроля логических узлов | 1982 |

|

SU1020829A1 |

| Логический пробник | 1983 |

|

SU1132268A1 |

| Устройство для контроля электрического монтажа | 1981 |

|

SU993275A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Устройство для группового поиска кратных дефектов в комбинационных логических блоках | 1980 |

|

SU896628A1 |

| АНАЛИЗАТОР ДЛЯ КОНТРОЛЯ ХАРАКТЕРИСТИК ДИНАМИЧЕСКИХ СИСТЕМ | 1971 |

|

SU300875A1 |

| Устройство для оценки профессиональной пригодности операторов | 1989 |

|

SU1647620A1 |

/2

1±

Г7

Авторы

Даты

1978-11-15—Публикация

1976-08-23—Подача