Изобретение относится к автоматике и вычислительной технике и может быть использовано, в частности, в ин- формандонно-измерительных и управляю- 11щх системах для получения цифрового значения логарифма входного напряжения .

Цель изобретения расширение области применения.

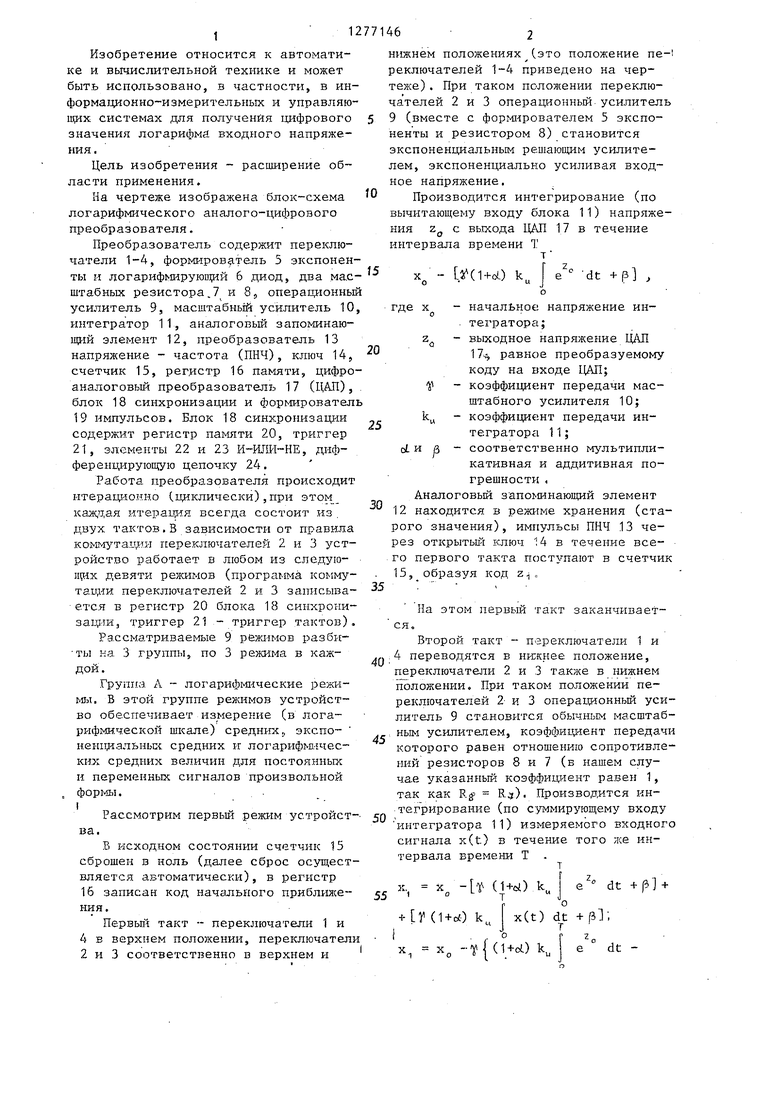

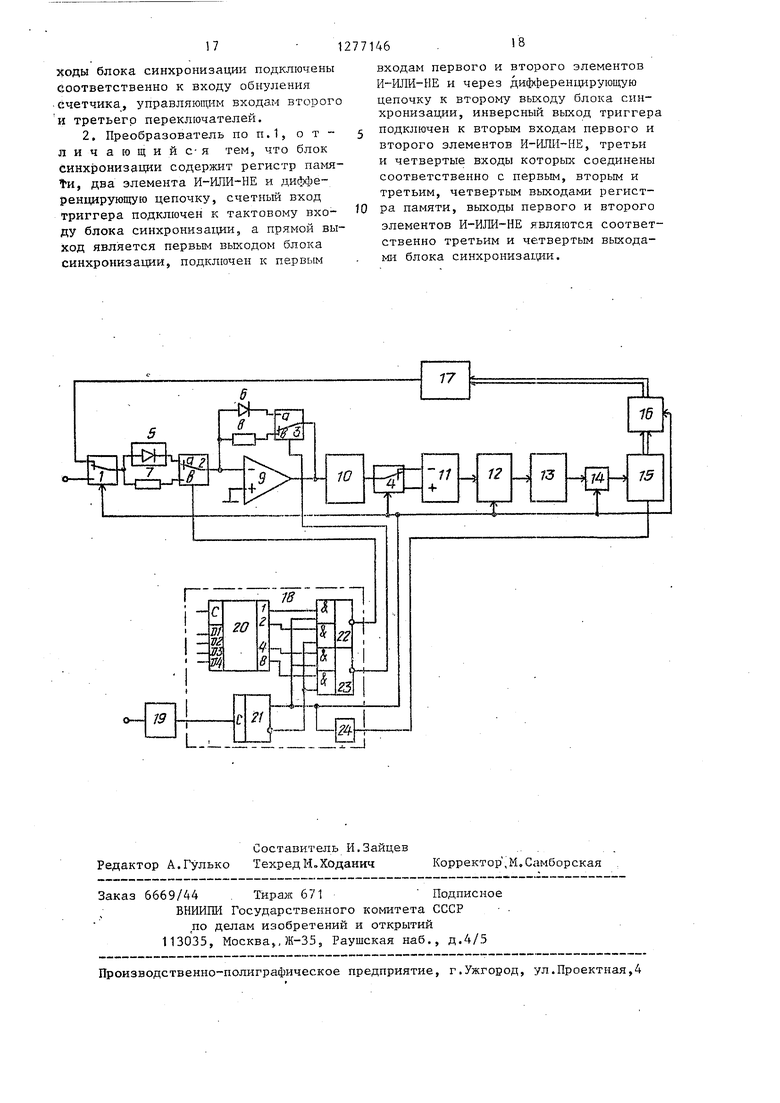

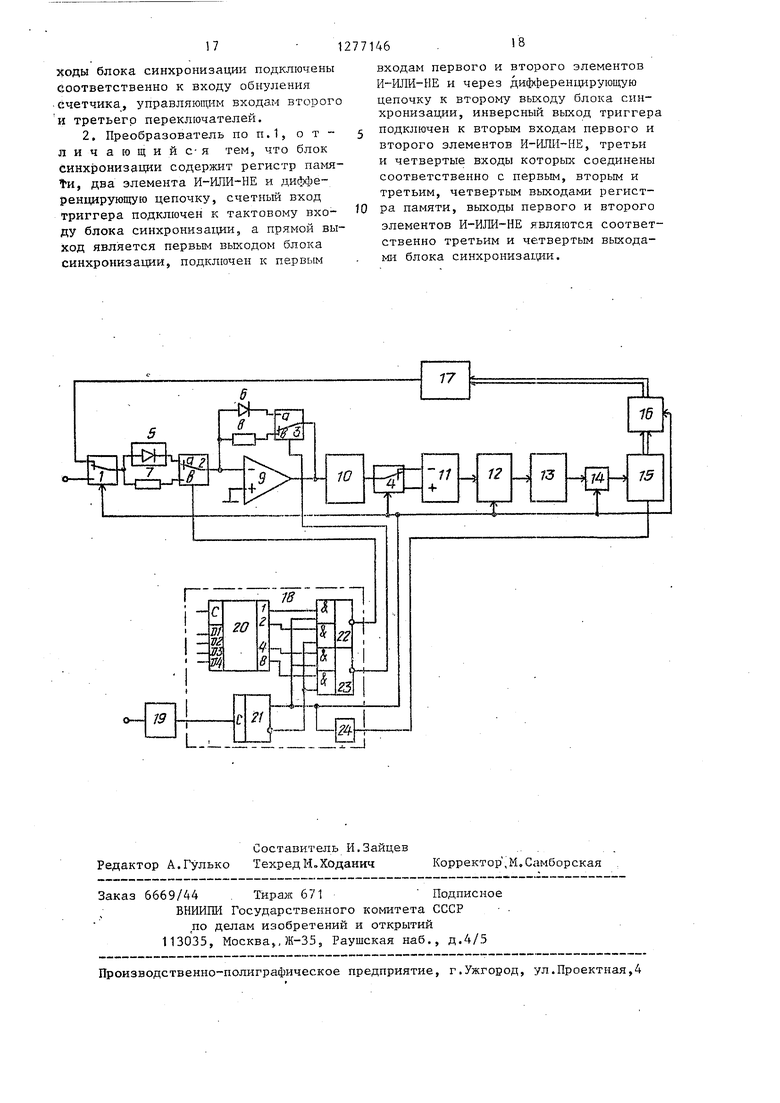

На чертеже изображена блок-схема логарифмического аналого-цифрового преобразователя.

Преобразователь содержит переключатели 1-4, формирователь 5 экспоненты и догарифмируюпщй 6 диод, два мае штабных резистора.7 и 8,, операционны усилитель 9, масштабнь® усилитель 10 интегратор 1 1, аналоговый запогуинаю- щий элемент 12, преобразователь 13 напряжение - частота (ПНЧ), ключ 14, счетчик 15, регистр 16 памяти, цифро аналоговьш преобразователь 17 (ЦАП), блок 18 синхронизации и формировател 19 импульсов. Блок 18 синхронизации содержит регистр памяти 20, триггер 21, элементы 22 и 23 И-ШШ-НЕ, дифференцирующую цепочку 24.

Работа преобразователя происходит итерац,ионно (циклически) , при этом каж,цая итерация всегда состоит из двух, тактов. В зависимости от правила комГ Гута1щи переключателей 2 и 3 устройство работает в любом из следуго- лрх девяти релсимов (программа комму- таиди переключателей 2 и 3 записывается в регистр 20 блока 18 синхрони- заидди, триггер 21 - триггер тактов). Рассматриваемые 9 режимов разби- ты на 3 группы, по 3 в каждой.

Группа А логарифмические режи- . В этой группе режимов устройство обеспечивает измерение (в лога

рифмической шкале) средних, экспо- нен1щальны;с средних и лoгapиф й-iчec- ких средних величин для постоянных и переменных сигналов произвольной

фOpIv Ы.. .

I

Рассмотрим первый режим устройст-- 0

ва.

В Р1СХОДНОМ состоянии счетчик 15 сброшен в ноль (далее сброс осуществляется автоматически), в регистр 16 записан код начального приблиясе- ния.

Первьш такт - переключатели 1 и 4 в верхнем положении, переключатели 2 и 3 соответственно в верхнем и

0

5

0

5

нижнем положениях (это положение ne-i реключателей 1-4 приведено на чертеже) . При таком положении переключателей 2 и 3 операционный усилитель 9 (вместе с формирователем 5 экспоненты и резистором 8) становится экспоненциальным решающим усилителем, экспоненциально усиливая входное напряжение.

Производится интегрирование (по вычитающему входу блока 11) напряжения Zjj с выхода ЦАП 17 в течение

интервала времени Т

т

х - i d+oL) k J е -dt +р ,

о где X - начальное напряжение ин- тегратора; z - выходное напряжение ЦАП

17ч, равное преобразуемому коду на входе ЦАП; f - коэффициент передачи масштабного усилителя 10; k - коэффициент передачи интегратор 1 11;

oL и А - соответственно мультипликативная и аддитивная погрешности ,

Аналоговьй запо шнающий элемент 12 находится в режиме хранения (старого значения), импульсы ПНЧ 13 через открытьй 1ШЮЧ 14 в течение всего первого такта поступают в счетчик 15, образуя код. Е ,

0

5

0

На этом первый такт заканчивается.

Второй такт - переключатели 1 и

.4 переводятся в ни;кнее положение, переключатели 2 и 3 также в нижнем положении. При таком положении переключателей 2 и 3 операционный усилитель 9 становится обычным масштаб: ным усилитаяем, коэффициент передачи которого равен отношению сопротивлений резисторов 8 и 7 (в нашем случае указанный коэффициент равен 1, так как Rg - R). Производится интегрирование (по с;утммирую1цему входу

интегратора 11) измеряемого входного сигна.ла x(t.) в течение того же интервала времени Т .

55

+ |3 +

1

- (1+ol) k x(t) dt, (1)

о . .

где X , - новое улучшенное приближение на выходе интегратора.

Аналогичный запоминающий элемент 12 открыт - в течение всего второго такта выходное напряжение интегратора 11 непрерывно записывается в аналоговый запоминаюпщй элемент 12.

На этом одна итерация заканчивается. По ее окончании на выходе ПНЧ 13 получаем новое, уточненное значе- ние частоты f |. Вторая итерадия проводится полностью аналогично первой

Первый такт - переключатели 1 и 4 переводятся в верхнее положение, переключатели 2 и J соответственно в верхнем и нижнем положениях.

Код 2, из счетчика 15 переписьюается в регистр 16, после чего импульсом дифференцирующей цепочки 24 счетчик 15 сбрасывается в ноль.

. Производится интегрирование напряжения 2 с выхода ЦАП 17 в течение интервала Т

К своему установившемуся значению X. В пределе , в установившемся режиме, выходная величина интегратора 11 от итерации к итерации не меняет ся, т.е. х х X. Как следует из алгоритма (3), выражение в фигур ных скобках равно нулю т

X, -(-(ИЙ ч dt . р, ,, I z. . j, j ,,

где X jj - напряжение на выходе интегратора, полученное после первой итерации.

Импульсы ПНЧ 13 через открытый ключ 14 в течение всего первого так- та поступают в счетчик 15, образуя новый код 2 2.

.Второй такт - переключатели 1 и 4 переводятся в нижнее положение, переключатели 2 и 3 также в нижнем положении.

Производится интегрирование измеряемого входного сигнала x(t) в течение того же интервала времени Т

Т

х, X, (l+ot) k I е - dt + pi +

т + у (1+ы) k, x(t) dt +p

i т

x2 X + d k I e .dt - - (1 + ci) k I x(t) dt} ° (2)

где x - новое, улучшенное прибли- жение на выходе интегратора 1 1 . Аналоговый запоминающий элемент

12 открыт - в течение всего второго

O

5

0

такта напряжение с выхода интегратора 11 непрерывно записывается в ана- логовьй запоминающий элемент 12. На выходе ПНЧ 13 поступает новое, уточненное значение частоты f.

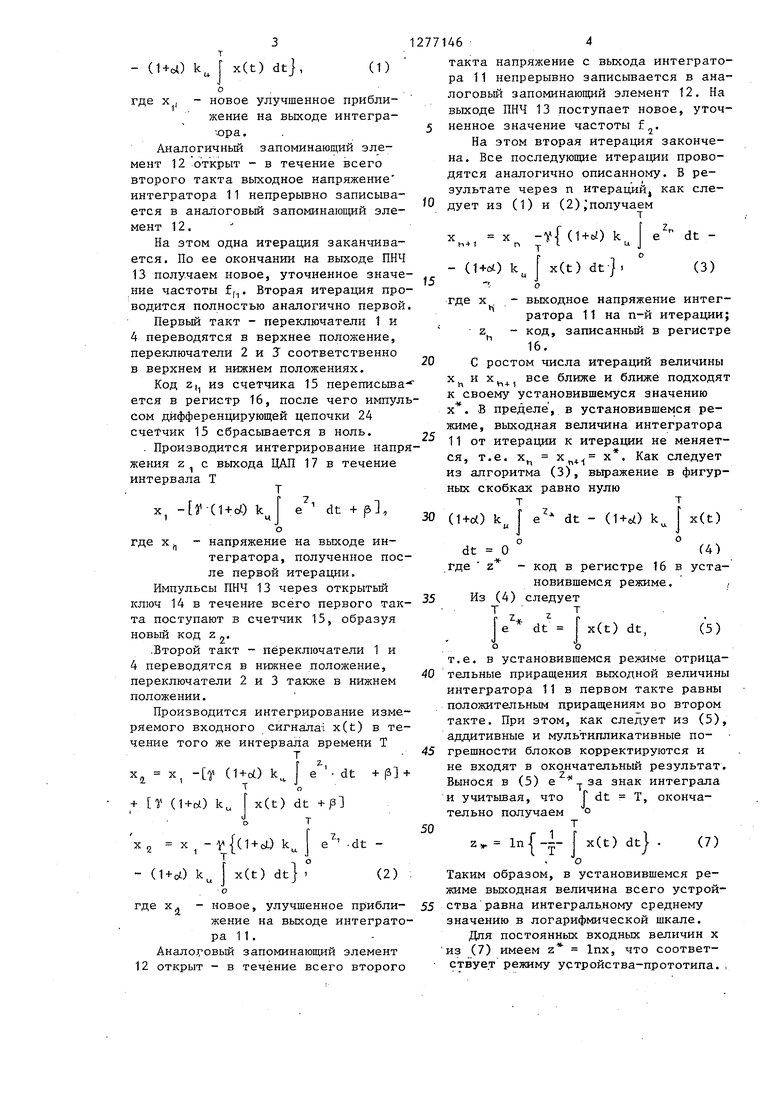

На этом вторая итерация закончена. Все последующие итерации проводятся аналогично описанному. В результате через п итераций, как следует из (1) и (2)Jполучаем

.., п ;V{(1-) ч| dt - (1+Ы) k I x(t) dfj. (3)

. о

где X - выходное напряжение интегратора 11 на п-й итерации; Z - код, записанный в регистре

16.

С ростом числа итераций величины X их.,, все ближе и ближе подходят

П 1

К своему установившемуся значению X. В пределе , в установившемся режиме, выходная величина интегратора 11 от итерации к итерации не меняется, т.е. х х X. Как следует из алгоритма (3), выражение в фигурных скобках равно нулю т

,, I z. . j, j ,,

dt О

(4)

5

0

0

5

Где Z - код в регистре 16 в установившемся режиме. Из (4) следует

} Z, г I е dt x(t) dt, (5)

° ь

т.е. в установившемся режиме отрицательные приращения выходной величины интегратора 11 в первом такте равны положительным приращениям во втором такте. При этом, как следует из (5), аддитивные и мультипликативные погрешности блоков корректируются и не входят в окончательный результат. Вынося в (5) е знак интеграла и учитьшая, что Г dt Т, окончательно получаем о Т

z 1п{- I x(t) dt) . (7)

о

Таким образом, в установившемся режиме выходная величина всего устройства равна интегральному среднему значению в логарифмической шкале.

Для постоянных входных величин х из (7) имеем z Inx, что соответствует режиму устройства-прототипа.,

На этом анализ и описание первого режима работы завершены.

Рассмотрим второй режим устройства. Измерение экспоненциальных средних в логарифмической шкале.

В исходном состоянии счетчик 15 сброшен в ноль, а в регистр 16 записан код начального приближения z,

Переключатели 2 и 3, задающие режим работы всего устройства, на все время работы установлены соответственно в верхнее и нижнее положения ,

Работа устройства происходит итерационно, при этом каждая итератщя, как и ранее, состюит из двух тактов

Первый такт - переюиочатели 1 и 4 вновь в верхнем положении. Производится интегрирование напряжения ZQ с выхода ЦАП 17 в течение интервала времени Т

Хр гЧ1+Ы) k

е ° dt +/з

Аналоговый запоминающий элемент 12 находится в режиме хранения старо- .го значения. Импульсы ПАЧ 13 через открытый ключ 14 (в течение всего первого такта) поступают в счетчик 15, образуя новый код z/.,.

Второй такт - переключатели 1 и 4 переводятся в нила1ее положение. Производится интегрирование (по суммирующему входу блока i 1) измеряемого входного сигнала в течение того

же интервала времени Т

Т

х.| X - v|(1-i-cL) k I dt Т ;tt) о

- (1 + oL) k е dt(7)

где X

- повое, улучшенное приближение на выходе интегратора 11.

Аналоговьй запоминающ-Уй элемент 12 открыт - выходное напряжение интегратора 11 непрерывно переписывается в блок 12. По .окончании второг такта.(и одной итерации в целом) на выходе ПАЧ 13 получаем новое, уточненное значение частоты

Вторая итерация проводится полностью аналогично первой.

Первьй такт - переютючатели 1 и 4 в верхнем положении. Код z, из счетчика 15 переписьюается в регис 16, после чего импульсом дифференциальной цепочки 24 счетчик 15 сбрсывается в ноль. Производится ин

тегрирование напряжения z,, с выхода ЦАП 17 в течение интервала времени Т

f-,

dt о

Импульсы ПНЧ 13 через ключ 14 поступают в счетчик 15, образуя новый

(1+с) k е dt +р1

f

код z

2

Второй такт - переключатели 1 и 4 переводятся в нижнее положение. Производится интегрирование входного сигнала в течение интервала времени Т

X

. (1+oi) k j

f x(t) -.0 - d+of) k,, I e dt)

dt (8)

Аналоговый запоминающий элемент 12 открыт - выходное напряжение интегратора 1 1 в течение всего второго такта непрерывно записываются в блок 12. На выходе ПНЧ 13 получаем новое уточненное значение частоты f г.

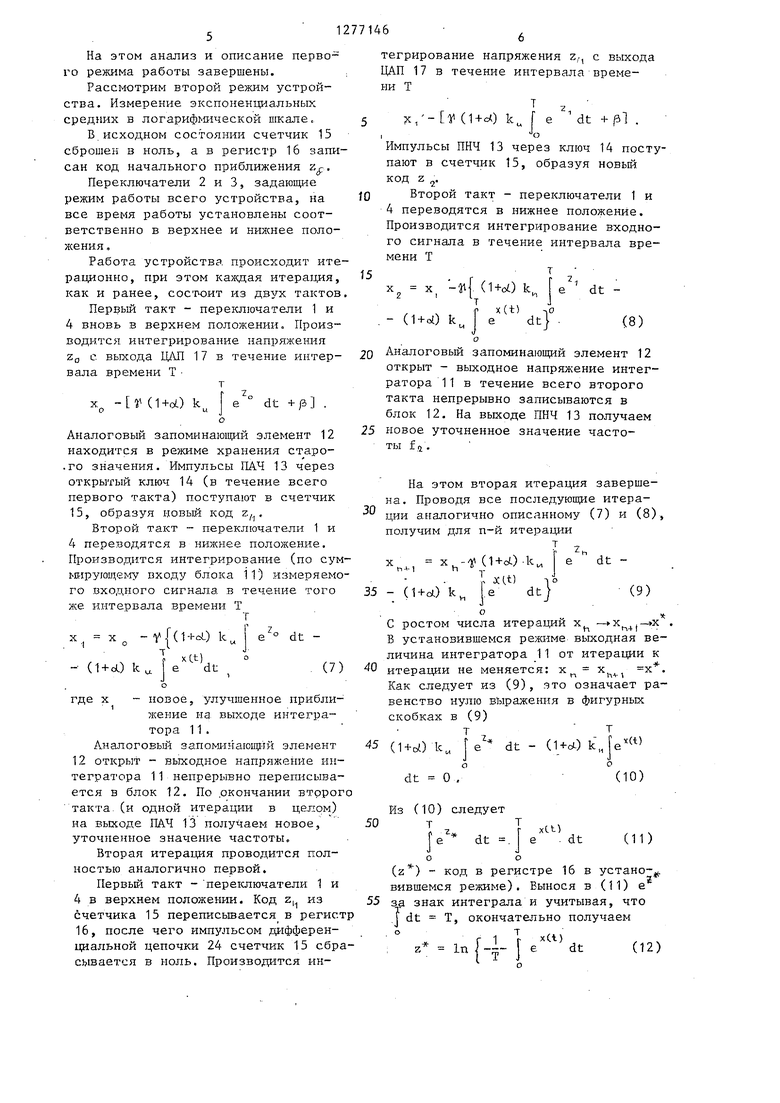

На этом вторая итерация завершена. Проводя все последуюшр;е итерации аналогично описанному (7) и (8), получим для п-й итерации

т

е dt ..-, -t(- x(t)

- (l+d.) k,

dt

(9)

о

.tИз

С ростом числа итераций х В установившемся режиме выходная величина интегратора 11 от итерации к итерации не меняется: х х х. Как следует из (9), это означает равенство нулю выражения в фигурньк скобках в (9) т .

(1+о1) k, dt О

dt - (1+с) kJe

Krt)

(10)

(10) т

следует

dt

I

J

xCt) e . dt

(z) - код в регистре 16 в устано- вившемся режиме). Вынося в (11) е за знак интеграла и учитывая, что , dt Т, окончательно получаем

° . Г 1 I

- {-Т

dt

(12)

Таким образом, в установившемся ре- име выходная величина всего устрой- cTBa равна экспоненциальному среднему значению x(t) в логарифмической шкале. При этом, как следует из (10), (11) (12), аддитивные и мультипликативные погрешности блоков исключаются и не входят в окончательный результат.

Третий режим. Измерение логарифмических средних в логарифмической шкале.

Вновь в исходном состоянии счетчик 15 сброшен в ноль, а в регистр 16 записан код начального приближения Zg .

Переключатели 2 и 3, задающие реясим работы всего устройства, на первом такте каждой итерации находятся соответственно в верхнем и нижнем положениях, а на втором такте каждой итерации меняю т свое положение на противоположное.

Первый такт - переключатели 1 и 4 в верхнем положении. Переключатели 2 и 3 соответственно в верхнем и нижнем положениях.

Производится интегрирование напряжения Z с выхода ЦАП 17 в течение интервала времени Т

т

х (1 + ol)-k I е dt +(В1 . , о

Импульсы ПНЧ 13 через ключ 14 поступают в счетчик 15, образуя новый .код Z/ .

Второй такт - переключатели 1 и 4 в- нижнем положении, переключатеи 2 и 3 соответственно в нижнем и верхнем. Благодаря такому положеию переключателей 2 и 3, операци- нньй усилитель 9 превращается в огарифмический усилитель .

Производится интегрирование (по суммирующему входу блока 11) изме- ряемого входного сигнала x(t) в течение интервала Т

Т х (1+d) k j е dt +(3 +

+ l.V( + } k f In x(t) dt + pi;

0 Т x d+ol) k f e dt т b - (1 + oL) k J In x(t) dt} (13)

о

течение всего второго такта выодное напряжение блока 11 перепи

сывается в аналоговый запоминающий элемент 12. На выходе ПНЧ 13 получаем новое, уточненное значение частоты f. .

На этом первая итерация завершена, вторая итерация проводится аналогично первой, в результате чего,

как следует из (13), получим

Т

X X,-Y|(I+OL) kj е dt - 4 о

-(1+oL) k In x(t) dt} (14)

0

Осуществляя все последующие ите раци1Г аналогично описанному, получим дпя п-й.итерации

,,, х,-г{(И-Ы) kj dt - т о

-(1+dl) k J In x(t) dtj (15)

1D.

В установившемся режиме x х X, a выражение в фигурных скобках в .(15) равно нулю

(1 + сО k Г е dt -(l+oC) k,, S . о «In x(t) dt 0(16)

Из (16) следует

|e dt f In x(t)-dt . (17)

о . о Отсюда, окончательно, получаем

z In l-f l dtj.(18)

Таким образом, в рассматриваемом третьем режиме работы выходная величина всего устройства равна логарифмическому среднему значению x(t) в логарифмической шкале. При этом, как следует из (16), (17) и (18), аддитивные и мультипликативные погрешности блоков вновь корректируются и не оказывают влияния на окон- чательный результат.

Группа Б - антилогарифмические режимы.

В этой режимов устройство обеспечивает измерение средних,экспоненциальных средних и логарифми- ческих средних величин постоянных и переменных сигналов произвольной формы. При этом получаемые результаты представлены в антилогарифмической (экспоненциальной) шкале.

Четвертый режим устройства. Измерение средних в антилогарифмической шкале.

Исходное состояние счетчика 15 и регистра 16 такое же, как и в преды- 5 дуащх режимах.

Переключатели 2 и 3, задающие режим работы всего устройства, устанавливаются в первом такте каж,цой итерации в нижнее и верхнее положение (соответственно), а на втором такте каждой итерации - оба переключателя в нижнем положен1-ш:.

Рассмотрим сразу п-ю итерацию (все предьщущие итерации проводятся аналогично) .

Первьй такт - переключатели 1 и 4 в верхнем положении, переключатели 2 и 3 соответственно в нижнем и верхнем положениях.

Операционный усилитель 9 становит ся логарифмическим усилителем. Производится интегрирование напряжения с выхода ЦАП 17

X. (Hd) k

In z dt + p .

Импульсы ПИЧ 13 через открытьм ключ 14 поступают в счетчик 15, образуя новый код z,| .

Второй такт - переключатели 1 и 4 в нижнем положении, переключатели 2 и-3 тоже в нижнем пололсении.

Операционный усилитель 9 работает как масштабный усилиталь (повторитель) . Производится интегрирование входного сигнала x(t) (по суммирующему входу блока 11)

т

Пятый режим устройства. Измерение экспоненциальных средних в анти логарифмической шкале.

Исходное состояние - счетчик 15 сброшен в ноль, в регистре 16 записан код начального приблинсения z,.

Переключатели 2 и 3, задающие режим работы всего устройства, уста 35 иавливаются в первом такте казкдой

итерации в нижнее и верхнее положе- вне (соответственно), а во втором такте меняют свое положение на про-тивоположное.

30

-lY(1+oL) k In Z dt -Hpl-i- 0- Рассмотрим п-ю нтераилю. h+1 h - и j n Первый такт - переключатели 1 и

Т ° (1+d.) k x(t) dt

4 т

4 в верхнем положении, переключатели 2 и 3 соответственно в нижнем и верхнем. Операпдонный усилитель 9 45 работает в режиме логарифмического усилителя.

f«n.r - 1 1 -- (l + ol) k, |x(t) dt} ° (19)

0

Полученный алгоритм описывает работу устройства на всех итерациях п 0,1,2,.., .На вьпсоде ПНЧ 13 получаем новое значение частоты.

С ростом п выходная величина интегратора 11 стремится к установившемуся значению х . В установившемся режиме х х, х при этом, как следует из (19), выражение в фигурных скобках в (19) равно нулю

(1 + о() k, ) In z dt - (1+di) k,, :

n

« x(t) dt 0.

Из-(20) получаем

т т

(20)

In z dt x(t) dt

(21)

теперь, вынося In z за знак интеграла и учитывая, что f dt Т, окончательно имеем о f

jf. I J

z e

Т . antilnj--- x(t) dtj . (22)

0

5

Выражение (22) показывает, что выходная величина устройства в этом режиме работы равна интегральному среднему значению x(t) в антилогарифмической шкале. Как следует из (20), (21) и (22) аддитивные и мультипликативные погрешности блоков, как и ранее, корректируются и не входят в окончательный результат.

Пятый режим устройства. Измерение экспоненциальных средних в антилогарифмической шкале.

Исходное состояние - счетчик 15 сброшен в ноль, в регистре 16 записан код начального приблинсения z,.

Переключатели 2 и 3, задающие режим работы всего устройства, уста- 5 иавливаются в первом такте казкдой

итерации в нижнее и верхнее положе- вне (соответственно), а во втором такте меняют свое положение на про- тивоположное.

0

4 в верхнем положении, переключатели 2 и 3 соответственно в нижнем и верхнем. Операпдонный усилитель 9 работает в режиме логарифмического усилителя.

Производится интегрирование напрялсения z

с выхода ЦАП 17 Т

50

х, (1+Ю

In z dt +

.

Импульсы ПНЧ 13 поступают в счетчик 15, образуя новый код z.

Второй такт - переключатели 1 и в нижнем положении, переключатели 2 и 3 соответственно в верхнем и нижнем. Операционный усилитель 9 работает в режиме экспоненциального решающего усилителя.

11127714612

т Производится интегрирование вход- г (1+dl) k In z dt +P.

n „тлттотто v(

НОГО сигнала x(t)

т

Импульсы ГТНЧ 13 поступают в счетчик

г , J. ,alj.импульсы ИПЧ IJ nUCTyj

y-rv( 1+fj )k Iri z dt +PJ+.-,

1, h .; K j образуя код z,.

Т xtt)5 Второй такт - переключатели 1 и

+ 1У d + d; k j е dt +pj.д jg нижнем положении. Производится

9 Ринтегрирование входного сигнала x(t)

X X -f {(1+с() k In -т

.юХ I ) (23)10 -.- . -I 1 1 P

(1+d)k f In x(t) +pl;

Алгоритм (23) описывает работу уст-J т

ройства на всех итерациях п О, 1, yf(+() j f In z dt J

у I rt

Ha выходе ПНЧ 13 новое значение 5 (+) j Г y. j-j (26)

частоты f . С ростом числа итера- J

ций n выходная величина блока 11Полученный алгоритм описьгоает растремится к установившемуся знача-боту устройства при всех ,1,2,.... ,

нию X . В пределе х х х , ас ростом числа итераций устройстиз (23) имеем2 во стремится к установившемуся режиТ му. В пределе х,, х, х , как

(1+d) k In z dt -следует из (26), выражение в фигур0 ,,4,ных скобках равно нулю

- (1+dl) k, I е О .т

о (l+rt) k f dt Отсюда следуетоТ т

In z dt

т x(i)- (l+ot)k ( In x(t) dt 0

1 e .dt. (24) i

г 1 г x(t) -). ла, получа

antiln -f- j e dtj . (25) 35

z e

т

antiln|- -| In x(t) dt , (27)

Отсюда

теперь, вынося In z 33 знак интег- т .

рала, окончательно получаем| In z dt In x(t) dt

. .i °

2 s Вновь вынося In z за знак интеграx(t) , т ла, получ.аем

EbUt)dt

I g

оZ e

Таким образом, код z в регистре 16 равен экспоненциальному среднему значению x(t) в антилогарифмической

ле. При этом погрешности блоков, соответствует логарифмическому

и ранее, корректируются.среднему значению в антилогарифмиШестой режим. Измерение логариф-ческой шкале. Заметим, что выражение

мических средних в антилогарифмичес-(27) представляет собой аналог средкой шкале. него геометрического для непрерывИсходное состояние всех блоков j uj сигналов

такое же, как и в других режимах.)t Chlx X xj

e e

Переключатели 2 и 3, задающие режим работы устройства на все время 50 v x,, х , . .. .,х . работы, устанавливаются соответственно в нижнее и верхнее положения.Как и в рассмотренных режимах, ад- Операционный усилитель 9 работает вл 1тивные и мультипликативные погреш- режиме логарифмического усилителя.ности блоков корректируются и не Рассмотрим п-ю итерацию. еевходят в окончательный результат

Первый такт - переключатели 1 и(27) .

4 в верхнем положении. .Группа В - линейные режимы.

Производится интегрирование на-В этой группе режимов устройстпряжения Zr, с выхода ДАЛ 17во обеспечивает измерение средних,

Импульсы ГТНЧ 13 поступают в счетчик

импульсы ИПЧ IJ nUCTyj

.-,

13 экспоненциальных средних и логарифмических средних значений постоянны и переменных сигналов произвольной формы. При этом получаемые результаты представлены в обычной (линейной) шкале.

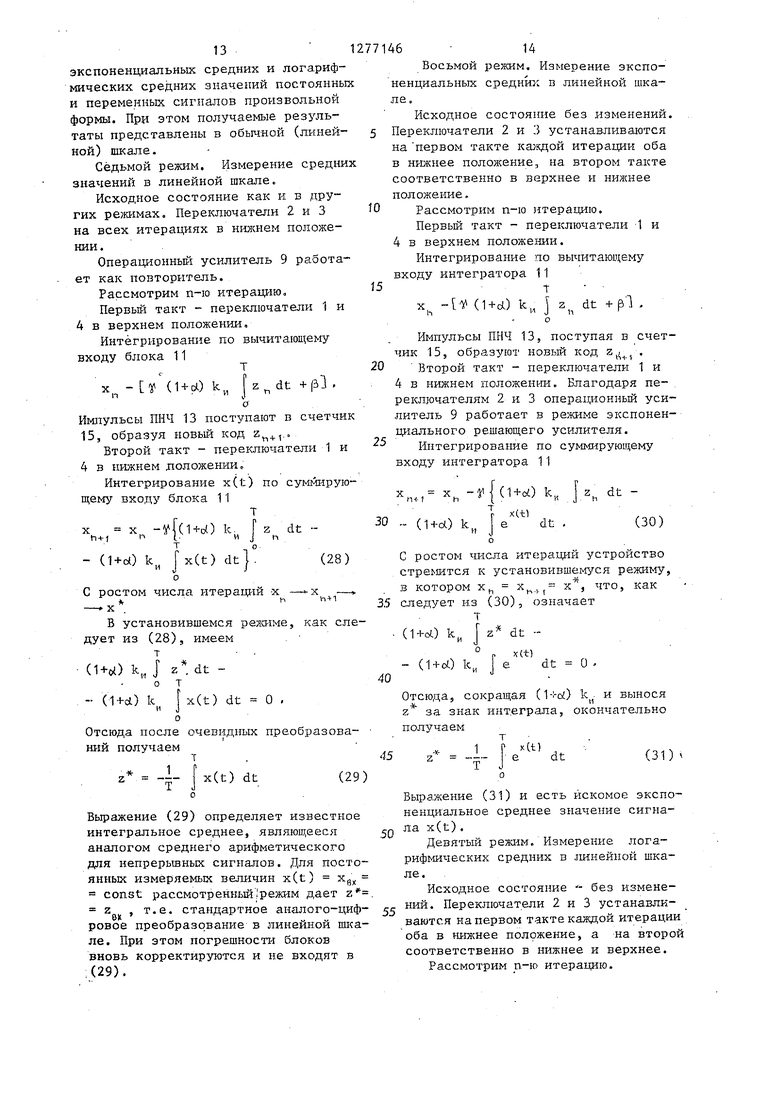

Седьмой режим. Измерение средни значений в линейной шкапе.

Исходное состояние как и в других регкимах. Переключатели 2 и 3 на всех итерациях в нилшем положении.

Операционньш усилитель 9 работает как повторитель.

Рассмотрим п-ю итерацию

Первый такт - переключатели 1 и 4 в верхнем положении.

Интегрирование по вычитаюЕ еку входу блока 11

т

х - (1 + pL) k,

z dt + (bl .

мпульсы ПНЧ 13 поступают в счетчик 15, образуя новьй код z,..

Второй такт - переключатели 1 и в нижнем доложении.

Интегрирование x(t) по суммируюему входу блока 11

Т X х, -у(1-«-с) k. Z dt h + ) 1 I- и J n

- (1+Ы) k, Jx(t) dt}° (28) о

С ростом числа итераций х -

hи+1

- X

В установившемся релдаме, как следует из (28), имеем

т .

(1+ы) k 2 dt о Т

- (1+d) k f x(t) dt О ,

Отсюда после очевидных преобразований получаем

, - 1

2 - -5x(t) dt

(29)

Выражение (29) определяет известное интегральное среднее, являющееся аналогом среднего арифметического для непрерывных сигналов. Для постоянных измеряемых величин x(t) Xg,, const рассмотренный дает z.

50

Выражение (31) и есть искомое экспоненциальное среднее значение сигнала x(t) .

Девятый режим. Измерение логарифмических средних в Jшнeйнoй шкале.

Исходное состояние - без изменеZ , т.е. стандартное аналого-циф- 55 ™ Переключатели 2 и 3 устанавлировое преобразо.ванне в линейной шкале. При этом погрешности блоков вновь корректируются и не входят в :(29).

ваются на первом такте каждой итерации оба в шгжнее положение, а на второй соответственно в нижнее и верхнее. Рассмотрим п-ю итерацию.

O

5

14

Восьмой режим. Измерение экспоненциальных среднике в линейной шкале.

Исходное состояние без изменений. Переключатели 2 и 3 устанавливаются на первом тг1кте кшэдой итерации оба в нижнее пололсение., на втором такте соответственно в верхнее и нилснее положение,

Рассмотрим п-ю итерацию.

Первый такт - переключатели 1 и 4 в верхнем положении.

Интегрирование по вычитающему входу интегратора 11

Т

X (l+d) k,, z dt + В 1 ,

h J

Импульсы 13, поступая в счетчик 15, образуЕот новый код z .

Второй Такт - переключатели 1 и 4 в нижнем положении. Благодаря переключателям 2 и 3 Операционньш усилитель 9 работает в режиме экспоненциального решающего усилителя.

Интегрирование по суммирующему

входу интегратора 11 (1+ci) k,.

n.1 h

dt

- (1+d) k J e

xC-t)

dt

(30)

С ростом числа итераидй устройство стремится к ycтaнoвившeI I cя режиму, в котором х x,j К, что, как следует из (30), означает Т

(1+oi) k J z dt ° p (t) - (1+ci) k.

dt О .

Отсюда, сокращая (1-:-ы) k и вынося г за знак интеграла, окончательно

получаем

т

x(tl

dt

(31)

о

50

Выражение (31) и есть искомое экспоненциальное среднее значение сигнала x(t) .

Девятый режим. Измерение логарифмических средних в Jшнeйнoй шкале.

Исходное состояние - без измене ™ Переключатели 2 и 3 устанавливаются на первом такте каждой итерации оба в шгжнее положение, а на второй соответственно в нижнее и верхнее. Рассмотрим п-ю итерацию.

10

15

151277146

Первьй такт - переключатели 1 и в верхнем положении. Интегрироваие по вычитающему входу интегратоа 11

т

- (1 + ) k. f z, dt ч-р ,

о

мпульсы ПНЧ 13 образуют в счетчике 5 новый код z .

Второй такт - переключатели 1 и в нижнем положении.Операционный силитель 9 благодаря переключатеям 2 и 3 переведен в режим экспоенциального усилителя.

Интегрирование по суммирующему

ходу блока .11

т

.., п (Но ) k г dt - т J

(1+d) k J In x(t) dt j . (31)

о

з (31) для установившегося режима аботы устройства получаем т .

1.+d) k г z dt J т

(1 + Ы) k I In x(t) dt 0 .

о тсюда, после очевидных упрощений,

кончательно получаем т

Z -1- f In x(t) dt , (32)

20

25

30

ном дом ты вых но жен сче рог дом вьк пре пул шин вых хро сое и у пом .щ и рен ден шта чет ный и и нен гов мой соо го вхо мас вхо лит чат сое го мас кот мир дом нен чат сое экс мас кот пер вход циф неи усил пот хрон вход чате гово вход мяти

Заметим, что аддитивные и мультипликативные погрешности блоков внов корректируются и не оказывают влияния на окончательньй результат.

Таким образом, как следует из приведенного описания режимов рабо- ты, устройство обеспечивает измерение девяти различных интегральных характеристик постоянных и переменных сигналов произвольной формы, -В числе которых среднее (интегральное. экспоненциальное среднее и логарифмическое среднее входных измеряемых сигналов. При этом результат измерений может быть представлен в любой из трех (выбираемых по желанию) шкал - линейной, логарифмической и антилогарифмической.

Формула изобретения

1. Логарифмический аналого-цифровой преобразователь, содержащий-первый переключатель, подключенный-первым сигнальным входом к информацион16

10

15

20

25

30

35

0 с

0

5

ному входу преобразователя, а выходом - к входу форшфователя экспоненты, аналоговый запоминающий элемент, выход которого через последовательно соединенные преобразоватепь напряжение - частота и ключ соединен со счетным входом счетчика, выход которого соединен с информационным входом регистра памяти, соединенного вькодом со входом цифроаналогового преобразователя, формирователь импульсов, вход которого соединен с шиной напряжения питающей сети, а выход - с тактовым входом блока син- хронй зации, первый выход которого соединен с управляющим входом ключа и управляющим входом аналогового запоминающего элемента, отличаю- .щ и и с я тем, что, с целью расши- рения области применения, в него введены логарифмируюш:ир 1 диод, два масштабных резистора, второй, третий и четвертый переключатели, операхщон- ный усилитель, масштабный усилитель и интегратор, выход которого соединен с информационным входом аналогового запоминающего элемента, а прямой и инверсный входы соединены с соответствующими выходами четвертого переключателя, информационный вход которого соединен с выходом масштабного усилителя, соединенного входом с выходом операционного усилителя и выходом третьего переключателя, сигнальные входы которого соединены с катодом логарифмического диода и первым выводом второго масштабного резистора, второй вывод которого соединен с анодом логарифмирующего диода и инвертирующим входом операционного усилителя, соединенного с выходом второго переключателя j сигнальные входы которого соединены с выходом формирователя экспоненты и первым выводом первого масштабного резистора, второй вывод которого соединен с выходом первого переключателя, второй сигнальный вход которого соединен с выходом цифроаналогового преобразователя, неинвертирующий вход операционного усилителя подключен к шине нулевого потенциала, первый выход блока синхронизации подключен к управляющим входам первого и четвертого переключателей, управляющему входу аналогового запоминающего элемента и входу разрешения записи регистра памяти, второй, третий и четвертый .выХоды блока синхронизации подключены Соответственно к входу обнуления

счетчика, управляющим входам второго

и третьегр переключателей.

2, Преобразователь по п.1, о т - и и ч а ю щ и и с- я тем, что блок синхронизации содержи т регистр памяти, два элемента И-ИЛИ-НЕ и дифференцирующую цепочку, счетный вход триггера подключен к тактовому входу блока синхронизахщи, а прямой выход является первьм выходом блока синхронизации, подключен к первым

Составитель И.Зайцев Редактор А.Гулько ТехредМ„Ходанич Корректор ,М.Самборская

Заказ 6669/44 . Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва,, Ж-355 Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

входам первого и второго элементов И-ШМ-НЕ и через диф1|)еренцирующую цепочку к второму выходу блока синхронизации, инверсный выход триггера подключен к вторым входам первого и второго элементов И-ИЛИ-НЕ, третьи и четвертые входы которых соединены соответственно с первым, вторым и третьим, четвертым выходами регистра памяти, выходы первого и второго элементов И-ИЛИ-НЕ являются соответственно третьим и четвертым выходами блока синхронизагщи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель напряжения | 1984 |

|

SU1239606A1 |

| Цифровой омметр | 1983 |

|

SU1129553A2 |

| Цифровой омметр | 1982 |

|

SU1046707A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ПРОМЕЖУТОЧНЫМ ПРЕОБРАЗОВАНИЕМ В ЧАСТОТУ | 1990 |

|

RU2007029C1 |

| Цифровой измеритель RLC-параметров | 1986 |

|

SU1337820A1 |

| Устройство для вычисления диаграмм разрежения индикаторов | 1978 |

|

SU792264A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2038694C1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1730722A2 |

| Устройство для настройки регуляторов | 1980 |

|

SU938256A1 |

| Цифровой измеритель RLC-параметров | 1986 |

|

SU1357874A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано, в частности, в информационно-измерительных и управляющих системах для получения цифрового значения логарифма входного напряжения. Целью изобретения является расширение области применения. Работа преобразователя происходит итерационно (циклически),при этом каждая итерация всегда состоит из двух тактов, Ъ зависимости от программы коммутации двухпозиционнык переключателей, Написанной в регистр памяти блока синхро- дазации, преобразователь может работать в девяти различных режимах. 1 з.п. ф-лы, 1 ил. I (Л 1C 4 О5

| Устройство для оценки дисперсии нецентрированного случайного процесса | 1973 |

|

SU484527A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Логарифмический аналого-цифровойпРЕОбРАзОВАТЕль | 1979 |

|

SU840947A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-15—Публикация

1985-05-06—Подача