Изобретение относится к приборостроению, в частности к системам передачи цифровой информации, и предназначено для использования в многоабонентных системах обмена цифровой информацией.

Целью изобретения является расши-. 1рение области применения устройства путем обеспечения возможности передачи сигналов по стандартному каналу

связи. 1

10

лов информации от первых и второго входов устройства в сдвиговый регистр 14.

Специального сигнала о прекращении подачи последовательного кода, в канал связи 5 не требуется, так как работа устройства приостанавливается с прекращением поступления на его третий и пятый входы синхросигналов .

Длительность сигнала синхронизации, поступающего на первые входы элементов И 21 и 22, определяется быстродействием элементной базы, Дли20

30

На чертеже приведена функциональная схема устройства.

Устройство содержит первый преобразователь кода 1, коммутатор 2, вто- 5 тельность этого сигнала должна быть рой преобразователь кода 3, формиро- не менее времени прохождения инфор- (ватель сигнала 4, канал связи 5, блок мации через группы элементов И 11 и управления 6,12, кодер 13 и записи кода в сдвиговый регистр 14.

Стробирование информации на входе сдвигового регистра 14 не требуется, поскольку фактически стробирование осуществляется на группах элементов И 11 и 12. Информация на первые входы устройства поступает в виде потенциалов и опрашивается импульсом синхронизации, проходящим с третьего входа устройства через элементы И 21 и 22. Запись информации в сдвиговый регистр 14 и в регистр 17 производится парафазным сигналом, воздействующим на установочные входы разрядов регистра Установка в ноль и Установка в единицу. Формирование 35 парафазного сигнала осуществляется на группах элементов И 11 и 12 и ко- дере 13.

Устройство работает следующим образом.

40 Режим передачи информации без сжатия определяется работой стандартного канала связи. По этому каналу информация передаётся двухчастотным (двухинтервальным) сигналом с двумя 45 фиксированными уровнями, при этом отношение минимального интервала к максимальному интервалу между переключениями сигнала с одного уровня на другой составляет 1:2. ко- 50 довой единицы передается по каналу связи переключением в середине интервала передачи разряда с верхнего уровня на нижний, а кодовый ноль - переключением с нижнего уровня на 55 верхний.

В связи с этим при передаче непрерывных последовательностей из нулей или из единиц на границах интерПервый преобразователь кода 1 содержит элементы совпадения 7-10. Коммутатор содержит первую группу элементов И 11, вторую группу элементов И 12 и кодер 13.

Второй преобразователь кода 3 содержит сдвиговый регистр 14, формиро- ватель,обратной связи 15, мультиплексор 16 и регистр 17. Формирователь сит нала 4 содержит элемент И 18 и счетный триггер 1S. Блок управления 6 содержит элемент НЕ 20 и первый и второй элементы И 21 и 22.

Устройство работает в системе многоабонентной связи во взаимодействии с другими устройствами этой системы. Поэтому синхронизирующие сигналы, поступающие на вход элементов И 21 и 22 (третий и четвертый входы устройства) , а также на первые входы сдвигового регистра 14 и элемента И 18 (пятый вход устройства), формируются во внешнем синхронизаторе и поступают на устройство.

Синхросигнал, поступающий на входы элементов И 21 и 22 (третий вход устройства) , является стартовым в работе устройства. По этому сигналу группа разрядов информации, подлежащая передаче, в конечном итоге записывается в сдвиговый регистр 14 по третьим его входам. Далее, в паузе между стартовыми импульсами, которые поступают периодически в течение всего времени передачи информа1дии, на пятый вход устройства, на первые входы сдвигового регистра 14 и элемента И 18 поступают восемь импульсов. По фазе эта пачка импульсов задержана на время прохождения сигна

лов информации от первых и второго входов устройства в сдвиговый регистр 14.

Специального сигнала о прекращении подачи последовательного кода, в канал связи 5 не требуется, так как работа устройства приостанавливается с прекращением поступления на его третий и пятый входы синхросигналов .

Длительность сигнала синхронизации, поступающего на первые входы элементов И 21 и 22, определяется быстродействием элементной базы, Длительность этого сигнала должна быть не менее времени прохождения инфор- мации через группы элементов И 11 и 12, кодер 13 и записи кода в сдвиго

валов производятся дополнительные переключения сигнала с одного уровня на другой. Исходная информация в виде- четырехразрядного параллельного кода поступает с первых входов устройства на первые входы первого преобразователя 1, на второй вход кторого поступает также сигнал с второго выхода формирователя сигнала 4 При этом сигнал синхронизации (третий вход усрройства) сопровождающий код информации, поступает на первый вход блока управления 6. Поскольку сигнал о работе в режиме уплотнения на четвертом входе устройства отсутствует, то сигнал сопровождения проходит через второй элемент И 22 блока управления 6 на опрос первой группы элементов 11 в коммутаторе 2. Одновременно этот же сигнал поступает на четвертый вход кодера 13.

В первом преобразователе 1 код исходной-информации (первые входы преобразователя 1) парами разрядов . совместно с информацией о коде пос- леднего разряда предыдущей четырехразрядной группы (второй вход преобразователя 1) поступает на четыре элемента совпадения 7-10. В результате на выходах этих элементов и. еле- довательно, на выходе первого преобразователя 1 формируется код, содержащий единицы, в разрядах для которых в исходном коде выполянется условие совпадения его значения со зна- чением предьщущего разряда. Сформированный код с выхода первого преобразователя 1 проходит на третьи входы коммутатора 2 и далее на первые (информационные) входы первой группы элементов И 11. Поскольку на второй (управляющий) вход этой группы элементов И 11 поступает импульс сопровождения информации, то сформирован

ный код проходит на кодер 13. В коде- ра 13 коммутатора 2. На четвертом

ре 13 код информации совместно с импульсом сопровождения, поступающим на четвертый ее вход, преобразуется таким образом, что на его выходе сборки образуется одиннадцатиразряд- ньш код, содержащий во всех четных разрядах, а также в 9 и 11 разрядах кодовые единицы, а в 1,3,5 и 7 разрядах - кодовые сигналы, соответвходе устройства при этом установл сигнал логической единицы.

Таким образом, код входной инфо мации, минуя блок подготовки кода и первую группу элементов И 11 ком татора 2, сразу через вторую групп элементов И 12 проходит на кодер 1 на выходе которого образуется один надцатиразрядный код. В этом коде.

ствующие коду, поступившему из блока , в первом, третьем, пятом и седьмом

подготовки кодов 1. Полученный код с выходов коммутатора 2 проходит на . первые и вторые входы преобразоватеразрядах образуются кодовые единицы, во втором и восьмом - кодовые нули, а в остальных код, соответ10

5

20

25зо,,

2771624

ля кода 3, где первые выходы коммутатора 2 записываются в сдвиговый регистр 14 по третьим его входам, а три оставшихся разряда (вторые выхо- 5 ды коммутатора 2) - в регистр 17. В результате под воздействием сигналов с выходов разрядов регистра 17 мультиплексор 16 обеспечивает подключение к четвертому входу сдвигового регистра 14 (последнего разряда) выход предыдущего разряда этого же регистра.

Таким образом, по мере поступления на первый вход второго преобразователя- кода 3 импульсов синхрочастоты с пятого входа устройства на его выходе будет формироваться последовательный восьмиразрядный потенциальный код. Этот код поступает на второй вход формирователя сигнала 4, где уже в виде импульсного кода с выхода элемента И 18 поступает на вход счетного триггера 19, и на первом выходе триггера 19 при его переключении по

каждой кодовой единице образуется требуемый сигнал, который и передается в канал связи.

В передачи информации со сжатием для канала связи также формируется в конечном итоге сигнал, обладающий теми же временными характеристиками, что и сигнал информации, передаваемой без уплотнения.

В этом режиме на первые входы и на второй вход устройства исходная информация поступает в виде пятиразрядного параллельного кода. Сигнал синхронизации с третьего входа устройства, сопровождающий код информации, при этом пройдет через блок управления и поступит на его первый выход, откуда далее пройдет на третий (управляющий) вход второй группы элементов И 12 и на третий вход кодевходе устройства при этом установлен сигнал логической единицы.

Таким образом, код входной информации, минуя блок подготовки кода 1 и первую группу элементов И 11 коммутатора 2, сразу через вторую группу элементов И 12 проходит на кодер 13, на выходе которого образуется одиннадцатиразрядный код. В этом коде.

в первом, третьем, пятом и седьмом

разрядах образуются кодовые единицы, во втором и восьмом - кодовые нули, а в остальных код, соответ$1

ствующнн коду входной информации. При этом в 9,10 и 11 разрядах образуются сигналы, соответствующие инверсному коду соответствующих разрядов исходной информации.

Образованный таким образом код с первых и вторых выходов коммутатора 2 поступает во второй преобразователь 3, где записывается в сдвиговый регистр 14 и в регистр 17. В ре- зультате под действием сигналов с выходов регистра 17 мультиплектор 16 обеспечивает необходимое подв:лю- чение разрядов. -К входу записи выходного (последнего) разряда сдвиго- вого регистра 14 подключается при этом выход либо один из предыдущих семи разрядов этого же регистра,, второй, четвертые и третий его выходы, либо выход формирователя сигнала об- ратной связи 15 .

Формирователь сигнала обратной связи 15 обеспечивает формирование из сигналов младшего (третий выход сдвигового регистра 14) и предпослед него разрядов (второй его выход) сдвигового регистра 14 сигнала, соответствующего кодовой единице, когда в предпоследнем разряде сдвигового регистра также находится кодовая единица либо кодовый ноль в младшем разряде.

В результате по мере поступления на вход второго преобразователя кода 3 импульсов синхрочастоты на его вы- ходе будет формироваться последовательный Потенциальный восьмиразрядный код.

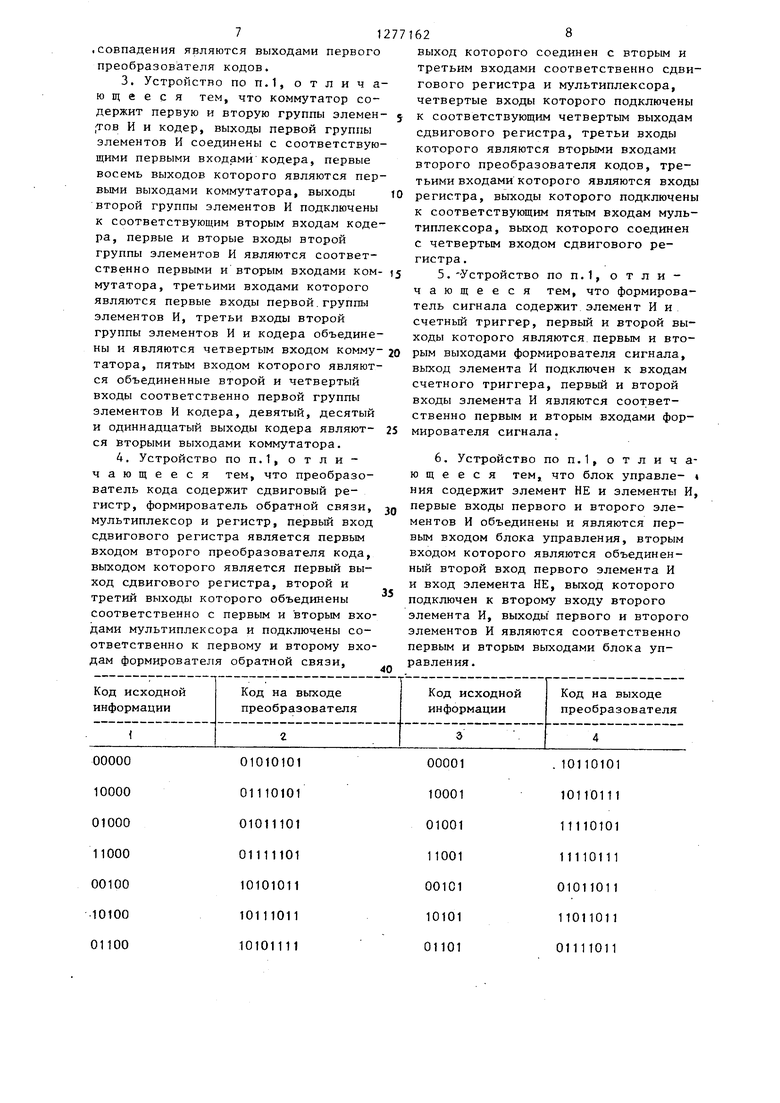

Код, получаемый на выходе преобразователя 3, в зависимости от исходно го пятиразрядного кода, поступающего на вход устройства, приведен в таблице .

Потенциальный последовательный код с выхода второго преобразователя кода 3 поступает на второй вход формирователя сигнала 4, где формируется сигнал, поступающш в канал связи 5.

Таким образом, предлагаемое устройство обеспечивает передачу цифро- вой информации по стандартному каналу связи как в режиме стандартного формирования сигнала передачи, так и в режиме передачи информации с уплотнением. При этом информационная пропускная способность-канала связи

626

увеличивается на 0,25 его номинальной величины.

Формула изобретения

1. Устройство для передачи цифровых сигналов с режимом сжатия, содержащее коммутатор, блок управления, формирователь сигналов и канал связи отличающееся тем, что, с целью расширения области применения устройства путем обеспечения возможности передачи сигналов по стандартному каналу связи, в него введены преобразователи кода, первые входы первого преобразователя кода объединены с соответствующими первыми входами коммутатора и являются первыми входами устройства, второй вход коммутатора является вторым входом устройства, первый и второй входы блока управления являются соответственно третьим и четвертым входами устройства, первый вход второго преобразователя кода объединен с первым входом формирователя сигнала и является пятым входом устройства, выходы первого преобразователя кодов подключены к соответствующим тре- тьим входам коммутатора, четвертый и пятый входы которого соединены соответственно с первым и вторым выходами блока управления, первые и вторые выходы коммутатора подключены соответственно к вторым и третьим входам второго преобразователя кода, выход которого соединен с вторым входом формирователя сигнала, первый и второй выходы которого подключены соответственно к каналу связи и второму входу первого преобразователя кода.

2. Устройство по п.1, о т л и ч а ю щ е ё с я тем, что первый преобразователь кода содержит элементы совпадения, объединенные попарно первые входы первого и второго элементов совпадения, второй вход второго элемента совпадения и первый, вход третьего элемента совпадения, второй вход третьего элемента совпадения и первый вход четвертого элемента совпадения, а также второй вход четвертого элемента совпадения являются первыми входами первого преобразователя кода,.вторым входом которого является второй вход первого элемента совпадения, выходы всех элементов

71

.совпадения являются выходами первого преобразователя кодов.

3.Устройство по П.1, отличающееся тем, что коммутатор содержит первую и вторую группы элемен froB И и кодер, выходы первой группы элементов И соединены с соответствующими первыми входами кодера, первые восемь выходов которого являются первыми выходами коммутатора, выходы второй группы элементов И подключены

к соответствующим вторым входам кодера, первые и вторые входы второй группы элементов И являются соответственно первыми и вторым входами ком мутатора, третьими входами которого являются первые входы первой.группы элементов И, третьи входы второй группы элементов И и кодера объединены и являются четвертым входом комму- татора, пятым входом которого являются объединенные второй и четвертый входы соответственно первой группы элементов И кодера, девятый, десятый и одиннадцатый выходы кодера являются вторыми выходами коммутатора,

4.Устройство по П.1, отличающееся тем, что преобразователь кода содержит сдвиговый регистр, формирователь обратной связи, мультиплексор и регистр, первый вход сдвигового регистра является первым входом второго преобразователя кода, выходом которого является первый выход сдвигового регистра, второй и третий выходы которого объединены соответственно с первым и вторым входами мультиплексора и подключены соответственно к первому и второму входам формирователя обратной связи.

jtO

15 20

25

30

5

162

выход которого соединен с вторым и третьим входами соответственно сдвигового регистра и мультиплексора, четвертые входы которого подключены к соответствующим четвертым выходам сдвигового регистра, третьи входы которого являются вторыми входами второго преобразователя кодов, третьими входами которого являются входы регистра, выходы которого подключены к соответствующим пятым входам мультиплексора, выход которого соединен с четвертым входом сдвигового регистра.

5. Устройство по П.1, отличающееся тем, что формирователь сигнала содержит элемент И и счетный триггер, первый и второй выходы которого являются первым и вторым выходами формирователя сигнала, выход элемента И подключен к входам счетного триггера, первый и второй входы элемента И являются соответственно первым и вторым входами формирователя сигнала.

6.Устройство по П.1, отличающееся тем, что блок управле- « ния содержит элемент НЕ и элементы И, первые входы первого и второго элементов И объединены и являются первым входом блока управления, вторым входом которого являются объединенный второй вход первого элемента И

и вход элемента НЕ, выход которого подключен к второму входу второго элемента И, выходы первого и второго элементов И являются соответственно первым и вторым выходами блока управления.

Заказ 6670/45 Тираж 515Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, А

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ПЕРЕДАЧИ ПОСЛЕДОВАТЕЛЬНОСТИ СИГНАЛОВ | 2005 |

|

RU2299474C2 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1988 |

|

SU1606996A1 |

| Система для передачи информации с двукратной фазовой манипуляцией сверточным кодом | 1982 |

|

SU1027748A1 |

| Устройство для редактирования | 1982 |

|

SU1117669A1 |

| Устройство для записи цифровой информации | 1989 |

|

SU1607008A1 |

| Устройство для обнаружения ошибок в блоках памяти | 1985 |

|

SU1249593A1 |

| Система передачи телевизионного сигнала с помощью дифференциальной импульсно-кодовой модуляции | 1983 |

|

SU1107342A2 |

| Устройство сопряжения | 1981 |

|

SU993240A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ И ПЕРЕДАЧИ СИГНАЛОВ | 2004 |

|

RU2282246C2 |

Изобретение относится к области приборостроения, в частности к системам передачи цифровой информации, и предназначено для использования в многоабонентных системах обмена цифровой информацией. Целью изобретения является обеспечение передачи цифровой информации с режимом сжатия по стандартному цифровому каналу связи. Информационные разряды подаются на первьй преобразователь кодов, состоящий из первого, второго, третьего и четвертого элементов совпадения, и на коммутатор. В состав коммутатора входит первая и вторая группы элементов И и кодер. Выходы коммутатора подключены ко входам второго преобразователя кода, состоящего из сдвигового регистра, формирователя обратной связи, мультиплексора и регистра. Выход второго преобразователя кода соединен со вторым входом формирователя - сигнала, к первому входу которого подключен вход битовой синхронизации устройства,, который также соединен с од- ним из входов второго преобразователя кода. Второй вькод формирователя сигнала подключен к одному из входов первого преобразователя кода, а первый - ко входу канала связи. Блок управления имеет два входа, являющиеся третьим и четвертым входами устройства, и содержит элемент НЕ и два элемента И. Выходы блока управления подключен ко входам коммутатора. Устройство имеет пять входов. Формирователь сигнала содержит элемент И и счетный триггер. 5 э.п. ф-лы, 1 ил. I (Л

| Устройство для передачи информации со сжатием | 1983 |

|

SU1091206A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Фремке А.В | |||

| Телеизмерения | |||

| Ы.: Высшая школа, 1975 с | |||

| Машина для удаления камней из почвы | 1922 |

|

SU231A1 |

Авторы

Даты

1986-12-15—Публикация

1985-02-08—Подача