Изобретение относится к области передачи-приема телеметрических сообщений в частности к проблеме кадровой синхронизации в этих сообщениях, может найти применение при ре- 5 шении задач дистанции метрирования с использованием псевдослучайных зондирующих сигналов, а также в системах многостанционного доступа при идентификации адресных полей в сооб- tO щениях различных пользователей.

Целью изобретения является повышение надежности работы устройства.

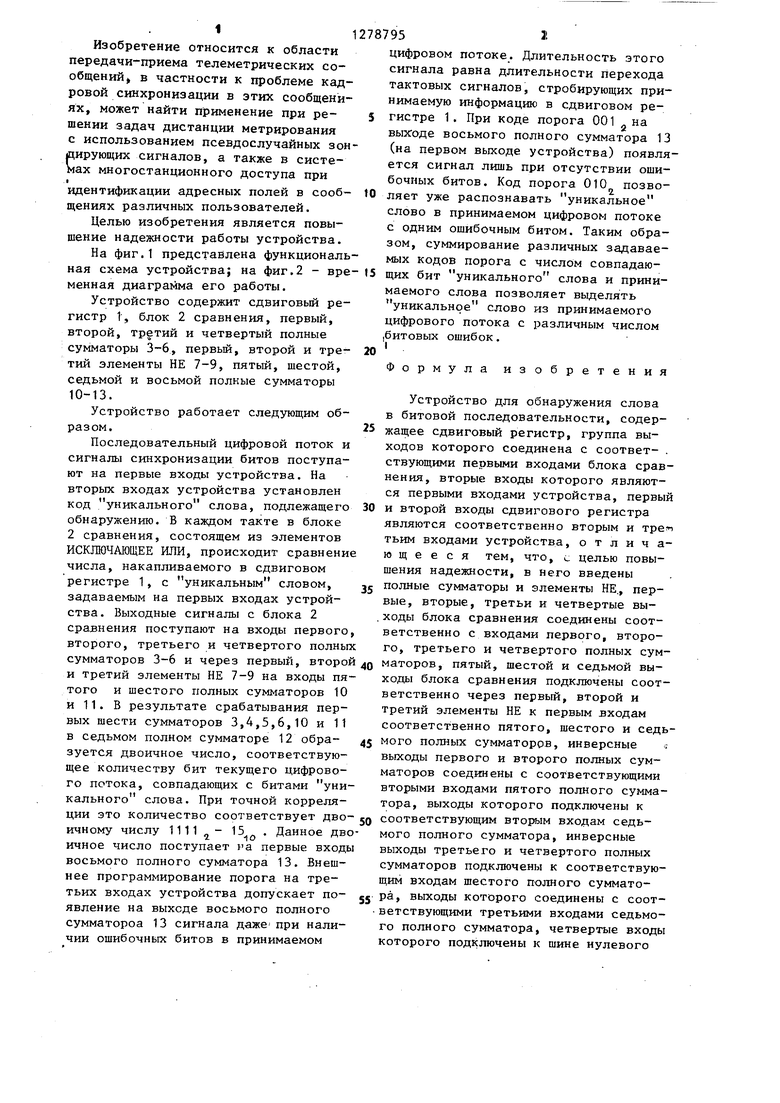

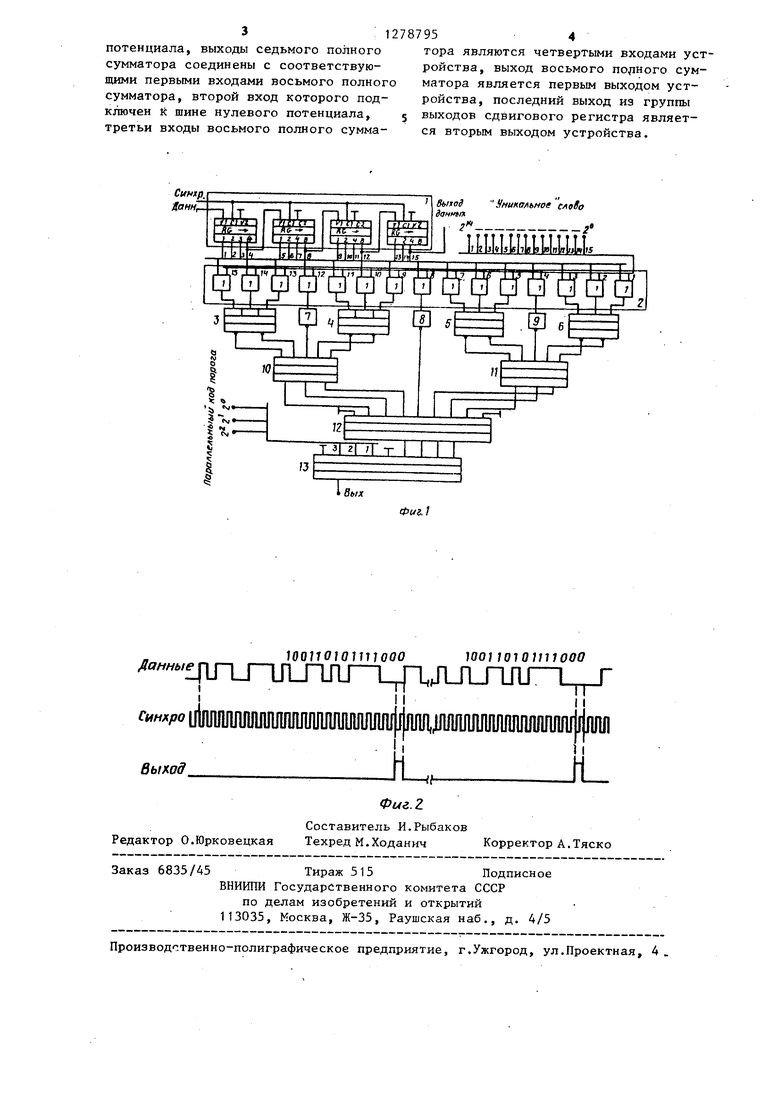

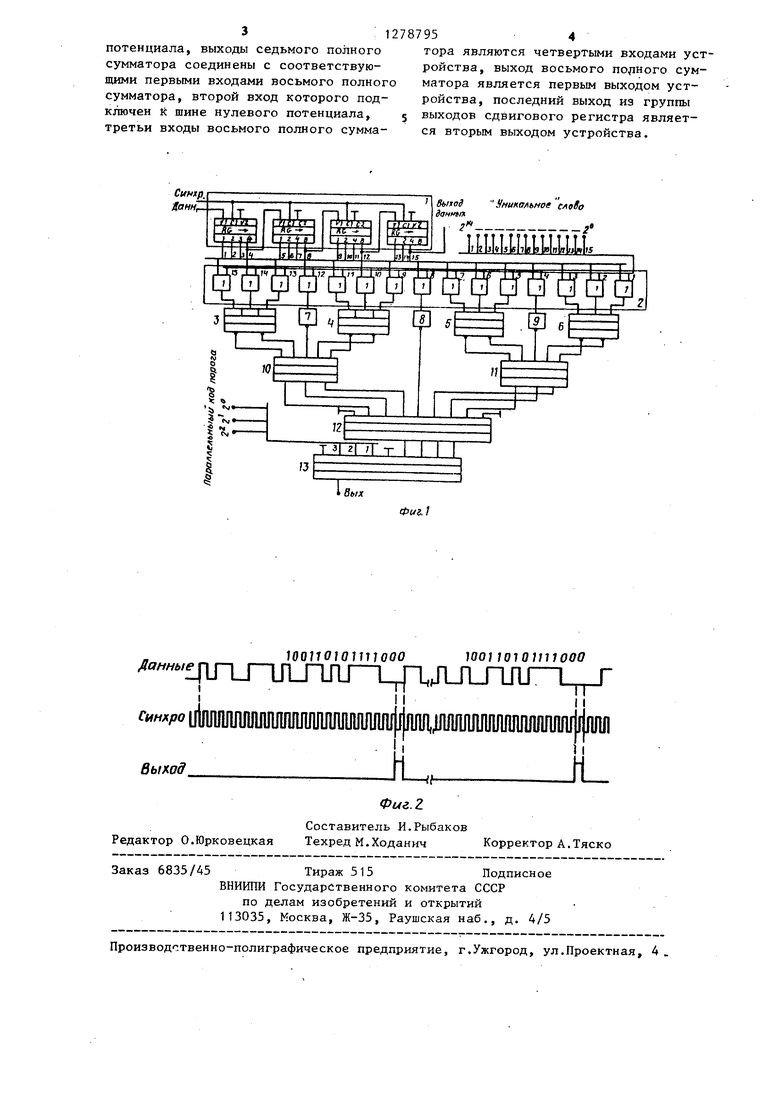

На фиг.1 представлена функциональная схема устройства; на фиг.2 - вре- |5 щих бит уникального менная диаграмма его работы.

Устройство содержит сдвиговый регистр 1, блок 2 сравнения, первый, второй, третий и четвертый полные сумматоры 3-6, первый, второй и тре- 20 тий элементы НЕ 7-9, пятый, шестой, седьмой и восьмой полные сумматоры 10-13.

Устройство работает следующим образом.

Последовательный цифровой поток и сигналы синхронизации битов поступают на первые входы устройства. На вторых входах устройства установлен код уникального слова, подлежащего обнаружению. В каждом такте в блоке 2 сравнения, состоящем из элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, происходит сравнение числа, накапливаемого в сдвиговом

цифровом потоке. Длит сигнала равна длитель тактовых сигналов, ст нимаемую информацию в гистре 1. При коде по выходе восьмого полно (на первом выходе уст ется сигнал лишь при бочных битов. Код пор ляет уже распознавать слово в принимаемом ц с одним ошибочным бит зом, суммирование раз мых кодов порога с чи

маемого слова позволя уникальное слово из цифрового потока с ра .битовых ошибок.

I

ормула изо

регистре 1, с уникальным словом,

Устройство для обн в битовой последовате

25 жащее сдвиговый регис ходов которого соедин ствующими первыми вхо нения, вторые входы к ся первыми входами ус

30 и второй входы сдвиго являются соответствен тьим входами устройст ющееся тем, что шения надежности, в н

35 полные сумматоры и эл вые, вторые, третьи и . ходы блока сравнения ветственно с входами го, третьего и четвер

35 полные сумматоры и элементы НЕ., первые, вторые, третьи и четвертые вы- . ходы блока сравнения соединены соответственно с входами первого, второго, третьего и четвертого полных сумзадаваемым на первых входах устройства. Выходные сигналы с блока 2 сравнения поступают на входы первого, второго, третьего и четвертого полных сумматоров 3-6 и через первый, второй д маторов, пятый, шестой и седьмой вы- и третий элементы НЕ 7-9 на входы пя- ходы блока сравнения подключены соот- того и шестого полных сумматоров 10 и 11. В результате срабатывания первых шести сумматоров 3,4,5,6,10 и 11 в седьмом полном сумматоре 12 образуется двоичное число, соответствующее количеству бит текущего цифрового потока, совпадающих с битами уникального слова. При точной корреляции это количество соответствует дво- JQ соответствующим вторым входам седь- ичному числу 1111 - 15 . Данное дво- мого полного сумматора, инверсные ичное число поступает va первые входы восьмого полного сумматора 13. Внешветственно через первый, второй и третий элементы НЕ к первым входам соответственно пятого, шестого и седь- 45 мого полных сумматоров, инверсные -. выходы первого и второго полных сумматоров соединены с соответствующими вторыми входами пятого полного сумматора, выходы которого подключены к

выходы третьего и четвертого полных сумматоров подключены к соответствующим входам шестого полного суммато- 55 ра, выходы которого соединены с соот- ветствующими третьими входами седьмого полного сумматора, четвертые входы которого подключены к шине нулевого

нее программирование порога на третьих входах устройства допускает появление на выходе восьмого полного сумматороа 13 сигнала даже при наличии ошибочных битов в принимаемом

щих бит уникального

цифровом потоке. Длительность этого сигнала равна длительности Перехода тактовых сигналов, стробирующих принимаемую информацию в сдвиговом регистре 1. При коде порога 001 на выходе восьмого полного сумматора 13 (на первом выходе устройства) появляется сигнал лишь при отсутствии ошибочных битов. Код порога 010 позволяет уже распознавать уникальное слово в принимаемом цифровом потоке с одним ошибочным битом. Таким образом, суммирование различных задаваемых кодов порога с числом совпадаюслова и принимаемого слова позволяет выделять уникальное слово из принимаемого цифрового потока с различным числом .битовых ошибок.

I

ормула изобретения

Устройство для обнаружения слова в битовой последовательности, содержащее сдвиговый регистр, группа выходов которого соединена с соответ- . ствующими первыми входами блока сравнения, вторые входы которого являются первыми входами устройства, первый

и второй входы сдвигового регистра являются соответственно вторым и тьим входами устройства, отличающееся тем, что, с целью повышения надежности, в него введены

полные сумматоры и элементы НЕ., первые, вторые, третьи и четвертые вы- ходы блока сравнения соединены соответственно с входами первого, второго, третьего и четвертого полных сумматоров, пятый, шестой и седьмой вы- ходы блока сравнения подключены соот- соответствующим вторым входам седь- мого полного сумматора, инверсные

д маторов, пятый, шестой и седьмой вы- ходы блока сравнения подключены соот- JQ соответствующим вторым входам седь- мого полного сумматора, инверсные

ветственно через первый, второй и третий элементы НЕ к первым входам соответственно пятого, шестого и седь- 45 мого полных сумматоров, инверсные -. выходы первого и второго полных сумматоров соединены с соответствующими вторыми входами пятого полного сумматора, выходы которого подключены к

д маторов, пятый, шестой и седьмой вы- ходы блока сравнения подключены соот- JQ соответствующим вторым входам седь- - мого полного сумматора, инверсные

выходы третьего и четвертого полных сумматоров подключены к соответствующим входам шестого полного суммато- 55 ра, выходы которого соединены с соот- ветствующими третьими входами седьмого полного сумматора, четвертые входы которого подключены к шине нулевого

312787954

потенциала, выходы седьмого полноготора являются четвертыми входами устсумматора соединены с соответствую-ройства, выход восьмого no iHoro сумщими первыми входами восьмого полногоматора является первым выходом устсумматора, второй вход которого под-ройства, последний выход из группы

ключен tc шине нулевого потенциала, 5выходов сдвигового регистра являеттретьи входы восьмого полного сумма-ся вторым выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Процессор | 1984 |

|

SU1247884A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Устройство для коррекции отказов в полупроводниковой памяти | 1982 |

|

SU1049981A1 |

| Устройство для формирования изображений кривых второго порядка на экране телевизионного приемника | 1988 |

|

SU1596376A1 |

| БОРТОВОЙ СПЕЦВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2522852C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП БИТ В БИНАРНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2020 |

|

RU2728957C1 |

| ПРИЕМНИК СИГНАЛОВ ШЕСТНАДЦАТИПОЗИЦИОННОЙ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МАНИПУЛЯЦИИ | 2004 |

|

RU2287225C2 |

| Устройство для обслуживания сообщений | 1983 |

|

SU1128256A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ ШЕСТНАДЦАТИПОЗИЦИОННОЙ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МАНИПУЛЯЦИИ | 2003 |

|

RU2249921C2 |

Изобретение относится к пробле-г ме кадровой синхронизации телеметрических сообщений и может найти применение в системах многостанционного доступа при идентификации адресных полей в сообщ€ ниях различных пользователей. Целью изобретения является повьшение надежности устройства. Последовательный цифровой поток и сигналы синхронизации битов поступают на первые входы устройства. На вторых входах устройства установлен код уникального слова, подлежащего обнаружению. В каждом такте в блоке сравнения происходит сравнение числа, накапливаемого в сдвиговом регистре, с уникальным словом, задаваемым на первых входах устройства. Выходные сигналы с блока сравнения поступают на входы первого, второго, третьего и четвертого полных сумматоров и через первый, второй и третий элементы НЕ на входы пятого и шестого полных сумматоров. В результате срабатывания первых шести полных сумматоров в седьмом полном сумматоре образуется двоичное число, соответствующее количеству бит текущего цифрового потока, совпадающих с битами уникаль- Щ ного слова. Данное двоичное число поступает на восьмой полный сумматор, где суммируется с кодом порога, задаваемого на третьих входах устройства. Код порога указывает максимально возможное число бит в цифровом потоке, которые могут не совпадать с соответствующими битами уникального слова. На выходе восьмого полного сумматора появляется сигнал в случае распознавания устройством уникального слова с различным числом ошибок. 2 ил. W го СХ) со ел

Унина ьное слово

К

ь

.

т 31 2| 71 т

I

/3

flatiHbie

looiioionuooo

WOJ 10101111000

innjnjUnJirn AJlJ Lr

IIIII

p 1ЛпШ1Ш1ШШ1ШПШ111Ш1 1ШиШ1ии

|ЩЩШи1 1ШШШ11иШ

f|lUUI

Bbtxoff

Фиг. 2

Составитель И.Рыбаков Редактор О.Юрковецкая Техред М.Ходанич

Заказ 6835/45Тираж 515Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4 .

WOJ 10101111000

III

|ЩЩШи1 1ШШШ11иШ

f|lUUI

I

Корректор А.Тяско

| Устройство для обработки измерительной информации с контролем достоверности | 1978 |

|

SU750540A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Лаврусевич В.В | |||

| Синхронизатор телеметрического формата и декоммутатор в наземной станции ЕТМС | |||

| Препринт ИКИ АН СССР | |||

| Пр,-177, М., 1974. | |||

Авторы

Даты

1986-12-23—Публикация

1985-04-29—Подача