Изобретение относится к радиотехнике и может быть использовано при демодуляции сигналов шестнадцатипозиционной квадратурной амплитудной манипуляции (КАМ-16), используемых в высокоскоростных системах спутниковой и радиорелейной связи.

Известен демодулятор сигналов шестнадцатипозиционной квадратурной амплитудной манипуляции, содержащий два фазовых детектора, два фильтра нижних частот, фазовращатель и два квантователя (см. патент РФ №2020767, МКИ 5 H 04 L 27/22, опубл. БИ №18, 30.09.94 г.) [1].

Недостатком известного демодулятора является то, что уровень сигнала КАМ-16 не подстраивается в процессе работы так, чтобы всегда оптимальным образом соответствовать уровням срабатывания квантователей. Между тем уровни срабатывания квантователей установлены равными (0; +1; -1) в каждом из каналов известного устройства именно в предположении об оптимальном уровне сигнала как на входе устройства, так и в каждом из каналов. Пороги квантователей образуют шестнадцать зон принятия решения для каждой точки сигнала КАМ-16 и, в том числе, если уровни сигналов на входах квантователей оказываются отличными от нормативных, зоны принятия решений оказываются сформированными неоптимально (отличными от критерия Котельникова-Зигерта [2]), что приводит к увеличению вероятности ошибки на выходе демодулятора и соответствующему снижению помехоустойчивости.

Известен также демодулятор сигналов шестнадцатипозиционной квадратурной амплитудной манипуляции, содержащий блок восстановления несущей, выход которого подключен ко второму входу первого фазового детектора и, через фазовращатель на 90° - ко второму входу второго фазового детектора, первый вход которого соединен с первым входом первого фазового детектора и является входом демодулятора, выходы первого и второго фазовых детекторов соединены, соответственно, с входами первого и второго фильтров нижних частот, при этом входы первого, второго, третьего, седьмого и восьмого компараторов соединены, а выходы седьмого и восьмого компараторов соединены с входами первого элемента ИЛИ, выход которого подключен к входу первого счетчика и первому входу второго элемента ИЛИ, выход и второй вход которого соединены, соответственно, с входом второго счетчика и входом третьего счетчика, который подключен к выходу третьего элемента ИЛИ, входы которого соединены с выходами девятого и десятого компараторов, входы которых соединены с входами четвертого, пятого и шестого компараторов, при этом выходы второго и пятого компараторов являются, соответственно, первым и вторым выходами демодулятора, выходы первого и третьего компараторов соединены, соответственно, с первым входом четвертого элемента ИЛИ и прямым входом первого элемента И, инверсный вход и выход которого соединены, соответственно, с выходом второго компаратора и вторым входом четвертого элемента ИЛИ, выход которого является третьим выходом демодулятора, четвертым выходом которого является выход пятого элемента ИЛИ, входы которого соединены, соответственно, с выходами шестого компаратора и второго элемента И, к прямому и инверсному входам которого подключены, соответственно, выходы четвертого и пятого компараторов (см. А.С. №2019051, МКИ 5 H 04 L 27/22, опубл. БИ №16, 30.08.94 г.) [3].

Недостатком известного демодулятора является низкая помехоустойчивость, обусловленная, как и в устройстве [1], тем, что уровень сигнала КАМ-16 не подстраивается на входах компараторов в процессе работы так, чтобы всегда соответствовать зонам принятия решений, установленным оптимально по критерию идеального наблюдателя.

Из известных технических решений наиболее близким к заявляемому объекту (прототипом) является демодулятор сигналов шестнадцатипозиционной квадратурной амплитудной манипуляции, содержащий блок восстановления несущей, выход которого подключен ко второму входу первого фазового детектора и, через фазовращатель на 90° - ко второму входу второго фазового детектора, первый вход которого соединен с первым входом первого фазового детектора и является входом демодулятора, выходы первого и второго фазовых детекторов соединены, соответственно, с входами первого и второго фильтров нижних частот, при этом входы первого, второго, третьего, седьмого и восьмого компараторов соединены, а выходы седьмого и восьмого компараторов соединены с входами первого элемента ИЛИ, выход которого подключен к входу первого счетчика и первому входу второго элемента ИЛИ, выход и второй вход которого соединены, соответственно, с входом второго счетчика и входом третьего счетчика, который подключен к выходу третьего элемента ИЛИ, входы которого соединены с выходами девятого и десятого компараторов, входы которых соединены с входами четвертого, пятого и шестого компараторов, при этом выходы второго и пятого компараторов являются, соответственно, первым и вторым выходами демодулятора, выходы первого и третьего компараторов соединены, соответственно, с первым входом четвертого элемента ИЛИ и прямым входом первого элемента И, инверсный вход и выход которого соединены, соответственно, с выходом второго компаратора и вторым входом четвертого элемента ИЛИ, выход которого является третьим выходом демодулятора, четвертым выходом которого является выход пятого элемента ИЛИ, входы которого соединены, соответственно, с выходами шестого компаратора и второго элемента И, к прямому и инверсному входам которого подключены, соответственно, выходы четвертого и пятого компараторов, первый, второй, третий и четвертый входы дешифратора подключены, соответственно, к первому, второму, третьему и четвертому выходам демодулятора, первый, второй, третий и четвертый выходы дешифратора соединены с соответствующими входами шестого элемента ИЛИ, выход которого соединен с первым входом четвертого счетчика, выход которого соединен с первым входом первого блока сравнения, второй вход которого соединен с выходом пятого счетчика, вход которого соединен с выходом седьмого элемента ИЛИ входы которого соединены, соответственно, с пятым, шестым, седьмым и восьмым выходами дешифратора, выход шестого счетчика соединен со вторыми входами четвертого, пятого и первого реверсивного счетчиков, первый и третий входы первого реверсивного счетчика соединены, соответственно, с первым и вторым выходами первого блока сравнения, выход первого реверсивного счетчика соединен с входом первого цифроаналогового преобразователя, первый вход и выход первого управляемого усилителя, соединены, соответственно, с выходом первого фильтра нижних частот и входом первого компаратора, первый вход и выход второго управляемого усилителя соединены, соответственно, с выходом второго фильтра нижних частот и входом четвертого компаратора (см. патент РФ №2198470, МПК 7 H 04 L 27/22, опубл. БИ №4, 10.02.2003 г.) [4] - прототип.

В устройстве-прототипе существуют специальные технические средства, позволяющие оптимизировать в процессе работы уровень сигналов на входах компараторов. Тем не менее, недостатком известного устройства является его низкая помехоустойчивость, обусловленная следующими факторами.

Автоматическое регулирование уровня сигналов на входах первого - десятого компараторов в известном устройстве основано на подсчете за некоторый выбранный интервал счета m количества сигнальных точек, отнесенных демодулятором к любой из четырех зон принятия решений, которые соответствуют входному сигналу с максимальной амплитудой. Аналогично подсчитывают за тот же интервал счета m количество сигнальных точек, отнесенных демодулятором к любой из четырех зон принятия решений, которые соответствуют входному сигналу с минимальной амплитудой. Сравнивая между собой количества сигнальных точек с максимальной и минимальной амплитудой в первом блоке сравнения, делают вывод о необходимости изменения или сохранения неизменным уровня сигналов на входах первого - десятого компараторов.

Сигнал управления с выхода первого реверсивного счетчика через первый цифроаналоговый преобразователь ЦАП) поступает на вторые (управляющие) входы первого и второго управляемых усилителей. Таким образом замыкается петля автоматического регулирования уровня входного сигнала.

При этом выбранный в прототипе способ регулирования уровня входного сигнала, основанный на сравнении частот попадания сигнальных точек в различные квадраты, является "грубым", поскольку он не чувствителен к положению сигнальных точек внутри соответствующих квадратов. Таким образом, в известном устройстве после достижения равенства количества подсчитываемых точек с максимальной и минимальной амплитудой, дальнейшая оптимизация их расположения внутри зон принятия решений по критерию Котельникова-Зигерта не осуществляется, что приводит к соответствующей потере помехоустойчивости.

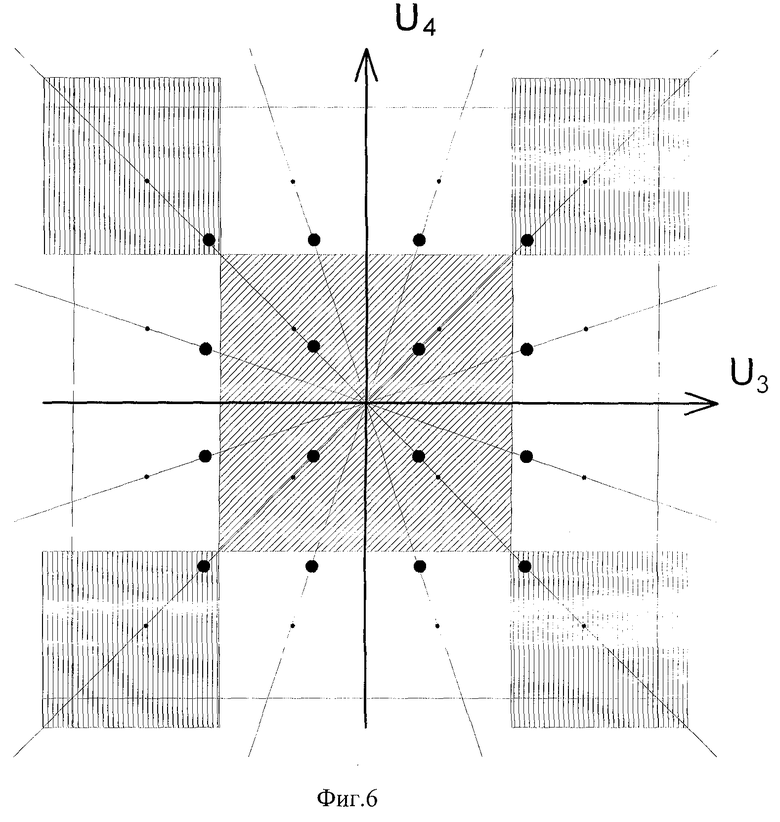

Используемые в известном устройстве специальные технические средства регулирования через первый ЦАП уровня сигнала на входе компараторов позволяют осуществлять лишь "грубую" (первоначальную) настройку на сигнал. В связи с этим в известном устройстве вероятна ситуация, при которой даже несмотря на выполненное регулирование уровня входного сигнала по выбранному критерию, сигнальные точки даже в отсутствие шума располагаются не в центрах своих зон принятия решений (см. фиг.6), что обуславливает низкую помехоустойчивость известного устройства при демодуляции сигналов КАМ-16.

Повышение помехоустойчивости демодуляторов КАМ-16 является важной задачей при создании систем связи, поскольку данная характеристика прямо связана с экономической эффективностью всей системы связи.

Технический результат - повышение помехоустойчивости демодуляции сигналов КАМ-16 за счет более точной установки уровней сигналов на входах компараторов, соответствующих ситуации попадания сигнальных точек в центры зон принятия решений, достигается выполнением следующих операций над сигналом:

- каждую демодулированную тетраду информационных символов ABCD дешифрируют и определяют номер зоны принятия решения, к которой относится принятая сигнальная точка;

- устанавливают циклически повторяющийся интервал счета m тактов;

- подсчитывают за выбранный интервал счета m количество сигнальных точек, отнесенных к любой из четырех зон принятия решений, номера которых соответствуют входному сигналу с максимальной амплитудой;

- подсчитывают за выбранный интервал счета m количество сигнальных точек, отнесенных к любой из четырех зон принятия решений, номера которых соответствуют входному сигналу с минимальной амплитудой;

- один раз в конце выбранного интервала счета сравнивают подсчитанные количества демодулированных сигнальных точек с максимальной и минимальной амплитудой и, в случае их несовпадения, изменяют на одну дискрету уровень сигнала на выходе первого ЦАП, при этом;

- в случае, если количество сигнальных точек с максимальной амплитудой больше (меньше) количества сигнальных точек с минимальной амплитудой, то изменяют уровень сигнала на выходе первого ЦАП таким образом, чтобы это приводило к уменьшению (увеличению) сигнала на выходах первого и второго управляемого усилителей.

Новыми операциями над сигналом являются следующие:

- устанавливают циклически повторяющийся интервал счета n тактов;

- за выбранный интервал счета n для тех сигнальных точек, которые отнесены к любой из четырех зон принятия решений, номера которых соответствуют входному сигналу с максимальной амплитудой, раздельно подсчитывают количество сигнальных точек с увеличенной и уменьшенной сверх нормативного значения амплитудой;

- один раз в конце выбранного интервала счета сравнивают подсчитанные количества демодулированных сигнальных точек с увеличенной и уменьшенной сверх нормативного значения амплитудой и, в случае их несовпадения, изменяют на одну дискрету уровень сигнала на выходе второго ЦАП, при этом;

- в случае, если количество сигнальных точек с увеличенной амплитудой больше (меньше) количества сигнальных точек с уменьшенной амплитудой, то изменяют уровень сигнала на выходе второго ЦАП таким образом, чтобы это приводило к уменьшению (увеличению) сигнала на выходах первого и второго управляемого усилителей.

Таким образом, реализуется не только первоначальная "грубая" настройка по амплитуде на сигнал КАМ, но и осуществляется более точная подстройка уровня сигналов на выходах управляемых усилителей так, чтобы в процессе работы уровни этих сигналов соответствовали критерию идеального наблюдателя для достижения наивысшей помехоустойчивости.

Это достигается тем, что демодулятор сигналов шестнадцатипозиционной квадратурной амплитудной манипуляции содержит блок восстановления несущей, выход которого подключен ко второму входу первого фазового детектора и, через фазовращатель на 90° - ко второму входу второго фазового детектора, первый вход которого соединен с первым входом первого фазового детектора и является входом демодулятора, выходы первого и второго фазовых детекторов соединены, соответственно, с входами первого и второго фильтров нижних частот, при этом входы первого, второго, третьего, седьмого и восьмого компараторов соединены, а выходы седьмого и восьмого компараторов соединены с входами первого элемента ИЛИ, выход которого подключен к входу первого счетчика и первому входу второго элемента ИЛИ, выход и второй вход которого соединены, соответственно, с входом второго счетчика и входом третьего счетчика, который подключен к выходу третьего элемента ИЛИ, входы которого соединены с выходами девятого и десятого компараторов, входы которых соединены с входами четвертого, пятого и шестого компараторов, при этом выходы второго и пятого компараторов являются, соответственно, первым и вторым выходами демодулятора, выходы первого и третьего компараторов соединены, соответственно, с первым входом четвертого элемента ИЛИ и прямым входом первого элемента И, инверсный вход и выход которого соединены, соответственно, с выходом второго компаратора и вторым входом четвертого элемента ИЛИ, выход которого является третьим выходом демодулятора, четвертым выходом которого является выход пятого элемента ИЛИ, входы которого соединены, соответственно, с выходами шестого компаратора и второго элемента И, к прямому и инверсному входам которого подключены, соответственно, выходы четвертого и пятого компараторов, первый, второй, третий и четвертый входы дешифратора подключены, соответственно, к первому, второму, третьему и четвертому выходам демодулятора, первый, второй, третий и четвертый выходы дешифратора соединены с соответствующими входами шестого элемента ИЛИ, выход которого соединен с первым входом четвертого счетчика, выход которого соединен с первым входом первого блока сравнения, второй вход которого соединен с выходом пятого счетчика, вход которого соединен с выходом седьмого элемента ИЛИ, входы которого соединены, соответственно, с пятым, шестым, седьмым и восьмым выходами дешифратора, выход шестого счетчика соединен со вторыми входами четвертого, пятого и первого реверсивного счетчиков, первый и третий входы первого реверсивного счетчика соединены, соответственно, с первым и вторым выходами первого блока сравнения, выход первого реверсивного счетчика соединен с входом первого цифроаналогового преобразователя, первый вход и выход первого управляемого усилителя соединены, соответственно, с выходом первого фильтра нижних частот и входом первого компаратора, первый вход и выход второго управляемого усилителя соединены, соответственно, с выходом второго фильтра нижних частот и входом четвертого компаратора.

Согласно изобретению, в него введены одиннадцатый, двенадцатый, тринадцатый и четырнадцатый компараторы, восьмой и девятый элементы ИЛИ, третий и четвертый элементы И, седьмой, восьмой и девятый счетчики, второй блок сравнения, второй реверсивный счетчик, второй цифроаналоговый преобразователь и сумматор, причем входы одиннадцатого и двенадцатого компараторов соединены с входом второго компаратора, входы тринадцатого и четырнадцатого компараторов соединены с входом пятого компаратора, выходы одиннадцатого и двенадцатого компараторов соединены с входами восьмого элемента ИЛИ, выходы тринадцатого и четырнадцатого компараторов соединены с входами девятого элемента ИЛИ, выход восьмого элемента ИЛИ соединен с первыми входами третьего и четвертого элементов И, выход девятого элемента ИЛИ соединен с вторыми входами третьего и четвертого элементов И, выход шестого элемента ИЛИ соединен с третьими входами третьего и четвертого элементов И, четвертые входы которых соединены с выходом второго элемента ИЛИ, четвертый вход третьего элемента И и первый, второй и четвертый входы четвертого элемента И являются инверсными, выход третьего элемента И соединен с первым входом седьмого счетчика, выход которого соединен с первым входом второго блока сравнения, второй вход которого соединен с выходом восьмого счетчика, вход которого соединен с выходом четвертого элемента И, выход девятого счетчика соединен с вторыми входами седьмого, восьмого и второго реверсивного счетчиков, первый и второй выходы второго блока сравнения соединены, соответственно, с первым и третьим входами второго реверсивного счетчика, выход которого соединен с входом второго цифроаналогового преобразователя, выход которого соединен с вторым входом сумматора, первый вход которого соединен с выходом первого цифроаналогового преобразователя, выход сумматора соединен с вторыми входами первого и второго управляемых усилителей.

Введение компараторов с одиннадцатого по четырнадцатый с соответствующими порогами срабатывания позволяет разбить четыре зоны принятия решений, соответствующие входному сигналу с максимальной амплитудой, на дополнительные квадраты, попадания сигнальной точки в которые свидетельствуют об отклонении уровня входного сигнала от нормативного (оптимального) значения. Подсчитывая седьмым и восьмым счетчиками количества точек с увеличенной и уменьшенной амплитудой и сравнивая их в конце интервала счета между собой во втором блоке сравнения, можно получить на выходе второго ЦАП управляющее напряжение для компенсации этой составляющей потерь помехоустойчивости, которая связана с неточным выставлением уровня входного сигнала относительно центра зон принятия решений. Это приводит к достижению максимально возможной помехоустойчивости.

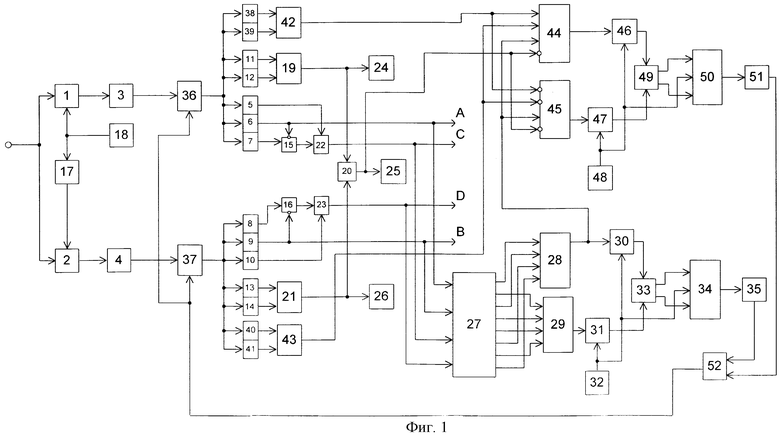

На фиг.1 приведена функциональная схема демодулятора сигналов КАМ-16.

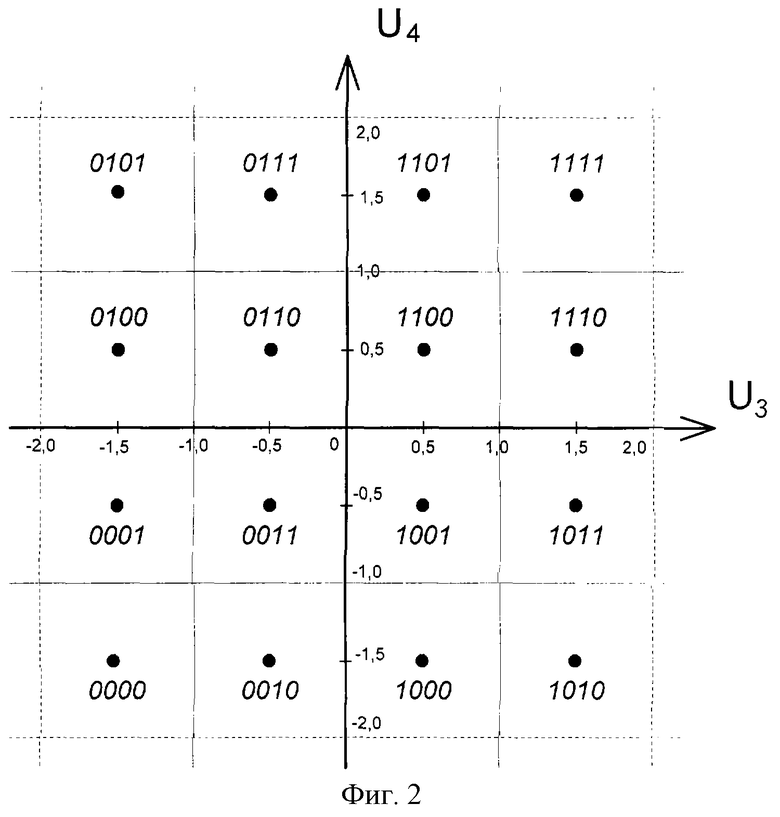

На фиг.2 приведены сигнальные точки ансамбля КАМ-16 и соответствующие им оптимальные зоны принятия решений. Символами U3 и U4 обозначены, соответственно, напряжения на выходе первого и второго фильтров нижних частот.

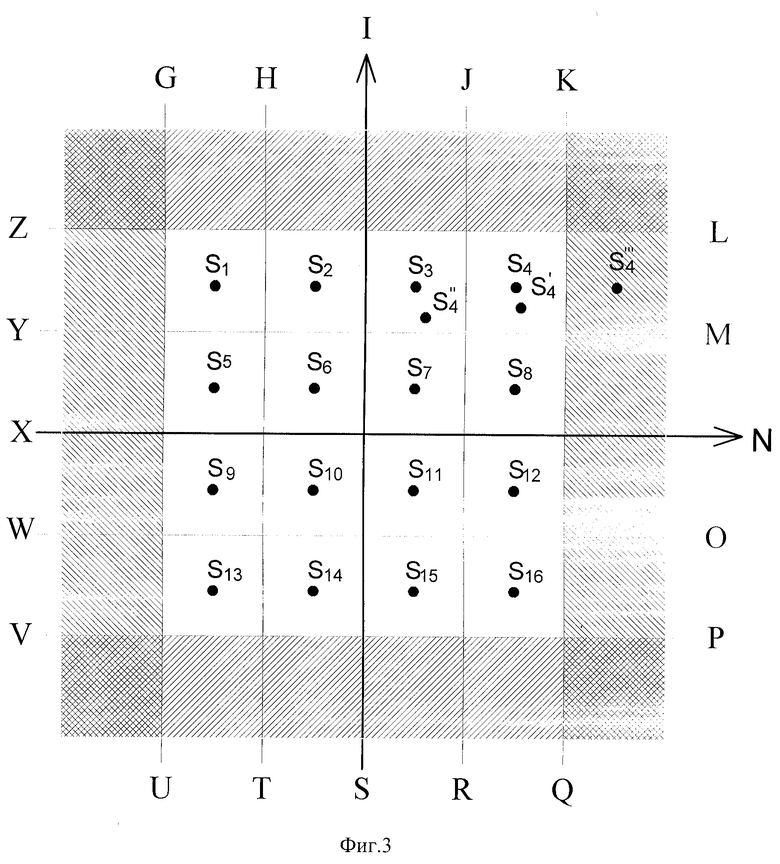

Фиг.3 иллюстрирует принцип измерения вероятности ошибки на выходе демодулятора. Штриховкой выделена зона, по частоте попадания сигнальных точек в которую делается вывод о вероятности ошибки на выходе демодулятора.

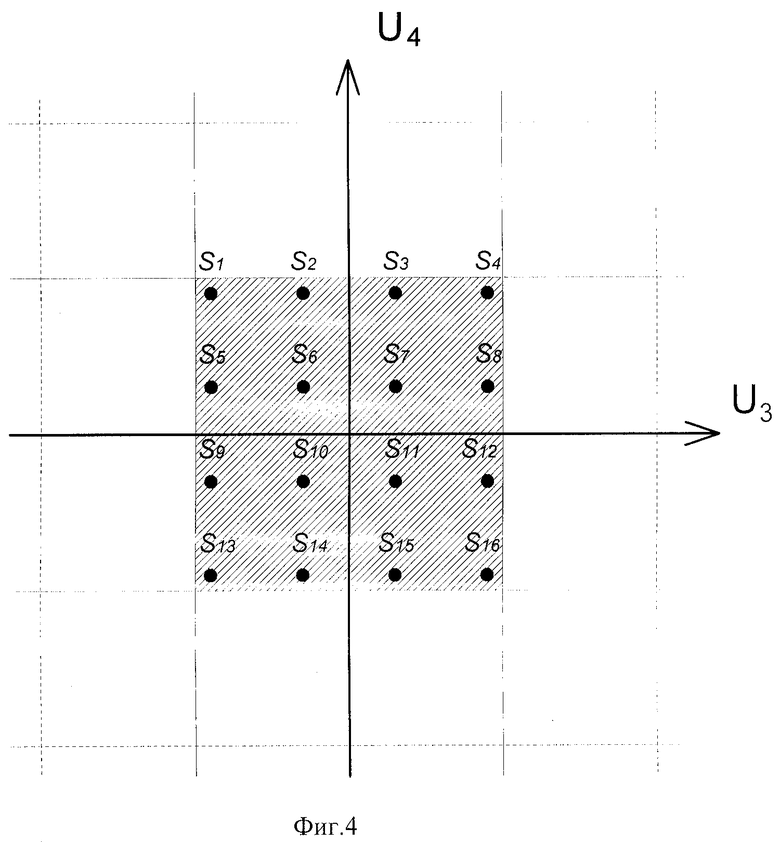

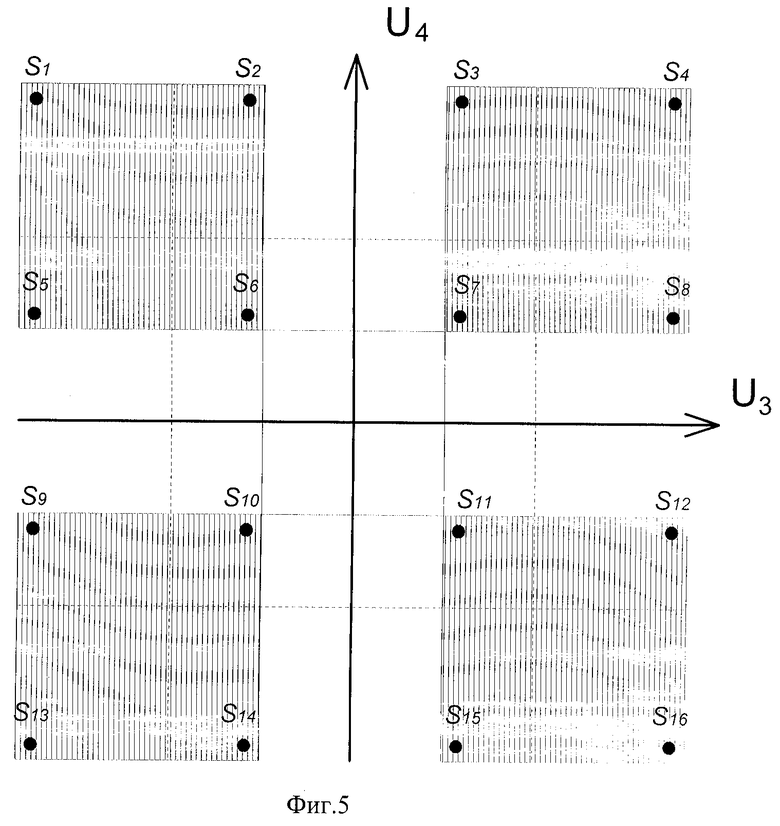

Фиг.4 и 5 иллюстрируют принцип "грубой" (первоначальной) настройки уровня входного сигнала. При этом фиг.4 соответствует предельно малому уровню входного сигнала, а фиг.5 - предельно большому.

Фиг.6 и 7 иллюстрируют принцип точной настройки уровня входного сигнала. При этом фиг.6 показывает один из возможных негативных случаев в работе прототипа, когда учет только частоты попадания сигнальных точек в заштрихованные области приводит к установлению неоптимального уровня входного сигнала (на фиг.6 - недостаточный уровень).

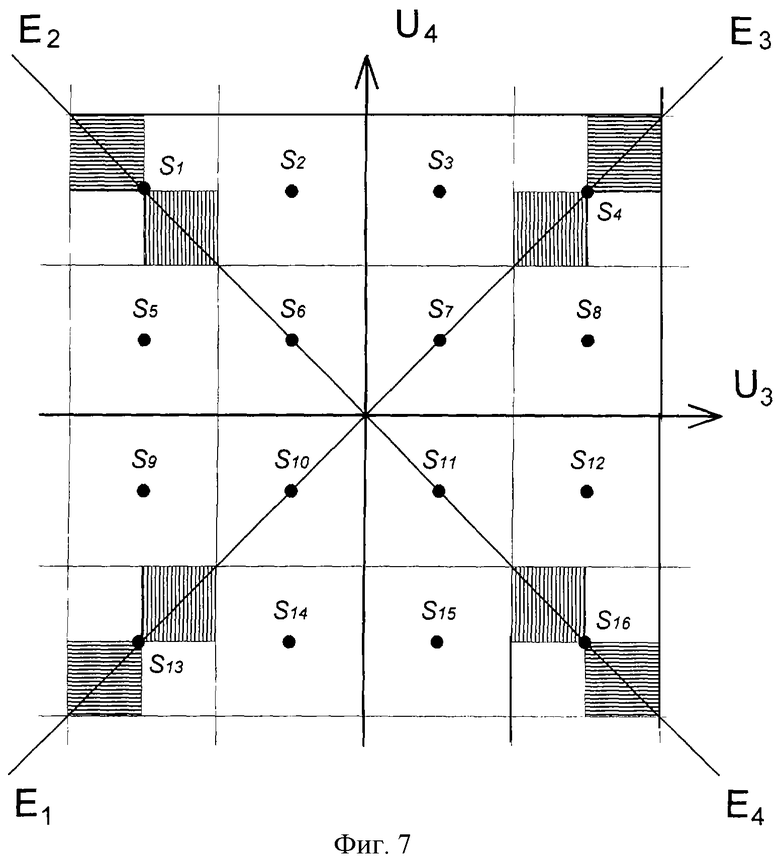

На фиг.7 штриховкой выделены дополнительные участки сигнальной плоскости (квадраты), образованные одиннадцатым - четырнадцатым компараторами, учет частоты попадания сигнальных точек в которые позволяет точно установить уровень входного сигнала.

В таблице 1 приведены уровни срабатывания компараторов, в таблице 2 показана работа дешифратора.

Демодулятор сигналов КАМ-16 содержит первый, второй фазовые детекторы 1, 2, первый, второй фильтры 3, 4 нижних частот (ФНЧ), первый - десятый компараторы 5-14, первый, второй элементы И 15, 16, фазовращатель 17 на 90°, блок 18 восстановления несущей, первый - пятый элементы ИЛИ 19-23, первый, второй, третий счетчики 24-26, дешифратор 27, шестой и седьмой элементы ИЛИ 28, 29, четвертый - шестой счетчики 30-32, первый блок 33 сравнения, первый реверсивный счетчик 34, первый цифроаналоговый преобразователь (ЦАП) 35, первый и второй управляемые усилители 36, 37, одиннадцатый - четырнадцатый компараторы 38-41, восьмой и девятый элементы ИЛИ 42, 43, третий и четвертый элементы И 44, 45, седьмой - девятый счетчики 46-48, второй блок сравнения 49, второй реверсивный счетчик 50, второй ЦАП 51, сумматор 52.

При этом выход блока 18 восстановления несущей подключен ко второму входу первого фазового детектора 1 и, через фазовращатель 17 на 90° - ко второму входу второго фазового детектора 2, первый вход которого соединен с первым входом первого фазового детектора 1 и является входом демодулятора. Выходы первого и второго фазовых детекторов 1 и 2 соединены, соответственно, с входами первого и второго фильтров нижних частот 3 и 4, при этом входы первого 5, второго 6, третьего 7, седьмого 11 и восьмого 12 компараторов соединены, а выходы седьмого 11 и восьмого 12 компараторов соединены с входами первого элемента ИЛИ 19, выход которого подключен к входу первого счетчика 24 и первому входу второго элемента ИЛИ 20, выход и второй вход которого соединены, соответственно, с входом второго счетчика 25 и входом третьего счетчика 26, который подключен к выходу третьего элемента ИЛИ 21, входы которого соединены с выходами девятого и десятого компараторов 13 и 14, входы которых соединены с входами четвертого 8, пятого 9 и шестого 10 компараторов.

Выходы второго 6 и пятого 9 компараторов являются, соответственно, первым и вторым выходами демодулятора, выходы первого 5 и третьего 7 компараторов соединены, соответственно, с первым входом четвертого элемента ИЛИ 22 и прямым входом первого элемента И 15, инверсный вход и выход которого соединены, соответственно, с выходом второго компаратора 6 и вторым входом четвертого элемента ИЛИ 22, выход которого является третьим выходом демодулятора, четвертым выходом которого является выход пятого элемента ИЛИ 23, входы которого соединены, соответственно, с выходами шестого компаратора 10 и второго элемента И 16, к прямому и инверсному входам которого подключены, соответственно, выходы четвертого и пятого компараторов 8 и 9, первый, второй, третий и четвертый входы дешифратора 27 подключены, соответственно, к первому, второму, третьему и четвертому выходам демодулятора, первый, второй, третий и четвертый выходы дешифратора 27 соединены с соответствующими входами шестого элемента ИЛИ 28, выход которого соединен с первым входом четвертого счетчика 30, выход которого соединен с первым входом первого блока сравнения 33, второй вход которого соединен с выходом пятого счетчика 31, вход которого соединен с выходом седьмого элемента ИЛИ 29, входы которого соединены, соответственно, с пятым, шестым, седьмым и восьмым выходами дешифратора 27, выход шестого счетчика 32 соединен со вторыми входами четвертого 30, пятого 31 и первого реверсивного 34 счетчиков, первый и третий входы первого реверсивного счетчика 34 соединены, соответственно, с первым и вторым выходами первого блока сравнения 33, выход первого реверсивного счетчика 34 соединен с входом первого цифроаналогового преобразователя 35, первый вход и выход первого управляемого усилителя 36, соединены, соответственно, с выходом первого фильтра нижних частот 3 и входом первого компаратора 5, первый вход и выход второго управляемого усилителя 37 соединены, соответственно, с выходом второго фильтра нижних частот 4 и входом четвертого компаратора 8.

Входы одиннадцатого и двенадцатого компараторов 38 и 39 соединены с входом второго компаратора 6, входы тринадцатого и четырнадцатого компараторов 40 и 41 соединены с входом пятого компаратора 9, выходы одиннадцатого и двенадцатого компараторов 38 и 39 соединены с входами восьмого элемента ИЛИ 42, выходы тринадцатого и четырнадцатого компараторов 40 и 41 соединены с входами девятого элемента ИЛИ 43, выход восьмого элемента ИЛИ 42 соединен с первыми входами третьего и четвертого элементов И 44 и 45, выход девятого элемента ИЛИ 43 соединен с вторыми входами третьего и четвертого элементов И 44 и 45, выход шестого элемента ИЛИ 28 соединен с третьими входами третьего и четвертого элементов И 44 и 45, четвертые входы которых соединены с выходом второго элемента ИЛИ 20, четвертый вход третьего элемента И 44 и первый, второй и четвертый входы четвертого элемента И 45 являются инверсными, выход третьего элемента И 44 соединен с первым входом седьмого счетчика 46, выход которого соединен с первым входом второго блока сравнения 49, второй вход которого соединен с выходом восьмого счетчика 47, вход которого соединен с выходом четвертого элемента И 45, выход девятого счетчика 48 соединен с вторыми входами седьмого 46, восьмого 47 и второго реверсивного 50 счетчиков, первый и второй выходы второго блока сравнения 49 соединены, соответственно, с первым и третьим входами второго реверсивного счетчика 50, выход которого соединен с входом второго цифроаналогового преобразователя 51, выход которого соединен с вторым входом сумматора 52, первый вход которого соединен с выходом первого цифроаналогового преобразователя 35, выход сумматора соединен с вторыми входами первого и второго управляемых усилителей 36 и 37.

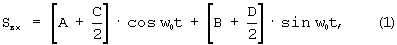

Демодулятор работает следующим образом. На вход демодулятора поступает сигнал КАМ-16 в виде:

где А, В, С, D - выбираемые из множества /-1; +1/ информационные символы:

w0 - несущая частота сигнала.

Представление сигнала КАМ-16 в виде (1) хорошо согласуется с суперпозиционным принципом формирования сигнала КАМ-16.

Между передаваемыми информационными символами /-1; +1/ в каждом разряде квадруплета ABCD и битами тетрады битов при каждой сигнальной точке ансамбля КАМ-16 существует простое соответствие: символ - 1 соответствует биту 0, а символ +1 соответствует биту 1.

Исходя из этого, можно сказать, что в тетраде битов, приписанных каждой сигнальной точке ансамбля КАМ-16 на фиг.2, первый бит соответствует символу А, второй - В, третий – C и четвертый - D. Так, тетрада 0101 означает передачу следующих символов: A = -1, B = +1, C = -1, D = +1.

Обозначим напряжение на выходе фильтра 3 как U3, напряжение на выходе фильтра 4 как U4 (см. фиг.2).

На выходе компараторов 5-11, 13, 38 и 40 логическая 1 формируется, если уровень сигнала на входе компаратора превышает порог срабатывания. Компараторы 12, 14, 39 и 41 имеют инверсные входы, т.е. на выходах этих компараторов логическая 1 формируется, если уровень сигнала на входе компаратора меньше порога срабатывания.

Пороги срабатывания компараторов приведены в таблице 1.

Из сопоставления расположения сигнальных точек ансамбля КАМ-16 и зон принятия решения на фиг.2 следует то, что на выходе компаратора 6 формируется символ А, на выходе компаратора 9 - символ В.

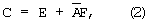

Образование символа С происходит по правилу:

где Е и F - двоичные данные на выходе компараторов 5 и 7, соответственно;

+ - символ булевской операции сложения (ИЛИ).

Образование символа D происходит по аналогичному правилу.

При этом блоки 15, 22 и 16, 23 формируют уравнение вида (2) для определения символов С и D, соответственно.

Рассмотрим, каким образом происходит восстановление данных при демодуляции, например, сигнальной точки S8 (см. фиг.3). При приеме сигнальной точки S8 на выходах ФНЧ 3 и ФНЧ 4 напряжения будут таковы, что срабатывают компараторы 6 и 9 с нулевыми порогами и на первом выходе демодулятора появится бит 1 (А = +1), на втором выходе появится бит 1 (В = +1). Поскольку компаратор 5 также сработает (ибо напряжение U3 превышает пороговую для компаратора 5 величину +1), то через элемент ИЛИ 22 на третьем выходе демодулятора появится бит 1 (С = +1).

Компаратор 10 не сработает, ибо U4 не превышает пороговой для компаратора величины 1. Компаратор 8 срабатывает, так как порог составляет - 1, но элемент И 16 будет закрыт по инверсному входу сигналом с выхода компаратора 9 и в итоге на выходе элемента ИЛИ 23 будет сформирован бит 0 (D = -1). Данный набор битов 1110 полностью соответствует коду на фиг.2 для точки S8 (фиг.3).

При передаче любой сигнальной точки S1-S16 логика работы компараторов 5-14, элементов И 15, 16 и элементов ИЛИ 22, 23 такова, что всегда на первом выходе демодулятора будет формироваться символ А, на втором выходе - символ В, на третьем - символ С, на четвертом - D (см. фиг.1) в соответствии с выбранным манипуляционным кодом (см. фиг.2).

Рассмотрим, каким образом происходит измерение вероятности ошибки на выходе демодулятора.

Поскольку заявляемый демодулятор принимает решения по критерию идеального наблюдателя, то ошибки при приеме сигналов ансамбля КАМ-16 происходят в демодуляторе только тогда, когда передаваемая сигнальная точка под воздействием шума попадает на сигнальной плоскости в зону принятия решения, соответствующей другой сигнальной точке. Так, при приеме символа S’4 (см. фиг.3) демодулятор выносит решение в пользу ближайшей разрешенной сигнальной точки S4, и ошибки не происходит. Если же под воздействием шума передаваемая точка занимает место S’’4 (т.е. попадает в зону решения другой сигнальной точки), то решение выносится в пользу точки S3 (см. фиг.3), и на выходе демодулятора возникает ошибка в символе.

Факт такой ошибки при приеме полностью случайного информационного сигнала (не имеющего корреляционной связи между символами) никаким образом не может быть обнаружен. Однако, если положить, что вероятностью пересечения векторного шума более чем одной границы на решающей сети (фиг.3) можно пренебречь (что всегда выполняется на практике), то, в этом случае, наблюдая за попаданием точек в дополнительные зоны, можно измерять вероятность ошибок.

Действительно, пребывание точки S’’’4 в заштрихованной зоне не приводит к возникновению ошибки (поскольку решение выносится в пользу истинной точки S’4), однако при этом можно составить представление о действующем на входе векторе шума S4S’’’4, который при передаче любой из точек S1-S3, S5-S7, S9-S11, S13-S15 привел бы к возникновению ошибки.

Перейдем к строгому доказательству возможности измерения вероятности ошибки в заявляемом устройстве.

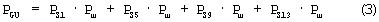

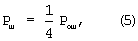

Вероятность PGU пребывания точки в левой полуплоскости, ограниченной прямой (GU), определяется по формуле:

где РS1=РS5=РS9=PS13 - априорные вероятности передачи сигнальных точек S1,S5, S9, S13;

Pш - вероятность того, что шум уведет передаваемую точку влево за границу GU.

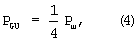

Поскольку все сигнальные точки ансамбля КАМ-16 передаются с одинаковой вероятностью, равной 1/16, то формулу 3 можно преобразовать к виду:

Поскольку шум “уводит” сигнальные точки от их истинного положения в соседние зоны принятия решения с одинаковой вероятностью (канал симметричен), то

где Рош - вероятность ошибки на выходе демодулятора.

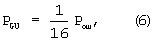

Подставляя выражение (5) в выражение (4), имеем:

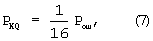

Аналогично этому, вероятность пребывания точки в правой полуплоскости, ограниченной прямой KQ, есть

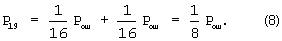

Поскольку события, заключающиеся в нахождении сигнальной точки слева от прямой GU или справа от прямой KQ, несовместимы, то вероятность того, что произойдет любое из этих событий, есть сумма вероятностей, определяемых формулами (4) и (7)

Факт появления сигнальной точки слева от прямой GU определяется по срабатыванию компаратора 12 с порогом срабатывания - 2. Факт появления сигнальной точки справа от прямой KQ определяется по срабатыванию компаратора 11 с порогом срабатывания +2. Прямые GU и KQ пересекают ось абсцисс на фиг.2 именно в точках -2 и +2. Значит, объединяя через элемент ИЛИ 19 выходы компараторов 11 и 12, можно измерять вероятность ошибки в символе по данному квадратурному каналу (по оси U3, на фиг.2).

Поток импульсов с выхода элемента ИЛИ 19 поступает на счетчик 24. Умножая на коэффициент, равный 8, показания счетчика 24 (в соответствии с формулой (8)), можно определить вероятность ошибки в символах А и С на выходе демодулятора.

Аналогично этому, вероятность ошибки в символах В и D можно определить по показаниям счетчика 26 (также через коэффициент, равный 8).

Итоговую вероятность (по всем символам А, В, С, D) ошибки можно определить по показаниям счетчика 25, умножая их на 4.

При этом вероятность ошибки определяется так:

где Рош - вероятность ошибки на выходе демодулятора;

N25 - показания счетчика 25;

m - длительность интервала счета в тактах.

Рассмотрим, каким образом происходит первоначальная ("грубая") настройка амплитуды входного сигнала за счет подсчета количества сигнальных точек с максимальной (минимальной) амплитудой, принятых за период счета m тактов. Период счета m задается шестым счетчиком 32.

Дешифратор 27 является дешифратором двоичных кодов, поступающих на его вход, при этом первый вход дешифратора 27 соответствует старшему разряду, а четвертый вход - младшему. Логическая 1 формируется на одном из выходов дешифратора при поступлении на его вход кодов в соответствии с таблицей 2.

В этой же таблице показаны номера сигнальных точек, соответствующих кодам на входах дешифратора 27.

В соответствии с этим и логикой работы элементов ИЛИ 30 и 31, показания N30 четвертого счетчика 30 будут означать количество сигнальных точек максимального уровня (S13, S1,S16, S4), демодулированных за интервал счета, а показания N31 пятого счетчика 31 - количество сигнальных точек минимального уровня (S10, S6,S11, S7), демодулированных за тот же интервал. Интервал счета m тактов, определяемый шестым счетчиком 32, выбирается по различным соображениям от m = 1 до m = (10-100)·16.

Показания четвертого 30 и пятого 31 счетчиков сравниваются первым блоком сравнения 33, на первом выходе которого формируется логическая 1 (на втором выходе формируется 0), если N30>N31. Если N30<N31, то логическая единица формируется на втором выходе (на первом выходе формируется 0). Если N30=N31, то на обоих выходах блока 33 формируются логические 0. Первый блок сравнения 33 может быть реализован как устройство для сравнения чисел, описанное в работах [5, 6].

Первый вход первого реверсивного счетчика 34 является входом уменьшения его состояния; третий вход - входом увеличения его состояния, а второй вход - входом разрешения изменения состояния (записи).

В конце каждого интервала наблюдения (по истечении m тактов) на выходе шестого счетчика 32 формируется сигнал разрешения изменения состояния первого реверсивного счетчика 34 и обнуления состояний счетчиков 30 и 31 перед новым интервалом счета.

Следовательно, при превышении за интервал счета количества сигнальных точек с максимальной (минимальной) амплитудой над количеством сигнальных точек с минимальной (максимальной) амплитудой, состояние первого реверсивного счетчика 34 в конце каждого интервала счета уменьшается (увеличивается) на единицу.

Так происходит до тех пор, пока не будет выполнятся равенство N30=N31 и состояние первого реверсивного счетчика 34 будет сохраняться неизменным.

В случае же существенного отклонения уровня входного сигнала от оптимального значения, в первом реверсивном счетчике 34 по указанному выше алгоритму формируется код, пропорциональный величине этого рассогласования, который через первый ЦАП 35, первый вход сумматора 52 и вторые входы усилителей 36 и 37 замыкает петлю автоматической "грубой" (первоначальной) подстройки по уровню входного сигнала.

Состояние первого реверсивного счетчика 34 изменяется от минимального значения N34min через N34opt до максимального значения N34max.

При этом напряжение на выходе первого ЦАП 35 пропорционально коду на выходе первого реверсивного счетчика 34. Увеличение напряжения на выходе сумматора 52 и, соответственно, напряжений на вторых (управляющих) входах управляемых усилителей 36 и 37 приводит к увеличению их коэффициентов передачи, т.е. к увеличению напряжений на их выходах.

Предельные случаи, которые могут возникнуть в процессе работы блоков 27-35 иллюстрируют фиг.4 и 5.

При этом фиг.4 соответствует предельно малому уровню входного сигнала, при котором в конце каждого интервала счета оказывается N30<<N31 (т.к. все сигнальные точки S1-S16 попадают в заштрихованные косой штриховкой зоны принятия решений).

Фиг.5 соответствует предельно большому уровню входного сигнала, при котором в конце каждого интервала счета оказывается N30>>N31 (т.к. все сигнальные точки S1-S16 попадают в заштрихованные вертикальной штриховкой зоны принятия решений).

В интервале между данными значениями входного сигнала устройство обеспечивает автоматическое поддержание уровня входного сигнала таким, чтобы выполнить равенство N30=N31.

Выполнение равенства N30=N31 является безусловно необходимым, однако не достаточным условием для обеспечения максимально возможной помехоустойчивости при демодуляции сигналов КАМ-16.

Так, например, на фиг.6 показан случай неоптимального уровня входного сигнала, при котором, тем не менее (формально выполняется равенство N30=N31. На фиг.6 видно, что недостаточный уровень входного сигнала приводит к тому, что сигнальные точки расположены не в центрах зон принятия решений. Это обуславливает низкую помехоустойчивость при демодуляции сигналов КАМ-16, в связи с чем петля автоматического регулирования уровня входного сигнала по описанному выше способу через первый ЦАП 35 и первый вход сумматора 52 выполняет роль петли первоначальной "грубой" настройки.

Рассмотрим, каким образом происходит точная подстройка амплитуды входного сигнала, приводящая к достижению максимальной помехоустойчивости.

Одиннадцатый - четырнадцатый компараторы 11-14 с порогами срабатывания ±1,5 (в соответствии с табл. 1) позволяют сформировать на сигнальной плоскости дополнительные зоны. При этом в соответствии с логикой работы третьего и четвертого элементов И 44 и 45 такие зоны имеют вид квадратов, показанных штриховкой на фиг.7. Такие дополнительные зоны (квадраты) делят на четыре равные части каждую из зон принятия решений, номера которых соответствуют входному сигналу с максимальной амплитудой (точки S1,S4, S13, S16 на фиг.3).

Поскольку на пересечении таких квадратов лежит центр зоны принятия решения о точке с максимальной амплитудой (см. фиг.7), это дает возможность использовать подсчет частоты попадания сигнальной точки в такие квадраты для точной подстройки уровня входного сигнала. При этом для выработки управляющего сигнала наблюдают за частотами попадания сигнальной точки именно в заштрихованные, а не другие зоны на фиг.7, по следующим соображениям.

Во-первых, эти зоны принадлежат точкам с максимальной амплитудой S1,S4, S13, S16, которые наименее подвержены воздействию шума. Во-вторых, другие (незаштрихованные на фиг.7) квадраты не включают в себя участки прямых OE1, ОЕ2, ОЕ3, ОЕ4 (см. фиг.7), по которым перемещаются сигнальные точки при подстройке, т.е. изменении в процессе регулирования уровня входного сигнала.

Итак, точная настройка (подстройка) уровня входного сигнала после достижения равенства N30=N31 основана на сравнении за циклически повторяющийся интервал счета n количества сигнальных точек с увеличенной (горизонтальная штриховка на фиг.7) и уменьшенной (вертикальная штриховка на фиг.7) сверх нормативного значения амплитудой.

В соответствии с логикой работы блоков 38-45, на выходе третьего элемента И 44 формируется логическая 1 при попадании сигнальной точки в квадраты, выделенные на фиг.7 горизонтальной штриховкой. Количество таких сигнальных точек подсчитывается седьмым счетчиком 46. На выходе четвертого элемента И 45 формируется логическая 1 при попадании сигнальной точки в квадраты, выделенные на фиг.7 вертикальной штриховкой. Количество таких сигнальных точек подсчитывается восьмым счетчиком 47.

Логика работы блоков 46-51 аналогична работе блоков 30-35.

В соответствии с этим, при превышении за интервал счета n количества сигнальных точек с увеличенной (уменьшенной) амплитудой над количеством сигнальных точек с уменьшенной (увеличенной) амплитудой, состояние второго реверсивного счетчика 50 в конце каждого интервала счета уменьшается (увеличивается) на единицу.

Так происходит до тех пор, пока не будет выполняться равенство N46=N47 и состояние второго реверсивного счетчика 50 будет сохраняться неизменным.

В случае же отклонения уровня входного сигнала от нормативного уровня (соответствующего центру зоны принятия решений), во втором реверсивном счетчике 50 по указанному выше алгоритму формируется код, пропорциональный величине этого рассогласования, который через второй ЦАП 51, второй вход сумматора 52 и вторые входы усилителей 36 и 37 замыкает петлю автоматической точной (окончательной) подстройки по уровню входного сигнала.

Согласование работы двух петель автоматического регулирования достигается следующим образом. Интервал счета n, задаваемый девятым счетчиком 48, выбирается гораздо большим интервала счета m. Тогда, при выполнении условия n>>m, петля точной регулировки уровня входного сигнала будет работать после завершения регулирования в петле "грубой" (первоначальной) установки уровня входного сигнала.

Кроме того, диапазон выходных значений напряжений ЦАП 35 должен в несколько раз превосходить тот же параметр для ЦАП 51. Тогда изменение напряжения на выходе ЦАП 35 будет способно перемешать сигнальные точки из зоны в зону (см. фиг.4 и 5) для достижения первоначальной настройки уровня, а изменение напряжения на выходе ЦАП 51 будет способно перемещать сигнальные точки вблизи центров зон принятия решения для точной настройки уровня входного сигнала.

Таким образом достигается точная адаптация демодулятора к амплитуде входного сигнала, приводящая к достижению максимально возможной помехоустойчивости заявляемого демодулятора.

Источники информации

1. Патент РФ №2020767, МКИ 5 H 04 L 27/22, опубл. БИ №18, 30.09.94 г.

2. Тихонов В.И. Статистическая радиотехника. - М.: Радио и связь - 1982. - 624 с.

3. А.С. №2019051, МКИ 5 H 04 L 27/22, опубл. БИ №16, 30.08.94 г.

4. Патент РФ №2198470, МПК 7 H 04 L 27/22, опубл. БИ №4, 10.02.2003 г. - прототип.

5. А.С. №1501037, МКИ 4 G 06 F 7/02, опубл. БИ №30, 15.08.89 г.

6. А.С. №1383 333, МКИ 4 G 06 F 7/02, опубл. БИ №11, 23.03.88 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕМОДУЛЯТОР СИГНАЛОВ ШЕСТНАДЦАТИПОЗИЦИОННОЙ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МАНИПУЛЯЦИИ | 2005 |

|

RU2291583C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ ШЕСТНАДЦАТИПОЗИЦИОННОЙ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МАНИПУЛЯЦИИ | 2003 |

|

RU2234814C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ ШЕСТНАДЦАТИПОЗИЦИОННОЙ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МАНИПУЛЯЦИИ | 2005 |

|

RU2286650C2 |

| ДЕМОДУЛЯТОР СИГНАЛОВ ШЕСТНАДЦАТИПОЗИЦИОННОЙ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МАНИПУЛЯЦИИ | 2001 |

|

RU2198470C1 |

| ПРИЕМНИК СИГНАЛОВ ШЕСТНАДЦАТИПОЗИЦИОННОЙ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МАНИПУЛЯЦИИ | 2004 |

|

RU2287225C2 |

| ДЕМОДУЛЯТОР СИГНАЛОВ ШЕСТНАДЦАТИПОЗИЦИОННОЙ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МАНИПУЛЯЦИИ | 2002 |

|

RU2235440C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ ШЕСТНАДЦАТИПОЗИЦИОННОЙ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МАНИПУЛЯЦИИ | 1991 |

|

RU2019051C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ ШЕСТНАДЦАТИПОЗИЦИОННОЙ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МАНИПУЛЯЦИИ | 2003 |

|

RU2246182C1 |

| АНАЛОГО-ЦИФРОВОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2121712C1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

Изобретение относится к радиотехнике и может быть использовано при демодуляции сигналов шестнадцатипозиционной квадратурной амплитудной манипуляции. В демодуляторе наличие компараторов с одиннадцатого по четырнадцатый с соответствующими порогами срабатывания позволяет разбить зоны принятия решений, соответствующих входному сигналу с максимальной амплитудой, на дополнительные квадраты, попадания сигнальной точки в которые свидетельствует об отклонении уровня входного сигнала от нормативного. Седьмой и восьмой счетчики подсчитывают количество точек с увеличенной и уменьшенной амплитудами соответственно, сравнивая которые во втором блоке сравнения можно получить на выходе второго ЦАП управляющее напряжение для компенсации этой составляющей потерь помехоустойчивости. Технический результат - повышение помехоустойчивости. 7 ил. и 2 табл.

Демодулятор сигналов шестнадцатипозиционной квадратурной амплитудной манипуляции, содержащий блок восстановления несущей, выход которого подключен ко второму входу первого фазового детектора и, через фазовращатель на 90° - ко второму входу второго фазового детектора, первый вход которого соединен с первым входом первого фазового детектора и является входом демодулятора, выходы первого и второго фазовых детекторов соединены соответственно с входами первого и второго фильтров нижних частот, при этом входы первого, второго, третьего, седьмого и восьмого компараторов соединены, а выходы седьмого и восьмого компараторов соединены с входами первого элемента ИЛИ, выход которого подключен к входу первого счетчика и первому входу второго элемента ИЛИ, выход и второй вход которого соединены соответственно с входом второго счетчика и входом третьего счетчика, который подключен к выходу третьего элемента ИЛИ, входы которого соединены с выходами девятого и десятого компараторов, входы которых соединены с входами четвертого, пятого и шестого компараторов, при этом выходы второго и пятого компараторов являются соответственно первым и вторым выходами демодулятора, выходы первого и третьего компараторов соединены соответственно с первым входом четвертого элемента ИЛИ и прямым входом первого элемента И, инверсный вход и выход которого соединены соответственно с выходом второго компаратора и вторым входом четвертого элемента ИЛИ, выход которого является третьим выходом демодулятора, четвертым выходом которого является выход пятого элемента ИЛИ, входы которого соединены соответственно с выходами шестого компаратора и второго элемента И, к прямому и инверсному входам которого подключены соответственно выходы четвертого и пятого компараторов, первый, второй, третий и четвертый входы дешифратора подключены соответственно к первому, второму, третьему и четвертому выходам демодулятора, первый, второй, третий и четвертый выходы дешифратора соединены с соответствующими входами шестого элемента ИЛИ, выход которого соединен с первым входом четвертого счетчика, выход которого соединен с первым входом первого блока сравнения, второй вход которого соединен с выходом пятого счетчика, вход которого соединен с выходом седьмого элемента ИЛИ, входы которого соединены соответственно с пятым, шестым, седьмым и восьмым выходами дешифратора, выход шестого счетчика соединен со вторыми входами четвертого, пятого и первого реверсивного счетчиков, первый и третий входы первого реверсивного счетчика соединены соответственно с первым и вторым выходами первого блока сравнения, выход первого реверсивного счетчика соединен с входом первого цифроаналогового преобразователя, первый вход и выход первого управляемого усилителя соединены соответственно с выходом первого фильтра нижних частот и входом первого компаратора, первый вход и выход второго управляемого усилителя соединены соответственно с выходом второго фильтра нижних частот и входом четвертого компаратора, отличающийся тем, что в него введены одиннадцатый, двенадцатый, тринадцатый и четырнадцатый компараторы, восьмой и девятый элементы ИЛИ, третий и четвертый элементы И, седьмой, восьмой и девятый счетчики, второй блок сравнения, второй реверсивный счетчик, второй цифроаналоговый преобразователь и сумматор, причем входы одиннадцатого и двенадцатого компараторов соединены со входом второго компаратора, входы тринадцатого и четырнадцатого компараторов соединены со входом пятого компаратора, выходы одиннадцатого и двенадцатого компараторов соединены со входами восьмого элемента ИЛИ, выходы тринадцатого и четырнадцатого компараторов соединены со входами девятого элемента ИЛИ, выход восьмого элемента ИЛИ соединен с первыми входами третьего и четвертого элементов И, выход девятого элемента ИЛИ соединен с вторыми входами третьего и четвертого элементов И, выход шестого элемента ИЛИ соединен с третьими входами третьего и четвертого элементов И, четвертые входы которых соединены с выходом второго элемента ИЛИ, четвертый вход третьего элемента И и первый, второй и четвертый входы четвертого элемента И являются инверсными, выход третьего элемента И соединен с первым входом седьмого счетчика, выход которого соединен с первым входом второго блока сравнения, второй вход которого соединен с выходом восьмого счетчика, вход которого соединен с выходом четвертого элемента И, выход девятого счетчика соединен с вторыми входами седьмого, восьмого и второго реверсивного счетчиков, первый и второй выходы второго блока сравнения соединены соответственно с первым и третьим входами второго реверсивного счетчика, выход которого соединен с входом второго цифроаналогового преобразователя, выход которого соединен с вторым входом сумматора, первый вход которого соединен с выходом первого цифроаналогового преобразователя, выход сумматора соединен с вторыми входами первого и второго управляемых усилителей, при этом первый цифроаналоговый преобразователь имеет диапазон выходных значений напряжений, превосходящий в несколько раз этот же параметр для второго цифроаналогового преобразователя, а девятый счетчик задает интервал счета гораздо большим интервала счета, задаваемого шестым счетчиком.

| ДЕМОДУЛЯТОР СИГНАЛОВ ШЕСТНАДЦАТИПОЗИЦИОННОЙ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МАНИПУЛЯЦИИ | 2001 |

|

RU2198470C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ ШЕСТНАДЦАТИПОЗИЦИОННОЙ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МАНИПУЛЯЦИИ | 1991 |

|

RU2019051C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ ШЕСТНАДЦАТИПОЗИЦИОННОЙ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МАНИПУЛЯЦИИ | 1990 |

|

RU2020767C1 |

| US 5940451 А, 17.08.1999. | |||

Авторы

Даты

2005-04-10—Публикация

2003-04-11—Подача