ключей к вторым входам третьего, восьмого и девятого элементов И,этого узла, узел управления записью содержит восемнадцать элементов И, два элемента ИЛИ, триггер и счетчик, причем выход первого элемента И узла управления записью подключен к первым входам второго и третьего элементов И узла управления записью, выход третьего элемента И этого узла подключен к счетному входу счетчика этого узла, выход четвертого элемента И узла управления записью соединен с первыми входами пятого, шестого, седьмого, восьмого и девятого элементов И этого узла, выход десятого элемента И узла управления записью соединен с первыми входами одиннадцатого, двенадцатого и тринадцатого элементов И этого узла, выходы второго и. одиннадцатого элементов И атого узла соединены с первыгл и вторым входами первого элемента ИЛИ этого узла, выход первого элемента ИЛИ узла управления записью соединен с единичньм входом триггера этого узла, выход триггера узла управления записью подключен к второму входу третьего элемента И этого узла, вход сброса триггера этого узла подключен к выходу второго элемента ИЛИ этого узла, первый и второй входы второго элементаИЛИ узла управления записью подключены к выходам пятого и шестого элементов И узла управления записью второй вход шестого элемента И узла управления записью соединен с вторым входом второго элемента. И узла управления записью и с выходом четырнадцатого элемента И узла управления записью, второй вход одиннадцатого элемента И узла управления записью подключен к вторым входам шестого, седьмого и двенадцатого элементов И этого узла и к.выходу пятнадцатого элемента И этого узла, первый прямой выход счетчика узла управления, записью .соединен с первыми входами четырнадцатого,, шестнадцатого и семнадцатого элементов И узла управления записью,, первый инверсный выход счетчика этого узла подключен к первым входам пятнадцатого

и восемнадцатого элементов И -этого узла, второй прямой выход счётчика узла управления записью соединен с вторыми входами шестнадцатого, семнадцатого и восемнадцатого элемен- тов И этого узла, второй инверсный выход счетчика узла управления записью подключен к вторым входам четырнадцатого и пятнадцатого элементов И этого узла, третий прямой выход счетчика узла управления записью., соединен с третьим входом семнадцатого элемента И этого узла, третий инверсный выход счетчика узла

подключен к третьим входам четырнадцатого, пятнадцатого, шестнадцатого и восемнадцатого ЭJieмeнтoв И узла управления записью, выход шестнадцатого элемента И этого узла подключен к второму входу девятого элемента И узла управления записью, выходсемнадцатого элемента И этого узла соединен с вторым входом восьмого элемента И этого узла, выход восемнадцатого элемента .И узла управления записью подключен к второму входу тринадцатого элемента И узла, первый запросный вход устройства подключен к третьему входу первого элемента И узла управления чтением, группа информационных входов устройства соединена с группой входов регистра группа выходов которого соединена с группой входов шифратора и с группой входов сдвигового регистра, входзаписи которого подключен к выходу двенадцатого элемента И узла управления записью и к счетному входу счетчика адреса записи, выход восьмого элемента И узла управления записью подключен к входу управления сдвигом сдвигового регистра, к счетному входу первого счетчика, к вхоДУ управления записью первого счетчика, к входу управления записью первого блока памяти и к первому управляющему входу сумматора. Тактовый вход первого счетчика подключен к выходу седьмого элемента И узла управления записью и к .управляющему входу второго блока памяти; группа выходов счетчика адреса зациси соединена с группой адресных входов .записи второго блока памяти, информационный вход которого подключен к выходу сдвигового регистра, группа адресных входов чтения второГО блока памяти соединена с группой выходов счетчика адреса чтения, счетный вход которого подключен к счетному входу второго счетчика, к выходу пятого элемента И узла управления чтением и к счетному входу третьего счетчика, выход восьмого элемента И узла управления чтением подключен к тактовому входу второго счетчика и к тактовому входу выходного регистра, вход сброса которого подключен к выходу третьего элемента И у.зла управления чтением, группа выходов второго счетчика соединена с группой входов дешифратора, группа выходов которого соединена с группой входов выходного регистра, вход управления записью которого подключен к выходу второго блока памяти, выход девятого элемента И уз|ла управления записью подключен к первому входу первого элемента И и к первому сигнальному выходу устройства, второй вход первого элемента И подключен к второму запросному входу устройства и к третьегвходу второго элемента И узла управления записью, инверсные входы первого, второго и десятого элементов И которого подключены к второму сигнальному выходу устройства и к выходу первого элемента ИЛИ, группа входов которого соединена с группой выходов | сумматора, второй управляющий вход которого подключен к выходу , шестого элемента И узла управления чтением и к счетному входу четвертого счетчика, выход первого триггера узла управления чтением-подключен к входу элемента. .НЕ и к инверсным входам второго,.третьего и четвертого элементов И, выходы которых соеди.Невы с прямыми входами соответственно первого, второго и.третьего элементов И узла управления записью, третий вход одиннадцатого .элемента И которого соединен с выходом второго элемента ИЛИ, группа входов которого соединена с группой выходов первого счетчика, группа входов которого соединена с группой информационных , входов первого блока памяти , с группой выходов дешифратора и первой группой входов сумматора, вторая группа входов которого соединена с группой выходов третье1о счетчика и с .группой входов третьего элемента ИЛИ, выход которого подключен к третьему входу четвертого элемента И узла управления чтением, инверсный вход первого элемента И которого подключен к третьему сигналь.ному выходу устройства и к выходу

схемы сравнения, первая группа входов которой соединена с первой груп-. пой входов коммутатора и с группой выходов четвертого счетчика, выход девятого элемента И узла управления чтением подключен к входу управления чтением первого блока памяти и к тактовому входу третьего счетчика, выход тринадцатого элемента И узла управления записью подключен к счетному входу пятого счетчика, группа выходов которого соединена с второй группой входов сравнения и с второй группой входов коммутатора, группа выходов которого соединена с группой адресных входов первого блока памяти, группа выходов которого соединена с группой входов третЁ)его счетчика, выход третьего-триггера узла управления чтением подключен к выходу готовности устройства, прямой и инверсный выходы элемента НЕ подключены соответственно к первому и второму управляющим входам коммутатора, выход первого элемента И подключен к тактовому входу регистра, первый выход генератора синхросерий подключен к второму входу второго элемента И узла управления чтением и к прямому входу четвертого элемента И, прямой вход второго элемента И подключен к второму выходу генератора синхросерий и к второму входу седьмого элемента И узла управления чтением, третий выходГенератора синхросерий соединен с первым входом четвертого элемента И узла управления чтением.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

УСТРОЙСТВО ДЛЯ ОБСЛУЖИВАНИЯ СООБЩЕНИЙ, содержащее выходной регистр, первый блок памяти, узел управления записью, генератор синхросерий, узел управления чтением, причем группа выходов выходного регистра соединена с группой информационных выходов устройства, отличающее с я тем, что, с целью расширения его функциональных возможностей путем обеспечения возможности работы с сообщениями переменной длина, в него введены три элемента ИЛИ, пять счетчиков, второй блок памяти, регистр, четыре элемента И, счетчик адреса записи, счетчик адреса чтения, дешифратор, эле- мент НЕ, коммутатор, сумматор, сдвиговый регистр, схема сравнения, шифратор, узел управления чтением содержит д ;евять элементов И, два эле мента-ИЛИ, три триггера, счетчик, дешифратор, причем первый вход-первого элемента И узла управления чтением подключен к первому выходу дешифратора- узла управления чтением, и первому входу второго элемента И этого- узла, выход второго элемента И .узла управления чтением подключен к первому входу первого элемента ИЛИ . узла управления чтением, второй вход которого подключен к.выходу третьего элемента И узла управления чтением, первый вход четвертого элемента И узла управления чтением подключен к второму входу первого элемента И узлауправления чтением, к пер вым входам пятого и шестого элементов и этогб узла и к входу синхронизации первого триггера этого узла, второй вход четвертого элемента И узла управления чтением подключен к второму выходу дешифратора этого узла, к первому входу третьего элемента И этого узла и к второму.входу пятого элемента И узла управления чтением, выходы первого и четвертого элементов и узла управления чтением подключены к первому и втогрому входам второго элемента ИЛИ этого узла, выход второго элемента ИЛИ узла управления чтением под-. I ключен к единичному входу второго триггера узла управления чтением, (Л нулевой вхрд которого соединен с выходом первого элемента ИЛИ этого узла, выход второго триггера узла управления чтением подключен к первому вхрду седьмого элемента И этого узла, выход седьмого элемента И узла управления чтением подключен к: счетному входу счетчика этого узла, группа выходов счетчика узла упю равления чтением соединена с группой входов дешифратора этого- узла, 00 tsd третий выход дешифратора узла управления чтением подключен к первому ; входу восьмого элемента И этого узсд ла и к единичному входу первого ffi триггера этого узла, вход сброса первого триггера узла управления чтением подключен к выходу шестого элемента И этого узла, четвертый выход дешифратора узла управления чтением соединен с вторым входом шестого и с первым входом девятого элементов И этого узла, пятый выход дешифратора этого узла подключен к еди.ничному входу третьего триггера этого узла, вход сброса которого соединен с выходом восьмого элемента И уэ ла управления чтением, второй вход второго элемента И этого узла под

Изобретение относится к вычислительной технике, в частности к устройствам для обслуживания запросов, и может быть использовано при построении вычислительных.систем для обра.ботки данных большого .объема.

Известно многоканальное устройство приоритетных прерываний, содержащее выходной регистр, блоки оче-. редност.и, счетчик, элементы И, узлы управления, причем группа выходов в лходного регистра соединена с группой информационных выходов устройства fl. Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство Для приоритетного обслуживания .запросов, содержащее выходной регистр, запоминающий ,блок сдвиговых регистров, блок элементов И-ИЛИ, блок элементов И, дешифратор адреса, распределитель импульсов, блок элемен- тов ИЛИ, причем группа выходов выходного регистра соединена с группой информационных выходов устройства, вход Запрос на чтение подключен к первому входу блока элементов ИЛИ, выход распределителя подключен к второму входу блока элементов ИЛИ 2..

Недостатком известных устройств является невозможность обслуживания сообщений переменной длины, так как устройства не обладают средствами

управления своими ресурсами в зависимости от разрядности входного сообщения.

Цель изобретения - расширение функциональных возможностей устройства.путем обеспечения возможности работы с сообщениями переменной длины.

Цель достигается тем, что в устройство для обслуживания сообщений, содержащее выходной регистр, первый блок памяти, узел управления записью, генератор- синхросерий, узел управления чтением, причем группа выходов выходного регистра соединена с группой инсЬормационных выходов устройства, введены три элемента ИЛИ, пять счетчиков, второй блок памяти, регистр, четире элемента И, счетчик адреса записи, счетчик адреса чтения, дешифратор, элемент НЕ коммутатор, сумматор, сдвиговый регистр, схема сравнения, шифратор узел управления чтением содержит девять элементов И, два элемента ИЛ три триггера, счетчик, дешифратор, причем первый вход первого элемента И у.зла управления чтением подключен к первому выходу дешифратора узла управления чтением и первому входу второго элемента И этого узла, выход второго элемента И узла управления чтением подключен к первому входу первого элемента ИЛИ узла управления чтением, второй вход которого подклрочен к выходу третьего элемента И узла управления чтением, первый вход четвертого элемента ,И узла управления чтением подключен к второму входу .первого элемента И узла управления чтением, к первым входам пятого и шестого элементов И этого узла и к входу синхронизации первого триггера этого узла, второй вход четвертого элемента И узла управления чтением подключен к второму входу дешифратора этого узла, к первому входу третьего эле- . мента И этого узла и к второму входу пятого элемента И узла управления чтением, выходы первого и четвертого элементов И узла управления чтением подключены к первому и второму входам второго элемента ИЛИ этого узла, выход второго элемента ИЛИ узла управления чтением подключен к единичьэму входу второго триггера узла управления чтением, нулевой вход которого соединен с выходом первого -элемента ИЛИ этого узла, выход второго триггера узла управления чтением подключен к первому входу седьмого элемента И этого узла, выход седьмого элемента И узла управления чтением подключен к счетному входу счетчика этого узла, группа выходов счетчика узла управления чтением соединена с группой входов дешифратора этого узла, третий выход дешифратора узла управления чтением подключен к первому входу восьмого элемента И этого узла и к единичному входу первого триггера этого узла, вход сброса первого триггера узла управления чтением подключен к выходу шестого

элемента И этого узла, четвертыйвыход дешифратора узла управления чтением соединен с вторым входом шестого и с первым входом девятого элементов и этого узла, пятый выход дешифратора этого узла подключен к единичному входу третьего .триггера этого узла., вход сброса которого соединен с выходом восьмого элемента И узла управления чтением, второй вход второго элемента И этого узла подключен к вторым входам третьего, восьмого и девятого элеме.нтов И этого узла, узел управления записью содержит восемнадцать элементов И, два элемента ИЛИ, триггер и счетчик, причем выход первого элемента И узла управления записью подключен к первым входам второго и третьего элементов И узла управления записью, выход третьего элемента И этого узла подключен к счетному входу счетчика этого узла, выход четвертого элемента И узла управления записью соединен с первыми входами пятого, шестого, седьмого, восьмого и девятого элементов И этого узла, выход десятого элемента И узла Управления записью соединен с первыми входами одиннадцатого, двенадцатого и тринадцатого элементов И этого узла, выходы второго и одиннадцатого элементов И этого узла соединены с первым и вторым входами первого элемента ИЛИ этого узла, выход первого элемента ИЛИ узла уп-. равления записью соединен с единичным входом триггера этого узла, выход триггера узла управления записью подключен к второму входу- третьего элемента И этого узла, вход сброса триггера этого узла подключен к выходу второго элемента ИЛИ этого узла, первый и второй входы второго элемента ИЛИ узла управления за-писью подключены к выходам пятого и шестого элементов И узла управления записью, второй вход шестого элемента И узла управления записью соединен с вторым входом второго элемента И узла управления записью и с выходом четырнадцатого элемента И узла управления записью, второй вход одиннадцатого элемента. И узла управления записью подключен к вторым входам шестого, седьмого и двенадцатого элементов И этого узла и к выходу пятнадцатого элемента И этого узла, первый прямой выход счетчика узла управления за писью соединен с первыми входами четырнадцатого, шестнадцатого и семнадцатого элементов И узла управления записью, первый инверсный выход счетчика - этого узла подключен к первым входам пятнадцатого и восемнадцатого элементов И этого узла, второй прямой выход счетчика узла управления записью соединен с вторыми входами шестнадцатого, семнадцатого и восемнадцатого элементов И этого узла, второй инверсный выход счетчика узла управления записьюподключен к вторым входам четырнадцатого и пятнадцатого элементов И этого узла, третий прямой выход счетчика узла управления записью соединен с третьим входом семнадцатого элемента И этого узла, третий -инверсный выход счетчика узла подключен к третьим входам четырнадцатого, пятнадцатого, шестнадцатого и восемнадцатого элементов И узла управления записью, выход шестнадцатого элемента И этого узла подключен к второму входу -девятого элемента И узла управления записью, выход семнадцатого элемента И этого узла соединен с вторым входом восьмого элемента-И этого узла, выход восемнадцатоз70 элемента И узла управления записью подключен к второму входу тринадцатого элемента И узла, первый запросный вход устройства подключен к третьему входу первого элемента И узла управления чтением, группа информационных входов устройства соединена с группой входов регистра, группа выходов которого соединена с группой входов шифратора и с Группой входов сдвигового регистра, вход записи которого подключен к выхрДУ двенадцатого элемента И узла управления записью и к счетному входу счетчика адреса записи, выход восьмого элемента И узла управления записью подключен к входу управления сдвигом сдвигового .регистра, к счетному входу первого счетчика, к входу управления записью первого блока памяти и к первому управляющему входу сумматора, т.актовый вход первого счетчика подключен к выходу седьмого элемента И узла управления записью и к управляющему входу второго блока памяти, группа выходов счетчика адреса записи соединена с группой адресных входов записи второго блока памяти, информационный вход которого подключен к выходу сдвигового регистра, группа адресных входов чтения второго блока памяти соединена с группой выхо дов счетчика адреса чтения, счетный вход которого подключен к счетному входу второго .счетчика, к выходупятого элемента И узла управления чтением и к счетному входу третьего счетчика, выход восьмого элемента И узла управления чтением подключен к тактовому входу второго счетчика и-: к тактовому входу выходного регистра, вход сброса которого подключен к выходу третьего элемента И- узла управления чтением, группа выходов второго счетчика соединена с группой входов де1Шфратора, группа вы- .

ходов которого соединена с группой входов выходного регистра, вход управления записью которого подключен ,. к выходу второго блока памяти, выход девятого элемента И узла управления .записью подключен к первому входу первого элемента И и. к первому сигнальному выходу устройства, второй вход первого элемента И подключен к второму запросному входу уст0ройства и к третьему входу второго элемента И узла управления записью, инверсные входы первого, второго и десятого элементов И которого ключены к второму сигнальному выходу устройства и к выходу первого

5 элемента ИЛИ, группа входов которого соединена с группой выходов сумматора, второй управляющий вход которого подключен к выходу шестого элемента И узла управления чтением и к

0 счетному входу четвертого счетчика, выход первого триггера узла управления чтением подключен к входу эле-, мента НЕ и к инверным входам второго, третьего и четвертого элемен5тов И, выходы которых соединены с прямыми входами соответственно первого, второго и третьего элементов И узла управления записью, третий вход одиннадцатого элемента И которого

0 соединен с выходом второго элемента ИЛИ, группа входов которого Соединена с группой выходов первого счетчика, группа входов которого соединена с группой информационных

5 входов первого блока памяти, с группой выходов шифратора и первой группой входов сумматора, вторая группа входов которого соединена -с -группой выходов третьего счетчика и с группой входов третьего элемента ИЛИ,

0 выход которого подключен к третьему входу четвертого элемента И узла управления чтением, инверсный вход первого элемента И которого подключен к третьему сигнальному выходу

5 устройства и к выходу cxet-M сравнения , первая группа входов которой соединена с первой группой входов коммутатора и с группой выходов четвертого счетчика, выход девятого

0 элемента И узла управления чтением подключен к входу управления чтением первого блока памяти и к тактовому входу третьего счетчика, выход тринадцатого элемента И узла управле5нйя записью подключен к счетному входу пятого счетчика, группа выхо- дов которого соединена с второй группой входов схемы сравнения и с второй группой входов коммутатора,

0 группа выходов которого соединена с группой адресных входов первого блока памяти, группа выходов которого соединена с группой входов третьего счетчика, выход третьего триггера узла управления чтением подключен к

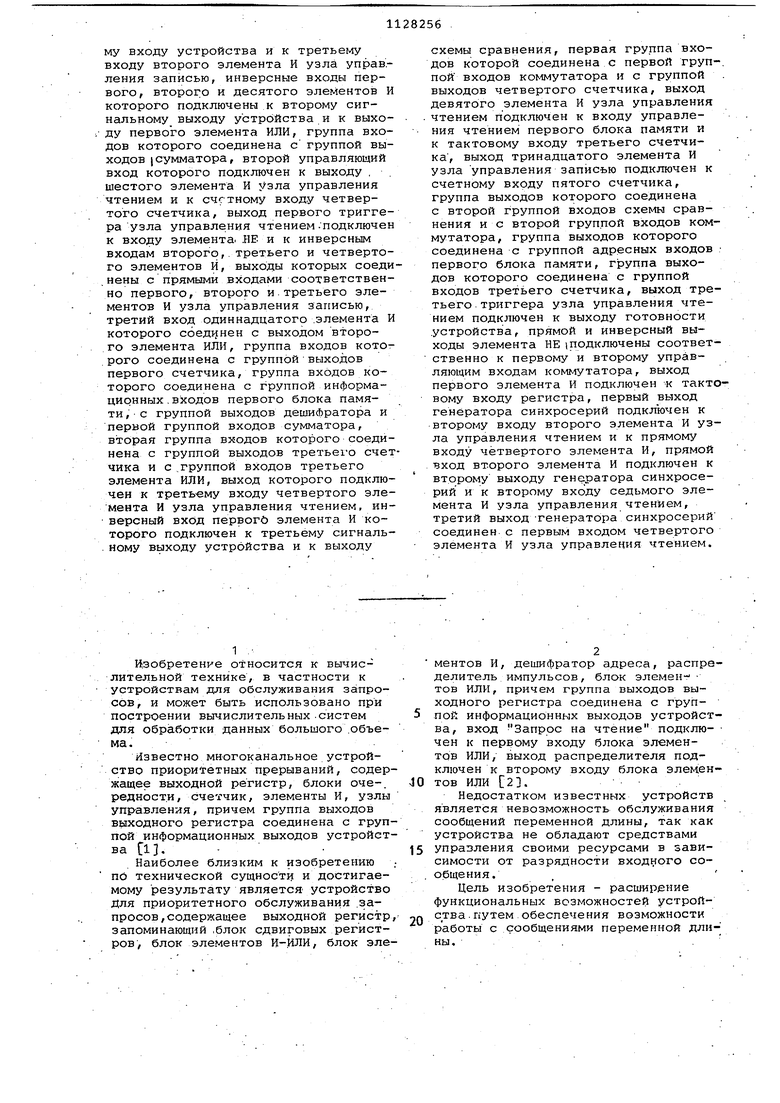

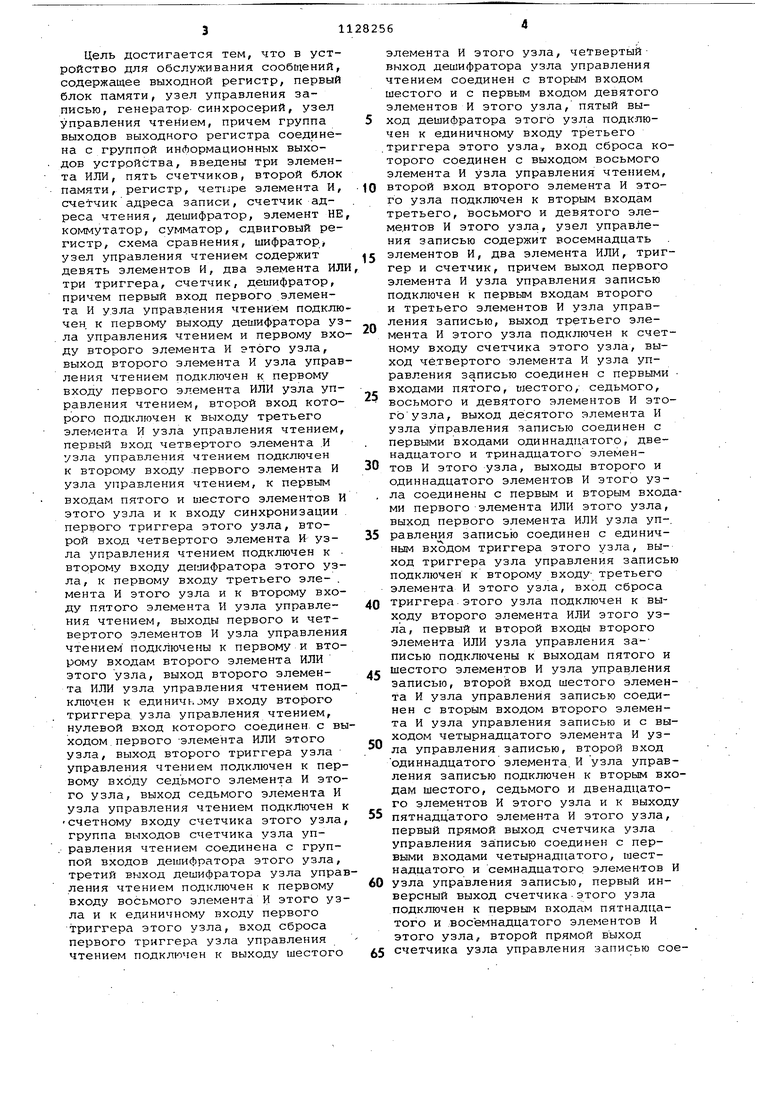

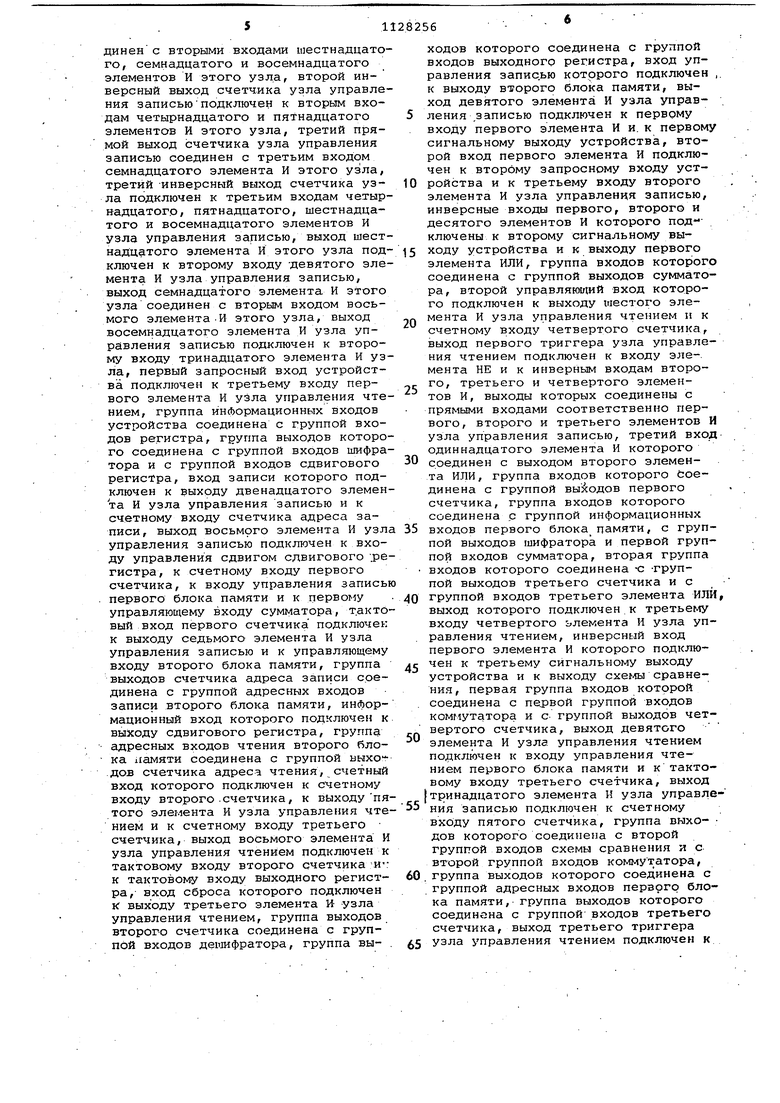

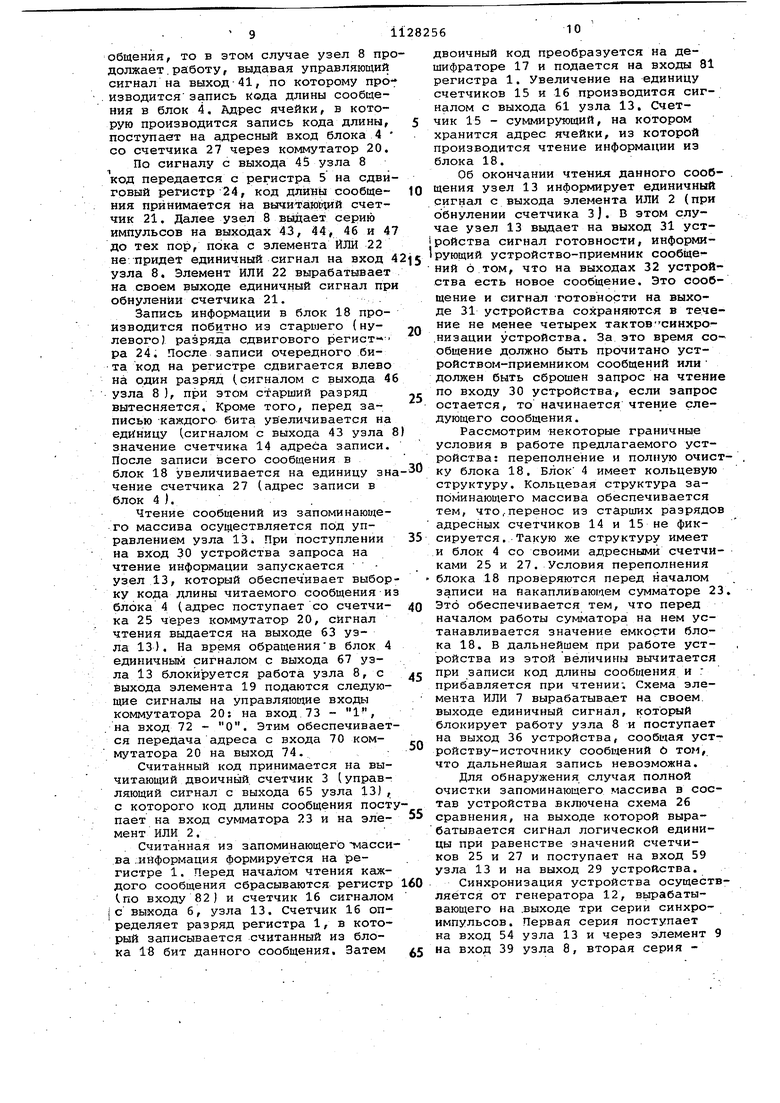

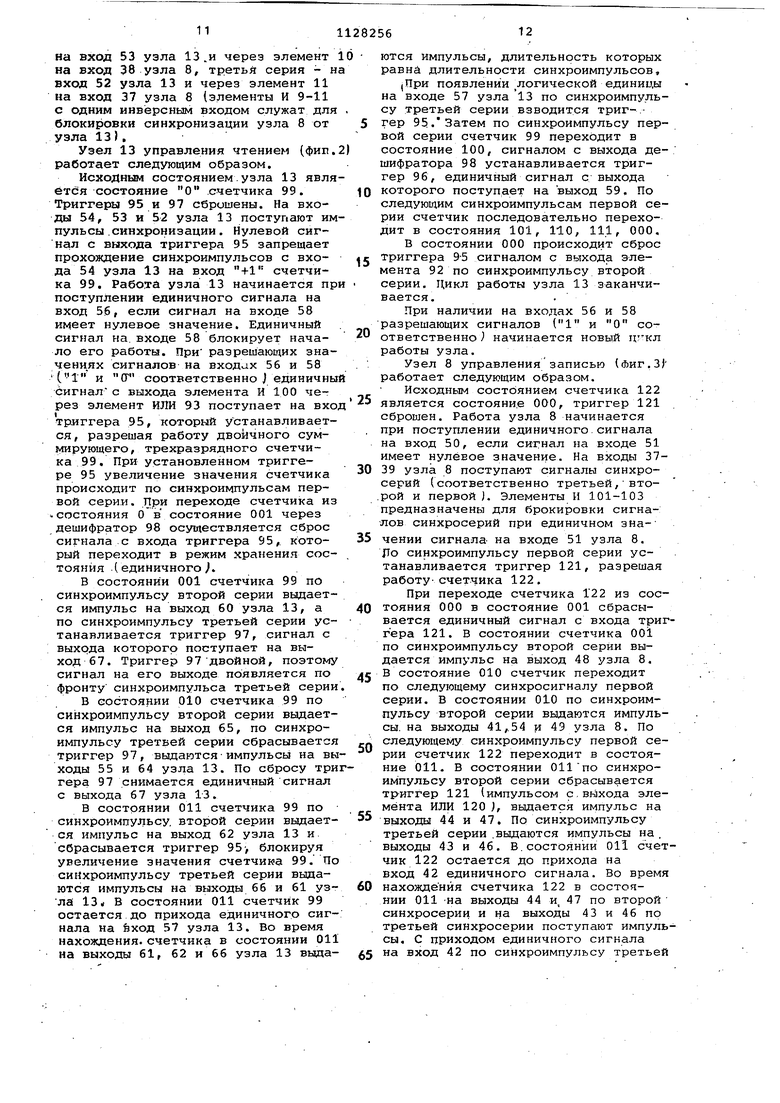

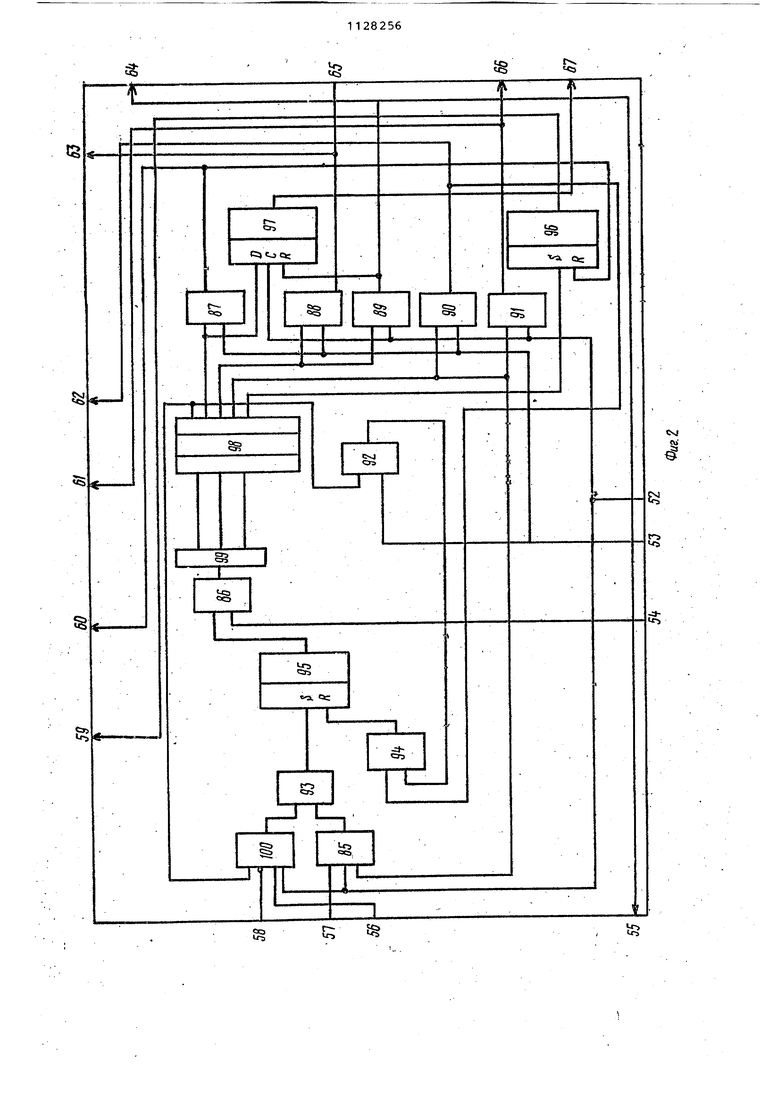

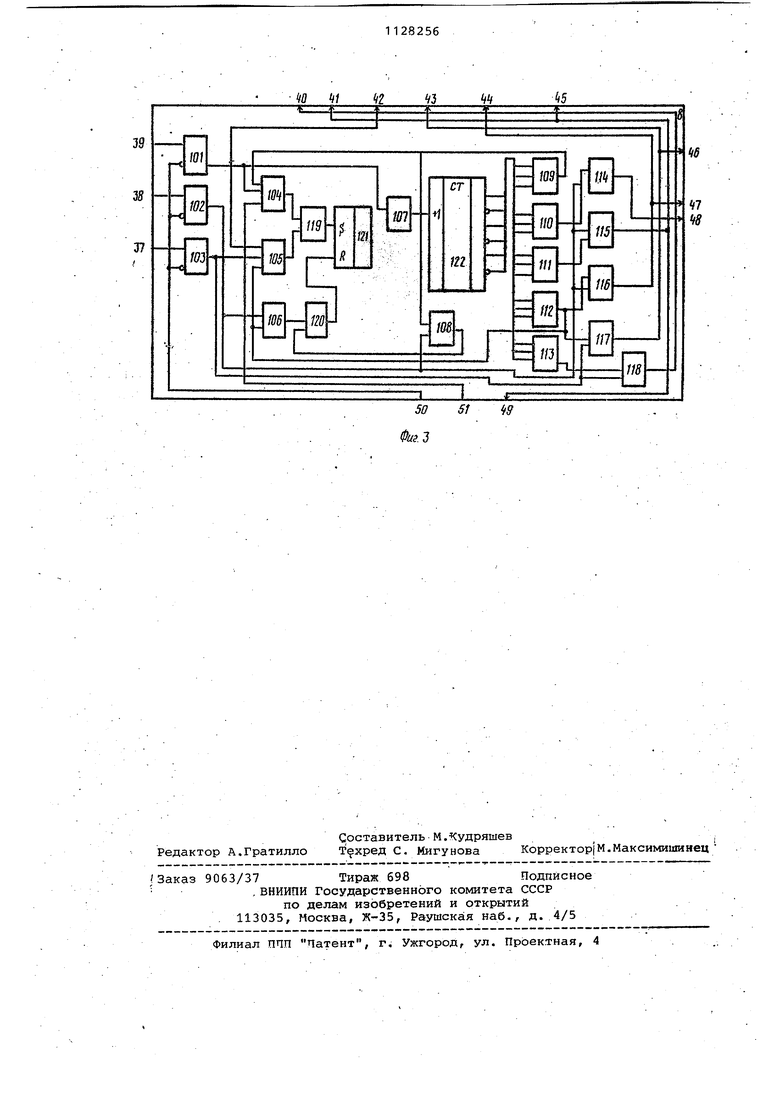

5 выходу готовности устройства, прямой и инверсный выходы элемента НЕ подключены соответственно к первому и второму управляющим входам коммутатора, выход первого элемента И по ключен к тактовому входу регистра, первый выход генератора синхросерий подключен к второму вхЪду второго элемента И узла управления чтением и к прямому входу четвертого элемента И, прямой вход второго элемен та И подключен к второму выходу генератора синхросерий-и к второму йходу седьмого.элемента И узла управления чтением, третий выход гене ратора синхросерий соединен с первым входом четвертого элемента И уз Ла управления чтением. На фиг.1 приведена структурная схема устройства; на фиг.2 - функци нальная схема узла управления чтением; на фиГ.З - то же узла управления записью. Устройство для обслуживания сооб щений переменной длины (фиг.1) содержит выходной регистр 1, ; мент ИЛИ 2, счетчик 3, блок 4 памяти, регистр 5, элемент И б, эле. мент ИЛИ 7, узел 8 управления записью, элементы И 9-11, генератор 1 синхросерий, узел 13 управления чте нием, счетчик 14 адреса записи, сче чик 15 адреса чтения, счетчик 16, дешифратор 17, блок 18 памяти, элемент НЕ (инвертор ) 19, коммутатор 2 счетчик 21, элемент ИЛИ 22, сумма-, тор 23, сдвиговый регистр 24, счетчик.25, схему 26 сравнения, счетчик. 27, шифратор 28, сигнальный выход 29 устройства, запроснвй вход 3 устройства, выход 31 готовности уст ройства, группа информационных выходов 32 устройства, группа информа ционных входов 33 устройства, запросный вход 34 устройства, сигналь ный выход 35 устройства, сигнальный выход 36 устройства, входы 37-39 уйла 8 управления записью, выхог; ды 40 и 41 узла 8 управления записью., вход 42 узла 8 управления эа пи.сью, выходы 43-49 узла 8 управления записью, первый 50 и второй 51 входы узла 8 управления записью входы 52-54 узла 13 управления чтением, выход 55 узла 13 управления чтением, входы 56-58 узла 13 управления чтением, выходы 59-67 узла 13 управления чтением, группы входов 68 и выходов 69 шифратора 28, группы информационных входов 70 и 7 коммутатора 20, управляющиевходы 7 и 73 коммутатора 20, группу выходов 74 коммутатора 20, информационный вход .75 блока 18, -группы адрес.ных входов 76 записи адресных вхо1дов .77 чтения блока 18, информацион ный выход 78 блока 18, управляющий вход 79 блока 18, вход 80 управле|ния записью выходного регистра 1, .вход 81 выходного регистра 1, тактовый вход 82 выходного регистра 1, группу инфомационных выходов 83 выходного регистра 1,вход сбрЛЬса 84 выходного регистра 1, Узел 13 управления чтением (фиг,2) содержит элементы И 85-92, элементы ИЛИ 93 и .94, триггеры 95-97, дешифратор 98, счетчик 99, эле- мент И 100. Узел 8 управления записью (фиг.3) содержит элементы И 101-118, элементы ИЛИ 119 и 120, триггер 121, счетчик 122. Устройство работает следующим образом. Сообщение поступает на выход 33, 1фиг,1) на вход 34 устройства поступает запрос на прием сообщения. Если в данный момент прием сообщения возможен, узел 8 вырабатывает на выходе 48 разрешающий сигнал, который поступает на вход элемента И 6 и на выход 35 устройства.. По сигналу с выхода элемента И 6 происходит прием на регистр 5. Принятый код в регистре 5 содержится в левой части, начиная с нулевого разряда, сообщения. Неиспользуемые правые разряды регистра 5 зэполнены нулями. Сигнал на выходе 35 устр ойства сигнализирует источнику сообщений о том, что сообщение принято. С регистра 5 код поступает на группу входов 68 шифратора 28 и на сдвиговый регистр.24. На выходах 69 шифратора 28 вырабатывается код длины сообщения, который . поступает на счетчик 21, на вход накапливающегосумматора 23, на информационные блока 4. Перед началом работы устройства на сумматоре 23 устанавливается значение максимальной емкости (в битах) блока 18. На входы сумматора поступают коды длины сообщений (соответственно при записи и чтении). Си.гнал с выхода 49 узла 8 разрешает вычитание из TeKyirjero значения кода, поступившего на вход -. Сигнал с выхода 55 узла 13 разрешает суммирование кода на входе +, сумматора с текущим значением сумматора 23.Таким образом, на сумматоре вычисляется код длины свободной части блока 18, который контролируется элементом ИЛИ 7. Сигнал с выхода элемента ИЛИ 7 поступает на вход 51 узла 8 и на выход 36 устройства. Единичный уровень сигнала на вхо- . де 51 узла 8 запрещает его работу. Сигнал на. выходе 36 устройства информирует устройство-источник сообщений о том, что дальнейигий прием сообщений пока .невозможен из-за пе-. реполнения запоминающего массива.. Если в блоке 18 достаточно места для записи поступившего входного сообщения, то в этом случае узел 8 пр должает . работу , выдавая управляющий сигнал на выход-41, по которому про изводится запись кода длины сообщения в блок 4. Адрес ячейки, в которую производится запись кода длины, поступает на адресный вход блока 4 со счетчика 27 через коммутатор 20. По сигналу с выхода 45 узла 8 код передается с регистра 5 на сдви говый регистр 24, код длйиы сообщеНИН принимается на вычитаюй ий счетчик 21. Далее узел В вьвдабт серию импульсов на выходах 43, 44, 46 и 4 до тех пор, пока с элемента ИЛИ 22 не придет единичный сигнал на вход узла 8, Элемент ИЛИ 22 вырабатывает на своем выходе единичный сигнал пр обнулении счетчика 21.. Запись информации в блок 18 производится побитно из старшего (нулевого) разряда сдвигового регист ра 24. После записи очередного би та код на регистре сдвигается влево на один разряд (.сигналом с выхода 4 узла 8 ), при этом с-гарший разряд вытесняется. Кроме того, перед записью -каждого бита увеличивается на единицу (.сигналом с выхода 43 узла значение счетчика 14 адреса записи. После записи всего сообщения в блок 18 увеличивается на единицу зн чение счетчика 27 (адрес записи в блок 4 ). Чтение сообщений из запоминающего массива осуществляется под управлением узла 13. При поступлении на вход 30 устройства запроса на чтение информации запускается узел 13, который обеспечивает выбор ку кода длины читаемого сообщения и блока 4 (адрес поступает со счетчика 25 через коммутатор 20, сигнал чтения выдается на выходе 63 узла 13). На время обращенияв блок 4 единичным сигналом с выхода 67 узла 13 блокируется работа узла 8, с выхода элемента 19 подаются следующие сигналы на управляющие входы коммутатора 20: на вход 73 - 1, на вход 72 - О. Этим обеспечивает ся передача адреса с входа 70 коммутатора 20 на выход 74. : Считанный код принимается на вычитающий двоичный счетчик 3 (управляющий сигнал с выхода 65 узла 13), с которого код Длины сообщения пост пает на вход сумматора 23 и на элемент ИЛИ 2. Считанная из запоминающего-масси ва /информация формируется на регистре 1. Перед началом чтения каждого сообщения сбрасываются регистр (по входу 82) и счетчик 16 сигналом |с выхода 6, узла 13. Счетчик 16 определяет разряд регистра 1, в который записывается считанный из блока 18 бит данного сообщения. Затем двоичный код преобразуется на дешифраторе 17 и подается на входы 81 регистра 1. Увеличение на единицу счетчиков 15 и 16 производится сигналом с выхода 61 узла 13. Счетчик 15 - суммирующий, на котором хранится адрес ячейки, из которой производится чтение информации из блока 18. Об окончании чтения данного сообщения узел 13 информирует единичный сигнал с выхода элемента ИЛИ 2 (при обнулении счетчика 3 J. В этом случае узел 13 выдает на выход 31 устройства сигнал готовности, информирующий устройство-приемник сообще ний 6 том, что на выходах 32 устройства есть новое сообщение. Это сообщение и сигнал ГОТОВНОСТИ на выходе 31 устройства сохраняются в течение не менее четырех тактов синхро.низации устройства. За это время сообщение должно быть прочитано устройством-приемником сообщений или должен быть сброшен запрос на чтение по входу 30 устройства, если запрос остается, то начинается чтение следующего сообщения. Рассмотрим некоторые граничные условия в работе предлагаемого устройства: переполнение и полную очистку блока 18. Блок 4 имеет кольцевую структуру. Кольцевая структура запоминающего массива обеспечивается тем, что ..перенос из старших разрядов адресных счетчиков 14 и 15 не фиксируется. Такую структуру имеет и блок 4 со своими адресными счетчиками 25 и 27. Условия переполнения блока 18 проверяются перед началом записи на накапливающем сумматоре 23. Это обеспечивается тем, что перед началом работы сумматора на нем устанавливается значение емкости блока 18. в дальнейшем при работе устройства из этой величины вычитается при записи код длины сообщения и : прибавляется при чтении; Схема элемента ИЛИ 7 вырабатывает на своем, выходе единичный сигнал, который блокирует работу узла 8 и поступает на выход 36 устройства, сообщая устройству-источнику сообщений U том, что дальнейшая запись невозможна. Для обнаружения случая полной очистки запоминающего массива в состав устройства включена схема 26 сравнения, на выходе которой вырабатывается сигнал логической единицы при равенстве значений счетчиков 25 и 27 и поступает на вход 59 узла 13 и на выход 29 устройства. Синхронизация устройства осуществляется от генератора 12, вьфабатывающего на .выходе три серии синхроимпульсов. Первая серия поступает на вход 54 узла 13 и через элемент 9 на вход 39 узла 8, вторая серия на вход 53 узла 13.и через элемент на вход 38 узла 8, третья серия - н вход 52 узла 13 и через элемент 11 на вход 37 узла 8 (элементы И 9-11 с одним инверсным входом служат для блокировки синхронизации узла 8 от узла 13),

Узел 13 управления чтением (фил. работает следующим образом.

Исходным состоянием.узла 13 является состояние О счетчика 99. Триггеры 95 и 97 сброшены. На входы 54, 53 и 52 узла 13 поступают импульсы .синхронизации . Нулевой сигнал с выхода триггера 95 запрещает прохождение синхроимпульсов с входа 54 узла 13 на вход +1 счетчика 99, Работй узла 13 начинается пр поступлении единичного сигнала на вход 56, если сигнал на входе 58 имеет нулевое значение. Единичный сигнал на. входе 58 блокирует начало его работы. При разрешающих значениях сигналов на входах 56 и 58 и ОТ соответственно J единичны сигнал с выхода элемента И 100 через элемент ИЛИ 93 поступает на вхо триггера 95, который устанавливается, разрешая работу двоичного суммирующего, трехразрядного счетчика 99. При установленном триггере 95 увеличение значения счетчика происходит по синхроимпульсам первой серии. При переходе счетчика из «состояния О в состояние 001 через дешифратор 98 осуществляется сброс сигнала с входа триггера 95,. который переходит в режим хранения соетоянйя (единичного.

В состоянии 001 счетчика 99 по синхроимпульсу второй серии выдается импульс на выход 60 узла 13, а по синхроимпульсу третьей серии устанавливается триггер 97, сигнал с выхода которого поступает на выход 67. Триггер 97 двойной, поэтому сигнал на его выходе появляется по фронту синхроимпульса третьей серии

В состоянии 010 счетчика 99 по синхроимпульсу второй серии выдается импульс на выход 65, по синхроимпульсу третьей серии сбрасывается триггер 97, выдаются-импульсь на выходы 55 и 64 узла 13. По сбросу тригера 97 снимается единичный сигнал с выхода 67 узла 13.

В состоянии 011 счетчика 99 по синхроимпульсу, второй серии выдается импульс на выход 62 узла 13 и. сбрасывается триггер 95) блокируя увеличение значения счетчииа 99. По синхроимпульсу третьей серии выдаются импульсы на выходы 66 и 61 узла 13 В состоянии 011 счетчик 99 остается до прихода единичного сигнала на ёход 57 узла 13. Во время нахождения, счетчика в состоянрги 011 на выходы 61, 62 и 66 узла 13 вьщаются Импульсы, длительность которых равна длительности синхроимпульсов,

(При появлении логической единицы на входе 57 узла 13 по синхроимпульсу третьей серии взводится триг-.гер 95.Затем по синхроимпульсу первой серии счетчик 99 переходит в состояние 100, сигналом с выхода дешифратора 98 устанавливается триггер 96, единичный сигнал с выхода которого поступает на выход 59. По следующим синхроимпульсам первой серии счетчик последовательно переходит в состояния 101, 110, 11.1, 000.

В состоянии 000 происходит сброс триггера 95 сигналом с выхода элемента 92 по синхроимпульсу второй серии. Цикл работы узла 13 заканчивается,.

При наличии на входах 56 и 58 разрешающих сигналов (1 и О соответственно начинается новый цгкл работы узла.

Узел 8 управлениязаписью (сЬиг,3) работает следующим образом.

Исходным состЬянием счетчика 122 является состояние 000, триггер 121 сброшен. Работа узла 8 начинается при поступлении единичного.сигнала на вход 50, если сигнал на входе 51 имеет нулевое значение. На входы 3739 узла 8 поступают сигналы синхросерий (соответственно третьей,вто.рой и первой ), Элементы И 101-103 предназначены для брокировки сигналов синхросерий при единичном значении сигнала на входе 51 узла 8, JIo синхроимпульсу первой серии устанавливается триггер 121, разрешая работу-счетчика 122,

При переходе счетчика 122 из состояния 000 в состояние 001 сбрасывается единичный сигнал с входа триггера 121. В состоянии счетчика 001 по синхроимпульсу второй серии выдается импульс на выход 48 узла 8, В состояние 010 счетчик переходит по следующему синхросигналу первой серии. В состоянии 010 по синхроимпульсу второй серии выдаются импульсы, на выходы 41,. 5 4 и 49 узла 8, По следующему синхроимпульсу первой серии счетчик 122 переходит в состояние 011. В состоянии синхроимпульсу второй серии сбрасывается триггер 121 (импульсом с,выхода элемента ИЛИ 120 )f выдается импульс на выходы 44 и 47 По синхроимпульсу третьей серии .выдаются импульсы на. выходы 43 и 46, В.состоянии Oil счетчик 122 остается до прихода на вход 42 единичного сигнала. Во время нахождения счетчика 122 в состоянии 011 На выходы 44 и 47 по второй синхросерий и на выходы 43 и 46 по третьей синхросерий поступают импульсы. С приходом единичного сигнала на вход 42 по синхроимпульсу третьей

серии устанавливается триггер 121, разрешая работу счетчика 122. По следующему синхроимпульсу первой серии счетчик 122 переходит в состояние 111, в котором по синхроимпульсу третьей серии на выход 40 вьщается импульс. Следующим импульсом первой синхросерии счетчик 122 переводится в состояние 000. В этом состоянии по импульсу второй синхросерии на выходе элемента И 106 вырабатывается импульс, поступающий через элемент ИЛИ 120 на входсброса триггера 121, который сбрасывается, запре щая дальнейшую работу счетчика 122. Цикл работы узла 8 заканчивается. Счетчик 122 и триггер 121 находятся в исходном состоянии. Следукяций цикл работы узла 8 начинается в исходном состоянии с приходом разрешающих сигналов на входы 50 и 51,

как это было описано вы.ие. 1 I

Применение предлагаемого изобретения позволяет расширить функциональные возможности устройства.

t;;

CQ i

C«sl

If5 М til W V3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для приоритетного обслуживания запросов | 1981 |

|

SU955069A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-07—Публикация

1983-08-12—Подача