Изобретение относится к вьгчисли- тельной технике, в частности к устройствам для сопряжения абонентов с ЦВМ, и может быть использовано в информационно-управляющих системах. Цель изобретения - повышение быстродействия устройства,

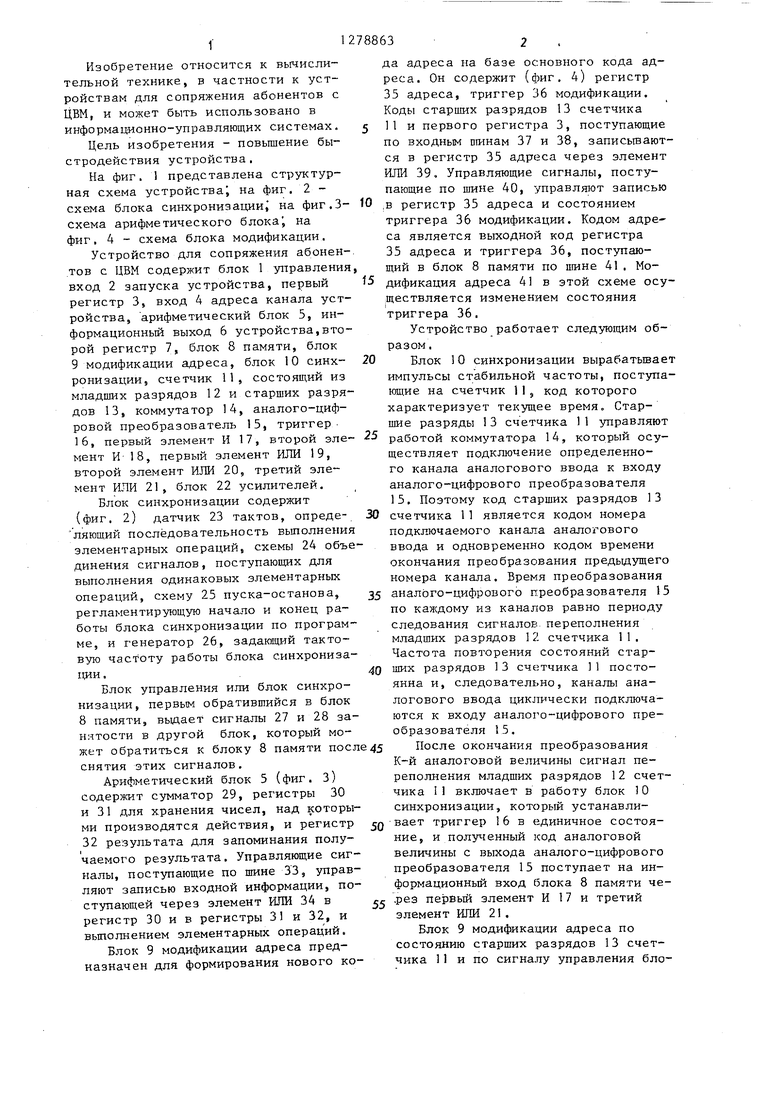

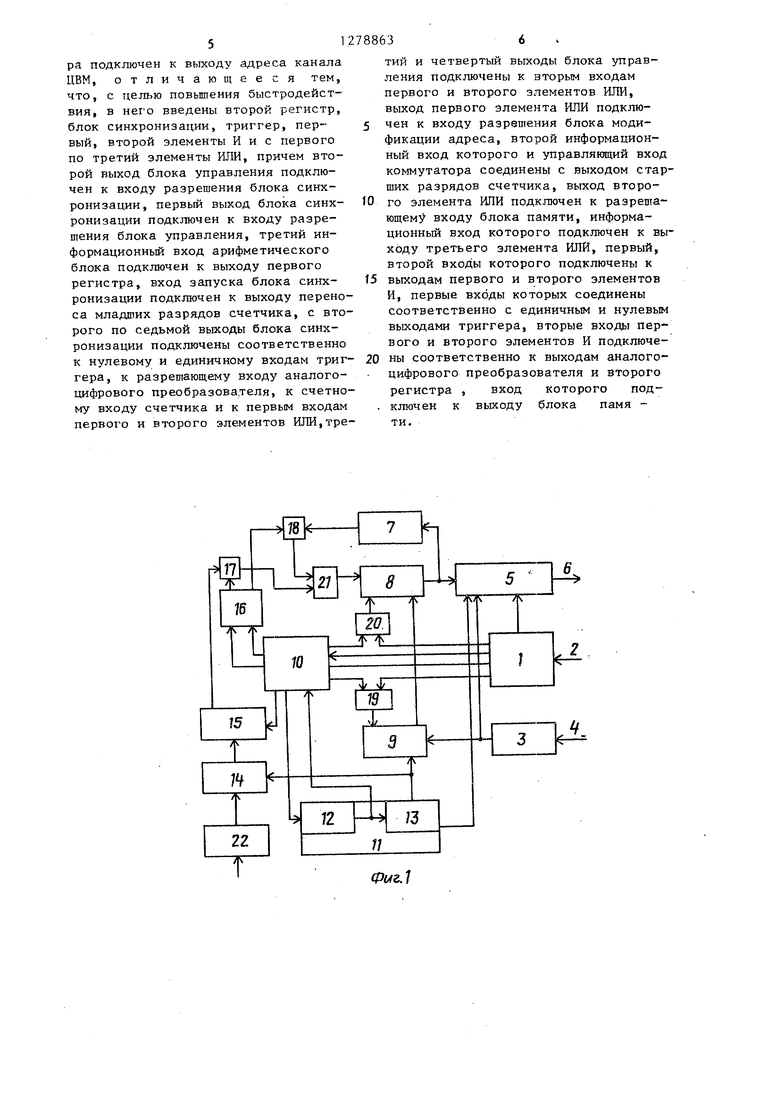

На фиг. 1 представлена структурная схема устройства, на фиг. 2 - схема блока синхронизации на фиг.З- схема арифметического блока, на фиг. 4 схема блока модификации.

Устройство для сопряжения абонен,тов с ЦВМ содержит блок 1 управления вход 2 запуска устройства, первый регистр 3, вход 4 адреса канала устройства, арифметический блок 5, информационный выход 6 устройства,второй регистр 7, блок 8 памяти, блок 9 модификации адреса, блок 10 синхронизации, счетчик 11, состоящий из младших разрядов 12 и старших разрядов 13, коммутатор 14, аналого-цифровой преобразователь 15, триггер 16, первый элемент И 17, второй элемент И- 18, первый элемент ИЛИ 19, второй элемент ИЛИ 20, третий элемент ИЛИ 21, блок 22 усилителей.

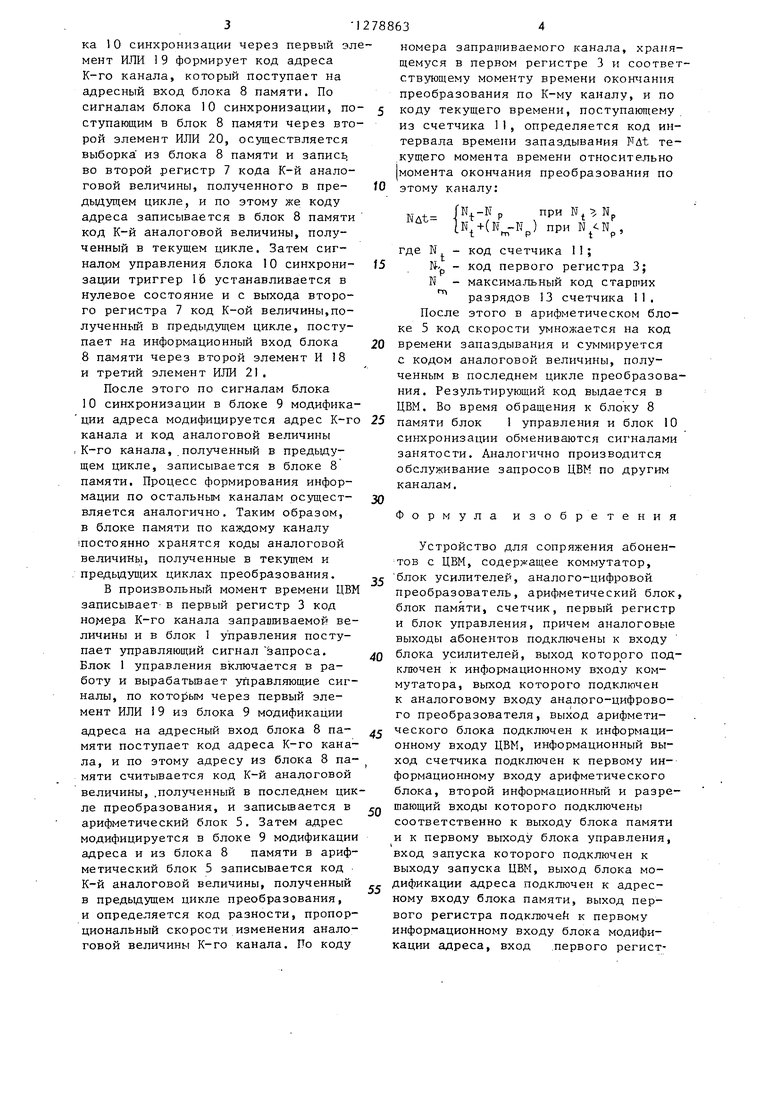

Блок синхронизации содержит (фиг. 2) датчик 23 тактов, опреде- ляющий последовательность выполнения элементарных операций, схемы 24 объединения сигналов, поступающих для выполнения одинаковых элементарных операций, схему 25 пуска-останова, регламентирующую начало и конец работы блока синхронизации по программе, и генератор 26, задающий тактовую частоту работы блока синхронизации.

Блок управления или блок синхронизации, первым обратившийся в блок 8 памяти, выдает сигналы 27 и 28 занятости в другой блок, который может обратиться к блоку 8 памяти посл снятия этих сигналов.

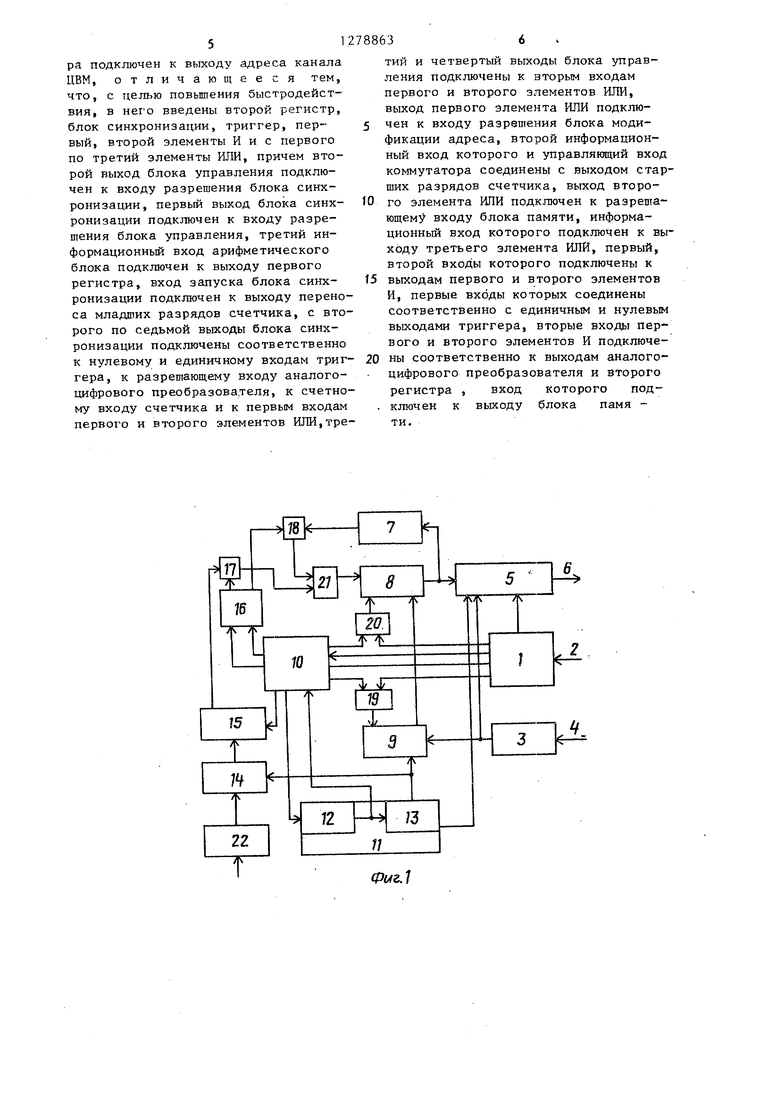

Арифметический блок 5 (фиг. З) содержит сумматор 29, регистры 30 и 31 для хранения чисел, над которыми производятся действия, и регистр 32 результата для запоминания получаемого результата. Управляющие CHI налы, поступающие по шине З З, управляют записью входной информации, поступающей через элемент ИЛИ 34 в регистр 30 и в регистры 31 и 32, и выполнением элементарных операций. Блок 9 модификации адреса предназначен для формирования нового ко

5

0

5

5

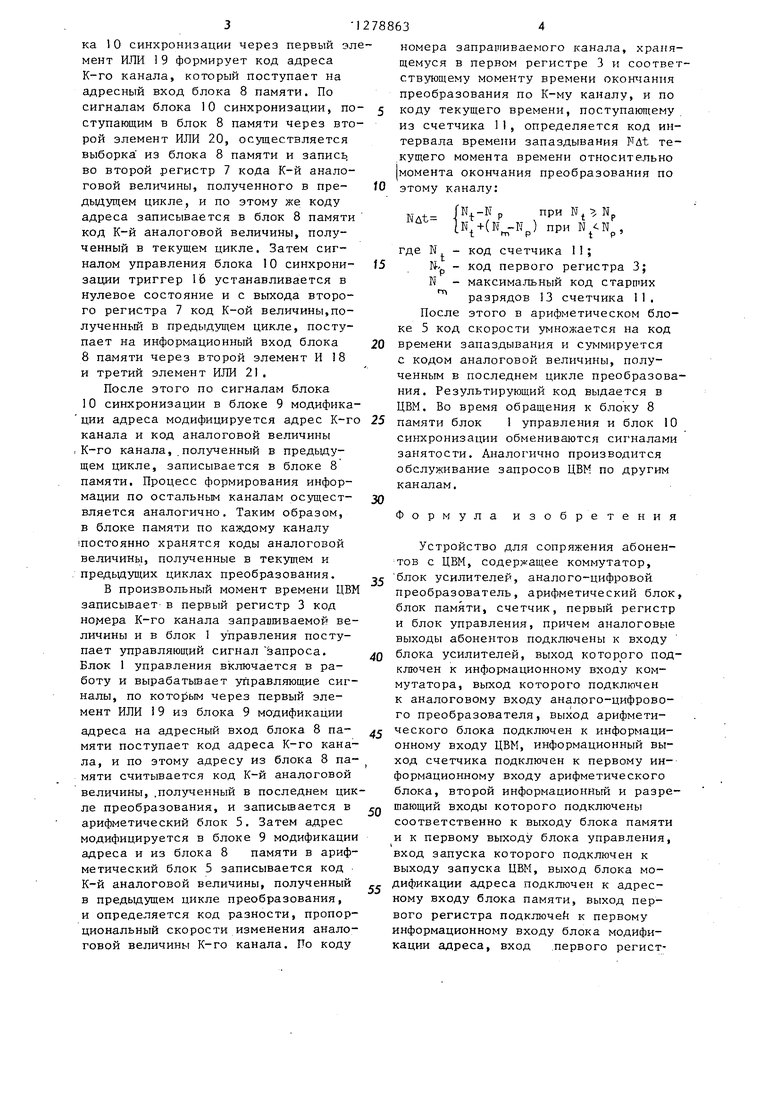

да адреса на базе основного кода адреса. Он содержит (фиг. 4) регистр 35 адреса, триггер 36 модификации. Коды старших разрядов 13 счетчика 11 и первого регистра 3, поступающие по входным шинам 37 и 38, записьшают- ся в регистр 35 адреса через элемент ИЛИ 39, Управляющие сигналы, поступающие по шине 40, управляют записью .в регистр 35 адреса и состоянием триггера 36 модификации. Кодом адре- са является выходной код регистра 35 адреса и триггера 36, поступающий в блок 8 памяти по шине 41. Модификация адреса 41 в этой схеме осуществляется изменением состояния i

триггера 36.

Устройство работает следующим образом.

Блок 10 синхронизации вырабатьшает импульсы стабильной частоты, поступающие на счетчик 11, код которого характеризует текущее время Старшие разряды 13 счетчика 11 управляют работой коммутатора 14, который осуществляет подключение определенного канала аналогового ввода к входу аналого-цифрового преобразователя 15. Поэтому код старших разрядов 13 счетчика 11 является кодом номера подключаемого канала аналогового ввода и одновременно кодом времени окончания преобразования предыдущего номера канала. Время преобразования аналого-цифрового преобразователя 15 по каждому из каналов равно периоду следования сигналов переполнения младших разрядов I2 счетчика 11. Частота повторения состояний старших разрядов 13 счетчика 11 постоянна и, следовательно, каналы аналогового ввода циклически подключаются к входу аналого-цифрового преобразователя 15.

После окончания преобразования К-й аналоговой величины сигнал переполнения младших разрядов 12 счетчика II включает в работу блок 10 синхронизации, который устанавли- вает триггер 16 в единичное состояние, и полу 1енный код аналоговой величины с выхода аналого-цифрового преобразователя 15 поступает на информационный вход блока 8 памяти че- с .рез первьш элемент И 17 и третий элемент ИЛИ 2.

Блок 9 модификации адреса по состоянию старших разрядов 13 счетчика 11 и по сигналу управления бло0

5

0

0

ка 10 синхронизации через первый элмент ИЛИ 19 формирует код адреса К-го канала, который поступает на адресный вход блока 8 памяти. По сигналам блока 10 синхронизации, по ступающим в блок 8 памяти через второй элемент ИЛИ 20, осуществляется выборка из блока В памяти и запись во второй регистр 7 кода К-й аналоговой величины, полученного в пре- дыдущем цикле, и по этому же коду адреса записывается в блок 8 памяти код К-й аналоговой величины, полученный в текущем цикле. Затем сигналом управления блока 10 синхрони- зации триггер 16 устанавливается в нулевое состояние и с выхода второго регистра 7 код К-ой величины,полученный в предыдущем цикле, поступает на информационный вход блока 8 памяти через второй элемент И 18 и третий элемент ИЛИ 21.

После этого по сигналам блока 10 синхронизации в блоке 9 модифика- ции адреса модифицируется адрес К-го канала и код аналоговой величины К-го канала,.полученный в предыдущем цикле, записывается в блоке 8 памяти. Процесс формирования информации по остальным каналам осущест- вляется аналогично. Таким образом, в блоке памяти по каждому каналу 1ПОСТОЯННО хранятся коды аналоговой величины, полученные в текущем и предьщущих циклах преобразования.

В произвольный момент времени ЦВМ записывает в первый регистр 3 код номера К-го канала запраишваемой величины и в блок I управления поступает управляющий сигнал запроса. Блок 1 управления включается в работу и вырабатьшает управляющие сигналы, по KOTOj5biM через первый элемент ИЛИ 19 из блока 9 модификации адреса на адресный вход блока 8 па- мяти поступает код адреса К-го канала, и по этому адресу из блока 8 па- мяти считывается код К-й аналоговой величины, .полученный в последнем цикле преобразования, и записьшается в арифметический блок 5, Затем адрес модифицируется в блоке 9 модификации адреса и из блока 8 памяти в арифметический блок 5 записывается код К-й аналоговой величины, полученный в предыдущем цикле преобразования, и определяется код разности, пропорциональный скорости изменения аналоговой величины К-го канала. По коду

номера запрашиваемого канала, хранящемуся в первом регистре 3 и соответствующему моменту времени окончания преобразования по К-му каналу, и по коду текущего времени, поступающему из счетчика 11, определяется код интервала времени запаздывания NAt текущего момента времени относительно момента окончания преобразования по этому каналу:

- .,

при N NP р) при ,

5 0 5 0

5 О

д

5

где N - код счетчика П;

N-. - код первого регистра 3;

N - максимальный код старших разрядов 13 счетчика 1 1 . После этого в арифметическом блоке 5 код скорости умножается на код времени запаздывания и суммируется с кодом аналоговой величины, полученным в последнем цикле преобразования. Результирующий код выдается в ЦВМ. Во время обращения к блоку 8 памяти блок 1 управления и блок 10 синхронизации обмениваются сигналами занятости. Аналогично производится обслуживание запросов ЦВМ по другим каналам.

Формула изобретения

Устройство для сопряжения абонен- тов с ЦВМ, содержащее коммутатор, блок усилителей, аналого-цифровой преобразователь, арифметический блок, блок памяти, счетчик, первый регистр и блок управления, причем аналоговые выходы абонентов подключены к входу блока усилителей, выход которого подключен к информационному входу коммутатора, выход которого подключен к аналоговому входу аналого-цифрового преобразователя, выход арифметического блока подключен к информационному входу ЦВМ, информационный выход счетчика подключен к первому информационному входу арифметического блока, второй информационный и разрешающий входы которого подключены соответственно к выходу блока памяти и к первому выходу блока управления, вход запуска которого подключен к выходу запуска ЦВМ, выход блока модификации адреса подключен к адресному входу блока памяти, выход первого регистра подключей к первому информационному входу блока модификации адреса, вход первого регистpa подключен к выходу адреса канала ЦВМ, отличающееся тем, что, с целью повышения быстродействия, в нег о введены второй регистр, блок синхронизации, триггер, первый, второй элементы И и с первого по третий элементы ИЛИ, причем второй выход блока управления подключен к входу разрешения блока синхронизации , первый выход блока синхронизации подключен к входу разрешения блока управления, третий информационный вход арифметического блока подключен к выходу первого регистра, вход запуска блока синхронизации подключен к выходу переноса младших разрядов счетчика, с второго по седьмой выходы блока синхронизации подключены соответственно к нулевому и единичному входам триггера, к разрешающему входу аналого- цифрового преобразователя, к счетному входу счетчика и к первым входам первого и второго элементов ИЛИ,тре

5

0

тий и четвертый выходы блока управления подключены к вторым входам первого и второго элементов ИЛИ, выход первого элемента ИЛИ подключен к входу разрешения блока модификации адреса, второй информационный вход которого и управляющий вход коммутатора соединены с выходом старших разрядов счетчика, выход второго элемента ИЛИ подключен к разреша- ющемз входу блока памяти, информационный вход которого подключен к выходу третьего элемента ИЛИ, первый, второй входы которого подключены к выходам первого и второго элементов И, первые входы которых соединены соответственно с единичным и нулевым выходами триггера, вторые входы первого и второго элементов И подключены соответственно к выходам аналого- цифрового преобразователя и второго регистра , вход которого подключен к выходу блока памя - ти.

Фи&Л

Т

фие.г o/n2f/2}

В

/ч

41

4f

35

Jff

тт

J8

0 фиеЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения абонентов с цвм | 1976 |

|

SU641437A1 |

| Устройство для сопряжения ЦВМ с магнитофоном | 1985 |

|

SU1317445A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1985 |

|

SU1291989A1 |

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1987 |

|

SU1490691A1 |

| Устройство для ввода информации | 1991 |

|

SU1800452A1 |

| Устройство для реализации алгоритма быстрого преобразования фурье | 1973 |

|

SU480079A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

Изобретение относится к области вычислительной техники, в частности к устройствам для сопряжения абонентов с ЦВМ, и может быть ис. пользовано в информационно-управляющих автоматизированных системах. Целью изобретения является повышение быстродействия устройства.Устройство содержит первый, второй блоки синхронизации, первый, второй регистры, блок памяти, аналого-цифровой преобразователь, коммутатор,блок усилителей, счетчик, триггер, арифметический блок, блок модификации адреса, первый, второй элементы И, с первого по третий элементы ИЛИ. Устройство обеспечивает прием и преобразование в цифровую форму акало- говых сигналов абонентов ЦВМ и запись полученных значений в память, откуда они могут быть считаны ЦВМ. 4 ил. О & 00 а оэ

Составитель С.Бурухин Редактор Н.Тупица Техред Л.ОлейникКорректор. М.Демчик

Заказ 6840/48 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород,ул. Проектная, 4

| Устройство для сопряжения | 1979 |

|

SU881722A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения абонентов с цвм | 1976 |

|

SU641437A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-23—Публикация

1985-05-15—Подача