сд

оо «i l

СП

Изобретение относится к вычислительной технике и может быть использовано в цифровых многоканальных системах обработки случайных процес- сов.

Целью изобретения является повышение быстродействия.

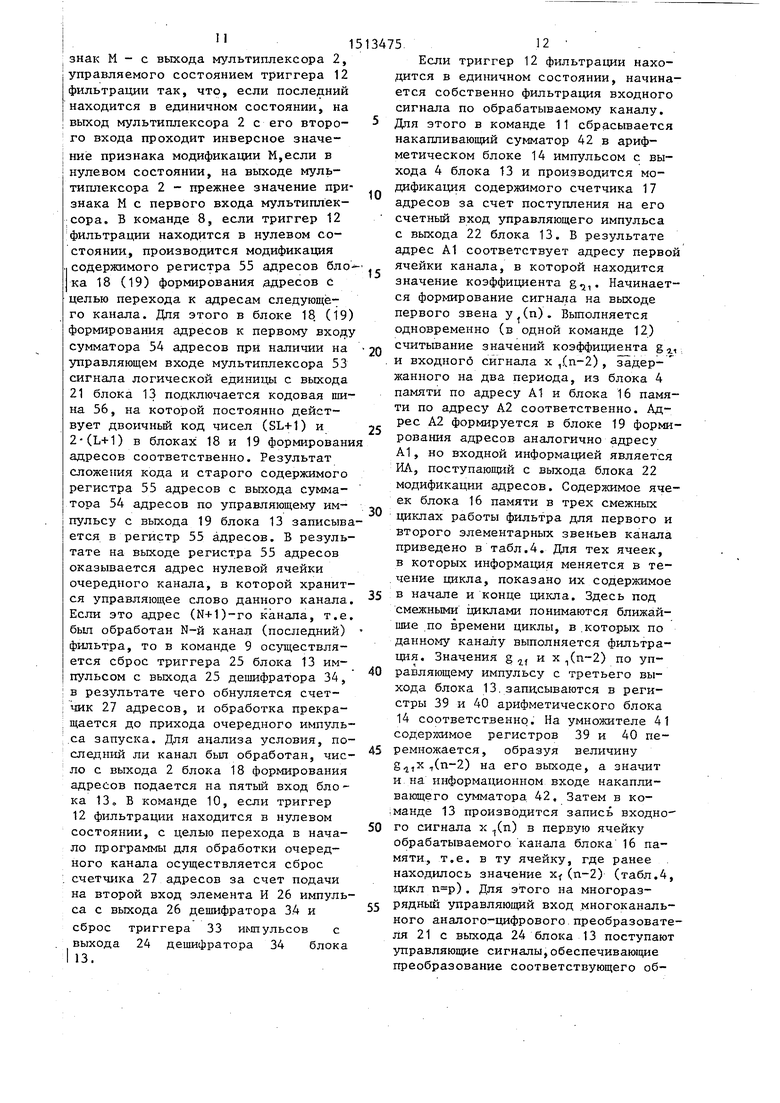

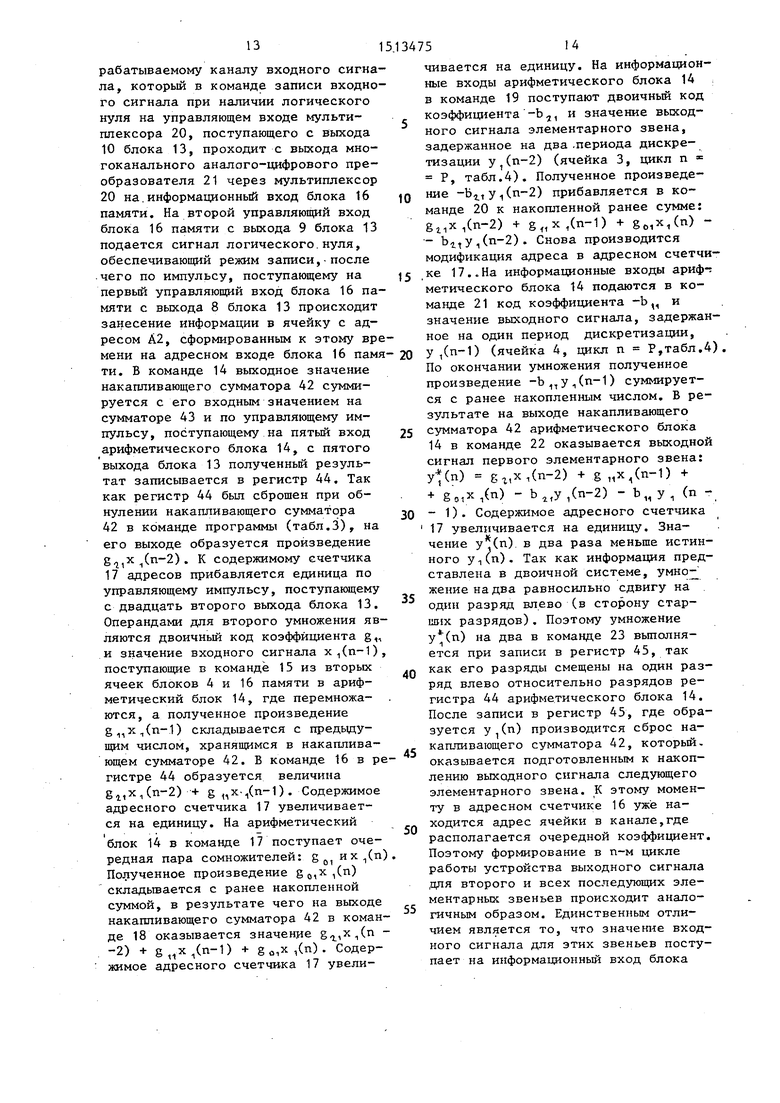

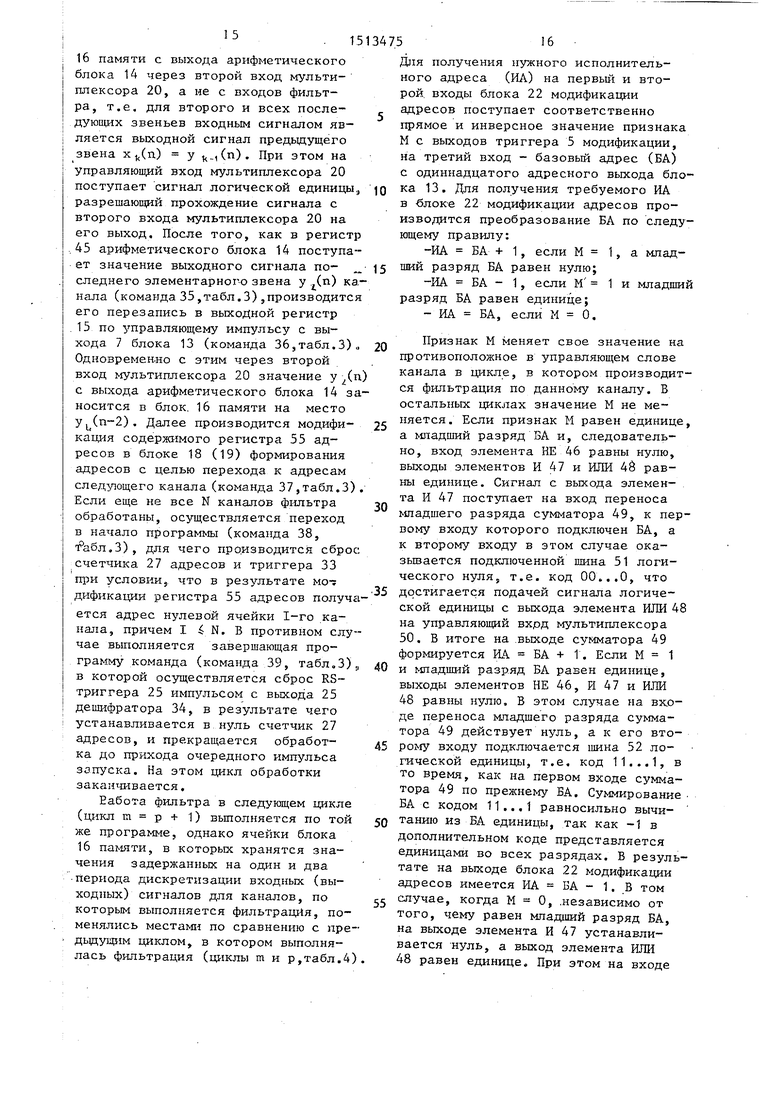

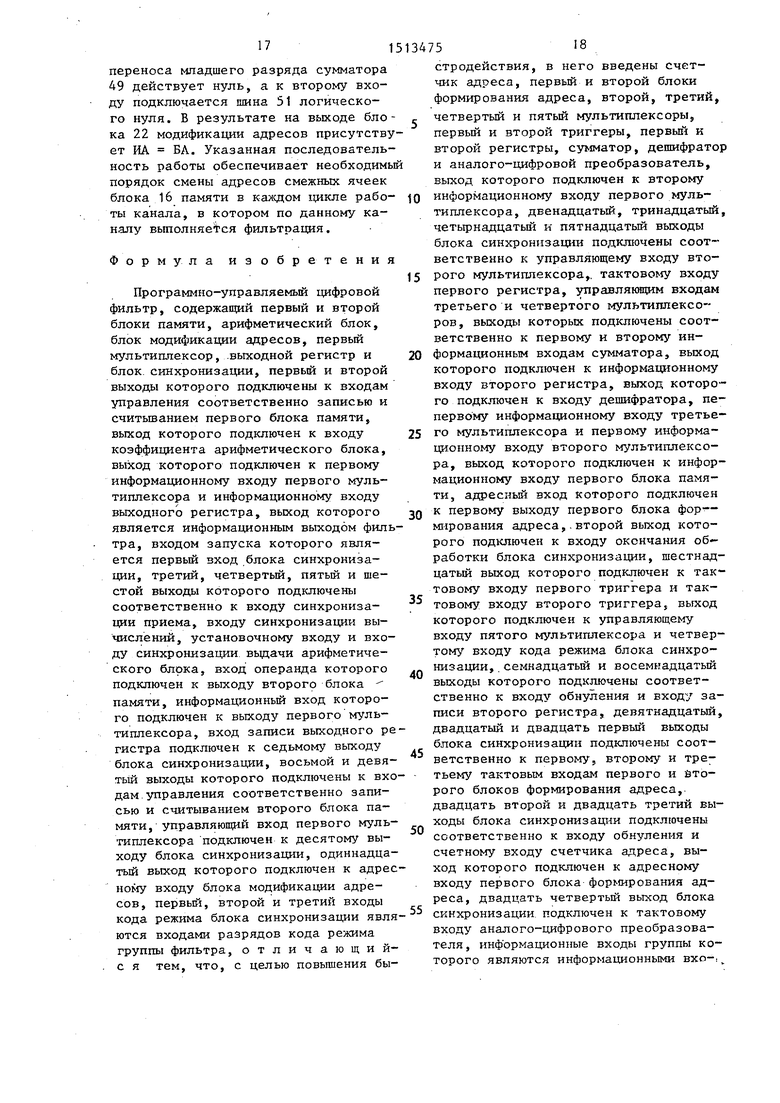

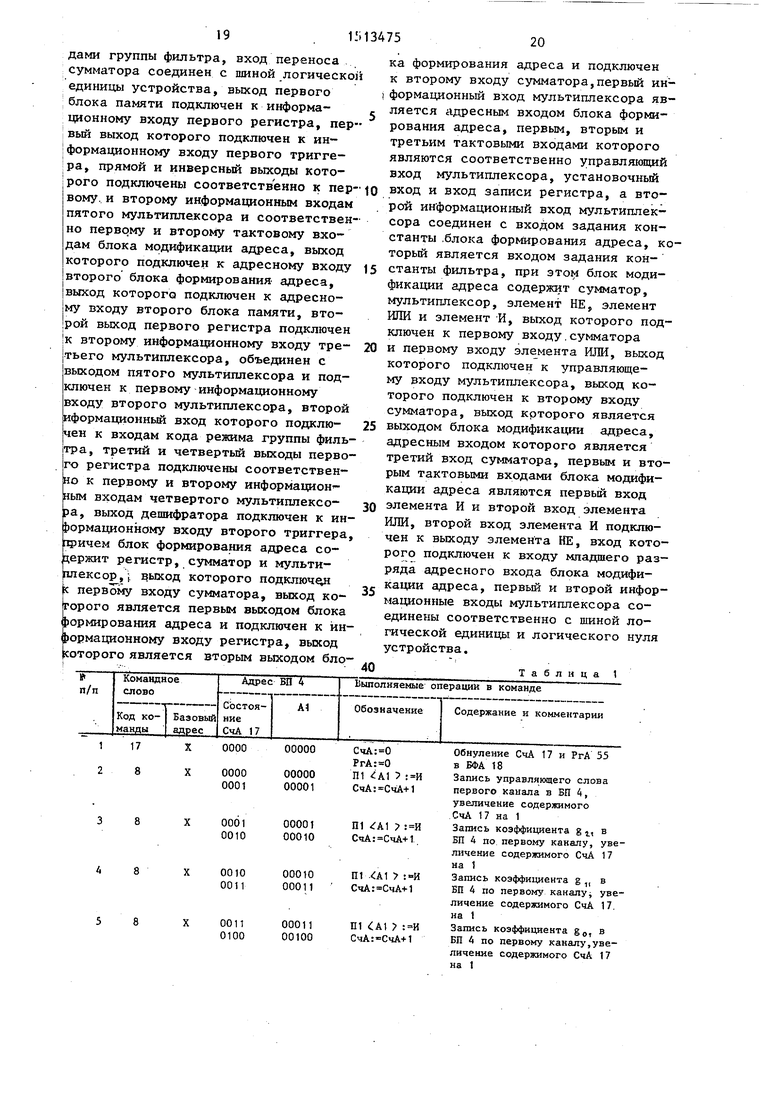

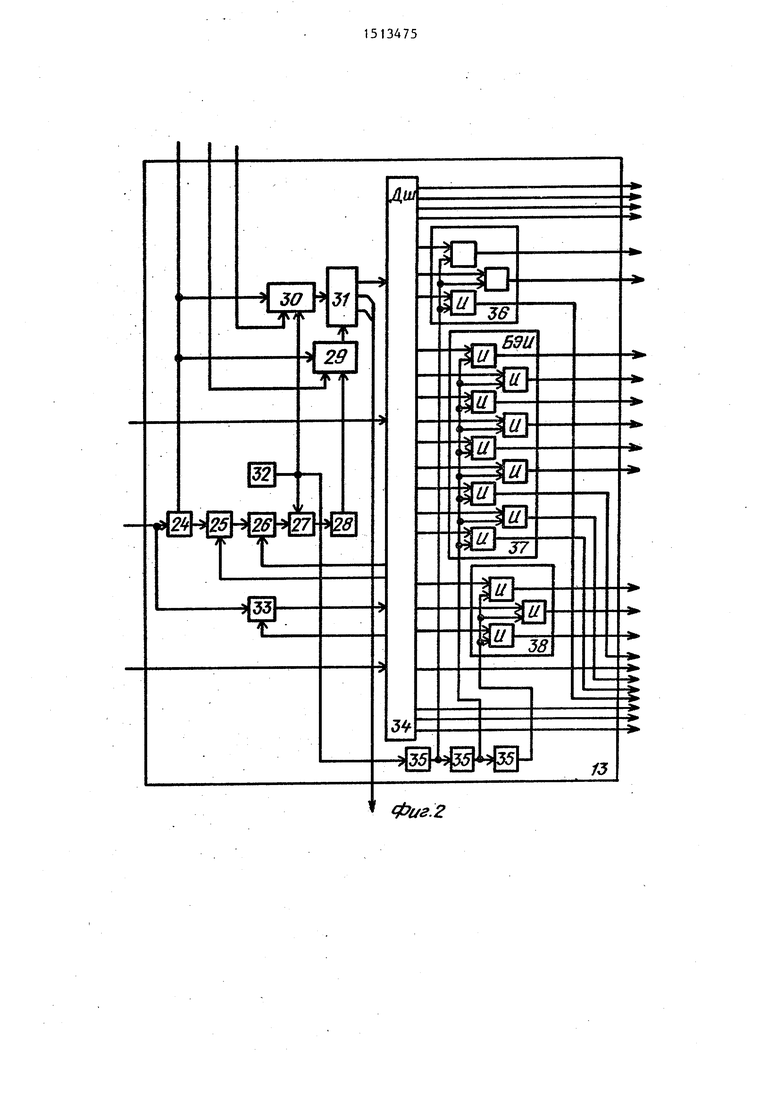

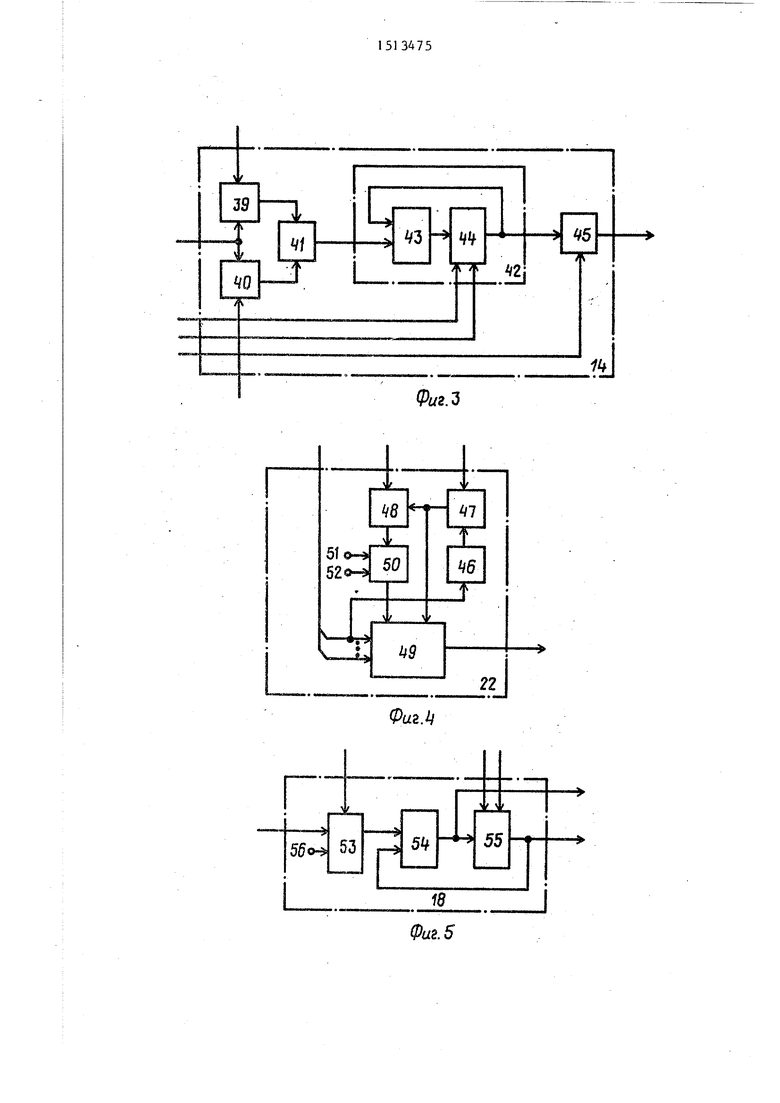

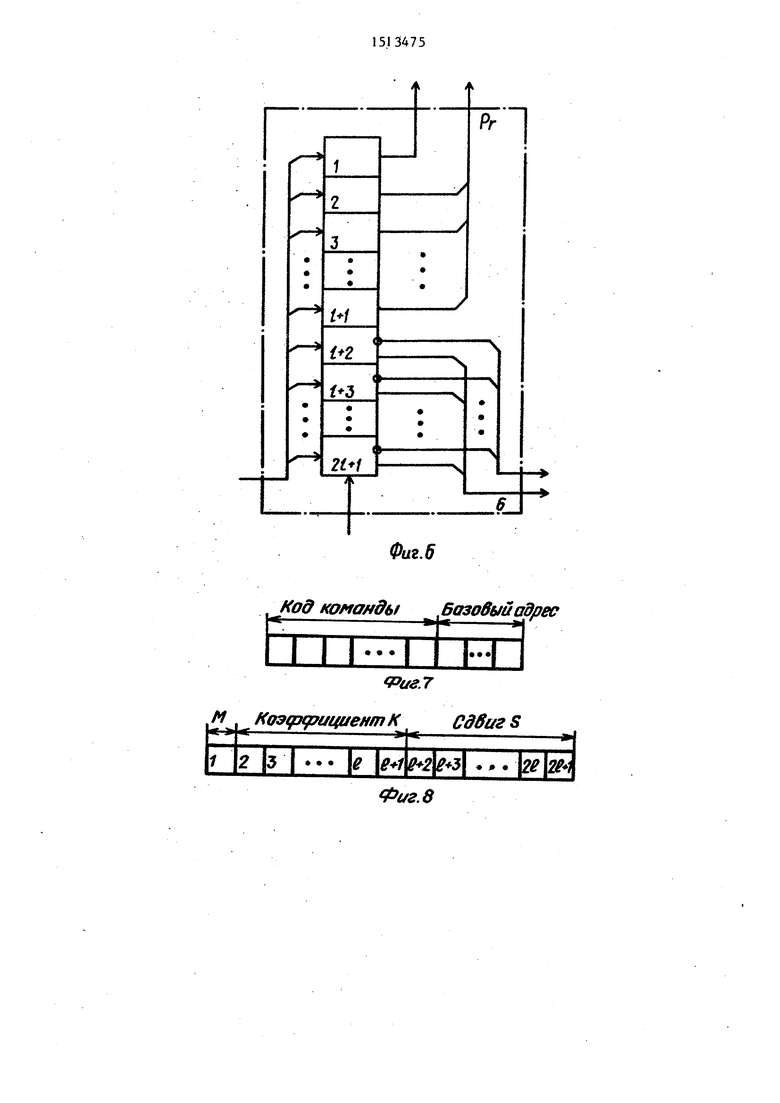

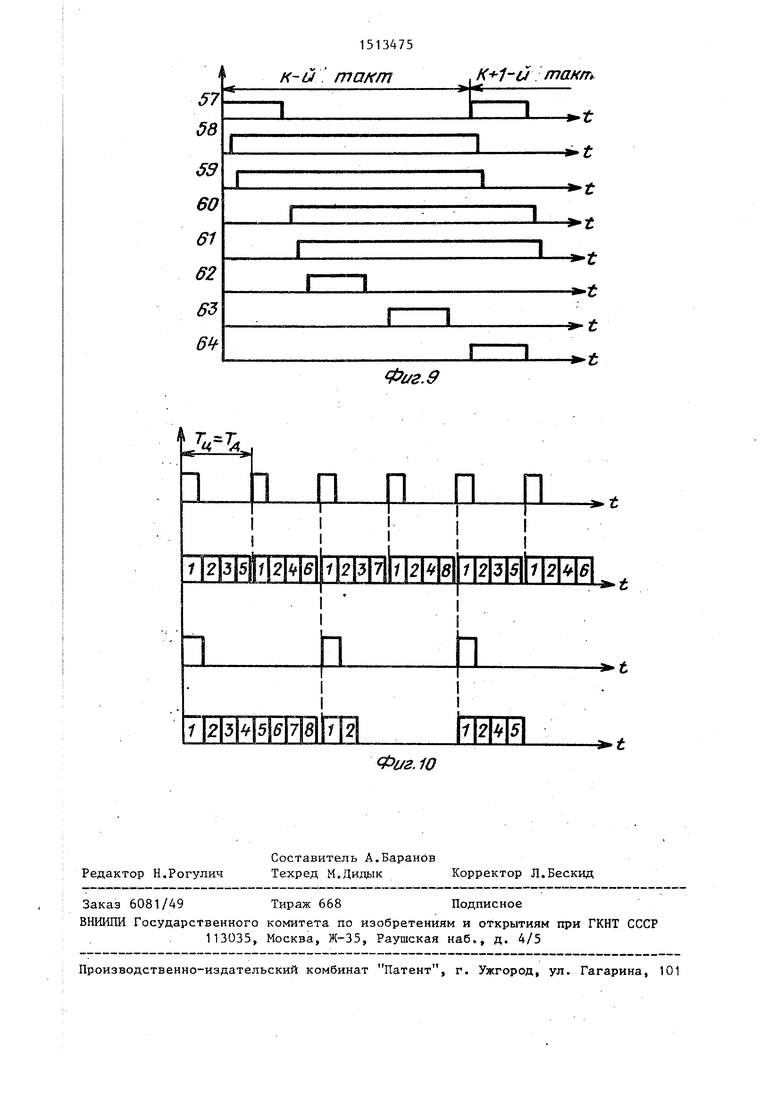

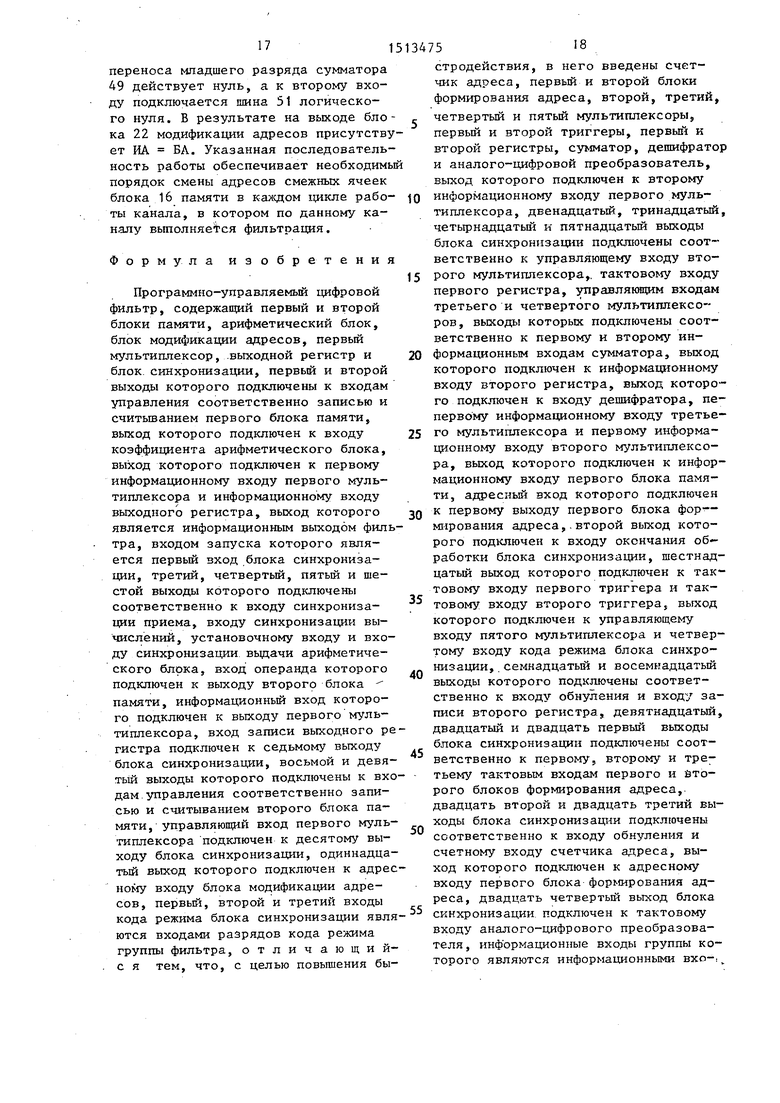

На фиг.1 изображена функциональна схема программно-управляемого цифро- вого фильтра; на фиг.2 - блок синхронизации; на фиг.З - арифметический блок; на фиг.4 - блок модификации адресов; на фиг.З - блок формирования адресов; на фиг.6 - регистр; на фиг.7 - структура командного слова; на фиг.8 - структура управляющего слова; на фиг.9 - временные диаграммы управляющих сигналов; на фиг. 10 -. временные диаграммы распределения ка налов по циклам обработки.

Программно-управляемый фильтр (фиг.1) содержит вход 1 задания режима, мультиплексоры 2 и 3, блок 4 памяти, триггер 5, регистр 6, муль- типлексоры 7 и 8, сумматор 9, регис 10, дешифратор 11, триггер 12, блок 13 синхронизации, арифметический блок 14, выходной регистр 15, блок 16 памяти, счетчик 17 адреса, блоки 18 и 19 формирования адреса, мультиплексор 20, аналого-цифровой преобразователь 21, блок 22 модификации адреса, вход 23 -задания логической единицы.

Блок 13 синхронизации (фиг.2) содержит элемент И 24, триггер 25, элемент И 26, счетчик 27, микропрограммную память 28, мультиплексор 29 и 30, регистр 31 команд, генера- тор 32 тактовых импульсов, триггер 33, дешифратор 34, элементы 35 за-, держки, блоки элементов И 36-38.

Арифметический блок 14 (фиг.З) :содержит регистры 39 и 40, умножите ;41, накашшвающий сумматор 42, состоящий из сумматора 43 и регистра 44 и регистр 45.

Блок 22 модификации адреса (фиг. содержит элемент НЕ 46, элемент И 47, элемент ИЛИ 48, сумматор 49, мультиплексор 50, входы 51 и 52 задания логического нуля и единицы,

, Блок 18 формирования адреса (фиг.5) содержит мультиплексор 53, сумматор 54, регистр 55, вход 56 задания константы.

В (21+1)-разрядном регистре 6 (фиг,6) первьш выход образован прямым выходом старшего (первого) разряда, второй 1-разрядный выход - прямыми выходаш разрядов регистра 6 с второго по (1+1)-ый,третий 1-разрядный выход - инверсными выходами разрядов с ,(1+2)-го по (21+1)-й, четвертый 1-разрядный выход - пря- 1Ф1ми выходами разрядов с (1+2)-го по (21+1)-и. Первый вход регистра 6 является его информационным входом, а второй вход - входом записи регистра.

Фильтр работает следующим обра зом.

Каналы фильтрации обрабатываются поочередно. Для каждогЬ элементарного звена второго порядка в каждом из каналов фильтр реализует разностное уравнение. Управление последовательностью работы цифрового фильтра производится блоком 13 синхронизации представляющ1-1м собой микропрограммный автомат. Микропрограмма работы хранится в микропрограммной памяти 28..

Перед началом фильтрации производится запись коэффициентов фильтра из блока 1 задания коэффициентов в блок 4 памяти, т.е. исходное про- гpaм ra:poвaниe каналов фильтрации на требуемые амплитудно-частотные характеристики (АЧХ). Для обеспечения работы каналов фршьтрации с различными значениями частоты дискретизации, кроме, значений коэффициентов, в блок 4-памяти для каждого из каналов записывается (21+1)-разрядное .управляющее слово, структура которого представлена на фиг.8. В управляющих словах, кроме коэффициентов К, определяющих во сколько раз частота работы (частота дискретизации) данного канала ниже частоты работы самого высокочастотного канала, имеются сдвиги S, позволяющие сделать равномерной временнзоо расстановку каналов по циклам обработки, т.е. в коэффициент К и исходное значение сдвига S заложена информация о частоте работы- и временном положении конкретного канала, показывающая, что по данному каналу фильтрация вьшол- няется в каждом (К+1)-м цикле обработки, начиная с (K-S+1)-ro цикла, если считать с момента прихода (после выполнения программирования блока 4 памяти) первого запускающего импульса. Признак модификации М ис

пользуется для формирования исполнительного адреса (ИА) в блоке 22 модификации адресов. Последовательност записи в блок 4 памяти следующая. На второй вход блока 13 синхронизации с входа 1 задания режима подается потенциальный сигнал логического нуля, запрещающий запуск микропро- граммь через элемент И 24 и перек31ю- чающий мультиплексоры 29 и 30 в положение, при котором информационный вход регистра 31 команд оказывается подключенным к третьему входу блока 13, а вход записи - к четвёртому входу блока. После этого начинается выполнение, программы записи коэффициентов фильтра в блок 4 памяти. В процессе записи третий из группы входов 1 через мультиплексор 3 оказы вается подключенным к входу блока 4 памяти, для чего на управляющий вход мультиплексора 3 с выхода 12 блока 13 подается сигнал логического нуля. Командное слово, установленное на входе 1, через мультиплексор 29 записывается в регистр 31 команд по импульсу, поступающему с входа 1 через мультиплексор 30 на вход записи регистра 31 команд. Командное слово (фиг.7) состоит из кода команды и базового адреса (БА). При записи информации с входа блок 4 памяти с входа 1 .блока 13 появляется сигнал логического нуля, устанавливающий режим записи, сама запись производится по управляющему импульсу, появляющемуся на выходе 2 блока 13. Запись информации производится по адресу А1, поступающему на адресный вход блока 4 памяти с первого выхода блока 18 формирования адресов. Адрес А1 представляет собой сумму содержимого счетчика 17 адресов и регистра 55 адресов блока 18 формирования адресов. Работа блока 18 формирования адресов приведена в описании внутренней программы фильтра.

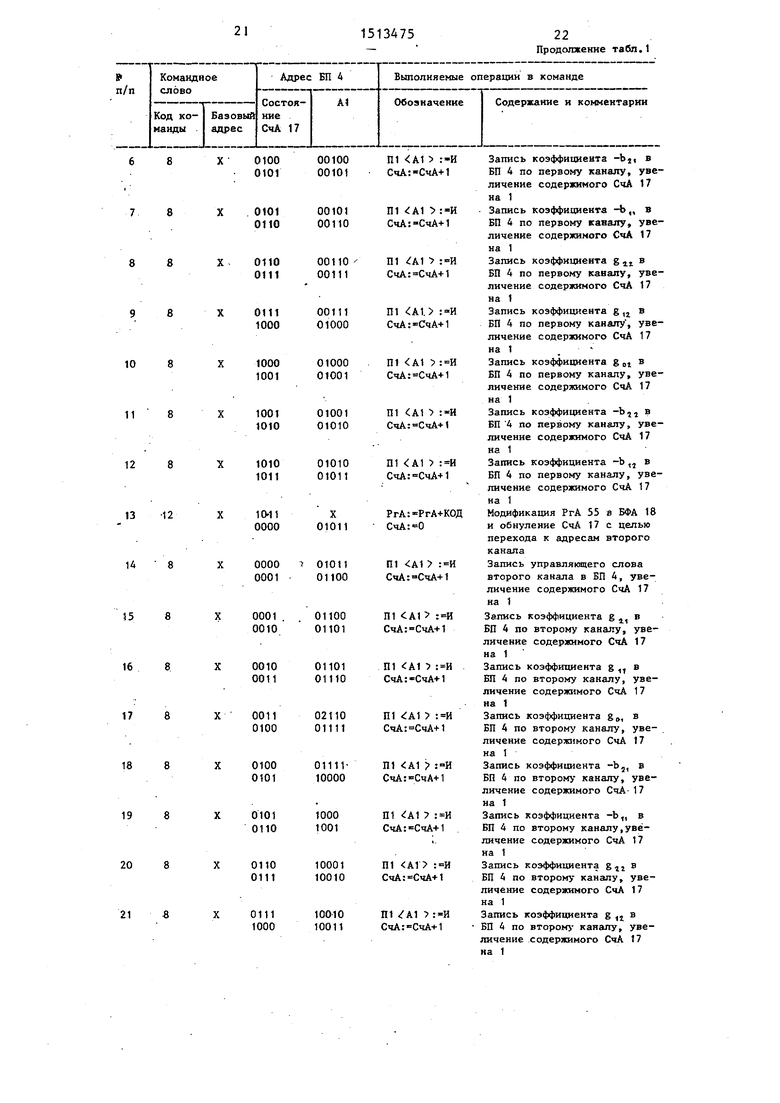

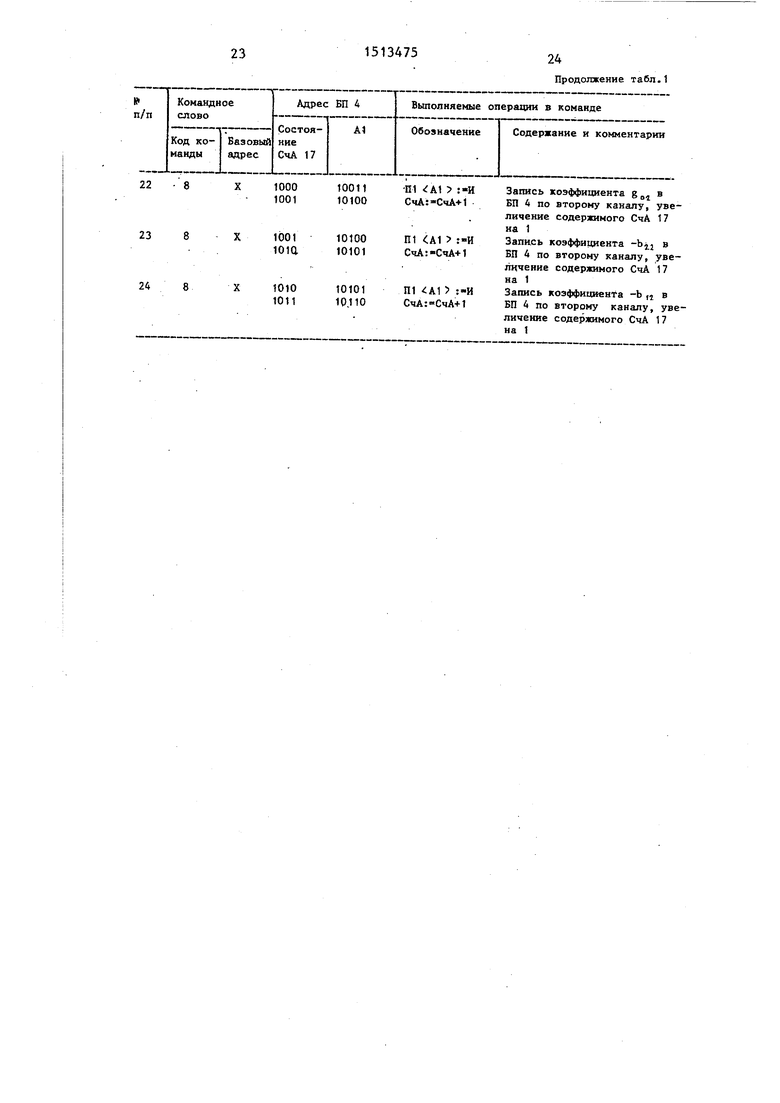

Программа записи коэффициентов фильтра четвертого порядка, состоящего из двух звеньев второго порядка, для случая двухканального устройства приведена в табл.1, где приняты следующие обозначения: П1 А1 - содержимое ячейки блока 4 памяти, имеющей адрес А1; И - число на первом входе мультиплексора 3, поступающее из блока задания ко0

5

0

5

0

5

0

5

0

5

эффициентов; X - значение безразлично .

При записи в блок 4 памяти по каждому из каналов сначала заносится управляющее слово, занимакяцее одну ячейку,памяти, затем заносятся коэффициенты первого элементарного звена фильтра, затем второго и т.д. Порядок расположения коэффициентов по каждому к-му элементарному звену следующий: gjt, g, g OK, - b iv, - bik. Для выполнения цифровой фильтрации N каналами, каждый из которых представляет L последовательно соединенных элементарных звеньев второго по рядка, блок 4 памяти должен содержать (SxL+1)xN ячеек.

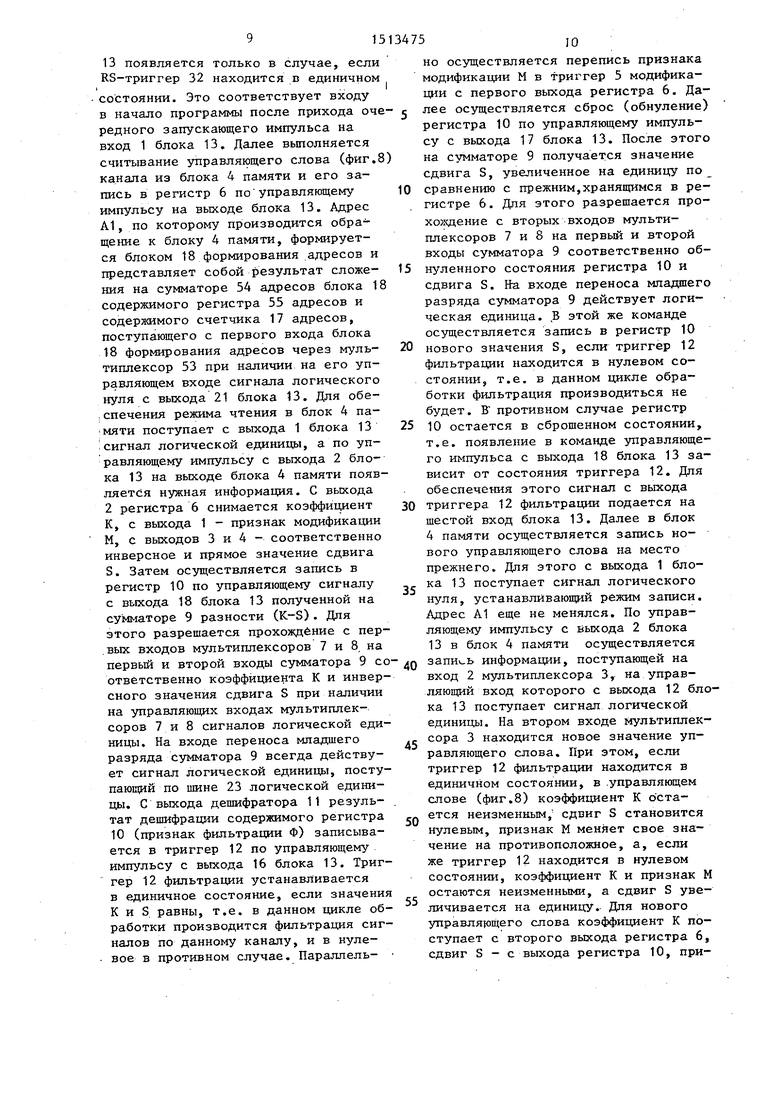

После окончания исходного программирования на вход 2 блока 13 с входа 1 подается потенциальньш сигнал логической единицы, в результате чего устройство переходит в режим работы по внутренней программе. При этом мультиплексоры 29 и 30 переключаются в положение, при котором информационный вход регистра 31 команд оказывается подключенным к выходу микропрограммной памяти 28, а вход записи - к выходу генератора 32 импульсов. Одновременно разрешается прохождение запускающих импульсов с первого входа блока 13 на S-вход триггера 25. При.поступлении запускающего импульса RS-триггер 25 переходит в единичное состояние, на входе установки в нуль счетчика 27 адресов появляется единица. Счетчик 27 адресов начинает счет импульсов генератора 32 импульсов (диаграмма 57, фиг.9), и начинается выполнение (цикл обработки) внутренней программы устройства, хранящейся в микро- программной памяти 28. Каждой из команд соответствует свой набор управляющих сигналов на выходах блока 13, которые определяют необходимую последовательность выполнения операции в цифровом фильтре. Управляющие сигналы на выходах блока 13 формируются следующим образом. В соответствии с состоянием счетчика 27 адресов на выходе микропрограммной памяти 28 появляется командное слово. Интервалы времени (для k-ro такта), в течение .которых адрес на выходе счет- счетчика 28 адресов и командные слова остаются неизменными, представлены соответственно диаграммами 58 и

59 (фиг,9). Командное слово записывается в регистр 31 команд по заднему фронту импульса генератора 32 импульсов (диаграммы 57 и 60, фиг.9 В соответствии с кодом команды на одном или нескольких выходах дешифратора 34 появляется импульс, длительность которого равна длительности команды (диаграмма 61, фиг.9). После стробирования импульсов в блоках 36-38 элементов И и на выходах блока 13 появляется один или несколько управляющих импульсов (диаграммы 62-64, фиг.9)5 наличие и временная расстановка которых обеспечивает требуемую последовательность выполнения операций в фильтре Временное положение импульса на ди аграмме 62 соответствует выходам 2, 16 и 8 блока 13, а на диаграммах 63 и 64 - выходам 17, 18, 13, 3, 4, 5, 20, 22, .23 и 6, 7 и 19 соответственно. Длительность нестробируе- мых управляющих сигналов на выходах 12, 1, 14, 15, 21, 9, 10 и 24 блока 13 равна длительности импульсов на выходах дешифратора 34 (диаграмма 61, фиг.9).

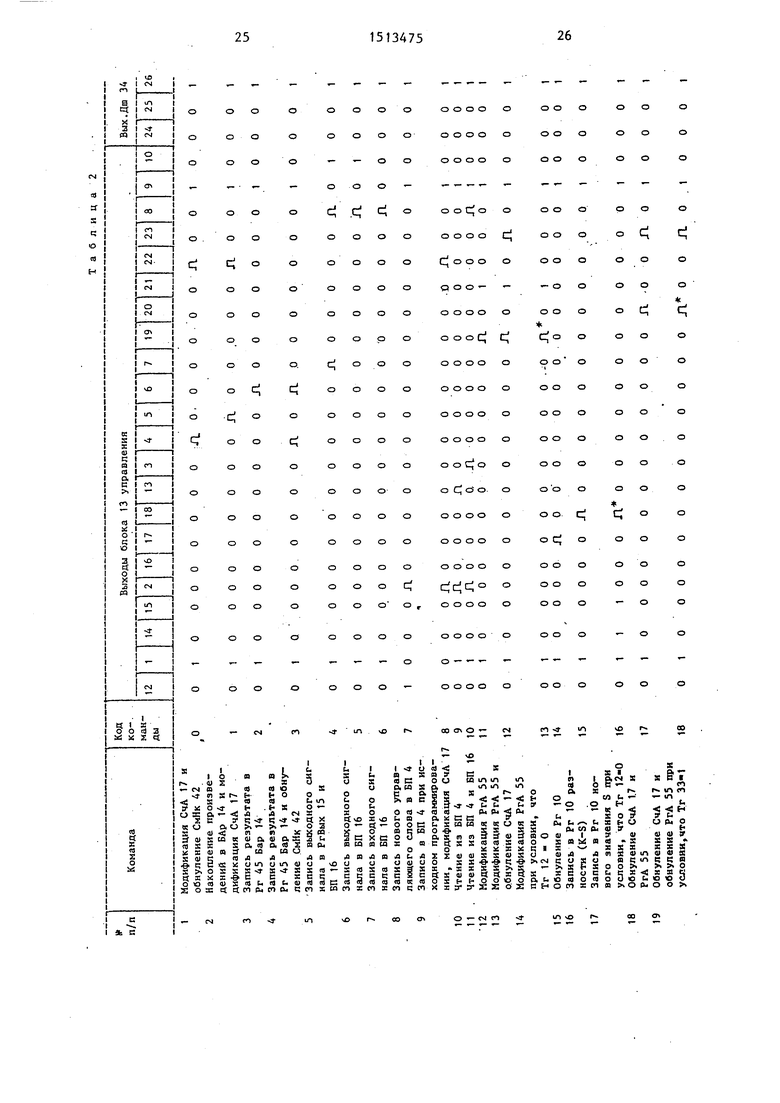

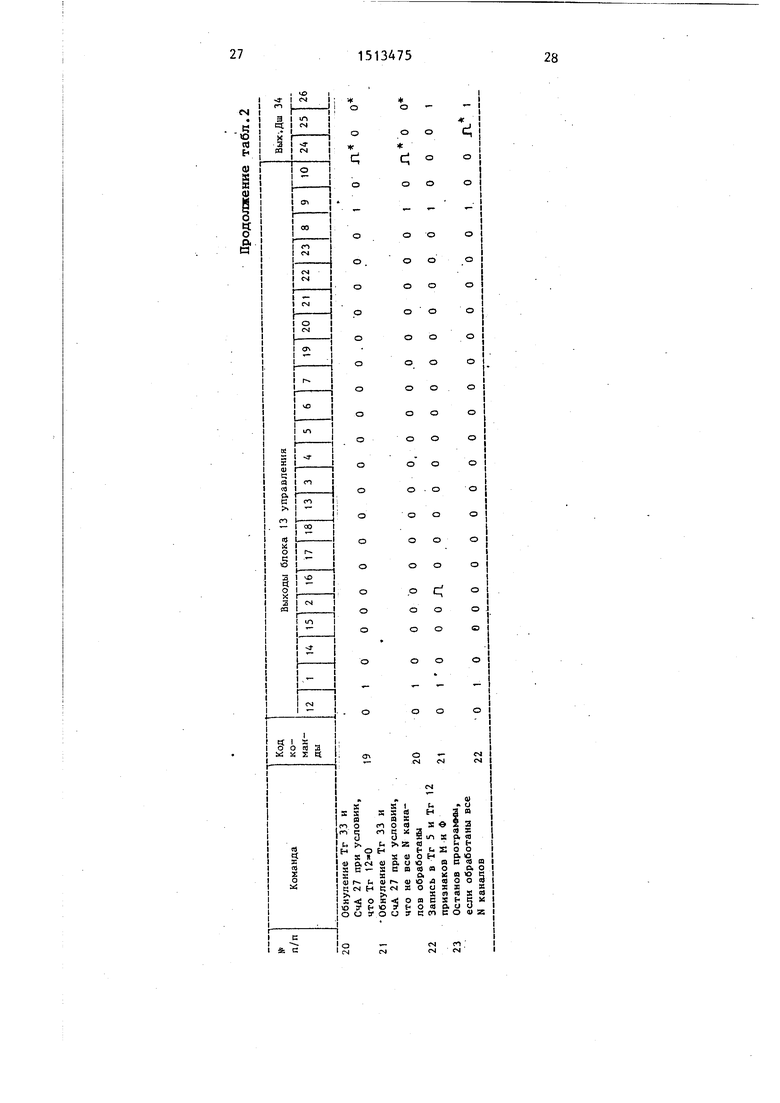

Набор необходимых управляющих сигналов, формируемых блоком 13 для калсдого типа команд приведен, в табл.2, где обозначения О и 1 соответствуют нулевому и единичному состоянию на выходах блока 13 управления длительностью в целую ко- .манду, знаком ГЪ обозначено появление в команде соответствующего управляющего имггульса, символом помечены сигналы, появляющиеся в команде только при выполнении условия, указанного в графе 2 таблицы.

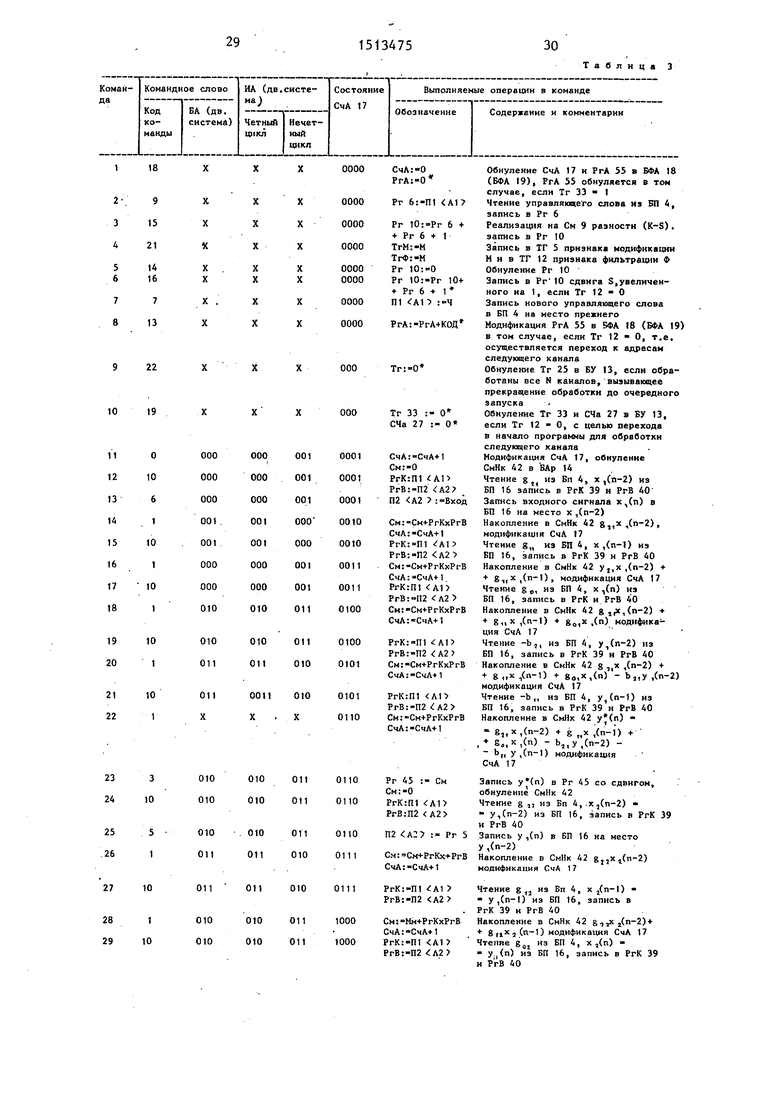

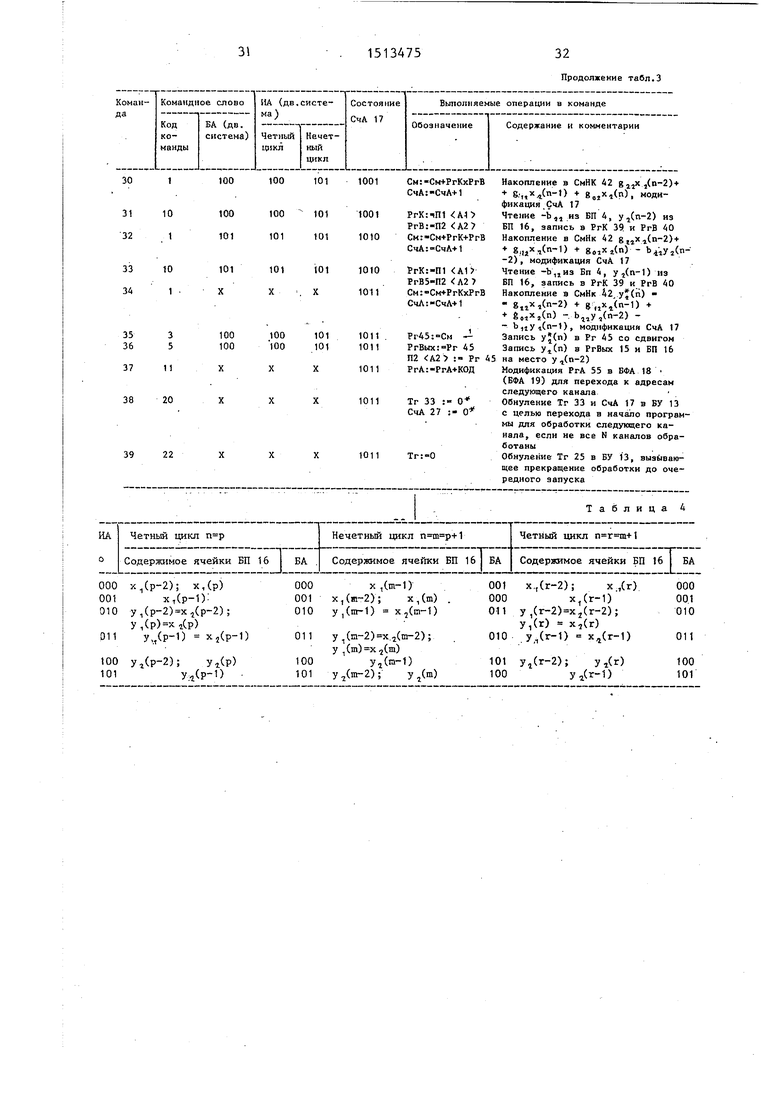

В табл.З приведена внутренняя программа устройства для случая,.когда фильтр состоит из двух звеньев второго порядка. В табл.3 использованы следующие обозначения: Рг 6д, Рг бд, Рг 6 - числа, поступающие . на входы сумматора 9 с второго, третьего и четвертого выходов регистра 6 и.представляющие соответственно К, S, S; М - признак модификации, снимаемый с первого выхода регистра 6; Ф - признак фильтрации, представляющий результат деширации содержимого 1-разрядного регистра 10 на дешифраторе 11; У - чло на втором входе мультиплексора П2 1А2 7 - содержимое ячейки блока

0

5

0

5

0

5

0

45

50

55

16 памяти, имеющей адрес А2, определяемый выходом блока 19 формирования адресов; КОД - состояние входа 56 в блоке 18 (19) формиирования адресов; РгКхРгВ - результат перемножения содержимого регистров 39 и 40 арифметического блока 14;, См «4- - запись со сдвигом влево на один разряд в регистр 45 содержимого накапливающего сумматора 42 арифметического блока 14.

Для реализации программы в блоке 16 памяти для каждого канала каждому элементарному звену 9тведены две ячейки для.хранения значений входных сигналов данного звена, задержанных на два и один период . частоты дискретизации, и две ячейки для хранения аналогичных значений выходного сигнала. Так как выходные отсчеты, к-го элементарного звена являются входными для (k+1)-ro звена, то для выполнения цифровой фильтрации N каналами, каждый из которых представляет L последовательно соединенных элементарных звеньев второго порядка, блок 16 памяти должен содержать 2-(L+1) N ячеек памяти. Для считывания из блока 16 памяти на управляющие входы этого блока должны быть поданы сигнал логической единицы.длительностью в целую команду, устанавливаю.щий режим чтения (девятый выход блока 13) и импульс, по которому на выходе блока 16 памяти появляется число (восьмой

выход блока 13), I

При вьшолнении в-нутренней программы под действием управляющих сигналов, элементы устройства работают в следующей последовательности (табл.3) . В табл.3 символом, помечены опе- , имеющие место при наличии условий, указанных в. графе 8 табли-. цы. В командах с 1 по 7 определяется на основе содержимого управляющего слова данного канала необходимость выполнения фильтрации (решения разностного уравнения в данном цикле обработки) и производится запись нового состояния управляющего слова на место прежнего. Для этого сначала сбрасываются (обнуляются) счетчик 17 адресов и регистр 55 адресов блока 18 (19) формирования адреса. Причем импульс сброса регистра 55 адресов блока 18 (19) форми- рования адресов с выхода 20 блока

10

15

20

25

13 появляется только в случае, если RS-триггер 32 находится в единичном

состоянии. Это соответствует входу в начало программы после прихода оче- редного запускающего импульса на вход 1 блока 13. Далее выполняется считывание управляющего слова (фиг.8) канала из блока 4 памяти и его запись в регистр 6 по управляющему импульсу на выходе блока 13. Адрес А1, по которому производится обращение к блоку 4 памяти, формируется блоком 18 формирования .адресов и представляет собой результат сложения на сумматоре 54 адресов блока 18 содержимого регистра 55 адресов и содерясимого счетчика 17 адресов, поступающего с первого входа блока 18 формирования адресов через мультиплексор 53 при наличии на его управляющем входе сигнала логического куля с выхода 21 блока 13. Для обеспечения режима чтения в блок 4 памяти поступает с выхода 1 блока 13 сигнал логической единицы, а по управляющему импульсу с выхода 2 блока 13 на выходе блока 4 памяти появляется нужная информация. С выхода 2 регистра 6 снимается коэффициент К, с выхода 1 - признак модификации М, с выходов 3 и 4 - соответственно инверсное и прямое значение сдвига S. Затем осуществляется запись в регистр 10 по управляющему сигналу с выхода 18 блока 13 полученной на сумматоре 9 разности (K-S), Для этого разрешается прохождение с первых входов мультиплексоров 7 и 8, на первьй и второй входы сумматора 9 соответственно коэффициента К и инверсного значения сдвига S при наличии на управляющих входах мультиплексоров 7 и 8 сигналов логической единицы. На входе переноса младшего разряда сумматора 9 всегда действует сигнал логической единицы, поступающий по шине 23 логической единицы. С выхода дешифратора 11 резуль- . тат дешифрации содержимого регистра 10 (признак фильтрации Ф) записывается в триггер 12 по управляющему импульсу с выхода 16 блока 13. Триггер 12 фильтрации устанавливается в единичное состояние, если значения К и S равны, т.е. в данном цикле обработки производится фильтрация сигналов по данному каналу, и в нуле- вое в противном случае. Параллель-

Q

30

35

45

50

55

но ос5пцествляется перепись признака модификации М в триггер 5 модификации с первого выхода регистра 6. Далее осуществляется сброс (обнуление) регистра 10 по управляющему импульсу с выхода 17 блока 13. После этого на сумматоре 9 получается значение сдвига S, увеличенное на единицу по сравнению с прежним,хранящимся в регистре 6. Для этого разрешается про- хо хдение с вторых входов мультиплексоров 7 и 8 на первый и второй входы сумматора 9 соответственно обнуленного состояния регистра 10 и сдвига S. На входе переноса младшего разряда сумматора 9 действует логическая единица. В этой же команде осуществляется запись в регистр 10 нового значения S, если триггер 12 фильтрации находится в нулевом состоянии, т.е. в данном цикле обработки фильтрация производиться не будет. В противном случае регистр 10 остается в сброшенном состоянии, т.е. появление в команде згаравляюще- го импульса с выхода 18 блока 13 зависит от состояния триггера 12. Для обеспечения этого сигнал с выхода триггера 12 фильтрации подается на шестой вход блока 13. Далее в блок 4 памяти осуществляется запись нового управляющего слова на место прежнего. Для этого с выхода 1 блока 13 поступает сигнал логического нуля, устанавлйваюш й режим записи. Адрес А1 еще не менялся. По управляющему импульсу с выхода 2 блока 13 в блок 4 памяти осуществляется информации, поступающей на вход 2 мультиплексора 3, на управляющий вход которого с выхода 12 блока 13 поступает сигнал логической единицы. На втором входе мультиплексора 3 находится новое значение управляющего слова. При этом, если триггер 12 фильтрации находится в единичном состоянии, в .управляющем слове (фиг.8) коэффициент К о ста

ется неизменным, сдвиг S становится нулевым, признак М меняет свое значение на противоположное, а, если же триггер 12 находится в нулевом состоянии, коэффициент К и признак М остаются неизменными, а сдвиг S увеличивается на единицу. Для нового управляющего слова коэффициент К поступает с второго выхода регистра 6, сдвиг S - с выхода регистра 10, признак М - с выхода мультиплексора 2, управляемого состоянием триггера 12 фильтрации так, что, если последний находится в единичном состоянии, на выход мультиплексора 2 с его второго входа проходит инверсное значение признака модификации М,если в нулевом состоянии, на выходе мультиплексора 2 - прежнее значение признака М с первого входа мультиплексора, В команде 8, если триггер 12 фильтрации находится в нулевом состоянии, производится модификация содержимого регистра 55 адресов бло ка 18 (19) формирования ддресов с целью перехода к адресам следующего канала. Для этого в блоке 18. (19) формирования адресов к первому сумматора 54 адресов при наличии на управляющем входе мультиплексора 53 сигнала логической единицы с выхода 21 блока 13 подключается кодовая шина 56, на которой постоянно действует двоичньй код чисел (SL+1) и 2-(L+1) в блоках 18 и 19 формировани адресов соответственно. Результат сложения кода и старого содержимого регистра 55 адресов с выхода сумматора 54 адресов по управляющему импульсу с выхода 19 блока 13 записывается в регистр 55 адресов. В результате на выходе регистра 55 адресов оказывается адрес нулевой ячейки очередного канала, в которой хранится управляюй ее слово данного канала. Если это адрес (N+1)-ro канала, т.е. был обработан N-й канал (последний) фильтра, то в команде 9 осуществляется сброс триггера 25 блока 13 импульсом с выхода 25 дешифратора 34, в результате чего обнуляется счетчик 27 адресов, и обработка прекращается до прихода очередного импуль- ,са запуска. Для анализа условия, последний ли канал бьш обработан, число с выхода 2 блока 18 формирования адресов подается на пятый вход бло - ка 13, В команде 10, если триггер 12 фильтрации находится в нулевом состоянии, с целью перехода в начало программы для обработки очередного канала осзпцествляется сброс счетчика 27 адресов за счет подачи на второй вход элемента И 26 импульса с вькода 26 дешифратора 34 и сброс триггера 33 и шyльcoв с выхода 24 дешифратора 34 блока I 13.

5

0

5

0

5

0

5

0

5

Если триггер 12 фильтрации находится в единичном состоянии, начинается собственно фильтрация входного сигнала по обрабатываемому каналу. Для этого в команде 11 сбрасывается накапливающий сумматор 42 в арифметическом блоке 14 импульсом с выхода 4 блока 13 и производится модификация содержимого счетчика 17 адресов за счет поступления на его счетный вход управляющего импульса с выхода 22 блока 13. В результате адрес А1 соответствует адресу первой ячейки канала, в которой находится значение коэффициента g,. Начинается формирование сигнала на выходе первого звена у (п). Выполняется одновременно (в одной команде 12) считывание значений коэффициента g, и входногб сигнала х ,(п-2), задер- жанного на два периода, из блока 4 памяти по адресу А1 и блока 16 памяти по адресу А2 соответственно. Адрес А2 формируется в блоке 19 формирования адресов аналогично адресу А1, но входной информацией является ИА, поступающий с выхода блока 22 модификации адресов. Содержимое ячеек блока 16 памяти в трех смежных циклах работы фильтра для первого и второго элементарных звеньев канала приведено в табл.4. Для тех ячеек, в которых информация меняется в течение цикла, показано их содержимое в начале и конце цикла. Здесь под смежными циклами понимаются ближайшие по времени циклы, в.которых по данному каналу выполняется фильтрация. Значения g , и х т(п-2) по управляющему импульсу с третьего выхода блока 13. записываются в регистры 39 и 40 арифметического блока 14 соответственно. На умножителе 41 содержимое регистров 39 и 40 перемножается, образуя величину g,x,(n-2) на его выходе, а значит и на информационном входе накапливающего сумматора 42, Затем в ко- ;манде 13 производится запись входного сигнала х (п) в первую ячейку обрабатываемого канала блока 16 памяти, т.е. в ту ячейку, где ранее находилось значение х(п-2) (табл.4, 1ЩКЛ ). Для этого на многоразрядный управляюш 1й вход многоканального аналого-цифрового преобразователя 21 с выхода 24 блока 13 поступают управляющие сигналы,обеспечиваюище преобразование соответствующего об13

рабатываемому каналу входного сигнала, которьш в команде записи входного сигнала при наличии логического нуля на управляющем входе мультиплексора 20, поступающего с выхода 10 блока 13, проходит с выхода многоканального аналого-цифрового преобразователя 21 через мультиплексор 20 на,информационный вход блока 16 памяти. На второй управляющий вход блока 16 памяти с выхода 9 блока 13 подается сигнал логического.нуля, обеспечивающий режим записи,после чего по импульсу, поступающему на первый управляющий вход блока 16 памяти с выхода 8 блока 13 происходит занесение информации в ячейку с адресом А2, сформированным к этому времени на адресном входе блока 16 памяти. В команде 14 выходное значение накапливающего сумматора 42 суммируется с его входным значением на сумматоре 43 и по управляющему импульсу, поступающему на пятьм вход арифметического блока 14, с пятого выхода блока 13 полученньй результат записывается в регистр 44. Так как регистр 44 бьш сброщен при обнулении накапливающего сумматора 42 в команде программы (табл.3), на его выходе образуется произведение g,x(n-2). К содержимому счетчика 17 адресов прибавляется единица по управляющему импульсу, поступающему с двадцать второго выхода блока 13. Операндами для второго умножения являются двоичный код коэффициента g,, и значение входного сигнала хДп-1), поступающие в команде 15 из вторых ячеек блоков 4 и 16 памяти в арифметический блок 14, где перемножаются, а полученное произведение g,) складывается с предыдущим числом, хранящимся в накапливающем сумматоре 42. В команде 16 в регистре 44 образуется величина g,x,(n-2) + g „x-,(n-1). Содержимое адресного счетчика 17 увеличивается на единицу. На арифметический

блок 14 в команде 17 поступает очередная пара сомножителей: (n) Полученное произведение go,x,(n) складьшается с ранее накопленной суммой, в результате чего на выходе накапливающего сумматора 42 в команде 18 оказывается значение g,x.,(n - -2) + g ,х (п-1) + g о,х ,(п) . Содержимое адресного счетчика 17 увели

. 1347514

чивается на единицу. На информационные входы арифметического блока 14 ; в команде 19 поступают двоичный код коэффициента -Ь,(, и значение выходного сигнала элементарного звена, задержанное на два .периода дискретизации у (п-2) (ячейка 3, цикл п Р, табл.4). Полученное произведе Q ние -Б, уДп-2) прибавляется в команде 20 к накопленной ранее сумме: g,x,(n-2) + g, х,(п-1) + g,,x,(n) - - bi,y,(n-2). Снова производится модификация адреса в адресном счетчиJ5 .ке 17..На информационные входы арифт метического блока 14 подаются в команде 21 код коэффициента -Ь,, и значение выходного сигнала, задержанное на один период дискретизации,

20 у ,(п-1) (ячейка 4, цикл п Р,табл.4). По окончании умножения полученное произведение -Ь,,у,(п-1) суммируется с ранее накопленным числом. В результате на выходе накапливающего

25 сумматора 42 арифметического блока 14 в команде 22 оказывается выходной сигнал первого элементарного звена: у(п) g,x,(n-2) + g „х(п-1) + + g5,x ,(n) - b ,y ,(n-2) - b,, у , (n 30 - 1). Содержимое адресного счетчика 17 увеличивается на единицу. Значение у(п). в два раза меньше истинного у т(п). Так как информация представлена в двоичной системе, умно; жениенадва равносильно сдвигу на один разряд влево (в сторону старших разрядов). Поэтому умножение у(п) на два в команде 23 выполняется при записи в регистр 45, так

JQ как его разряды смещены на один разряд влево относительно разрядов регистра 44 арифметического блока 14. После записи в регистр 45, где образуется у (п) производится сброс накапливающего сумматора 42, который, оказывается подготовленным к накоплению выходного сигнала следующего элементарного звена. К этому моменту в адресном счетчике 16 уже на--. ходится адрес ячейки в канале,где располагается очередной коэффициент. Поэтому формирование в п-м цикле работы устройства выходного сигнала pfiK второго и всех последующих элементарных звеньев происходит аналогичным образом. Единственным отличием является то, что значение входного сигнала для этих звеньев поступает на информационный вход блока

35

45

55

6 памяти с выхода арифметического лока 14 через второй вход мультилексора 20, а не с входов фильта, т.е. для второго и всех послеующих звеньев входным сигналом явяется выходной сигнал предыдущего звена х(п) у .,(п). При зтом на пpaвляюш й вход мультиплексора 20 оступает сигнал логической единицы., азрешающий прохождение сигнала с торого входа мультиплексора 20 на его выход. После того, как в регистр 45 арифметического блока 14 поступает значение выходного сигнала по- „ следнего элементарног-о звена у .(п) канала (команда 35,табл.3) ,производится его перезапись в выходной регистр 15 по заправляющему импульсу с выхода 7 блока 13 (команда 36,табл.3),, Одновремен-но с этим через второй вход мультиплексора 20 значение у ;,(п) с выхода арифметического блока 14 заносится в блок. 16 памяти на место у(п-2). Далее производится модификация содержимого регистра 55 адресов в блоке 18 (19) формирования адресов с целью перехода к адресам следующего канала (команда 37,табл.3) . Если еще не все N каналов фильтра обработаны, осуществляется переход в начало программы (команда 38, гЪбл.З), для чего про.изводится сброс счетчика 27 адресов и триггера 33 щэи условии,, что в результате мо-7 дификации регистра 55 адресов получается адрес нулевой ячейки 1-го канала, причем I i N. В противном случае выполняется завершающая программу команда (команда 39, табл„3)э в которой осуществляется сброс КЗ- триггера 25 импульсом с выхода 25 дешифратора 34, в результате чего устанавливается в нуль счетчик 27 адресов, и прекращается обработка до прихода очередного ршпульса запуска. На этом цикл обработки заканчивается.

Вабота фильтра в следующем цикле (цикл m р + 1) вьшолняется по той же программе, однако ячейки блока 16 памяти, в которых хранятся значения задержанных на один и два периода дискретизации входных (выходных) сигналов для каналов, по которым выполняется фильтрация, поменялись MecTaMii по сравнению с лре- дьщущим , в котором выполнялась фильтрация (циклы m и р,табл.4).

Для получения нужного исполнительного адреса (ИА) на первый и второй, входы блока 22 модификации адресов поступает соответственно прямое и инверсное значение признака М с выходов триггера 5 модификации, на третий вход - базовый адрес (БА) с одиннадцатого адресного выхода бло- ка 13. Для получения требуемого ИА в блоке 22 модификации адресов производится преобразование БА по следующему правилу:

-ИА БА + 1, если М 1, а мпад- ший разряд БА равен нулю;

-ИА БА - 1, если М 1 и младший разряд БА равен единице;

- ИА БА, если М 0.

0

Признак М меняет свое значение на

противоположное в управляющем слове канала в цикле, в котором производится фильтрация по данному каналу. В остальных циклах значение М не мег няется. Если признак М равен единице, а младший разряд БА и, следовательно, вход элемента НЕ 46 равны нулю, выходы элементов И 47 и ИЛИ 48 равны единице. Сигнал с выхода элемента И 47 поступает на вход переноса младшего разряда сумматора 49, к первому входу которого подключен БА, а к второму входу в этом случае ока- зьшается подключенной шина 51 логического нуля, т.е. код 00. ..О, что 5 достигается подачей сигнала логической единицы с выхода элемента ИЛИ 48 на управляющий вхрд мультиплексора 50. В итоге на .выходе сумматора 49 формируется ИА БА + 1. Если М 1

0 и мпадщий разряд БА равен единице, выходы элементов НЕ 46, FI 47 и ИЛИ 48 равны нулю, В этом случае на входе переноса младшего разряда сумматора 49 действует нуль, а к его вто5 рону входу подключается шина 52 логической единицы, т.е. код 11...1, в то время, как на первом входе сумматора 49 по прежнему БА. Суммирование БА с кодом 11 ... 1 равносильно вычи-

0 танию из БА единицы, так как -1 в дополнительном коде представляется единицами во всех разрядах. В результате на выходе блока 22 модификации адресов имеется ИА БА - 1. В том

5 случае, когда М О, .независимо от того, чему равен младший разряд БА, на выходе элемента И 47 устанавливается нуль, а выход элемента ИЛИ 48 равен единице. При этом на входе

17

переноса младшего разряда сумматора 49 действует нуль, а к второму входу подключается шина 51 логического нуля. В результате на выходе бло - ка 22 модификации адресов присутствует ИА ВА, Указанная последовательность работы обеспечивает необходимьй порядок смены адресов смежных ячеек блока 16 памяти в кахсдом 15икле работы канала, в котором по данному каналу вьтолняется фильтрагщя.

Формула изобретения

Программно-управляемый цифровой фильтр, содержащий первый и второй блоки памяти, арифметический блок, блок модификации адресов, первый мультиплексор, .выходной регистр и блок, синхронизации, первый и второй выходы которого подключены к входам управления соответственно записью и считьюанием первого блока памяти, выход которого подключен к входу коэффициента арифметического блока, выход которого подключен к первому информационному входу первого мультиплексора и информационному входу выходного регистра, выход которого является информационным выходом фильтра, входом запуска которого является первый вход блока синхронизации, третий, четвертый, пятый и шестой выходы которого подключены соответственно к входу синхронизации приема, входу синхронизации вычислений, установочному входу и входу синхронизации вьздачи арифметического блока, вход операнда которого подключен к выходу второго блока памяти, информационный вход которого подключен к выходу первого мультиплексора, вход записи выходного ре гистра подключен к седьмому выходу блока синхронизации, восьмой и девятый выходы которого подключены к ВХО

дам.управления соответственно записью и считыванием второго блока памяти, управляющий вход первого мультиплексора подключен к десятому выходу блока синхронизации, одиннадцатый выход которого подключен к адрес Hoisiy входу блока модификации адресов, первый, второй и третий входы кода режима блока синхронизации явля ются входами разрядов кода режима группы фильтра, отличающий- с я тем, что, с целью повышения бы-й

513475i8

стродействия, в него введены счетчик адреса, первый и второй блоки формирования адреса, второй, третий, четвертый и пятый мультиплексоры, первый и второй триггеры, первый и второй регистры, сз матор, дешифратор и аналого-цифровой преобразователь, выход которого подключен к второму

10 информационному входу первого мультиплексора, двенадцатый, тринадцатый, четырнадцатьш и пятнадцатый выходы блока синхронизащш подключены соот ветственно к управляющему входу вто-

t5 рого мультиплексора,, тактовому входу первого регистра, управляющим входам третьего и четвертого мультиплексо ров, выходы которых подключены соответственно к первому и второму ин-

20 Формационным входам сумматора, выход которого подключен к информационному входу второго регистра, выход которого подключен к входу дешифратора, пе- первому информационному входу третье25 го мультиплексора и первому информационному входу второго мультиплексора, выход которого подключен к информационному входу первого блока памяти, адресньй вход которого подключен

30 к первому выходу первого блока фор-- мирования адреса,.второй выход которого подключен к входу окончания обработки блока синхронизации, шестнадцатый выход которого подключен к тактовому входу первого триггера и тактовому входу второго триггера, выход которого подключен к управляющему входу пятого мультиплексора и четвертому входу кода режима блока синхронизации, .семнадцатый и восемнадцатый выходы которого подключены соответственно к входу обнуления и входу записи второго регистра, девятнадцатый, двадцатый и двадцать первый выходы блока синхронизации подключены соответственно к первому, второму и третьему тактовым входам первого и ато- рого блоков формирования адреса, двадцать второй и двадцать третий выходы блока синхронизации подключены соответственно к входу обнуления и счетному входу счетчика адреса, выход которого подключен к адресному входу первого блока формирования адреса, двадцать четвертый выход блока

35

40

45

50

- 55 синхронизации подключен к тактовому входу аналого-цифрового преобразователя, информационные входы группы которого являются информационными вхо-,

дами группы фильтра, вход переноса сумматора соединен с шиной логической единицы устройства, выход первого блока памяти подключен к информационному входу первого регистра, первый выход которого подключен к информационному входу первого триггера, прямой и инверсный вьпсоды которого подключены соответственно к первому, и второму информационным входам пятого мультиплексора и соответственно первому и второму тактовому входам блока модификации адреса, выход которого подключен к адресному входу Iвторого блока формирования адреса, выход которого подключен к адресно- |му входу второго блока памяти, вто- ;рой выход первого регистра подключен |к второму информахщонному входу тре- |тьего мультиплексора, объединен с выходом пятого мультиплексора и подключен к первому информационному входу второго мультиплексора, второй иформационный вход которого подключен к входам кода режима группы филь- iTpa, третий и четвертый выходы перво- |го регистра подключены соответствен- JHO к первому и второму информацион- рым входам четвертого мультиплексора, выход дешифратора подключен к информационному входу второго триггера гц)ичем блок формирования адреса содержит регистр, сумматор и мультиплексор, t цыход которого подключен первш гу входу сумматора, выход которого является первым выходом блока формирования адреса и подключен к информационному входу регистра, выход которого является вторым выходом бло

5

ка формирования адреса и подключен к второму входу сумматора,первый ин- формационньш вход мультиплексора является адресным входом блока формирования адреса, первым, вторым и третьим тактовыми входами которого являются соответственно управляющий вход мультиплексора, установочный вход и вход записи регистра, а второй информационный вход мультиплексора соединен с входом задания константы .блока формирования адреса, который является входом задания константы фильтра, при этом блок модификации адреса содержит сумматор, мультиплексор, элемент НЕ, элемент ИЛИ и элемент И, выход которого подключен к первому входу.сумматора 0 и первому входу элемента ШШ, выход которого подключен к управляющему входу мультиплексора, выход которого подключен к второму входу сумматора, выход крторого является выходом блока модификации адреса, адресным входом которого является третий вход сумматора, первым и вторым тактовыми входами блока модификации адреса являются первый вход элемента И и второй вход элемента ИЛИ, второй вход элемента И подключен к выходу элемента НЕ, вход которого подключен к входу младшего разряда адресного входа блока модификации адреса, первый и второй информационные входы мультиплексора соединены соответственно с шиной логической единицы и логического нуля устройства.

5

0

35

40

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Программно-управляемый цифровой фильтр | 1985 |

|

SU1338006A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| Микропрограммный процессор | 1984 |

|

SU1211746A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

| МУЛЬТИКОНТРОЛЛЕР РАСПРЕДЕЛЯЕМОЙ ПАМЯТИ | 2014 |

|

RU2550555C1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1254506A1 |

| Процессор для обработки массивов данных | 1985 |

|

SU1293737A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДВУМЕРНОЙ СВЕРТКИ | 1992 |

|

RU2042209C1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых многоканальных системах обработки случайных процессов. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что в состав фильтра входят вход 1 заданния режима, мультиплексоры 2,3, блок 4 памяти, триггер 5, регистр 6, мультиплексоры 7,8, сумматор 9, регистр 10, дешифратор 11, триггер 12, блок 13 синхронизации, арифметический блок 14, выходной регистр 15, блок 16 памяти, счетчик 17 адреса, блоки 18,19 формирования адреса, мультиплексор 20, аналого-цифровой преобразователь 21, блок 22 модификации адресов, вход 23 задания логической единицы. 10 ил., 4 табл.

17

0000 00000 Обнуление СчА 17 и РгА 55 в БФА 18

000000000 П1 А1 7 Запись управляющего слова

000100001 СчА: СчА+1 первого канала в БП 4,

увеличение содержимого СчА 17 на 1

0001 00001 П1 А1 Запись коэффициента g i, в 0010 00010 СчА: СчА+1 БП А по первому каналу, увеличение содержимого СчА 17 на 1

001000010 П1 Запись коэффициента g,, в

001100011 ВП 4 по первому Kananyj увеличение содержимого СчА 17. на 1

0011 00011 П1 «CAI Запись коэффициента go, в 0100 00100 СчАг СчА+Т БП 4 по первому каналу,увеличение содержимого СчА 17 на 1

10

11

12

13

12

14

X0000 1 01011

000101100

0001 0010

01100 01101

0010 0011

01101

ото

X0011

0100

02110 01111

0100 0101

01111- 10000

0101 0110

1000 1001

оно

0111

10001 10010

0111 1000

10010 10011

1 А1 чА: СчА+1

1 А1 чА:-СчА-|-1

1 А1 ) чА:-СчА+1

1 :AI

чА: СчА+1

1 А1 чА: СчА+1

1 ;AI 7

чА: СчА+1

1 А1 чА: СчА+1

. в увв

личение содержимого СчА 17 на 1

Запись коэффициента -Ь „ в БП 4 по первому каналу, уве личение содержимого СчА 17 на 1

Запись коэффициента g ц в БП 4 по первому каналу, уве личение содержимого СчА 17 на 1

Запись коэффициента g ,j в БП 4 по первому каналу , увеличение содержимого СчА 17 на 1 . Запись коэффициента g щ в БП 4 по первому каналу, увеличение содержимого СчА 17 на 1

Запись коэффициента в БП 4 по первому каналу, увеличение содержимого СчА 17 на 1

Запись коэффициента -Ь „ в БП 4 по первому каналу, увеличение содержимого СчА 17 на 1

Модификация РгА 55 а БФА 18 и обнуление СчА 17 с целью перехода к адресам второго канала

Запись управляющего слова второго канала в БП 4, увеличение содержимого СчА 17 на 1

Запись коэффициента g , в ВП 4 по второму каналу, увеличение содержимого СчА 17 на 1

Запись коэффициента g , БП 4 по второму каналу, личение содержимого СчА 17 на 1

Запись коэффициента g,, в БП 4 по втором каналу, увеличение содержимого СчА на 1

Запись коэффициента -Ь,, БП 4 по второму каналу, увеличение содержимого СчА- 17 на 1

Запись коэффициента -Ь„ в БП 4 по второму каналу,увеличение содержимого СчА 17 на 1

Запись коэффициента g в БЦ 4 по второму каналу, увеличение содержимого СчА на 1

Запись коэффИ1щента g БП 4 по втором каналу, личение содержимого СчА на 1

в уве17

в

17

уве- 17

23

8

1001 101U

10100 10101

8

1010 1011

10101

10110

24

1513475

л

Продолжение табл.1

Содержание и комментарии

Запись коэффициента gg в БП 4 по второму каналу, увеличение содержимого СчА 17 на 1

Запись коэффициента в ВП 4 по второму каналу, увеличение содержимого СчА 17 на 1

Запись коэффициента -Ь ,г в БП 4 по второму каналу, увеличение содержимого СчА 17 на 1

22

000

3 10

5

1

10

t 10

010 010

010

on

oil

010 010

010 010

010

oil on

on on

on

010 010

010 on 010 on

one

Olio 0110

on 1

0111

1000 1000

Таблица 3

r:-0

r 45 :- CM M:-O

гК:П1 M- гВ:П2 A2

2 A2 :- Pr 5

M: См+РгКх+РгВ чА:-СчА 1

гк:-п :AI

гВ:-П2 A2

; Мм+РгКхРгВ чА: СчА+1 гК:-П1 А1) гВ:-П2 А2

случае, если Тг 33 I Чтение управляицето слова из БП 4, запись в Рг 6

Реалиэацыя на См 9 разности (), запись в Рг 10

Запись в ТГ 5 признака кодификации Н и в ТГ 12 признака фильтрации Ф Обнуление Рг 10

Запись в Рг 10 сдвига S,увеличенного иа 1, если Тг 12 О Запись нового управляющего слова в БП 4 на место прежнего Модификация РгА 55 в 5ФА 18 (БФА 19) в том случае, если Тг 12 О, т.е. осуществляется переход к адресам следующего канала

Обнуление Тг 25 в БУ 13, если обработаны все N каналов, вызывающее прекращение обработки до очередного запуска

Обнуление Тг 33 и СЧа 27 в БУ 13, если Тг 12 О, с цепью перехода в начало программы дпя обработки следующего канала Модификация СчА 17, обнуление СмНк 42 в БАр 14 Чтение g , из Бп 4, х ,(п-2) из БП 16 запись в РгК 39 н РгВ 40 Запись входного сигнала х,(п) в БП 16 на место х ,(п-2) Накопление в СмНк 42 g,,x,(n-2), модификация СчА 17 Чтение g,, из БП 4, х,(п-1) из БП 16, запись в РгК 39 н РгВ 40 Накопление в СмНк 42 yj,x ,{п-2) + + g,,x,(n-O, модификация СчА 17 Чтение g,, из БП 4, х ,(п) из БП 16, запись в РгК и РгВ 40 Накопление в СмНк 42 gj,(n-2) + g,, х,(п-) + goi ,(п) модификация СчА 17

Чтение -Ь,, из БП 4, у,(п-2) из БП 16, запись в РгК 39 и РгВ 40 Накопление в СнНк 42 g ,,х ,(п-2) + + g,,x,(n-1) + ge,x,n) - Ь5,у,(п-2) модификация СчА 17 Чтение -Ь „ из БП 4, у,(п-1) из БП 16, запись в РгК 39 н РгВ 40 Накопление в СмНк 42 у(п) - g,,x,(n-2)+ g „X ,(n-l) +

, + S,,x,M -Ь,,у/n-2) Ь„ y,(n-l)модификация СчА 17

Запись у(п) в Рг 45 со сдвигом,

обнуление СмНк 42

Чтение g ,, из Бп ,.х(п-2)

-у,Сп-2) из БП 16, запись в РгК 39 и РгВ 40

Запись у i(n) в БП 16 на место У ,(п-2)

Накопление в СмНк 42 gjjX(n-2) кодификация СчА 17

Чтение g, из Бп 4, Xj(n-l)

у,(п-1) из БП 16, запись в РгК 39 и РгВ 40

Накопление в СмНк 42 §,зХ(п-2) +

g цХ, (п-1) модификация СчА 17 Чтение g из БП 4, х ,(п) у,,(п) из БП 16, запись в РгК 39 и РгВ 40

31

1513475

32

Продолжение табл.3

Г

56o

53

PU8.//

5V

f0

te.5

И

команды , Базовый адрес

Ре/е.Т

М Коэахртшент К Сдвиг S сг «iLz: j g.

|з I le .

1

Фи.б

Фиг. 8

57 58

59 60 61 62

ад

6

ьЛгй.

Р П Р П

71 з|5А |фиШ-зИ| |г|Ф|Иг|з|5|| та

-

1грМ5М7|8|№

Фг/г.

д

I

iW

1111- д

Фб/г. 10

| Программно-управляемый цифровой фильтр | 1979 |

|

SU877787A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Программно-управляемый цифровой фильтр | 1985 |

|

SU1338006A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-07—Публикация

1987-07-06—Подача