Изобретение относится к автоматике и вычислительной технике и может быть использовано для допускового контроля радиоэлектронньж устройств.

Цель изобретения - повышение точности устройства

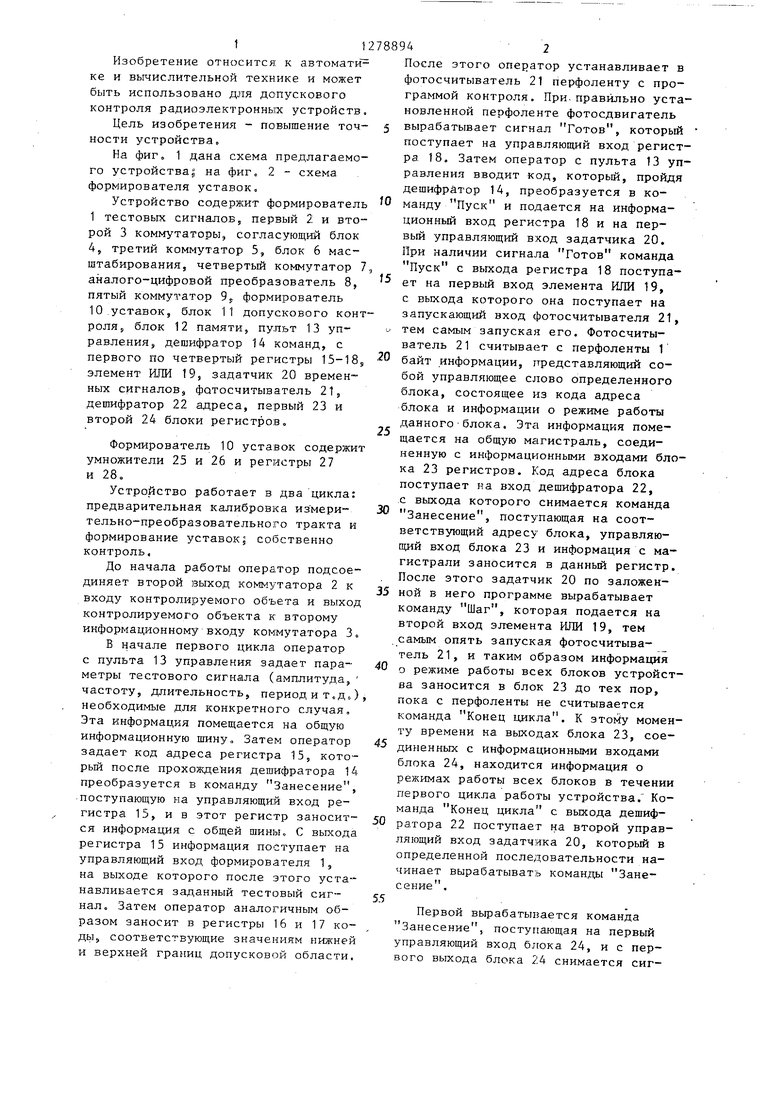

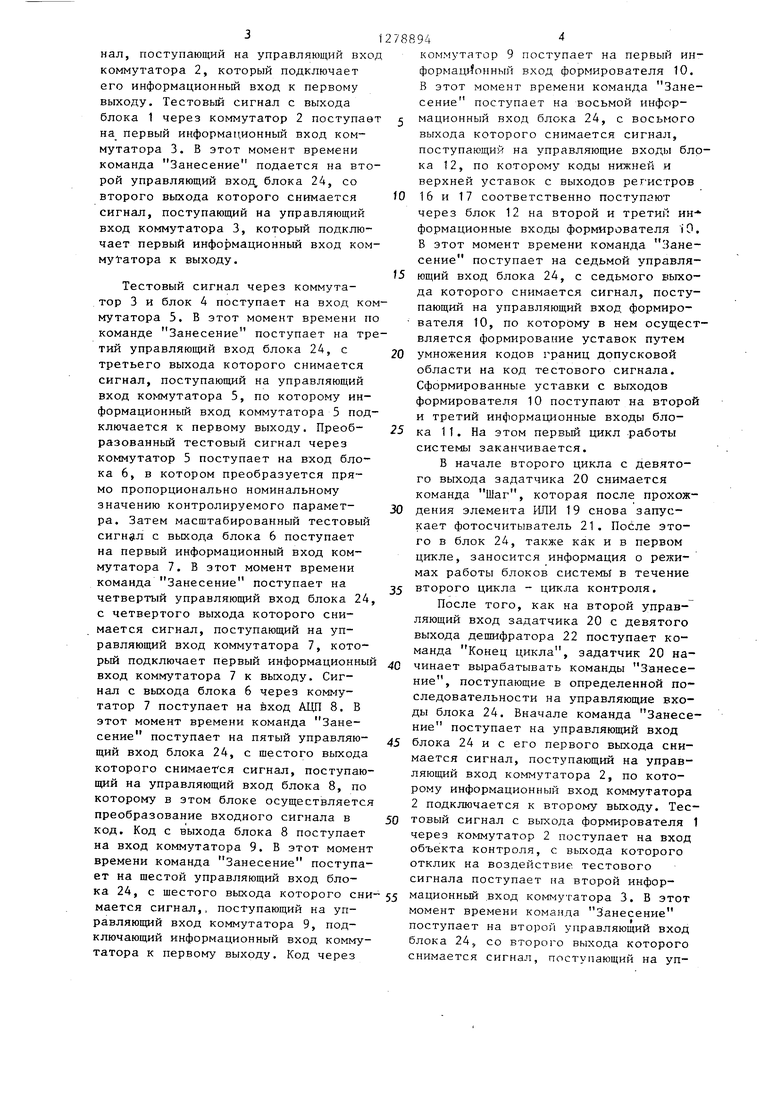

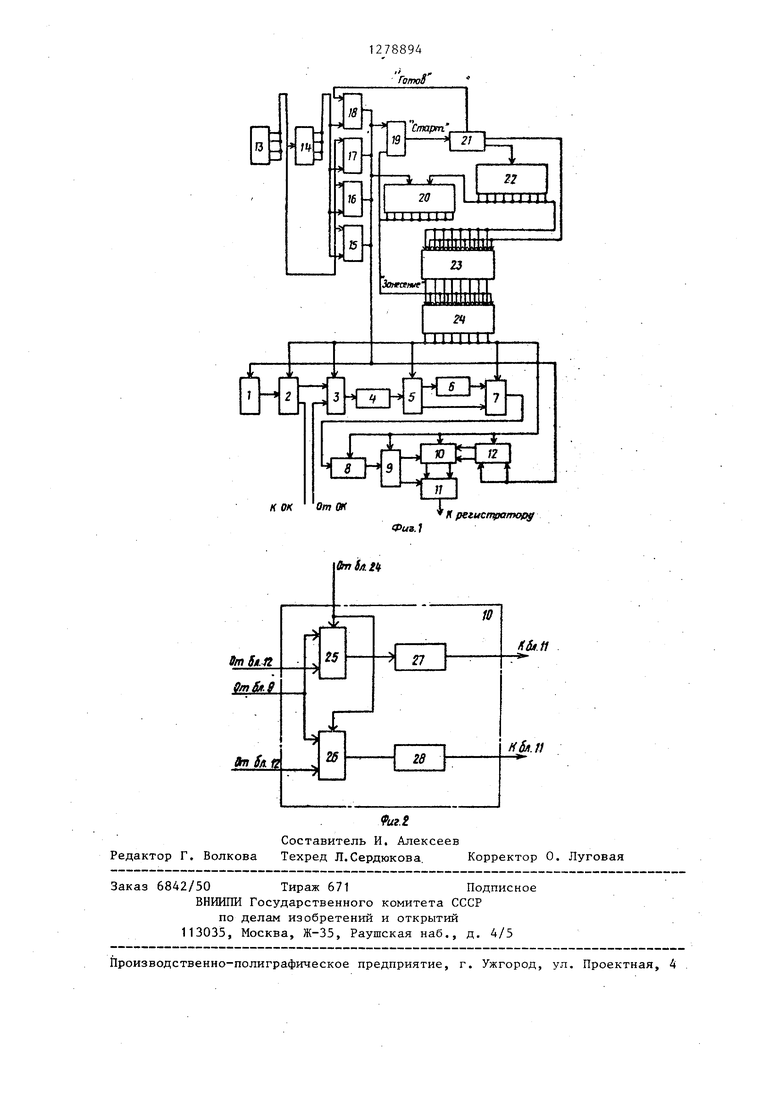

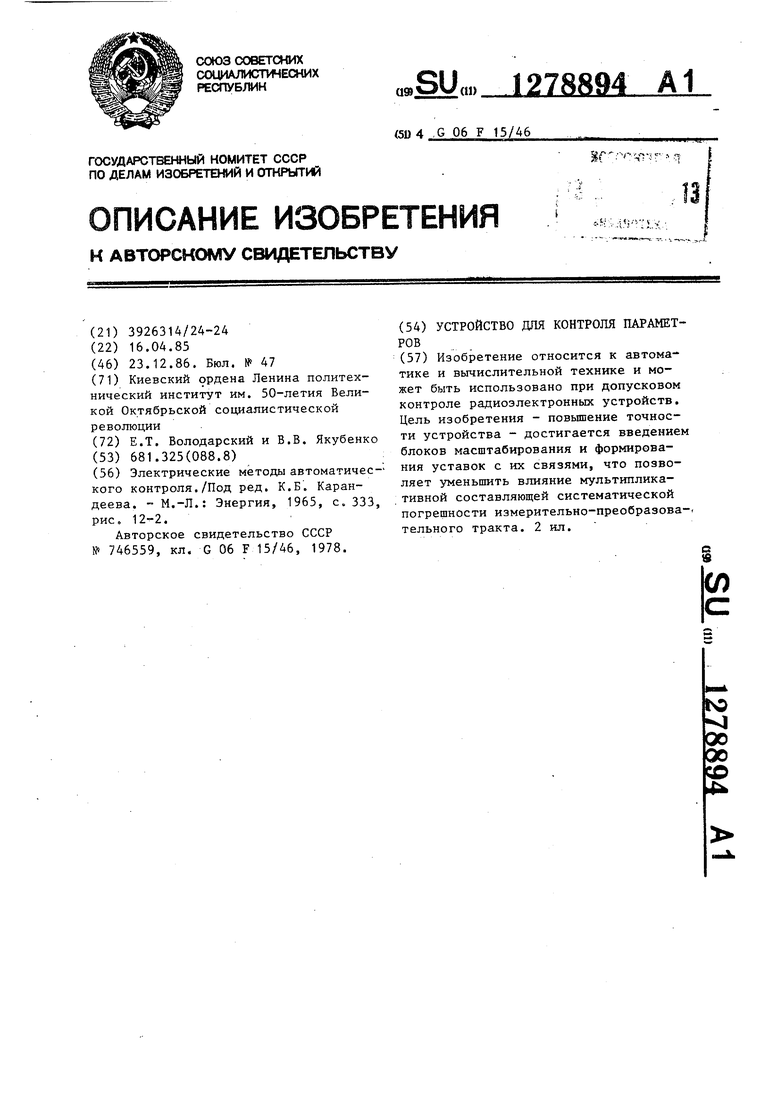

На фиг, 1 дана схема предлагаемого устройства| на фиг. 2 - схема формирователя уставок.

Устройство содержит формирователь 1 тестовых сигналов, первый 2 и второй 3 коммутаторы, согласующий блок 45 третий коммутатор 5, блок 6 масштабирования, четвертый коммутатор 7 аналого-цифровой преобразователь 8, пятыми коммутатор 9, формирователь 10.уставок, блок 11 допускового контроля блок 12 памяти, пульт 13 управления, дешифратор 14 команд, с первого по четвертый регистры 15-18, элемент ИЛИ 19, задатчик 20 временных сигналов, фотосчитыватель 21, дешифратор 22 адреса, первый 23 и второй 24 блоки регистров

Формирователь 10 уставок содержит умножители 25 и 26 и регистры 27 и 28.

Устройство работает в два цикла: предварительная калибровка измерительно-преобразовательного тракта и формирование уставок; собственно контроль.

До начала работы оператор подсоединяет второй выход коммутатора 2 к входу контролируемого объета и выход контролируемого объекта к второму информационному входу коммутатора 3

В начале первого цикла оператор с пульта 13 управления задает параметры тестового сигнала (амплитуда, частоту, длительность, период ит.д„) необходимые для конкретного случая, Эта информация помещается на общую информационную шину. Затем оператор задает код адреса регистра 15, который после прохождения дешифратора 14 преобразуется в команду Занесение, поступающую на управляющий вход регистра 15, ив этот регистр заносится информация с общей шины, С выхода регистра 15 информация поступает на управляющий вход формирователя 1, на выходе которого после этого устанавливается заданный тестовый сигнал. Затем оператор аналогичным образом заносит в регистры 16 и 17 коды, соответствующие значениям нижней и верхней границ допусковой области.

5

0

5

После этого оператор устанавливает в фотосчитыватель 21 перфоленту с программой контроля. При.правильно установленной перфоленте фотосдвигатель вырабатывает сигнал Готов, который поступает на управляющий вход регистра 18. Затем оператор с пульта 13 управления вводит код, которьй, пройдя дешифратор 14, преобразуется в команду Пуск и подается на информационный вход регистра 18 и на первый управляющий вход задатчика 20. При наличии сигнала Готов команда Пуск с выхода регистра 18 поступает на первый вход элемента ИЛИ 19, с выхода которого она поступает на запускающий вход фотосчитывателя 21, тем самым запуская его. Фотосчитыватель 21 считывает с перфоленты Г байт информации, ттредставляющий собой управляющее слово определенного блока, состоящее из кода адреса блока и информации о режиме работы данногоблока. Эта информация помещается на общую Мс1гистраль, соединенную с информационными входами блока 23 регистров. Код адреса блока поступает на вход дешифратора 22, с выхода которого снимается команда Занесение, поступающая на соответствующий адресу блока, управляющий вход блока 23 и информация с магистрали заносится в данный регистр. После этого задатчик 20 по заложен- 5 ной в него программе вырабатывает команду Шаг, которая подается на второй вход элемента ИЛИ 19, тем самым опять запуская фотосчитыватель 21, и таким образом информация о режиме работы всех блоков устройства заносится в блок 23 до тех пор, пока с перфоленты не считывается команда Конец цикла, К этоЯу моменту времени на выходах блока 23, соединенных с информационными входами блока 24, находится информация о режимах работы всех блоков в течении первого цикла работы устройства. Команда Конец цикла с выхода дешифратора 22 поступает на второй управляющий вход задатчика 20, который в определенной последовательности начинает вырабатывать команды Занесение,

0

0

5

0

Первой вырабатывается команда Занесение, поступающая на первый управляющий вход блока 24, и с первого выхода блока 24 снимается сигнал, поступающий на управляюн;ий вход коммутатора 2, который подключает его информационный вход к первому выходу. Тестовый сигнал с выхода блока 1 через коммутатор 2 поступает на первый информационный вход коммутатора 3. В этот момент времени команда Занесение подается на второй управляющий вход, блока 24, со второго выхода которого снимается сигнал, поступающий на управляющий вход коммутатора 3, который подключает первый информационный вход коммутатора к выходу.

Тестовый сигнал через коммутатор 3 и блок 4 поступает на вход коммутатора 5, В этот момент времени по команде Занесение поступает на третий управляющий вход блока 24, с третьего выхода которого снимается сигнал, поступающий на управляющий вход коммутатора 5, по которому информационный вход коммутатора 5 подключается к первому выходу. Преобразованный тестовый сигнал через коммутатор 5 поступает на вход блока 6, в котором преобразуется прямо пропорционально номинальному значению контролируемого параметра. Затем масштабированный тестовый сигнал с вькода блока 6 поступает на первый информационный вход коммутатора 7. В этот момент времени команда Занесение поступает на четвертый управляющий вход блока 24, с четвертого выхода которого снимается сигнал, поступающий на управляющий вход коммутатора 7, кото-- рый подключает первый информационный вход коммутатора 7 к выходу. Сигнал с выхода блока 6 через коммутатор 7 поступает на йход АЦП 8. В этот момент времени команда Занесение поступает на пятый управляющий вход блока 24, с шестого выхода которого снимается сигнал, поступающий на управляющий вход блока 8, по которому в этом блоке осуществляется преобразование входного сигнала в код. Код с выхода блока 8 поступает на вход коммутатора 9. В этот момент времени команда Занесение поступает на шестой управляющий вход блока 24, с шестого выхода которого снимается сигнал,, поступающий на управляющий вход коммутатора 9, подключающий информационный вход коммутатора к первому выходу. Код через

78894

коммутатор 9 поступает на первый информационный вход формирователя 10. В этот момент времени команда Занесение поступает на восьмой инфор- мационный вход блока 24, с восьмого выхода которого снимается сигнал, поступающий на управляющие входы блока 12, по которому коды нижней и верхней уставок с выходов регистров

fO 16 и 17 соответственно поступают

через блок 12 на второй и третий ин формационные входы формирователя iO, В этот момент времени команда Занесение поступает на седьмой управляf5 ющий вход блока 24, с седьмого выхода которого снимается сигнал, поступающий на управляющий вход формиро- - вателя 10, по которому в нем осуществляется формирование уставок путем

20 умножения кодов границ допусковой области на код тестового сигнала. Сформированные уставки с выходов формирователя 10 поступают на второй и третий информационные входы бло25 ка 11. На этом первый цикл работы системы заканчивается.

В начале второго цикла с девятого выхода задатчика 20 снимается команда Шаг, которая после прохож30 дения элемента ИЛИ 19 снова запускает фотосчитыватель 21. После этого в блок 24, также как и в первом цикле, заносится информация о режимах работы блоков системьг в течение

35 второго цикла - цикла контроля.

После того, как на второй управляющий вход задатчика 20 с девятого выхода дешифратора 22 поступает команда Конец цикла, задатчик 20 на40 чинает вырабатывать команды Занесение, поступающие в определенной последовательности на управляющие входы блока 24. Вначале команда Занесение поступает на управляющий вход

45 блока 24 и с его первого выхода снимается сигнал, поступающий на управляющий вход коммутатора 2, по которому информационный вход коммутатора 2 подключается к второму выходу. Тес50 товый сигнал с выхода формирователя 1 через коммутатор 2 поступает на вход объекта контроля, с выхода которого отклик на воздействие тестового сигнала поступает на второй инфор- 55 мационный вход кoм yгaтopa 3. В этот момент времени команда Занесение поступает на второй управляющий вход блока 24, со второго выхода которого снимается сигнал, поступающий на упШ

«5

1 авляющий вход коммутатора 3, по которому второй информационный вход коммутатора подключается к выходу. Отклик на воздействие тестового сигнала через коммутатор 3 поступает на вход блока 4, с выхода которого поступает на информационный вход коммутатора 5. В этот момент времени команда Занесение поступает на третий управляющий вход блока 24, с третьего выхода которого снимается сигнал, поступающий на управляющий вход коммутатора 5, по которому информа- ционньй вход коммутатора соединяется со вторым выходом. Отклик через коммутатор 5 поступает на второй информационный вход коммутатора 7. В этот момент времени команда Занесение поступает на четвертый управляющий вход блока 24, с четвертого выхода которого снимается сигнал, поступающий на управляющий вход коммутатора 7, по которому второй информационный вход коммутатора подключается к выходу. Отклик через коммутатор 7 поступает на вход АЦП 8. В этот момент, времени команда Занесение поступает на пятый управляющий вход блока 24, с пятого выхода которого снимается сигнал, поступающий на управляющий вход блока 8, по которому в этом блоке осуществляется пре- образование отклика в код. Код с выхода блока 8 поступает на информационный вход коммутатора 9. В этот момент времени команда Занесение поступает на шестой управляющий вход блока 24, с шестого выхода которого снимается сигнал, поступающий на управляющий вход коммутатора 9, по которому информационный вход коммутатора подключается к второму выходу. Код отклика через коммутатор 9 поступает на первый информационный вход блока 11, где сравнивается со сформи- 45 рованными кодами уставок. На этом работа системы заканчивается.

20

25

30

35

40

Математически все представленное выше можно описать следующим образом.

С выхода блока 1 снимается тесто- ВЫ1| сигнал X

X Х + S. .

Xjj - номинальное значение тестового сигнала;

аддитивная погрешность, вносимая блоком 1.

So

Сигнал X чере-з коммутаторы 2 и 3 блок 4 согласования и коммутатор 5 поступает на вход блока 6, где преобразуется пропорционально номинальному значению контролируемого параметра

х (х+д)(1+у),

где а - номинальное значение контролируемого параметра; Л - аддитивная погрешность измерительно-преобразовательного тракта;

У - мультипликативная погрешность измерительно-преобразовательного тракта. Сигнал к через коммутатор 7 поступает на вход АЦП 8, где кодируется. Код тестового сигнала, прошедшего весь измерительно-преобразова- тельньй тракт, определяется как N

(x+a)(H-|j ).

С выхода блока 8 код N через коммутатор 9 поступает на вход блока 10, где происходит формирование уставок

45

30

N,,

и N.

в

5

5

0

где К., и

В

0

коды г оминальных значений нижней и верхней границ области допуска соответственно.

Сформированные коды уставок поступают на входь блока 11. Затем тестовый сигнал X через коммутатор 2 поступает на вход контролируемого объекта, с выхода которого снимается отклик на воздействие тестового сигнала у

,

где а - действительное значение контролируемого параметра. , Отклик у через коммутатор 3, блок 4 согласования, коммутаторы 5 и 7 поступает на вход AI1JI 8, где кодируется. Код отклика N с учетом погрешностей измерительно-преобразовательного тракта имеет следующий вид:

55

N(y+u)(1+y).

Код N с выхода АЦП 8 через коммутатор 9 поступает на вход блока 11,

где происходит его сравнение с кодами сформированных уставок N и Ng по правилу

NH-N.N.

Осуществив ряд простейших преобразований, получаем;

а„()(Ну)К„(у+Л)(И-р ) fO .(Hp-Kg.

Обозначив

ао Ки -

получаем

а.(х+й) а-(х+й) а.(х+л); и6 20

а„х(Н А )х (а ) ( Н );

ЛАА

,(Н)..а(Н М..

Из последнего вьфажения видно, чт применение предлагаемой системы позволяет исключить влияние на результат контроля мультипликативной составляющей систематической погрешнос- ти измерительно-преобразовательного тракта. Кроме того, так как величина аддитивной составляющей погрешности измерительно-преобразовательного тракта много меньше величины тесто- вого сигнала, то их частное будет пренебрежимо мало. Обозначив б

- , получаем

Л

а(1+б)(Нб).

При вьтолнении условия Л «х,б. последнее выражение принимает вид

а, .

Таким образом, изобретение позволяет контролировать аналоговые параметры радиоэлектронных устройств С высокой точностью, так как на результат контроля не будут влиять такие погрешности: погрешность формирования тестового сигнала; аддитивная составляющая систематической погрешности измерительно-преобразо- вательного тракта; мультипликативная составляющая систематической погрешности измерительно-преобразовательного тракта.

O

5

0

5

0

0

5

0

Так как при контррле аналоговых параметров радиоэлектронных устройств основной по1 решностью, влияющей на результаты контроля, является частотная погрешность, представляющая собой мультипликативную составляющую систематической погрешности, то в устройстве могут быть применены блоки 1, 4 и 8 более низкой точности, если систематические составляющие погрешностей двух последних (А и 8) являются преобладающими, а случайные составляющие имеют пренебрежимо малые значения.

Применение предлагаемого устройства позволяет повысить точность, а следовательно, и достоверность контроля таких параметров радиоэлектронных устройств, как, например: коэффициент неравномерности АЧХ; коэф-- фициент нелинейности АХ; коэффициент амплитуды; коэффициент Ферми; коэффициент пульсаций; коэффициент гармонии и другие.

Использование предлагаемого устройства позволяет полностью автоматизировать процесс контроля и повысить производительность труда, так как нет необходимости перепроверять контролируемые параметры, признанные негодными из-за влияния перечисленных выше погрешностей.

Формула изобретения

Устройство для контроля параметров, содержащее формирователь тестовых сигналов, выход которого соединен с информационным входом первого коммутатора, один выход которого является выходом устройства, а другой выход подключен к первому информационному входу второго коммутатора, второй информационный вход которого является входом устройства, а вьпгод подсоединен через согласующий блок к информационному входу третьего коммутатора, первый выход которого подключен к первому информационному входу четвертого коммутатора, выходом подключенного к информационному входу аналого-цифт рового преобразователя, выход которого подключен к информационному входу пятого коммутатора, выходы первой группы которого соединеЛ с одними входами блока допускового контроля, выход которого является информахдионным выходом устройства, входы дешифратора команд и информационные входы регистров с первого по третий являются установочными входами устройства, управляющие входы регист- ров с первого по третий подключены соответственно к первому, второму и третьему выходам дешифратора команд, выход первого регистра соединен с управляющим входом формирова- теля тестовых сигналов, выходы второго и третьего регистров подключены к информационным входам блока памяти, четвертый выход дешифратора команд соединен с информационным вхо- дом четвертого регистра, выходом подключенного к первому входу элемента ИЛИ и первому управляющему входу задатчика временных сигналов, выход элемента ИЛИ соединен с входом фотосчитывателя, управляющий выход которого подсо единен -с управляющему входу четвертого регистра, адресный выход - к входу дешифратора адреса, с первого по восьмой выходы ко- торого подсоединены к управляющим входам первого блока регистров, информационные входы которого соединены с информационными выходами фотосчитывателя, девятый выход дешифра- тора адреса соединен с вторым управляющим входом задатчика временных сигналов, с первого по восьмой выходы которого подключены к управляющим входам второго блока регистров,

информационные входы которого соединены с выходами первого блока регистров, выходы с первого fio шестой и восьмой выход второго блока регистров соединены с управляющими входами коммутаторов с первого по четвертый, с управляющим входом аналого-цифрового преобразователя, с управляющим входом пятого KOMNryTa- тора и с управляющим входом блока памяти соответственно, девятый выход таймера соединен с вторым входом элемента ИЛИ, отличающееся тем, что, с целью повышения точности, в него введены блок масштабирования и формирователь уставок, содержащий первый и второй умножители, пятый и шестой регистры информационные входы которых соединены соответственно с выходами первого и второго умножителей, выходы пятого и шестого регистров подключены к другим входам блока допуско- вого контроля, управляющие входы умножителей соединены с седьмым выходом второго блока регистров, первые информационные входы умножителей соединены с выходом пятого коммутатора, а вторые информационные входы первого и второго умножителей подсоединены к соответствующим выходам блока памяти, второй выход комутатора через блок масштабирования подключен к второму информационному входу четвертого коммутатора.

Готов

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля | 1984 |

|

SU1198542A1 |

| Устройство автоматического контроля параметров | 1983 |

|

SU1201850A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Устройство для автоматизированного контроля параметров | 1988 |

|

SU1647520A1 |

| Устройство для сопряжения управляющей вычислительной машины с периферийными устройствами | 1983 |

|

SU1201841A1 |

| Устройство для программного управления технологическим оборудованием | 1986 |

|

SU1372277A1 |

| Устройство для диагностики неисправностей технических объектов | 1987 |

|

SU1515175A2 |

| Устройство для программного управления технологическим оборудованием | 1987 |

|

SU1423982A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Устройство для программного управления намоточным оборудованием | 1984 |

|

SU1273879A2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при допусковом контроле радиоэлектронных устройств. Цель изобретения - повышение точности устройства - достигается введением блоков масштабирования и формирования уставок с их связями, что позволяет уменьшить влияние мультипликативной составляющей систематической погрешности измерительно-преобразова-- тельного тракта. 2 ил.

Ю

Старт.

К OK От OK

Фиг.1

К petucn moffy

SrпSлif

flSt.tl

Нбл.Г)

fut.i

Составитель И. Алексеев Редактор Г. Волкова Техред Л.Сердюкова. Корректор О. Луговая

Заказ 6842/50 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Электрические методы автоматического контроля./Под ред | |||

| К.Б | |||

| Каран- деева | |||

| - М.-Л.: Энергия, 1965, с | |||

| Телефонная трансляция с катодными лампами | 1922 |

|

SU333A1 |

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Дискретная система автоматического контроля и измерения параметров | 1978 |

|

SU746559A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-23—Публикация

1985-04-16—Подача