Изобретение относится к вычислительной технике, предназначено для статического анализа случайных процессов путем вычисления взаимомодульной функции и может быть использовано в качестве приемника шумоподобных сигналов с модулированным периодом в условиях воздействия сосредоточенных периодических помех.

Цель изобретения - повьппение помехоустойчивости .

Сущность изобретения заключается в том, что за счет дополнительного введения генератора эталонного сигна ла в устройстве вычисляется двумерная взаимомодулярная функция G между входным шумоподобным сигналом и эталонным, период которого прини- мает L различных значений (,2,..

...,L; ,2,...,n - временной сдвиг, n - число символов шумоподобного сигнала). На выходе вычислителя взаимомодулярной функции соотношение сигнал/шум пропорционально входному соотношению сигнал/шум и объему выборки, что позволяет существенно повысить помехоустойчивость приема шумоподобных сигналов с модулированным периодом.

В основу алгоритма работы устрой- ства положена развертка периода эталонного сигнала, который сравнивается в каждом канале устройства с вход.

рые запускают аналого-цифровой прео разователь I, тактирующий сдвиги в генераторе 4 эталонного сигнала и в регистрах 2. На первом выходе с син ронизатора 3 вырабатывается последо вательность высокочастотных импульсов , тактирующих работу элементов 30 ИСКЛЮЧАЮЩЕЕ ИЛИ 9. При запуске аналого-цифрового преобразователя 1 на его выходе формируется временной ин тервал, длительность которого пропо циональна значений входного напряже

ным щумоподобным сигналом, фаза кото-35 ния. За счет этого в каждом такте

40

рого неизвестна. В процессе работы устройства в каждом цикле корреляционной свертки эталонного сигнала заданного периода с входным сигналом происходит запоминание минимального значения модульной функции, сформированного в одном из каналов. После этого происходит изменение периода эталонного сигнала на некоторую величину. После выполнения всех циклов анализа на выходных шинах устройства выдается код номера цикла, в котором модульная функция принимает минимальное значение, что соответствует периоду входного сигнала, выделенному на фоне помех.

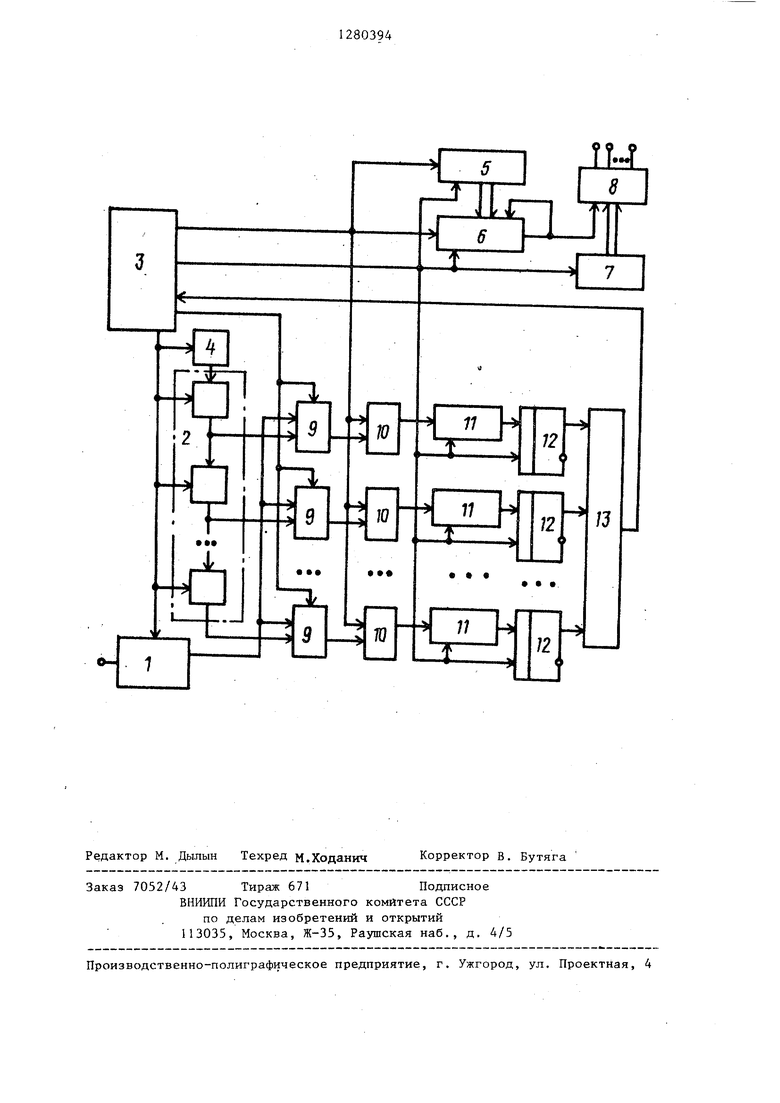

На чертеже представлена структурная схема устройства.

Устройство содержит аналого-цифровой преобразователь 1, регистры 2, 55 синхронизатор 3, генератор 4 эталонного сигнала, первый счетчик 5, делитель 6, второй счетчик 7, регистр ,8, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 9, элеменизмерения на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9 J-ro канала формирует ся пачка импульсов, количество которых пропорционально абсолютной ра ности значений входного сигнала х- и j-ro сдвига эталонного сигнала y.j . Импульсы с выхода элемента ИС КЛЮЧАЮЩЕЕ ИЛИ 9 калсдого канала чере элемент ИЛИ 10 своего канала поступ 45 ют на тактовый вход счетчика 11 . Та КИМ образом, после N тактов в каждом J-M счетчике 11 будет накоплен код значения модульной функции

..1

В начале (N+1)-го такта измерени k-ro цикла на четвертом выходе синх ронизатора 3 вырабатывается последо вательность высокочастотньпс импульсов, поступающих на тактовые входы счетчика 5, делителя 6 и через элементы ИЛИ 10 на тактовые входы счет чиков 11. В момент переполнения сче

50

to

20

ты ИЛИ 10, счетчик 11, триггер 12, элемент И 13.

Устройство работает следующим образом.

Вычисление точек двумерной взаимо:; - модульной функции и определение ее минимального значения осуществляется на протяжении L циклов, каждьй из которых состоит из (N+)-го тактов. В начале каждого цикла измерения на третьем выходе синхронизатора 3 формируется короткий импульс, по фронту нарастания которого осуществляется сброс счетчиков 11 и триггеров 12 всех каналов, а также счетчика 5 и делителя 6 в нулевое состояние.

По фронту спада импульса происходит увеличение на единицу кода, хранящегося в счетчике 7 . Одновременно с этим на втором выходе синхронизатора 3 формируются короткие импульсы,

следующие с частотой f, кото

рые запускают аналого-цифровой преобразователь I, тактирующий сдвиги в генераторе 4 эталонного сигнала и в регистрах 2. На первом выходе с синхронизатора 3 вырабатывается последовательность высокочастотных импульсов , тактирующих работу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 9. При запуске аналого-цифрового преобразователя 1 на его выходе формируется временной интервал, длительность которого пропорциональна значений входного напряжения. За счет этого в каждом такте

0

5

измерения на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9 J-ro канала формируется пачка импульсов, количество которых пропорционально абсолютной разности значений входного сигнала х- и j-ro сдвига эталонного сигнала y.j . Импульсы с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9 калсдого канала через элемент ИЛИ 10 своего канала поступа- 5 ют на тактовый вход счетчика 11 . Та- КИМ образом, после N тактов в каждом J-M счетчике 11 будет накоплен код значения модульной функции

..1

В начале (N+1)-го такта измерения k-ro цикла на четвертом выходе синхронизатора 3 вырабатывается последовательность высокочастотньпс импульсов, поступающих на тактовые входы счетчика 5, делителя 6 и через элементы ИЛИ 10 на тактовые входы счетчиков 11. В момент переполнения счет0

чика 11 каждого канала на его выходе формируется импульс, перебрасы- ваюпдай триггер 12 своего канала в единичное состояние. После перехода триггеров 12 всех каналов в единич- ное состояние на выходе элемента И 13 также появляется состояние Г, по фронту нарастания которого прекращается формирование импульсов на четвертом выходе синхронизатора 3, а также происходит изменение частоты следования импульсов дискретизации с второго выхода синхронизатора 3. Так как из всех триггеров 12 последним в единичное состояние перейдет триггер 12 j-ro канала, в котором модульная функция в k-м цикле имеет локальный минимум 0, „ , то коли чество импульсов, сформированных на четвертом выходе синхронизатора 3 и записанных в счетчике 5, равно значению обратного кода P-G „,„ , где Р - коэффициент пересчета счетчика 11. После окончания (k-l ).-го цикла коэффициент D., пересчета делителя 6 равен значению максимального из обратных кодов, определенных на интервале (k-l)-го циклов. Если значение Р-О, k-ro цикла превьша- ет значение коэффициента пересчета D., , то на выходе делителя 6 формируется импульс, разрешающий перепись кода из счетчика 5 в делитель 6. При этом происходит изменение коэффициента пересчета делителя 6, который ста новится равным значению кода, записанному в счетчике 5. Одновременно в регистр 8 переписывается код номера цикла, в котором модульной функции минимально из всех полу- ченных в предыдущих циклах.

В дальнейшем работа происходит аналогичным образом.

При этом в конце последнего L-ro цикла в регистре 8 будет формирован- код номера цикла, в котором взаимомодульная функция имеет глобальный минимум.

Формула изобретения

Многоканальное устройство для вычисления модульной функции, содержащее аналого-цифровой преобразователь синхронизатор и п каналов (п - число отсчетов модульной функции, натуральное число), каждый из которых содер

0

5

5 О 5 5 0

5

0

5

0

жит регистр, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, счетчик и триггер, причем информационный вход аналого-цифрового преобразователя является входом устройства, выход аналого-цифрового преобразователя соединен с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ каждого канала, вторые входы которых соединены с выходами регистров соответствующих каналов, а третьи входы соединены с первым выходом синхронизатора, второй выход которого соединен с тактовыми входами регистров каждого канала и аналого-цифрового преобразователя, информационный вход регистра каждого канала, кроме первого, соединен с выходом регистра предшествующего канала, выход счетчика каждого канала соединен с выходом установки 6 1 триггера соответствующего канала, вход установки в О триггеров и входы сброса счетчиков каждого канала соединены с третьим выходом синхронизатора, отличающееся тем, что, с целью повьшгения помехоустойчивости, в устройство введены генератор эталонного сигнала, первый и второй счетчики, делитель, регистр и элемент И, а в каждый канал устройства дополнительно введен элемент ИЛИ, тактовый вход генератора эталонного сигнала соединен с вторыми выходами синхронизатора, а выход соединен с информационным входом регистра первого канала, первый вход элемента ИЛИ каждого канала соединен с выходом элемента ИСКЛЮЧА- ОЩЕЕ ИЛИ своего канала, вторые входы элементов ИЛИ всех каналов соединены с тактовыми входами первого счетчика, делителя и под- ключены к четвертому выходу синхронизатора, выход элемента ИЛИ каждого канала соединен со счетным входом счетчика своего канала, вход элемента И соединен с входом запуска синхронизатора, третий выход которого соединен со счетным входом второго счетчика и входами сброса делителя и первого счетчика, выход которого соединен с входом задания коэффициента пересчета делителя, выход которого соединен со своим входом разрешения записи и входом разрешения записи регистра, информационный вход которого соединен с выходом второго счетчика, а выход - является выходом устройства.

Редактор М. Дылын Техред м.Ходанич

Заказ 7052/43 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно

-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор В. Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для вычисления модульной функции | 1982 |

|

SU1115062A1 |

| Многоканальное устройство для вычисления инвертированной модульной функции взаимокорреляции | 1989 |

|

SU1689969A1 |

| Многоканальное устройство для вычисления функции эквивалентности | 1985 |

|

SU1317455A1 |

| Многоканальное устройство для вычисления модульной корреляционной функции | 1989 |

|

SU1686433A1 |

| Многоканальное устройство для вычисления структурной функции | 1985 |

|

SU1282160A1 |

| Светолучевой осциллограф | 1984 |

|

SU1318918A1 |

| Устройство приема шумоподобных сигналов | 1987 |

|

SU1663772A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Статистический анализатор | 1989 |

|

SU1631557A1 |

| Статистический анализатор | 1983 |

|

SU1144120A1 |

Устройство относится к вычислительной технике и предназначено для статистического анализа случайных I процессов. Цель изобретения - повышение помехоустойчивости. В дснове работы устройства лежит развертка периода эталонного сигнала, который сравнивается в каждом канале устройства с входнЕ 1м шумоподобным сигналом, фаза которого неизвестна. В каждом цикле происходит запоминание минимального значения модульной функции, сформированного в одном из каналов, после чего происходит изменение периода сигнала на некоторую величину. После выполнения всех циклов анализа на выходных шинах устройства вьщается код,номера цикла, в котором модульная функция принимает минимальное значение, что соответствует периоду входного сигнала, выделенному на фоне помех. Устройство содержит аналого-цифровой преобразователь, синхронизатор, генератор эталонного сигнала, два счетчика, делитель, регистр п-каналов, в каждом канале - регистр, элемент ИС- КЛЮЧАЩЕЕ ИЛИ, элемент ИЛИ, счетчик, триггер, элемент И. 2 ил. i Л 1C 00 о со

| Курочкин С,С | |||

| Многоканальные счетные системы и коррелометры | |||

| - | |||

| М, : Энергия, 1972, с | |||

| Устройство для вытяжки и скручивания ровницы | 1923 |

|

SU214A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-30—Публикация

1985-07-01—Подача