1

(21)4684300/24

(22)28.04.89

(46) 28.02.91. Бюл. №8

(71) Уфимский авиационный институт

им. Серго Орджоникидзе

(72)Ю.Е.Алыпов, В.Е.Гвоздев, С.Ф.Фатиков

и Л.А.Горохова

(53)681.3(088.8)

(56)Авторское свидетельство СССР № 1368892,кл. G 06 F15/36, 1986. (54) СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР

(57)Изобретение относится к вычислительной технике и может быть использовано при

определении закона распределения случайных величин при малом числе наблюдений. Целью изобретения является расширение функциональных возможностей за счет определения энтропии распределения при малом числе наблюдений. Анализатор содержит счетчик 7, синхронизатор 8, триггер 5, регистры 3, 6 и 13, блоки вычисления 10 и 15 натурального логарифма, вы читатель 9, сумматоры 11 и 17, делители 12 и 14, аналого-цифровой преобразователь 1, элемент И 2, элементы задержки 4 и 19, блок 18 регистрации, элемент 16 сравнения. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения закона распределения | 1986 |

|

SU1388900A1 |

| Устройство для определения закона распределения случайной величины | 1987 |

|

SU1425715A1 |

| Устройство для определения закона распределения случайной величины | 1986 |

|

SU1425713A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Статистический анализатор | 1989 |

|

SU1695328A1 |

| Коррелометр | 1987 |

|

SU1478225A1 |

| Статистический анализатор | 1990 |

|

SU1698892A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Статистический анализатор | 1987 |

|

SU1499376A1 |

| Статистический анализатор | 1986 |

|

SU1401482A1 |

Изобретение относится к вычислительной технике и может бы гь использовано при определении закона распределения случайных величин при малом числе наблюдений

Целью изобретения является расширение функциональных возможностей за счет определения энтропии распределения при малом числе наблюдений.

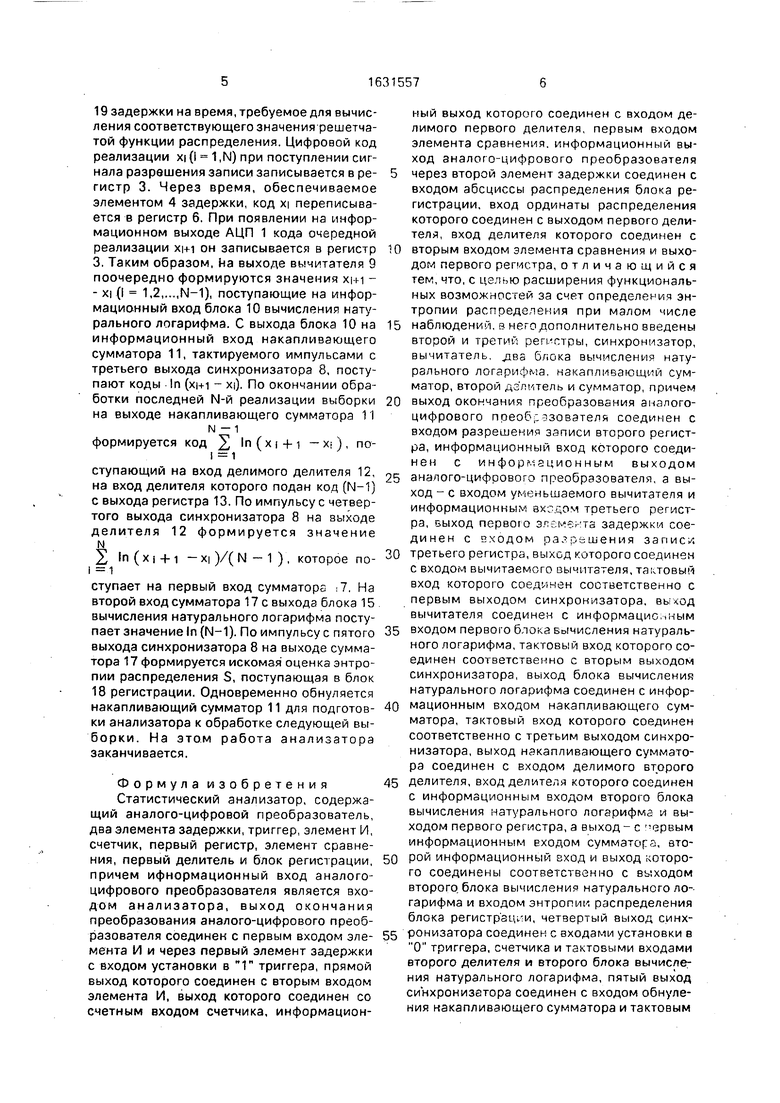

На чертеже приведена функциональная схема предлагаемого анализатора.

Анализатор содержит аналого-цифровой преобразователь (АЦП) 1, элемент И 2, регистр 3, элемент 4 задержки, триггер 5, регистр 6, счетчик 7, синхронизатор 8, вычи- татель 9,блок 10 вычисления натурального логарифма, накапливающий сумматор 11, делитель 12, регистр 13, делитель 14, блок 15 вычисления натурального логарифма, элемент 16 сравнения, сумматор 17, блок 18 регистрации и элемент 19 задержки.

Принцип действия статистического анализатора основан на использовании отдель- ных положений теории порядковых статистик. При этом полагаются известными из физических соображений нижняя а и верхняя b границы области возможных значений случайного сигнала X, которые совместно с реализациями случайного сигнала представляются в виде расширенной упорядоченной выборки

xi а Х2 хз

XN Ь

(1)

Соответствующие значения реальной функции распределения у F(x) образуют последовательность

yi уа ... ум

(2)

Плотность вероятности прохождения интегральной функции распределения на уровне у для i-ro элемента последовательности (1) в серии из N элементов характеризуется бета-распределением.

В соответствии с принципом максимального правдоподобия наилучшими (наиболее вероятными) оценками для элементов последовательности (2) - значений реальной функции распределения - являются значения yi, соответствующие максимальным значениям плотности вероятности;

...N.(3)

Оценка энтропии распределения, соответствующая полученной решетчатой оценке функции распределения (3), имеет вид «N - 1

2) In (xi + 1 -xi)

S In ( N - 1 ) + . (4)

Перед началом работы в регистр 13 заносится (N-1) заданное заранее значение объема выборки, уменьшенное на единицу, триггер 5 установлен в О. Поступающие на

вход (АЦП) 1 значения xi (i 1, N) расширенной упорядоченной выборки (включающие нижнюю границу области возможных значений случайной величины, упорядоченные реализации случайной величины и верхнюю

0 границу области возможных значений случайной величины) преобразуются в цифровой код. Преобразование каждого 1-го значения (I 1,2, ,N) выбооки завершается формированием на выходе (АЦП) 1 импуль5 сного сигнала, поступающего на вход элемента И 2, на вход разрешения записи регистра 3 и через элемент 4 задержки на вход установки в 1 триггера 5 и на вход разрешения записи второго регистра 6. На

0 выходе триггера 5 устанавливается единичный код, который поступает на вход элемента И 2. Поскольку время задержки, обеспечиваемое элементом 4, превышает длительность управляющего импульса, сиг5 налы, поступающие на вход элемента И 2, не совпадают во воемени и первый импульс последовательности не поступает на выход элемента И 2 и на счетный вход счетчика 7, Управляющие импульсы с номерами i

0 2, 3, .. N с выхода АЦП 1 поступают на вход элемента И 2, на другой вход которого одновременно поступает единичный сигнал с выхода триггера 5, и передаются на счетный вход счетчика 7, вызывая изменение его со5 стояния, и на вход запуска синхронизатора 8. В результате при поступлении каждого 1-го импульса в счетчике 7 формируется значение (i-1) Сигнал с выхода счетчика 7 поступает на второй вход элемента 16

0 сравнения и на вход делимого делителя 14, на второй вход элемента 16 сравнения и на вход делителя 14 подано значение (N-1) с выхода регистра 13, Как только сигналы на входах элемента 16 сравнения становятся0

5 равными (это имеет место при i N), на его выходе формируется сигнал, который подается на вход останова синхронизатора 8. Через время, необходимое для завершения операции деления в делителе 14, на четвер0 том выходе синхронизатора 8 формируется импульс, который поступает на входы установки счетчика 7 и триггера 5 в О. С выхода делителя 14 на вход ординаты распределения блока 18 регистрации последовательно

5 поступают значения M/N-1 (i 1,2,. ,,N) решетчатой функции распределения исследуемого случайного сигнала Одновременно на вход абсциссы распределения блока 18 регистрации поступают цифровые коды значений Xj (i 1.N). задержанные элементом

19 задержки на время, требуемое для вычисления соответствующего значения решетчатой функции распределения. Цифровой код реализации xi (I 1 ,N) при поступлении сигнала разрешения записи записывается в регистр 3. Через время, обеспечиваемое элементом 4 задержки, код xi переписывается в регистр 6. При появлении на информационном выходе АЦП 1 кода очередной реализации xi+i он записывается в регистр 3. Таким образом, На выходе вычитателя 9 поочередно формируются значения XIH - - xi (I 1,2,.,.,N-1), поступающие на информационный вход блока 10 вычисления натурального логарифма. С выхода блока 10 на информационный вход накапливающего сумматора 11, тактируемого импульсами с третьего выхода синхронизатора 8, поступают коды In (xj+i - xi). По окончании обработки последней N-й реализации выборки на выходе накапливающего сумматора 11

N - 1

формируется код ln(xi + i - х, ), поI 1

ступающий на вход делимого делителя 12, на вход делителя которого подан код (N-1) с выхода регистра 13. По импульсу с четвертого выхода синхронизатора 8 на выходе делителя 12 формируется значение

N

2) In ( х i + 1 - xi )/( N - 1 ) , которое по- I 1

ступает на первый вход сумматора 7, На второй вход сумматора 17 с выхода блока 15 вычисления натурального логарифма поступает значение In (N-1). По импульсу с пятого выхода синхронизатора 8 на выходе сумматора 17 формируется искомая оценка энтропии распределения S, поступающая в блок 18 регистрации. Одновременно обнуляется накапливающий сумматор 11 для подготовки анализатора к обработке следующей выборки. На этом работа анализатора заканчивается.

Формула изобретения Статистический анализатор, содержащий аналого-цифровой преобразователь, два элемента задержки, триггер, элемент И, счетчик, первый регистр, элемент сравнения, первый делитель и блок регистрации, причем ифнормационный вход аналого- цифрового преобразователя является входом анализатора, выход окончания преобразования аналого-цифрового преобразователя соединен с первым входом элемента И и через первый элемент задержки с входом установки в Г триггера, прямой выход которого соединен с вторым входом элемента И, выход которого соединен со счетным входом счетчика, информационный выход которого соединен с входом делимого первого делителя, первым входом элемента сравнения, информационный выход аналого-цифрового преобразователя

через второй элемент задержки соединен с входом абсциссы распределения блока регистрации, вход ординаты распределения которого соединен с выходом первого делителя, вход делителя которого соединен с

0 вторым входом элемента сравнения и выходом первого регистра, отличающийся тем, что, с целью расширения функциональных возможностей за счет определения энтропии распределения при малом числе

5 наблюдений, в него дополнительно введены второй и трети)/; регистры, синхронизатор, вычитатель, два блока вычисления натурального логарифма, накапливающий сумматор, второй дз литель и сумматор, причем

0 выход окончания преобразования аналого- цифрового поеоб,; ззовэтеля соединен с входом разрешения записи второго регистра, информационный вход которого соединен с информационным выходом

5 ачалого-цифоового преобразователя, а выход - с входом уменьшаемого вычитателя и информационным вхгцом тоетьего регистра, выход первого этме.-та задержки соединен с нчодом оа. уешения запис/.

0 третьего регистра, выход которого соединен с входом вычитаемого вычитзтеля, тазовый вход которого соединен соответственно с первым выходом синхронизатора, вь код вычитателя соединен с информацио ным

5 входом первого блока вычисления натурального логарифма, тактовый вход которого соединен соответственно с вторым выходом синхронизатора, выход блока вычисления натурального логарифма соединен с инфор0 мационным входом накапливающего сумматора, тактовый вход которого соединен соответственно с третьим выходом синхронизатора, выход накапливающего сумматора соединен с входом делимого второго

5 делителя, вход делителя которого соединен с информационным входом второго блока вычисления натурального логарифма и выходом первого регистра, а выход - с ервым информационным входом сумматора, вто0 РОЙ информационный вход и выход которого соединены соответственно с вь;ходом второго блока вычисления натурального логарифма и входом энтропии распределения блока регистрации, четвертый выход синх5 ронизатора соединен с входами установки в О триггера, счетчика и тактовыми входами второго делителя и второго блока вычисления натурального логарифма, пятый выход синхронизатора соединен с входом обнуления накапливающего сумматора и тактовым

входом сумматора, входы запуска и остано- венно с выходом элемента И и выходом ва синхронизатора соединены соответст- Равно элемента сравнения.

Авторы

Даты

1991-02-28—Публикация

1989-04-28—Подача