наглядности представления записанных аналоговых сигналов, их оперативной обработке, к. сокращению расхода фотоматериала и исключению градуировки аналоговых каналов. Устройство содержит оптическую систему 1, блок вибраторов 2, лентопротяжный механизм 3, делитель частоты 4, синхронизатор времени 5, задающий генератор 6, преобразователь 7 кода, программньй блок

1

Изобретение относится к электроизмерительной технике и может быть использовано для записи аналоговых и кодовых сигналов в .информационно-измерительных системах.

Целью изобретения является повышение точности считывания аналоговой информации при сохранении цифровой записи кодовых сигналов, что приводит к обеспечению наглядности представления записанных аналоговых сигналов, их оперативной обработке, к сокращению расхода фотоматериала и исключению градуировки аналоговых каналов.

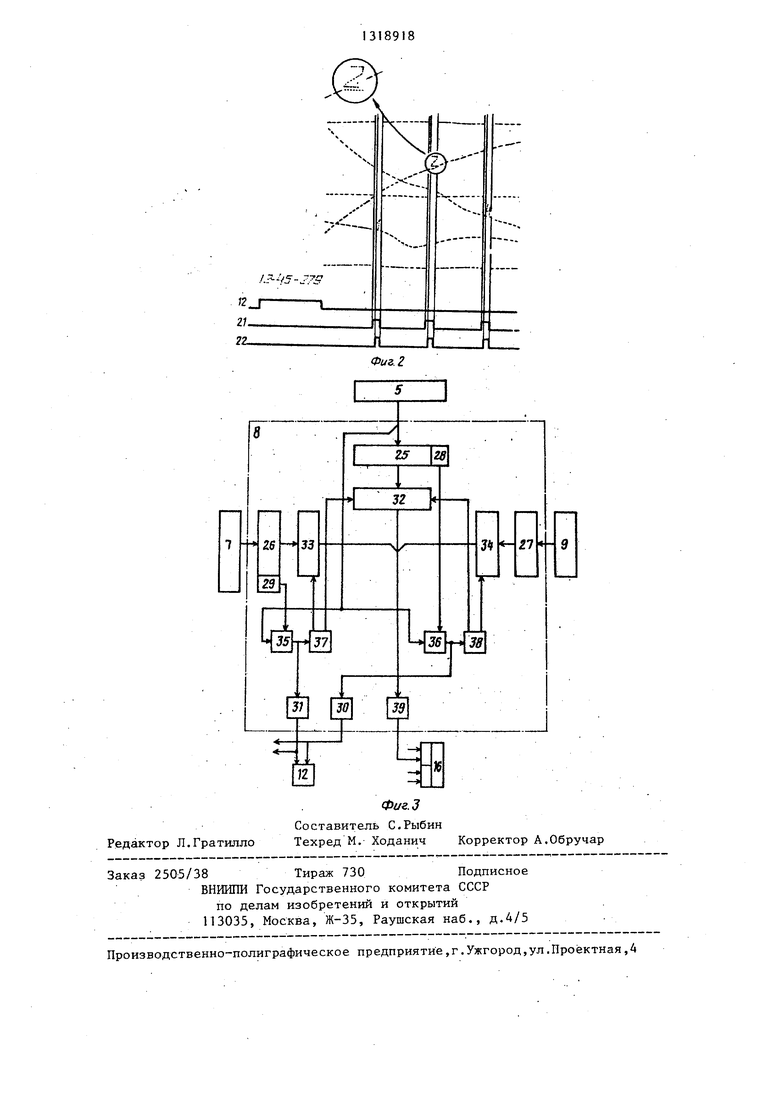

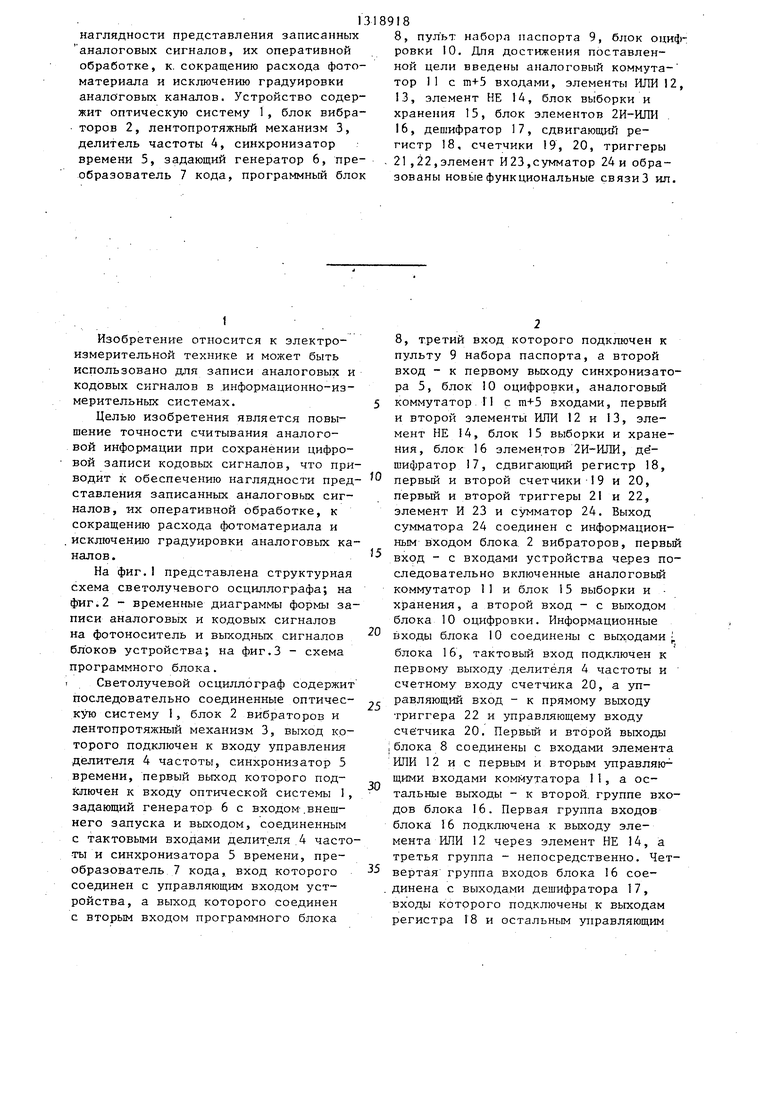

На фиг.1 представлена структурная схема светолучевого осциллографа; на фиг.2 - временные диаграммы формы записи аналоговых и кодовых сигналов На фотоноситель и выходных сигналов блоков устройства; на фиг.З - схема программного блока.

1 Светолучевой осциллограф содержит последовательно соединенные оптическую систему I, блок 2 вибраторов и лентопротяжный механизм 3, выход которого подключен к входу управления делителя 4 частоты, синхронизатор 5 времени, первый выход которого подключен к входу оптической системы , задающий генератор 6 с входом-.внешнего запуска и выходом, соединенным с тактовыми входами делителя .4 часто- Tbj и синхронизатора 5 времени, преобразователь 7 кода, вход которого соединен с управляющим входом устройства, а выход которого соединен с вторым входом программного блока

8, пульт набора паспорта 9, блок оцифровки 10, Для достижения поставленной цели введены аналоговый коммута- тор 11 с т+5 входами, элементы ИЛИ 12, 13, элемент НЕ 14, блок выборки и хранения 15, блок элементов 2И-ИЛИ 16, дешифратор 17, сдвигающий регистр 18, счетчики 19, 20, триггеры 21,22,элемент И23,сумматор 24 и образованы новьгефункциональные связи3 ил.

8, третий вход которого подключен к пульту 9 набора паспорта, а второй вход - к первому выходу синхронизатора 5, блок 10 оцифровки, аналоговьш

коммутатор 11 с т+5 входами, первый и второй элементы ИЛИ 12 и 13, элемент НЕ 14, блок 15 выборки и хранения, блок 16 элементов 2И-ИЛИ, дешифратор 17, сдвигающий регистр 18,

0 первый и второй счетчики 19 и 20, первый и второй триггеры 21 и 22, элемент И 23 и сумматор 24. Выход сумматора 24 соединен с информационным входом блока 2 вибраторов, первьй

вход - с входами устройства через последовательно включенные аналоговый коммутатор 11 и блок 15 выборки и хранения, а второй вход - с выходом блока 10 оцифровки. Информационные

входы блока 10 соединены с выходами . блока 16, тактовый вход подключен к первому делителя 4 частоты и счетному входу счетчика 20, а управляющий вход - к прямому выходу триггера 22 и управляющему входу счетчика 20. Первый и второй выходы ;блока 8 соединены с входами элемента ИЛИ 12 и с первым и вторым управляю щими входами коммутатора II, а остальные выходы - к второй, группе входов блока 16. Первая группа входов блока 16 подключена к выходу элемента ИЛИ 12 через элемент НЕ 14, а тре.тья группа - непосредс.твенно. Чет5 вертая группа входов блока 16 соединена с выходами дешифратора 17, входы которого подключены к выходам регистра 18 и остальным управляющим

5

0

313

входам коммутатора 11. Тактовый вход регистра 18 соединен с вторым выходом делителя 4 частоты, счетным входом счетчика 19 и первым входом элемента И 23, а вход разрешения сдвига - с инверсным выходом триггера 21 и управляющим входом счетчика 19, выход которого соединен с входом установки в единицу триггера 21. Вход установки в нуль триггера 21 подключен к выходу счетчика 20 и входу установки в нуль триггера 22, а прямой выход - к первому входу элемента ИЛИ 13, второй вход которого соединен с выходом элемента ИЛИ 12, а выход - с вторым входом элемента И 23. Вход установки в единицу триггера 22 подключен к выходу элемента И 23, а инвер- сный выход - к управляющему входу fлока 15 выборки и хранения.

Программный блок 8 (фиг.З) содержит приемные регистры 25-27 с разрядами признака кодов 28 и 29 .сигнала у регистров 25 и 26 соответст- венно. Входы регистров 25-27 подключены к первому, второму и третьему входам блока 8. Выходы одновибрато- ров 60 и 31 соединены с первым и вторым выходами блока 8. Первые группы входов блока элементов И 32-34 соединены с выходами регистров 25-27 соответственно, .Входы элементов И 35 и 36 соединены с первым входом блока 8, вторые входы - с выходами разря- ДОН признака кодов 29 и 28 сигнала, а выходы - с входами сдвигающих регистров 37 и 38 и одновибраторов 31 и 30 соответственно. Выходы регистра 36 соединены с вторыми группами вхо- дов блоков 32 и 34, а выходы регистра 37 - с третьей группой входов блока 32 и второй группой входов блока 34, выходы блоков 32-34 подключены к последующим выходам блока 8 через блок 39 элементов 1-ШИ.

Делитель 4 частоты имеет два входа и два выхода: тактовьш вход опорной частоты, первый выход - выход пересчитанной опорной частоты, слу- жащий для формирования о;гдельных точек цифр на фотоматериале, второй выход - также выход пересчитанной опорной частоты, служащий для коммутации аналоговых сигналов, второй вход не- обходим для одновременного изменения двух выходных частот при изменении скорости протяжки фотоносителя, обеспечиваемого лентопротяжным механизмом 3.

Преобразователь 7 кода является преобразователем двоичного кода в двоично-десятичный код.

Програм ный блок 8 при появлении метки времени обеспечивает последовательную выдачу цифр на информационном выходе кода времени и кода паспорта записи с формированием на первом управляющем выходе высокого уровня сигнала, а при появлении цифрового кода в двоично-десятичной форме на выходе преобразователя 7 кода обеспечивает последовательную выдачу на информационном выходе кода цифрового входа и кода времени с формированием на втором управляющем выходе высокого уровня сигнала.

Пульт 9 набора кода паспорта содержит группу переключателей, с помощью которых осуществляется набор кода паспорта записи в двоично-десятичной форме.

Блок 10 оцифровки служит для формирования цифр в точечной форме.

Аналоговый коммутатор 11 содержит т+5 информационных входов, один выход и три управляющих входа. Третий и последующие управляющие входы обеспечивают последовательное переключение на выход с 1 по т+3 вход (из них m входов предназначено для подачи измеряемых сигналов, на остальные три т+1 ; m-i-2; m+3 подаются эталонные сигналы, равные: один - нулевому уровню; второй - положительному эталонному уровню; третий - отрицательному эталонному уровню). При появлении сигнала управления на первом управляющем входе все указанные входы отключаются и подключается только . (т+4)-й вход, который обеспечивает уровень записи кода времени и кода паспорта записи. При появлении сигнала управления на втором управляющем входе также все указанные входы отключаются и подключается только ()-й вход, которьп обеспечивает уровень записи кода цифрового входа.

Устройство работает следующим образом.

Аналоговые сигналы как m входных для регистрации, так и три эталонных (т+1 - один нулевого уровня: и два т+2 и т+3 эталонных разнополяр- ных), подаваемые на входы аналогово513

го коммутатора 11, поочередно под управлением сдвигающего регистра 18 через устройство 15 выборки и хране- ния, работающего в режиме передачи данных, подаются на сумматор 24, который управляет работой блока 2 вибраторов. Тем самым на шлейфограмме обеспечивается поочередная запись аналоговых сигналов (фиг.2).

Через определенные промежутки времени (Т), задаваемые счетчиком 19, производится переброс триггера 21 в состояние единицы, при котором на входы управления сдвигающего регистра 18 и второго счетчика 19 подается сигнал, запрещающий сметой открывается по первому входу элемент ИЛИ 13. При этом следующей импульс со второго выхода делителя 4 частоты поступая на второй вход элемента И 23 перебрасывает триггер 22 в состояние единицы. Таким образом, во временном промежутке между выработкой счетчиком 19 и myльca управления и импульсом элемента И 23 обеспечивается запись куска аналогового сигнала перед оцифровкой. Единичное состояние триггера 22 разрешает также счет числа импульсов с первого выхода делителя 4 частоты в счетчике 20, переводит устройство 15 выборки и хранения в режим хранения последнего значения i-ro аналогового сигнала и включает блок- 10 оцифровки на формирование цифры i-ro аналогового сигнала, код которой подается через элементы 2И- ИЛИ 16 и дешифратор 17 от сдвигающего регистра 1.8. Это дает возможность сохранить значение i-ro аналогового сигнала постоянным и формировать цифру канала с помощью блока 10 оцифровки, сумматора 24 и блока 2 вибраторов. Включенный счетчик 20 производит подсчет импульсов с первого выхода делит-еля 4 частоты. По достижению в первом счетчике 20 числа импульсов, необходимых по времени для формирования полной цифры, счетчик 20 формирует сигнал, который устанавливает оба триггера 21 и 22 в состояние нуля, что предопределяет включение сдвигающего регистра 18 в последующий сдвиг, а счетчики 19 - в последующий счет. Далее повторяется все для другого канала (i+l)-ro сигнала, так как счетчик 18 имеет объем в (о( + 1)- единиц, где с/ - число ана8.6

логовых сигналов; р,-. любое целое число, определяемое как число штриховых линий от цифры канала до цифры канала в каждом канале.

При появлении на выходе синхронизатора 5 времени цифрового кода времени (с кодом признака) программный блок 8 обеспечивает (через первый управляющий выход) принудительное

включение (т+4)-го входного канала аналогового коммутатора I1, который через устройство 15 выборки и хранения и сумматор 24 передает на блок 2 вибраторов уровень записи цифрового

значения кода времени и кода паспорта, а также посредством элемента ИЛИ 12 запрещает прохождение через элементы 2И-ИЛИ 16 кода канала с дешифратора 17 и разреЕтает подачу через

элементы 16 на вход блока 10 оцифровки первой цифры кода времени, сформированного на информационном выходе программного блока 8, а через элементы ИЛИ 12 и 13, И 23 и триггер 22

осуществляет формирование разрешающего сигнала на управляющем входе блока

оцифровки.

Таким образом, на заданном (т+4)-м уровне на щлейфрграмме формируется первая цифра кода времени, затем аналогичным образом формируются последующие цифры кода времени и кода паспорта.

Работа программного блока 8 заключается в приеме данных с синхронизатора 5 времени, с пульта 9 набора паспорта и/или с преобразователя 7 соответственно в приемные регистры

25 с .приемным регистром 28 признака сигнала кода, 27 и/или 26 с приемным регистром 29 признака сигнала кода. Признаки кода 28 с синхрониза- тор а 5 времени (или признаки кода 29.

с цифрового входа устройства) открывают элемент И 36 (или И 35) для прохождения тактовых импульсов с синхронизатора 5 времени на- сдвигающий регистр 38 при появлении кода времени (или на сдвигаюшдй регистр 37 при появлении цифрового входного кода), которые производят подекадную передачу данньгх с приемных регистров 25 и 26 при признаке входного цифрового кода

в общую выходную группу элементов ИЛИ 39. Одновременно с этим при каждом сигнале выдачи последующей каждой декады с элемента И 36 (или 35)

7I

через формирователи типа одновибра- торов 30 (или 31) формируются первы (или вторые) сигналы управления с программного блока 8, При появлении кода цифрового входа (с кодом приз- нака) устройства на выходе преобразователя 7 аналогичным образом на заданном (т+5)-м уровне на шлейфо- грамме записываются первая и последующие цифры кода цифрового входа, а далее - код времени.

Формула изобретени

Светолучевой осциллограф, содержащий последовательно соединенные оптическую систему, блок вибраторов и лентопротяжный механизм, выход которого подключен к входу управления делителя частоты, тактовый вход котрого соединен с входом синхронизатора времени и с выходом задающего генератора, вход которого является вхдом внешнего запуска устройства, вход оптической системы соединен с вторым выходом синхронизатора времени, преобразователь кода, вход которого подключен к управляющему входу устройства, программный блок, пульт набора паспорта, блок оцифровки, о личающийся тем, что, с. целью повышения точности считьшания аналоговых данных, в него введены дополнительно -аналоговый коммутатор два элемента ИЛИ, элемент НЕ, блок выборки и хранения, блок элементов 2И-ШШ, дещифратор, сдвигающий регистр, два счетчика, два триггера, элемент И и сумматор, выход которог соединен с информационным входом бл ка вибраторов, первый вход - с входми устройства через последовательно соединенные аналоговый коммутатор и блок выборки и хранения, второй вхо с выходом блока оцифровки, тактовый вход которого соединен с первым выходом делителя частоты и со счетным

15

с fO

3520

25

30

40

45

входом второго сче-гчика, управляющий вход - с прямым выходом второго триггера и входом управления второго счетчика, а информационные входы подключены к выходам блока элементов 2И- ИЛИ, выход второго счетчика соединен С входами установки нуля второго и первого триггеров, инверсный выход второго триггера соединен с входом управления блока выборки и хранения, а вход установки единицы - с выходом элемента И, первый вход которого соединен с вторым выходом делителя частоты, со счетным входом первого счетчика и тактовым входом сдвигающего регистра, а второй вход - с прямым выходом первого триггера через пер- вый вход второго элемента ИЛИ, вход установки единицы которого соединен с выходом первого счетчика, а инвер- . сный выход - с входом управления первого счетчика и входом разрешения сдвига сдвигающего ре гистра, выходы последнего соединены с третьим и последующими управляющими входами аналогового коммутатора и с входами дешифратора, выходы которого соединены с четвертой группой входов блока элементов 2И-ИЛИ, третья группа входов

.последнего соединена с выходом первого элемента ИЛИ и с вторым входом второго элемента ИЛИ, первая группа - с выходом первого элемента ИЛИ через элемент НЕ, вторая группа - с третьим и последующими выходами программного блока, первый вход которого соединен с выходом синхронизатора времени, второй вход - с выходом преобразователя кода, третий вход - с пультом набора паспорта, первый выход - с первым управляющим входом аналогового коммутатора и с первым входом первого элемента ИЛИ, а второй выход - с вторым управляюш51м входом коммутатора и вторым входом пер вого элемента ИЛИ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования символов | 1983 |

|

SU1113840A1 |

| Преобразователь сдвига фазы в код скорости и ускорения | 1986 |

|

SU1358096A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1005170A1 |

| Многоканальный программируемый аналого-цифровой преобразователь | 1985 |

|

SU1266002A1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| Устройство для отображения системы координат на экране электронно-лучевой трубки | 1982 |

|

SU1053141A1 |

| Система экстремального регулирования | 1985 |

|

SU1352452A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Устройство стабилизации амплитуды видеосигнала | 1989 |

|

SU1748283A1 |

| Устройство для записи цифровой информации | 1987 |

|

SU1490690A1 |

Фиг.З

Составитель С.Рыбин Редактор Л.Гратияло Техред М. Ходанич .

ЗакаГ2505/38 Тираж 730П° °

ВНИИПИ Государственного комитета LOLF

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., Д.4/5

Производственно

-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

| Цифровой светолучевой осциллограф | 1977 |

|

SU700841A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 913263, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-06-23—Публикация

1984-11-15—Подача