Изобретение относится к вычислительной технике, предназначено для статического анализа случайных процессов путем вычисления структурной функции и может быть использовано для корреляционной обработки сигналов в реальном масштабе времени.

Цель изобретения - повьшение быстродействия устройства.

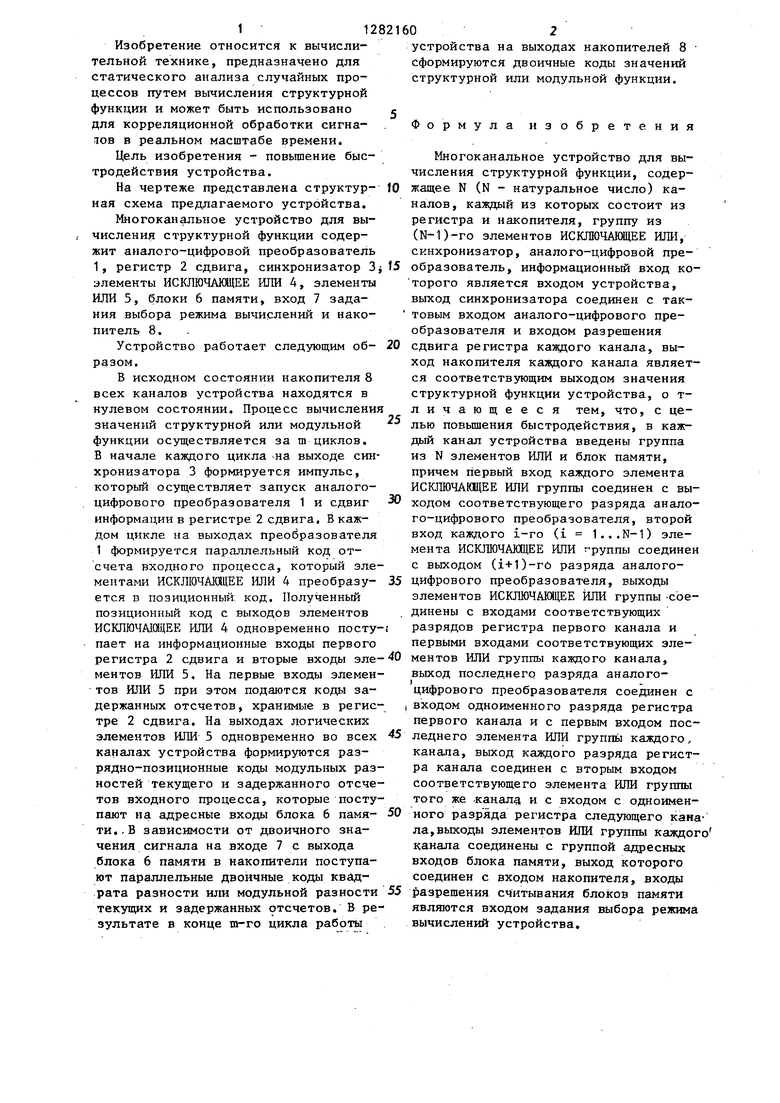

На чертеже представлена структурная схема предлагаемого устройства.

Многоканальное устройство для вычисления структурной функции содержит аналого-цифровой преобразователь

0

устройства на выходах накопителей 8 сформируются двоичные коды значений структурной или модульной функции.

Формула изобретения

Многоканальное устройство для вычисления структурной функции, содержащее N (N - натуральное число) каналов, каждый из которых состоит из регистра и накопителя, группу из (N-1)-ro элементов ИСКЛЮЧАЩЕЕ ИЛИ, синхронизатор, аналого-цифровой пре- 1, регистр 2 сдвига, синхронизатор образователь, информационный вход ко- элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 4, элементы торого является входом устройства, ИЛИ 5, блоки 6 памяти, вход 7 задания выбора режима вычислений и накопитель 8. .

Устройство работает следующим образом.

В исходном состоянии накопителя 8 всех каналов устройства находятся в нулевом состоянии. Процесс вычисления значений структурной или модульной функции осуществляется за m циклов. В начале каждого цикла на выходе синхронизатора 3 формируется импульс, который осуществляет запуск аналого- цифрового преобразователя 1 и сдвиг информации в регистре 2 сдвига. В каждом цикле на выходах преобразователя 1 формируется параллельный код отсчета входного процесса, который элементами ИСКЛЮЧАЩЕЕ ИЛИ 4 преобразу- 35 цифрового преобразователя, выходы ется в позиционный: код. Полученный элементов ИСКЛЮЧАЩЕЕ ИЛИ группы -сое- позиционный код с выходов элементов ИСКПЮЧА1ШЩЕ ИЛИ 4 одновременно посту- пает на информационные входы первого

20

25

30

выход синхронизатора соединен с тактовым входом аналого-цифрового преобразователя и входом разрешения сдвига регистра каждого канала, выход накопителя каждого канала является соответствующим выходом значения структурной функции устройства, о т- личающееся тем, что, с целью повышения быстродействия, в каждый канал устройства введены группа из N элементов ИЛИ и блок памяти, причем первый вход каждого элемента ИСКЛЮЧАЩЕЕ ИЛИ группы соединен с выходом соответствующего разряда аналого-цифрового преобразователя, второй вход каждого i-ro (i 1...N-1) элемента ИСКЛЮЧАЩЕЕ ИЛИ руппы соединен с выходом (i+1)-ro разряда аналогодинены с входами соответствующих разрядов регистра первого канала и первыми входами соответствующих элерегистра 2 сдвига и вторые входы ментов ИЛИ группы каждого канала.

ментов Ш1И 5. На первые входы элементов ИЛИ 5 при этом подаются коды задержанных отсчетов, хранимые в регистре 2 сдвига. На выходах логических элементов ИЛИ 5 одновременно во всех каналах устройства формируются раз- рядно-позиционные коды модульных разностей текущего и задержанного отсчетов входного процесса, которые поступают на адресные входы блока 6 памяти., В зависимости от двоичного значения сигнала на входе 7 с выхода блока 6 памяти в накопители поступают параллельные двоичные коды квадвыход последнего разряда аналого- цифрового преобразователя соединен с входом одноименного разряда регистра первого канала и с первым входом пос- 45 леднего элемента ИЛИ группь: каждого канала, выход каждого разряда регистра канала соединен с вторым входом соответствующего элемента ШШ группы того же .канала и с входом с одноименного разряда регистра следующего канала, выходы элементов ИЛИ группы каждого канала соединены с группой адресных входов блока памяти, выход которого соединен с входом накопителя, входы

50

рата разности шш модульной разности 55 разращения считывания блоков памяти текущих и задержанных отсчетов. В ре- являются входом задания выбора режима зультате в конце ш-го цикла работы вычислений устройства.

устройства на выходах накопителей 8 сформируются двоичные коды значений структурной или модульной функции.

Формула изобретения

Многоканальное устройство для вычисления структурной функции, содержащее N (N - натуральное число) каналов, каждый из которых состоит из регистра и накопителя, группу из (N-1)-ro элементов ИСКЛЮЧАЩЕЕ ИЛИ, синхронизатор, аналого-цифровой пре- образователь, информационный вход ко- торого является входом устройства,

жащее N (N - натуральное число) каналов, каждый из которых состоит из регистра и накопителя, группу из (N-1)-ro элементов ИСКЛЮЧАЩЕЕ ИЛИ, синхронизатор, аналого-цифровой пре- образователь, информационный вход ко- торого является входом устройства,

цифрового преобразователя, выходы элементов ИСКЛЮЧАЩЕЕ ИЛИ группы -сое-

выход синхронизатора соединен с тактовым входом аналого-цифрового преобразователя и входом разрешения сдвига регистра каждого канала, выход накопителя каждого канала является соответствующим выходом значения структурной функции устройства, о т- личающееся тем, что, с целью повышения быстродействия, в каждый канал устройства введены группа из N элементов ИЛИ и блок памяти, причем первый вход каждого элемента ИСКЛЮЧАЩЕЕ ИЛИ группы соединен с выходом соответствующего разряда аналого-цифрового преобразователя, второй вход каждого i-ro (i 1...N-1) элемента ИСКЛЮЧАЩЕЕ ИЛИ руппы соединен с выходом (i+1)-ro разряда аналогоцифрового преобразователя, выходы элементов ИСКЛЮЧАЩЕЕ ИЛИ группы -сое-

динены с входами соответствующих разрядов регистра первого канала и первыми входами соответствующих элевыход последнего разряда аналого- цифрового преобразователя соединен с входом одноименного разряда регистра первого канала и с первым входом пос- леднего элемента ИЛИ группь: каждого канала, выход каждого разряда регистра канала соединен с вторым входом соответствующего элемента ШШ группы того же .канала и с входом с одноименного разряда регистра следующего канала, выходы элементов ИЛИ группы каждого канала соединены с группой адресных входов блока памяти, выход которого соединен с входом накопителя, входы

разращения считывания блоков памяти являются входом задания выбора режима вычислений устройства.

Редактор И.Шулла

Составитель В.Орлов

Техред М.Ходанич Корректор Е.Сирохман

Заказ 7269/49 Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для вычисления функции эквивалентности | 1985 |

|

SU1317455A1 |

| Многоканальное устройство для вычисления инвертированной модульной функции взаимокорреляции | 1989 |

|

SU1689969A1 |

| Многоканальное устройство для вычисления модульной функции | 1982 |

|

SU1115062A1 |

| Многоканальное устройство для вычисления модульной корреляционной функции | 1989 |

|

SU1686433A1 |

| Многоканальное устройство для вычисления модульной функции | 1985 |

|

SU1280394A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для контроля частоты вращения вала турбобура | 1982 |

|

SU1086135A1 |

| Многоканальный статистический анализатор | 1977 |

|

SU732890A1 |

| Цифровой вероятностный фильтр | 1985 |

|

SU1252918A1 |

| Устройство для измерения функции интенсивности | 1980 |

|

SU877562A1 |

.Изобретение относится к вычислительной технике. Цель изобретения - повышение быстродействия устройств а. Сущность предложенного решения заключается в том, что коды отсчетов входного процесса преобразуются в позиционные коды, запоминаются и сравниваются с кодами текущих отсчетов. Устройство содержит аналого-цифровой преобразователь, регистры сдвига, синхронизатор, элементы ИСКЛЮЧАЮЩЕЕ ИЖ, элементы ИЛИ, блоки памяти, накопители. 1 ил. (Л С

| МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ КОРРЕЛЯТОР | 0 |

|

SU337784A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство для вычисления модульной функции | 1982 |

|

SU1115062A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство дляВычиСлЕНия СТРуКТуРНОй фуНКции | 1977 |

|

SU840924A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-07—Публикация

1985-07-02—Подача