Изобретение относится к автоматике и вычислительной технике, в частности к задатчикам поверочных и управляющих сигналов сложной формы.

Цель изобретения - повышение точ- нести воспроизведения сигналов сложной формы.

На фиг. 1 изображена структурная схема генератора сигналов сложной формы; на фиг. 2 - структурная схе- ма устройства- управленияJ на фиг. 3 - функциональная схема накапливающего сумматора; на фиг, А - функциональная схема узла формирования управляющих сигналов; на фиг. 5 - функциональная схема узла ввода; на фиг.6 и 7 - временные диаграммы работы устройства управления и генератора сигналов сложной формы.

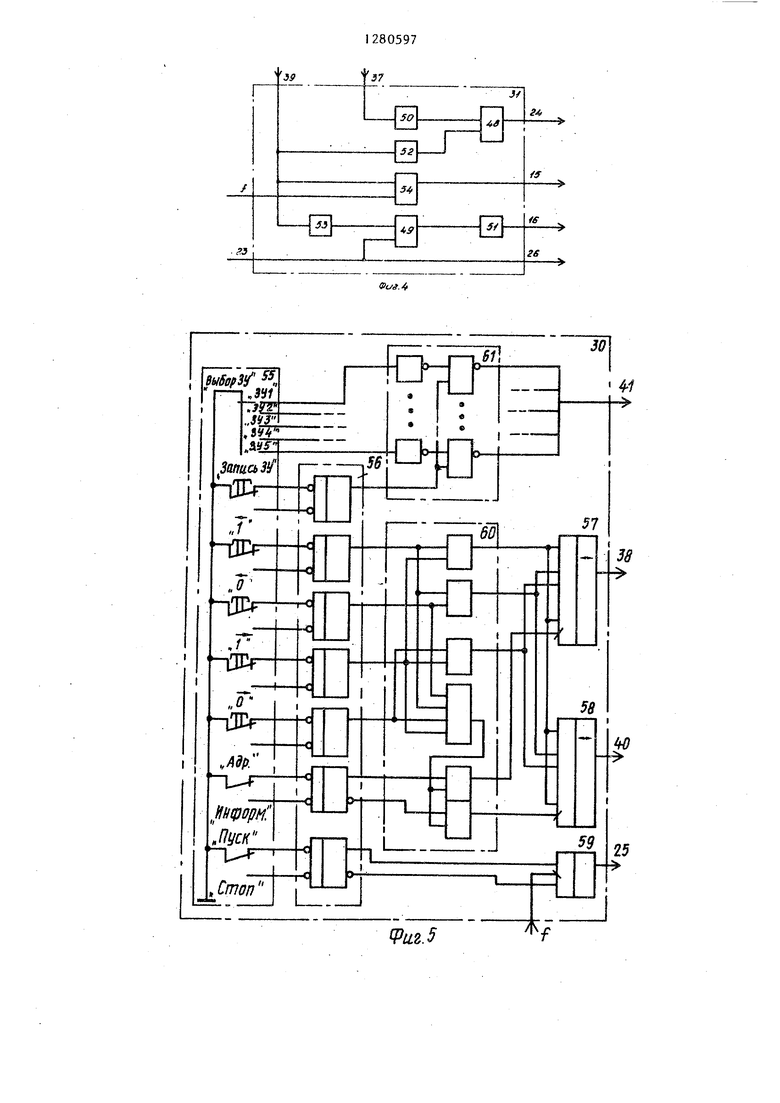

Генератор сигналов сложной формы содержит (фиг,1) генератор 1 тактовых импульсов, первый 2 и второй 3 делители частоты, п счетчиков 4 (где (п+1) - количество членов ряда, аппроксимирующего воспроизводимый сигнал) , коммутатор 5, сумматор 6, постоянное запоминающее устройство 7, умножитель 8, накапливающий сумматор 9, регистр 10 памяти, цифроана- логовьй преобразователь 11, аттенюатор 12, усилитель 13 мощности и блок 14 управления с входами-выходами 15-26.

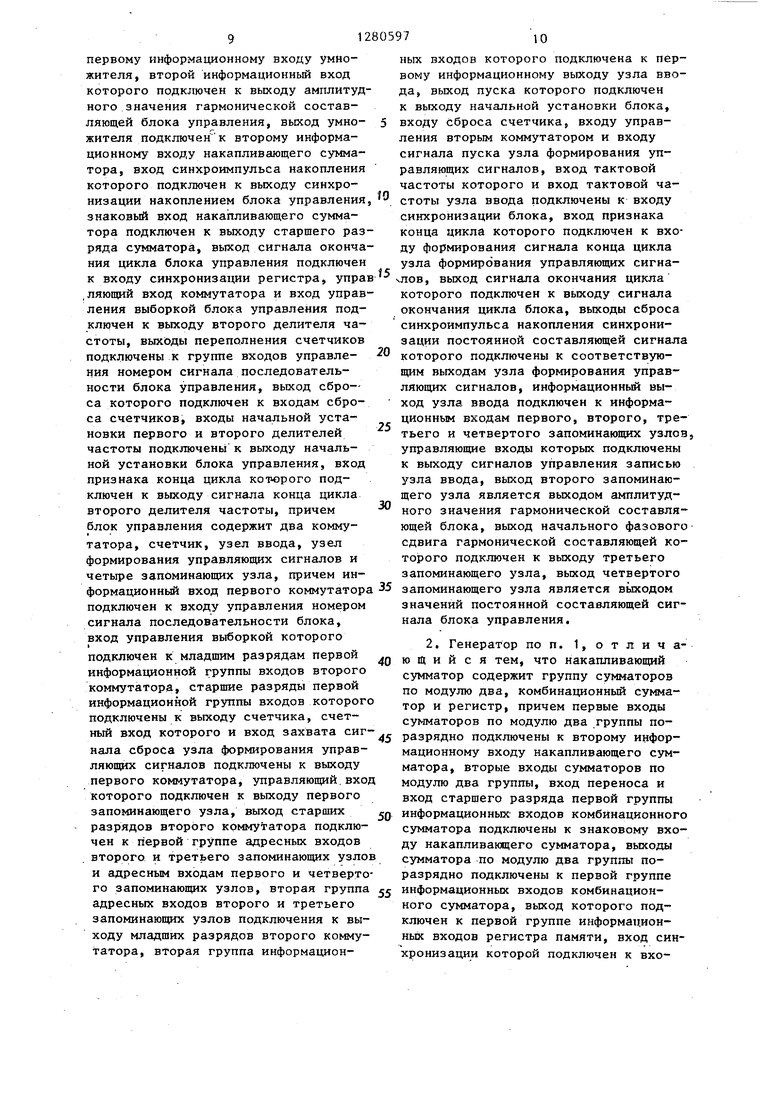

Блок 14 управления содержит (фиг. 2) второй 27 и третий 28 коммутаторы счетчик 29 сигналов сложной формы, узел 30 ввода, узел 31 формирования управляющих сигналов, первый 32,второй 33, третий 34, четвертый 35 запоминающие узлы, запоминающий узел 36, входы-выходы 37-41 узлов ввода и формирования управляющих сигналов. . Накапливающий сумматор 9 сод(ержит (фиг.З) комбинационный сумматор 42, второй регистр 43 памяти и группу 44 сумматоров по модулю два с входами- выходами 45-47.

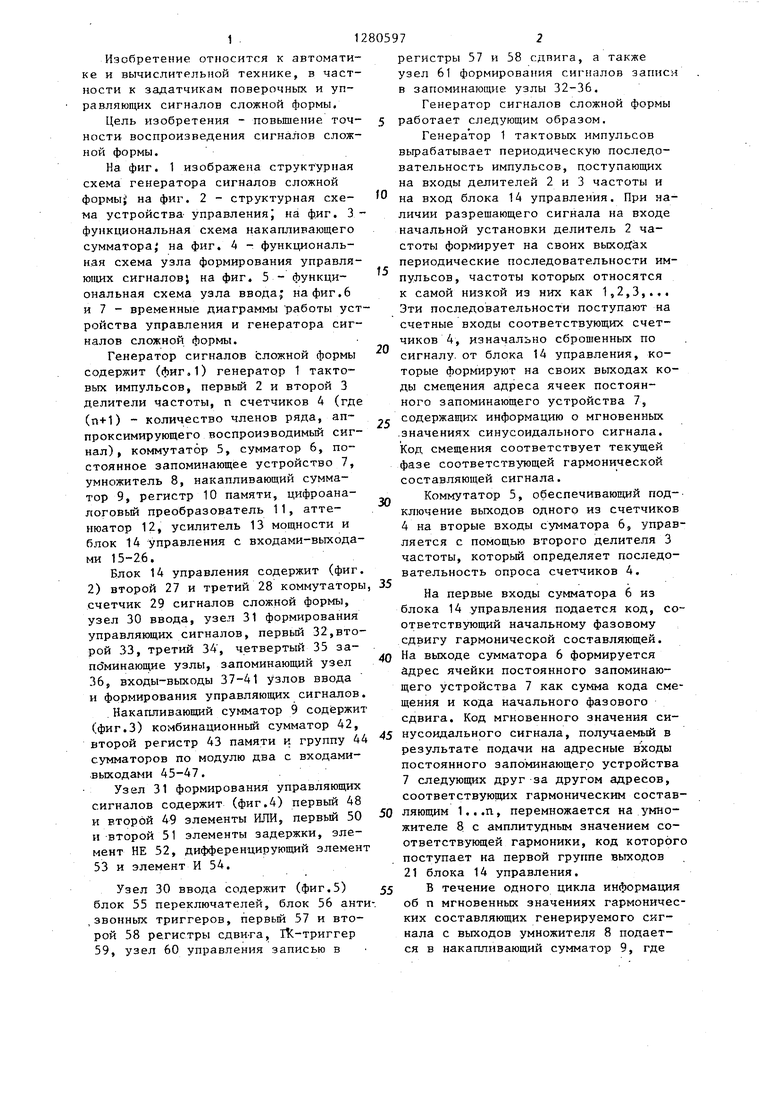

Узел 31 формирования управляющих сигналов содержит (фиг.4) первый 48 и второй 49 элементы ИЛИ, первый 50 и второй 51 элементы задержки, элемент НЕ 52, дифференцирующий элемент 53 и элемент И 54.

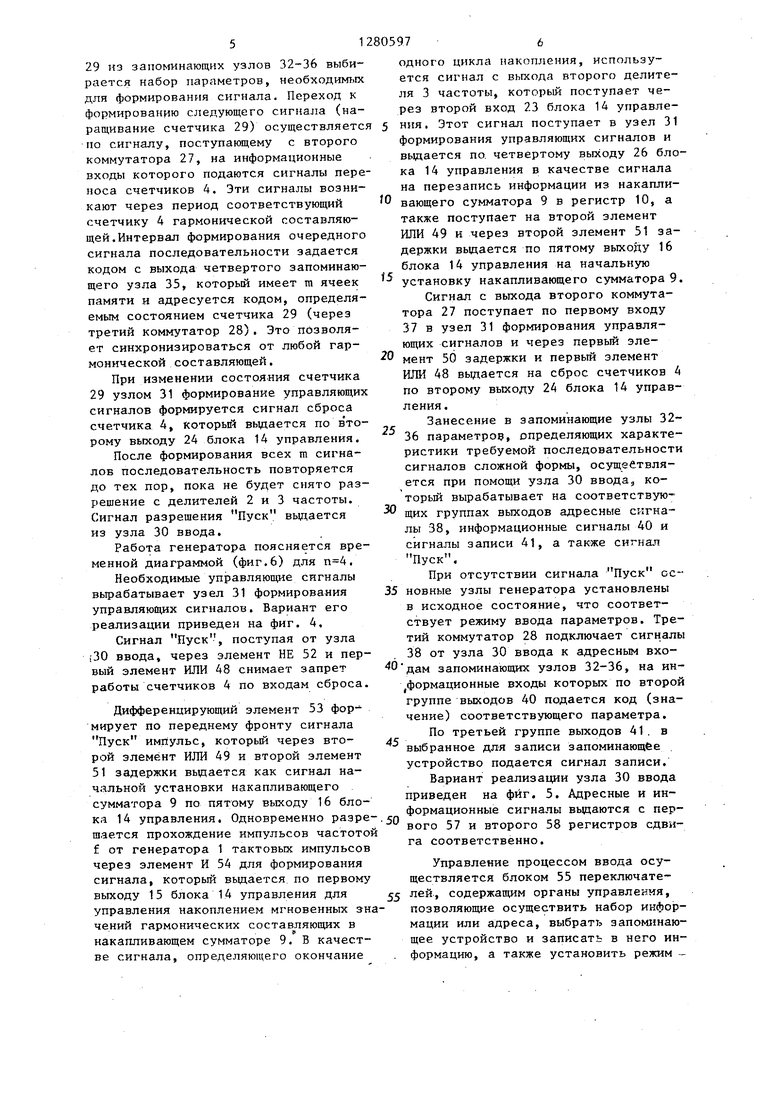

Узел 30 ввода содержит (фиг.5) блок 55 переключателей, блок 56 анти- звонных триггеров, первьй 57 и второй 58 регистры сдви-га, Л-триггер 59, узел 60 управления записью в

5

0

5

5

0

0

0

5

регистры 57 и 58 сдпига, а также узел 61 формирования сигналов записи в запоминающие узлы 32-36.

Генератор сигналов сложной формы работает следующим образом.

Генератор 1 тактовых импульсов вырабатывает периодическую последовательность импульсов, доступающих на входы делителей 2 и 3 частоты и на вход блока 14 управления. При наличии разрешающего сигнала на входе начальной установки делитель 2 частоты формирует на своих выходах периодические последовательности импульсов, частоты которых относятся к самой низкой из них как 1,2,3,.,. Эти последовательности поступают на счетные входы соответствующих счетчиков 4, изначально сброшенных по сигналу, от блока 14 управления, которые формируют на своих выходах коды смещения адреса ячеек постоянного запоминающего устройства 7, содержащих информацию о мгновенных .значениях синусоидального сигнала. Код смещения соответствует текущей фазе соответствующей гармонической составляющей сигнала.

Коммутатор 5, обеспечивающий под-- ключение выходов одного из счетчиков 4 на вторые входы сумматора 6, управляется с помощью второго делителя 3 частоты, которьй определяет последовательность опроса счетчиков 4,

На первые входы сумматора б из блока 14 управления подается код, соответствующий начальному фазовому сдвигу гармонической составляющей. На выходе сумматора 6 формируется адрес ячейки постоянного запоминающего устройства 7 как сумма кода смещения и кода начального фазового сдвига. Код мгновенного значения синусоидального сигнала, получаемый в результате подачи на адресные входы постоянного запоминающего устройства 7 следующих друг за другом адресов, соответствующих гармоническим составляющим 1...П., перемножается на умножителе 8 с амплитудным значением соответствующей гармоники, код которого поступает на первой группе выходов 21 блока 14 управления.

В течение одного цикла информация об п мгновенных значениях гармонических составляющих генерируемого сигнала с выходов умножителя 8 подается в накапливающий сумматор 9, где

определяется (с учетом знака) сумма всех мгновенньсс значений. Знак мгновенного значения определяется выходом старшего разряда сумматора 6, на котором О соответствует знаку пер- вого и второго квадранта (плюс), а 1 - третьего и четвертого (минус), Это позволяет в постоянном запоминающем устройстве 7 хранить значения половины периода синусоиды. В накап- ливающем сумматоре 9 осуществляется преобразование кода от умножителя 8 в дополнительный код.

Для этого используется группа 44 сумматоров по модулю два, инвертирующих входной код, преобразуя его в обратный при 1 в знаковом разряде Преобразование в дополнительный код и суммирование с ранее накопленным значением осуществляется с помощью комбинационного сумматора 42, на вход переноса и знакового (старшего) разряда которого подается значение знака.

Сумма кодов в накапливающем сумматоре 9 запоминается во втором регистре 43 памяти при подаче импульсов с первого выхода 15 блока 14 управления в момент, когда мгновенное значение очередной гармонической составляющей подано на входы накапли вающего сумматора 9с

В начале каждого цикла в накапливающий сумматор 9 заносится код, поступающий по четвертой группе вы- ходов 17 блока 14 управления. Эта начальная установка осуществляется по импульсу, поступающему по пятому выходу 16 блока 14 управления, и определяет постоянную составляющую формируемого сигнала сложной формы.

В течение цикла состояние счетчиков 4 не изменяется. По окончании цикла полученная в накапливающем сум- маторе 9 сумма переписьшается в ре- гистр 10 памяти (по сигналу, поступающему по четвертому выходу 26 блока 14 управления). Это приводит к изменению напряжения на выходе циф- роаиалогового преобразователя 11, мгновенные значения которого соответствуют выходному коду регистра 10 памяти. Это напряжение через аттенюатор 12, управляемый блоком 14 управ- ления по третьей группе выходов 18, и усилитель 13 можности поступает на выход генератора, оставаясь неизменным в течение следующего цикла

5

5 O

0

5 0

0

5

5

формирования мгновенного значения сигнала сложной формы.

Амплитудные значения гармонических составляющих сигнала, коды их начального фазового сдвига и код постоянной составляющей в блоке 14 управления считывается из первого 32, второго 33, третьего 34 запоминающих узлов соответственно. Код, управляющий аттенюатором 12, считывается из четвертого запоминающего узла 35.

Первый 32 и второй 33 запоминающие узлы содержат п ш ячеек памяти, где m - количество различных сигналов сложной формы в формируемой их последовательности. Для каждого сигнала последовательности в запоминаю- щих узлах 32 и 33 хранятся соответствующие коды для всех гармонических составляющих.

Третий 34 и четвертый 35 запоминающие узлы содержат по m ячеек памяти и хранят соответствующие коды для каждого сигнала последовательности.

Адресация для выбора кодов из пер вого 32 и второго 33 запоминающих узлов для каждой гармонической составляющей формируемого сигнала осуществляется по коду, поступающему от второго делителя 3 частоты через третий коммутатор 28.

Таким образом, на выходе генератора формируется сигнал последовательности (,...,т), определяемый выражением вида «

u(t)Ke + Zu;t, sin(iaH-cf,.f.). к ,

L ,-.,J Ь .

где и g- постоянная составляющая для f-ro сигнала последовательности, которая вводится на- . чальной установкой накапливающего сумматора 9, амплитудное значение i-й гармонической составляющей для сигнала, частота самой низкой гармонической составляющей выходного сигнала,

tfij- начальный фазовый сдвиг 1-й гармонической составляющей для f-ro сигнала, коэффициент определяеьшй кодом управления аттенюатором 12 для f-ro сигнала. Номер сигнала в последовательности

определяется счетчиком 29 сигналов

сложной формы, изначально сброщенным.

В соответствии с состоянием счетчика

;есо

5

29 из запоминающих узлов 32-36 выбирается набор параметров, необходим1.1 для формирования сигнала. Переход к формированию следующего сигнала (наращивание счетчика 29) осуществляет по сигналу, поступающему с второго коммутатора 27, на информационные входы которого подаются сигналы перноса счетчиков 4. Эти сигналы возникают через период соответствующий счетчику 4 гармонической составляющей. Интервал формирования очередног сигнала последовательности задается кодом с выхода четвертого запоминающего узла 35, которьй имеет га ячеек памяти и адресуется кодом, определя емьм состоянием счетчика 29 (через третий коммутатор 28). Это позволяет синхронизироваться от любой гармонической составляющей.

При изменении состояния счетчика 29 узлом 31 формирование управляющи сигналов формируется сигнал сброса счетчика 4, которьй выдается по в то рому выходу 24 блока 14 управления.

После формирования всех m сигналов последовательность повторяется до тех пор, пока не будет снято разрешение с делителей 2 и 3 частоты. Сигнал разрешения Пуск выдается из узла 30 ввода.

Работа генератора поясняется временной диаграммой (фиг.6) для .

Необходимые управляющие сигналы вырабатывает узел 31 формирования управляющих сигналов. Вариант его реализации приведен на фиг. 4.

Сигнал Пуск, поступая от узла |30 ввода, через элемент НЕ 52 и первый элемент ИЛИ 48 снимает запрет работы счетчиков 4 по входам сброса

Дифференцирующий элемент 53 формирует по переднему фронту сигнала Пуск импульс, который через второй элемент ИЛИ 49 и второй элемент 51 задержки вьщается как сигнал начальной установки накапливающего сумматора 9 по пятому выходу 16 блока 14 управления. Одновременно разр шается прохождение импульсов частот f от генератора 1 тактовых импульсо через элемент И 54 для формирования сигнала, который выдается по первому

выходу 15 блока 14 управления для 55 лей, содержащим органы управления, управления накоплением мгновенных эна- позволяющие осуществить набор инфор- чений гармонических составляющих в мации или адреса, выбрать запоминаю- накапливающем сумматоре 9. В качест- щее устройство и записать в него ин- ве сигнала, определяющего окончание . формацию, а также установить режим -

O

0

5

о

одного цикла накопления, используется сигнал с выхода второго делителя 3 частоты, который поступает через второй вход 23 блока 14 управле5 ния. Этот сигнал поступает в узел 31 формирования управляющих сигналов и выдается по. четвертому выходу 26 блока 14 управления в качестве сигнала на перезапись информации из накапливающего сумматора 9 в регистр 10, а также поступает на второй элемент ИЛИ 49 и через второй элемент 51 задержки вьщается по пятому выходу 16 блока 14 управления на начальную

5 установку накапливающего сумматора 9.

Сигнал с выхода второго коммутатора 27 поступает по первому входу

37в узел 31 формирования управляющих сигналов и через первый элемент 50 задержки и первый элемент ИЛИ 48 выдается на сброс счетчиков 4 по второму выходу 24 блока 14 управления.

Занесение в запоминающие узлы 32- 36 параметров, определяющих характеристики требуемой последовательности сигналов сложной формы, осущевтвля- ется при помощи узла 30 ввода, которьй вырабатывает на соответствующих группах выходов адресные сигналы 38, информационные сигналы 40 и сигналы записи 41, а также сигнал Пуск.

При отсутствии сигнала Пуск ос- 5 новные узлы генератора установлены в исходное состояние, что соответствует режиму ввода параметров. Третий коммутатор 28 подключает сигналы

38от узла 30 ввода к адресным вхо- О дам запоминающих узлов 32-36, на ин,формационные входы которых по второй группе выходов 40 подается код (значение) соответствующего параметра.

По третьей группе выходов 41, в выбранное для записи запоминающее устройство подается сигнал записи.

Вариант реализации узла 30 ввода приведен на фиг. 5. Адресные и информационные сигналы вьщаются с первого 57 и второго 58 регистров сдвига соответственно.

0

5

Управление процессом ввода осуществляется блоком 55 переключатеработы. Реализация блока 55 переключателей приведена на фиг. 5.

Первая группа выходов блока 55 переключателей, определяющая выбранное для записи запоминающее устройство, подключена к группе входов узла 61 формирования сигналов записи и в запоминающие узлы 32-36, Узел 61 (при использовании элементов ТТЛ) содержит блок элементов НЕ и блок элементов И-НЕ (по одному на каждый формируемый сигнал записи).

Сигнал выбора запоминающего устройства приходит с уровнем О, инвертируется и разрешает прохождение через соответствующий элемент п-НЕ сигнала записи, поступающего с первого выхода блока 56 антизвонных триггеров. С выходов блока элементов И-НЕ сигналы записи выдаются на третьей группе выходов 41 узла 30 вывода на соответствующие входы записи запоминающих устройств.

Вторая группа выходов блока 55 переключателей задает сигнал Запись ЗУ (от кнопки Запись ЗУ), сигналы последовательной записи О и 1 в младший разряд или в старший разряд (от кнопок О, 1 О, О), сигнал выбора регистра 57 или 58 сдвига (переключатель АДР/Информ) и сигнал Пуск (переключатель /Стоп). Дребезг контактов кнопок и пере1 ючателей устраняется блоком 56 антизвонных триггеров. Группа выходов 56 антизвонных триггеров,определяющая запись в регистр 57 или 58 сдвига необходимых кодов, подключена к входам узла 60 управления записью в регистры сдвига, который выбирает необходимый регистр 57 или 58 сдвига, формирует сигналы на входы SO и S1 регистров, управляющие направлением сдвига, а также сигнал на входы

последовательной записи информации DR и DL, определяющий значение оче- редного разряда записываемой информадии.

На фиг, 5 приведена функциональная Q сумматор и умножитель, причем выход

схема узла 60 управления записью в регистры сдвига для случая, когда в качестве регистров 57 и 58 сдвига используются универсальные регистры типа 155ИР13 или аналогичные.

Для синхронизации начала работы генератора сигналов сложной формы с импульсами генератора 1 тактовых им- ,пульсов используется 1К-триггер 59.

55

коммутатора подключен к первому информационному входу сумматора, второ информационный вход которого подключен к выходу начального фазового ; сдвига гармонической составляющей блока управления, информационный выход сумматора подключен к адресному входу постоянного запоминающего устройства, выход которого подключен к

На его входы 3 и К подаются сигналы с второго и третьего выходов блока 56 антизвонных триггеров 1 на которых соответствует наличию или отсутствию сигнала Пуск соответственно от блока 55 переключателей.

Триггер 59 изменяет- свое состояние при изменении сигналов на входах 1 и К по заднему фронту тактового импульса, поступающего на синхровход С ЗК- триггера. На его выходе формируется сигнал Пуск, синхронизированньй с импульсами генератора 1 тактовых импульсов,

Формула изобретения

0

0

5

0

5

1. Генератор сигналов сложной формы, содержащий генератор тактовых импульсов, два делителя частоты, п счетчиков , коммутатор, постоянное запоминающее устройство,накапливающий сумматор, регистр и блок управления,причем выход генератора тактовых импульсов 5 подключен к входам тактовых импульсов первого и второго делителей частоты и входу синхронизации блока управления, счетные входы счетчиков подключены к соотве уствующим выходам первого делителя частоты, информационные выходы счетчиков подключены к соответствующим информационным входам коммутатора, информационный выход накапливающего сумматора подключен к информационному входу регистра, выход которого является выходом генератора сигналов сложной формы,первая группа информационных входов накапливающего сумматора подключена к группе В1ьщодов установки постоянной составляющей сигнала блока управления, выход синхронизации постоянной составляющей сигнала которого подключен к синхровходу записи постоянной составляющей сигнала накапливающего сумматора, отличаю- ц и и с я тем, что, с целью повыше- шя точности воспроизведения сигна- пов сложной формы, в него введены

5

коммутатора подключен к первому информационному входу сумматора, второй информационный вход которого подключен к выходу начального фазового ; сдвига гармонической составляющей блока управления, информационный выход сумматора подключен к адресному входу постоянного запоминающего устройства, выход которого подключен к

первому информационному входу умножителя, второй информационный вход которого подключен к выходу амплитудного значения гармонической составляющей блока управления, выход умножителя подключен к второму информационному входу накапливающего сумматора, вход синхроимпульса накопления которого подключен к выходу синхронизации накоплением блока управления знаковый вход накапливающего сумматора подключен к выходу старшего разряда сумматора, выход сигнала окончания цикла блока управления подключен к входу синхронизации регистра, .ляющий вход коммутатора и вход управления выборкой блока управления подключен к выходу второго делителя частоты, выходы переполнения счетчиков подключены к группе входов управления номером сигнала последовательности блока управления, выход сбро-- са которого подключен к входам сброса счетчиков, входы начальной установки первого и второго делителей частоты подключены к выходу начальной установки блока управления, вход признака конца цикла котюрого подключен к выходу сигнала конца цикла второго делителя частоты, причем блок управления содержит два коммутатора, счетчик, узел ввода, узел формирования управляющих сигналов и четыре запоминающих узла, причем информационный вход первого коммутатор подключен к входу управления номером сигнала последовательности блока, вход управления выборкой которого

I

подключен к младшим разрядам первой информационной группы входов второго коммутатора, старшие разряды первой информационной группы входов которог подключены к выходу счетчика, счетупра

2. Генератор по п. 1, отлича ющийся тем, что накапливающий сумматор содержит группу сумматоров по модулю два, комбинационный сумматор и регистр, причем первые входы сумматоров по модулю два группы поный вход которого и вход захвата сиг- разряДно подключены к второму инфорнала сброса узла формирования управляющих сигналов подключены к выходу первого коммутатора, управляющий.вход которого подключен к выходу первого запоминающего узла, выход старших разрядов второго коммутатора подключен к первой группе адресных входов второго и третьего запоминающих узлов и адресным входам первого и четвертого запоминающих узлов, вторая группа ее адресных входов второго и третьего запоминающих узлов подключения к выходу младших разрядов второго татора, вторая группа информационмационному входу накапливающего сумматора, вторые входы сумматоров по модулю два группы, вход переноса и вход старшего разряда первой группы 50 информационных входов комбинационного сумматора подключены к знаковому входу накапливающего сумматора, выходы сумматора по модулю два группы поразрядно подключены к первой группе информационных входов комбинационного сумматора, выход которого подключен к первой группе информационных входов регистра памяти, вход синхронизации которой подключен к вхоO

35

чЛОВ,

0

5

0

0

нык входов которого подключена к первому информационному выходу узла ввода, выход пуска которого подключен к выходу начальной установки блока, входу сброса счетчика, входу управления вторьм коммутатором и входу сигнала пуска узла формирования управляющих сигналов, вход тактовой частоты которого и вход тактовой частоты узла ввода подключены к входу синхронизации блока, вход признака конца цикла которого подключен к входу формирования сигнала конца цикла узла формирования управляющих сигнавыход сигнала окончания цикла которого подключен к выходу сигнала окончания цикла блока, выходы сброса синхроимпульса накопления синхронизации постоянной составляющей сигнгша которого подключены к соответствую- щкм выходам узла формирования управляющих сигналов, информационный выход узла ввода подключен к информационным входам первого, второго, третьего и четвертого запоминающих узловj управляющие входы которых подключены к выходу сигналов управления записью узла ввода, выход второго запоминающего узла является выходом амплитудного значения гармонической составляющей блока, выход начального фазового- сдвига гармонической составляющей которого подключен к выходу третьего запоминающего узла, выход четвертого запоминающего узла является выходом значений постоянной составляющей сигнала блока управления.

2. Генератор по п. 1, отличающийся тем, что накапливающий сумматор содержит группу сумматоров по модулю два, комбинационный сумматор и регистр, причем первые входы сумматоров по модулю два группы по разряДно подключены к второму инфоре

мационному входу накапливающего сумматора, вторые входы сумматоров по модулю два группы, вход переноса и вход старшего разряда первой группы 0 информационных входов комбинационного сумматора подключены к знаковому входу накапливающего сумматора, выходы сумматора по модулю два группы поразрядно подключены к первой группе информационных входов комбинационного сумматора, выход которого подключен к первой группе информационных входов регистра памяти, вход синхронизации которой подключен к вхо111280597

ду синхроимпульса накопления накапливающего сумматора, первый информаци- онньй вход которого подключен к второй группе информационных входов рекопе то си

гистра памяти, вход синхронизации ко- 5 выходом сигнала окончания цикла узла.

выход первого элемента ИЛИ подключен к входу первого элемента задержки, выход которого подключен к выходу синхроимпульса постоянной составторой подключен к входу синхроимпульса записи постоянной составляющей сигнала накапливающего сумматора, выход регистра памяти подключен к

второй группе информационных входов ляющей узла, выход синхроимпульса

комбинационного сумматора и являет-сигнала накопления которого подклюся выходом накапливающего сумматора,чена к выходу элемента И, второй вход

3. Генератор по п. 1, о т л и ч а-которого подключен к входу тактовых ю щ и и с я тем, что узел формирова-импульсов узла, вход захвата сигна- ния управляющих сигналов содержит два сброса которого подключен к вхо- элемента ИЛИ, два элемента задержки,ду второго элемента задержки, выход элемент И, элемент НЕ и дифференциру-которого подключен к первому входу ющий элемент, причем вход сигнала пу-второго элемента ИЛИ, второй вход коска узла подключен к входу элементаторого подключен к выходу элемента НЕ, первому входу элемента И, входу НЕ, выход второго элемента ИЖ под- дифференцирующего элемента, выходключен к выходу сброса узла.

7

1 которого подключен к первому входу первого элемента ИЛИ, второй вход которого подключен к входу формирования сигнала конца циклов узла и является

выход первого элемента ИЛИ подключен к входу первого элемента задержки, выход которого подключен к выходу синхроимпульса постоянной составfut.3

(7

J

. J

&}/ Ч - IJ/f

эги

jyj

iVT

ЛУИ

ЗапиаЗ /

NET

.7

t-tlCF

J -liJDr

..0

пДСг

,%/r

,Cmon

-pC

«

4ff

zs

B1

30

JAT C

4-f

-

38

25

Редактор E. Копча

Составитель С. Курош Техред И.Попович

Заказ 7066/53Типаж 671 -Подписное

ВНИИПИ Государственного комитета СССР , по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

..- -. - - - - - - ™--

Производственно полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор А. Тяско

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

| Устройство для передачи дискретных сигналов | 1984 |

|

SU1277419A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Генератор периодических колебаний инфразвуковых частот с автоматической калибровкой | 1987 |

|

SU1497722A1 |

| ЦИФРОВОЙ МНОГОКАНАЛЬНЫЙ СИНТЕЗАТОР СЕТКИ ЧАСТОТ | 1995 |

|

RU2108655C1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| Цифровой анализатор спектра | 1979 |

|

SU798615A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

Изобретение относится к автоматике и вычислительной технике, в частности к задатчикзм поверочных и управляющих сигналов сложной формы. Целью изобретения является повышение течности воспроизведения сигналов , Генератор сигналов сложной формы содержит блок 14 управления, постоянное запоминающее устройство 7, генератор 1 тактовьк импульсов, два делителя частоты 2 и 3 цифроанало- говьй преобразователь 11, аттенюатор 12, усилитель 13 мощности, п счетчиков 4 (где п+1) - количество членов ряда, аппроксимирукяцего сигнал), коммутатор 5, накапливающий сумм°атор 9 и регистр 10 памяти, а устройство управления содержит пять запоминающих устройств, второй и третий коммутаторы, узел ввода и узел формирования управляющих сигналов. Цель изобретения достигается за счет введения сумматора и умножителя. 2 з.п. ф-лы, 7 ил. i (Л to о СП

| Электромагнитное реле | 1922 |

|

SU466A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-30—Публикация

1985-01-09—Подача