31497

фильтр 13 нижних частот, выходной масштабньш преобразователь 14, счетчики 15, 16, формирователь 17 импульсов, блок 19 сравнения и триггер 20, В устройство введены преобразователь 21 кода, коммутаторы 22, 23, вычислитель 24, элементы И 25-29, триггеры 30-33, блок 34 формирователей импульсов, реверсивньй счетчик 35, элементы ИЛИ 36-39, 49, оперативный за- поьпшающий блок 40, счетчики 41 и 42, блок 43 переключателей, регистры 44, 45, элементы 46-48 задержки. Сигналы

формируются в виде суммы: F(t) п

X (nu.i t+ (nwt) (1).

n 1 На первом этапе с помощью блоков 6

и 18 в оиеративньй запоминаюищй блок вводятся значения а „и Ь,. На втором этапе осуществляется синтез суммарного сигнала Последовательно формируются гармоники, входящие в сумму (1), причем синусоидальный цифровой сигнал

записан в постоянный запоминающий блок 8, умножение на коэффициенты а и Ьг, выполняется умножителем 9, частота данной гармоники определяется занесением кода в реверсивный счетчик 35с Сумматор 10 и оперативный запоминающий блок 11 выполняют накопление суммы (1),, На следующем этапе происходит автоматическая калибровка действующего значения зыходного сигнала. Для этого в вычислителе 24 вычисляется корень квадратный из суммы квадратов поступивших на него кодов и формируется нормирующий коэффициент, поступающий на выходной масштабный преоб1зазователь 14 о После г-то- го устройство генерирует периодический сигнал, определяемый формулой (1) с заданным действующим значением Элемент ИЛИ 49 позволяет ускорить формирование сигнала (1) при наличии нулевых значений а и Ь,; 2 ЗоП ф-лы, 2 ил о

| название | год | авторы | номер документа |

|---|---|---|---|

| Спироанализатор | 1986 |

|

SU1391621A1 |

| Устройство для сжатия и передачи информации | 1988 |

|

SU1515183A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| Калибратор периодических сигналов | 1989 |

|

SU1709262A1 |

| Анализатор спектра | 1984 |

|

SU1237987A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Фазометр | 1991 |

|

SU1817037A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Стенд для испытания энергоустановок электромобилей | 1985 |

|

SU1255890A1 |

Изобретение относится к импульсной технике и может быть использовано в генераторах сигналов для поверки и аттестации измерительной аппаратуры. Цель изобретения - расширение класса формируемых сигналов и уменьшение времени формирования сигнала. Устройство содержит генератор 1 импульсов, делитель 2 частоты, коммутаторы 3, 4, 7, блоки 5, 6, 18 переключателей, постоянный запоминающий блок 8, умножитель 9, сумматор 10, оперативный запоминающий блок 11, цифроаналоговый преобразователь 12, фильтр 13 нижних частот, выходной масштабный преобразователь 14, счетчики 15, 16, формирователь 17 импульсов, блок 19 сравнения и триггер 20. В устройство введены преобразователь 21 кода, коммутаторы 22, 23, вычислитель 24, элементы И 25-29, триггеры 30-33, блок 34 формирователей импульсов, реверсивный счетчик 35, элементы ИЛИ 36-39, 49, оперативный запоминающий блок 40, счетчики 41 и 42, блок 43 переключателей, регистры 44, 45, элементы 46-48 задержки. Сигналы формируются в виде суммы: F(T)=98C[ANCOS(NWT+WNSIN(NWT)] (1). На первом этапе с помощью блоков 6 и 18 в оперативный запоминающий блок вводятся значения AN и BN. На втором этапе осуществляется синтез суммарного сигнала. Последовательно формируются гармоники, входящие в сумму (1), причем синусоидальный цифровой сигнал записан в постоянный запоминающий блок 8, умножение на коэффициенты AN и BN выполняется умножителем 9, частота данной гармоники определяется занесением кода в реверсивный счетчик 35. Сумматор 10 и оперативный запоминающий блок 11 выполняют накопление суммы (1). На следующем этапе происходит автоматическая калибровка действующего значения выходного сигнала. Для этого в вычислителе 24 вычисляется корень квадратный из суммы квадратов поступивших на него кодов и формируется нормирующий коэффициент, поступающий на выходной масштабный преобразователь 14. После этого устройство генерирует периодический сигнал, определяемый формулой (1) с заданным действующим значением. Элемент ИЛИ 49 позволяет ускорить формирование сигнала (1) при наличии нулевых значений AN и BN. 2 з.п. ф-лы, 2 ил.

Изобретение относится к импульсной технике и может быть использовано в генераторах сигналов для поверки и аттестации измерительной аппаратуры.

Цель изобретения - расщирение класса формируемых сигналов за счет обеспечения формирования периодических сигналов произвольной формы при условии ограниченности их спектра Дополнительная цель изобретения - уменьпение времени формирования сигнала при наличии в нем нулевых гармоник

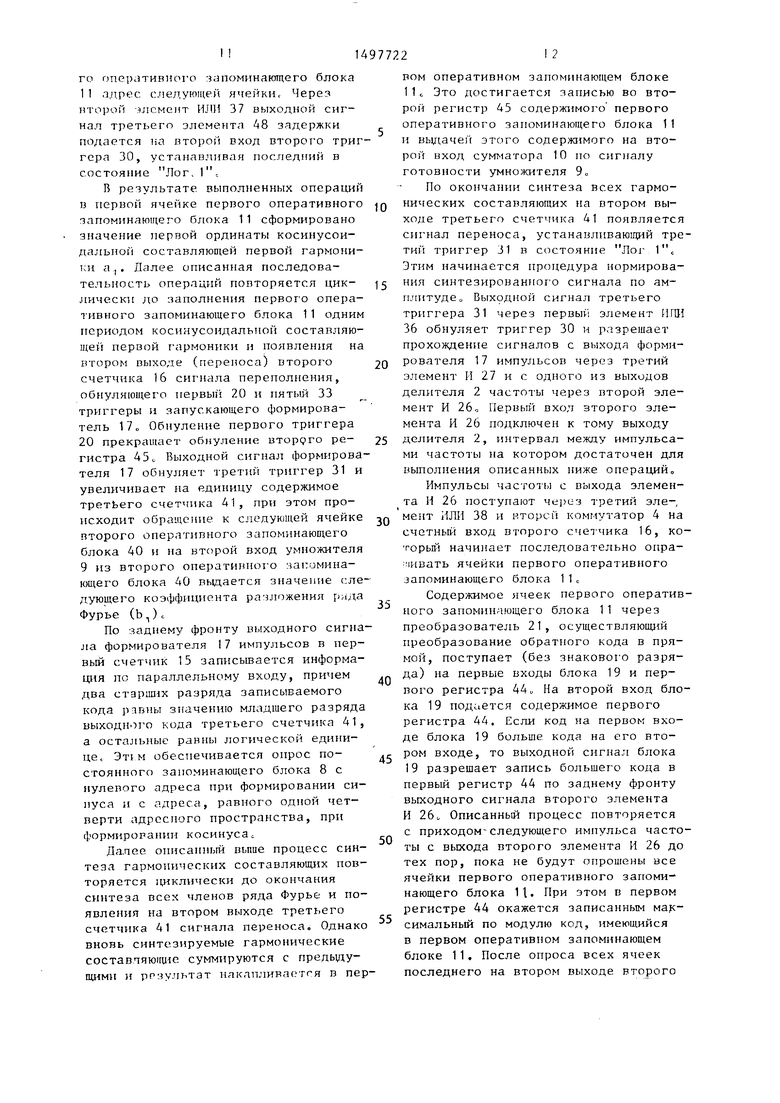

На фиг И изображена структурная схема генератора периодических колебаний инфразвуковых частот с автоматической калибровкой, на приведен пример выполнения вычислителя о

Устройство содержит последовательно соединенные генератор 1 импульсов, делитель 2 частоты, первый 3 и второй 4 коммутаторы, первьй блок 5 переключателей, выход которого соединен с управляющим входом первого коммутатора 3, второй блок 6 переключателей, выход которого подключен к первому входу третьего коьгмутатора 7, последовательно соединенные постоянный запоминаю1ций блок 8, умножитель 9, сумматор 10 и первый оперативный запоминающий блок 11, последовательно соединенные цифроаналого- вый преобразователь 12, фильтр 13 нижних частот и выходной масштабный преобразователь 14, причем выход последнего является выходом устройства, а также первый 15 и второй 16 счетчики, формирователь 17 импульсов, третий блок 18 переключателей, блок 19 сравнения, первый триггер 20, преобразователь 21 кода, четвертый ,

22 и пятый 23 коммутаторы, вычислитель 24, с первого по пятый элементы И 25-29, с второго по пятый триггеры 30-33, блок 34 формирователей импульсов, реверсивньй счетчик 35, с первого по четвертьй элементы ИЛИ 36-39, второй оперативный запоминающий блок 40, третий 41 и четвертый 42 счетчики, четвертьй блок 43 переключателей,первый 44 и второй 45 регистры, с первого по третий элементы 46-48 задержки, причем выход первого счетчика 15 соединен с адресным входом постоянного запоминающего блока 8, выход генератора 1 соединен с первым входом первого элемента И 25, выход которого связан с первым входом первого счетчика 15 и счетным входом реверсивного счетчика 35, второй вход первого элемента И 25 связан с выходом второ

го триггера 30, один из выходов делителя частоты соединен с первыми-входами второго, четвертого и пятого элементов И 26,28 и 29, выход второго элемента И 26 связан с первым входом третьего элемента ИЖ 38, РЫХОД реверсивного счетчика 35 подключен к управляющему входу постоянного запоминающего блока 8, первому входу первого элемента ИЛИ 36 и входу первого элемента 46, выход последнего связан с управляющим входом умножителя 9 и входом загрз зки реверсивного счетчика 35, второй выход умножителя 9 связан с первым входом второго регистра 45 и входом второго элемента 47, аыход которого связан с управляющим входом первого оперативного запоминающего блока 11 и входом третье- 20 27 элементов И и второму пходу перго элемента 48, выход последнего связан с вторым входом третьего элемента ИЛИ 38 и первым входом второго элемента ИЛИ 37, выход последнего соединен с вторым входом второго триггера 30, выход третьего элемента ИЛИ 38 соединен с вторым входом второго коммутатора 4, выход которого связан с входом второго счетчика 16, первый выход последнего соединен с адресным входом первого оперативного запоминающего блока 11, выход которого связан с входом преобразоватео1я 21 и вторым входом второго регистра 45, третий вход которого соединен с выходом первого триггера 20, выход второго регистра 45 связан с вторым входом сумматора 10, первый выход четвертого блока 43 соединен с управляющим входом третьего коммутатора 7, второй выход четвертого блока 43 связан с вторым входом второго элемента ИЛИ 37 и вторым входом первого триггера 20, третий выход четвертого блока 43 подключен к управляющему входу второго коммутатора 4, выход третьего блока 18 соединен с входом данных второго оперативного запоминающего блока 40 и входом блока 34

формирователей импульсов, выход кото- 50 входом вычислителя 24 и третьим вхо- рого подключен к входу четвертого дом третьего элемента ИЛИ 28, а выход вычислителя 24 связан с вторым входом выходного масщтабного прёобэлемента ИЛИ 39, выход последнего соединен с управляющим входом второго оперативного запоминающего блока 40, первый выход третьего коммутатора 7 связан с адресным входом .второго оперативного запоминающего блока 40 и входом данных реверсивного счетчика 35, второй выход третьего коммутато55

разователя 14,

Кроме того, генератор содержит пятый элемент ИЛИ 49, вход которого соединен с выходом второго оперативного запоминаюптег о блока 40, а выход

ра 7 соединен с вторым входом первого счетчика 15, выход второго оперативного запоминающего блока 40 подключен к второму входу умножителя 9, второй выход второго гчстчпка 16 динен с первь ми входам , первого 20 и пятого 33 триггере i nepBii -- пходо1формирователя 17, выход которого связан с входом третьего счетчика 1 , первьг 1и входами третьего триггера 31 и третьего элемента И 27 и третьим входом первого с етчлкл 15, первый выход третьего счетчика 41 соединен с BfOpbiM входом третьего коммутатора 7, второй выход третьего счетчика 41 связан с вторым входом третьего триггера 31, выход которого подключен к вторым входам второго 26 и третьего

0

вого элемента ИЛИ 36, выход которого соединен с первым иходом второт о триггера 30, выход третьего элемента И 27 связан с вторым входом четвер- 5 того триггера 32, выход последнего соединен с вторым входом четвертого . элемента И 28, выход последнего связан с входом четвертого счетчика 42, который своим выходом подключен к управляющим входам четвертого 22 и пятого 23 коммутаторов, выход преобразователя 21 соединен с первыми входами первого регистра 44 и блока 19, выход последнего соединен с третьим входом первого регистргг 44, выход преобразователя 21 также связан с входом четвертого коммутатора 22, выход которого соединен с первым входом вычислителя 24 и входом циф- роаналогового преобразователя 12, выход первого регистра 44 связан с вторым входом блока 19 и информационным входом пятого коммутатора 23, выход последнего соединен с первым входом четвертого триггера 32 и вторым входом пятого триггера 33, выход которого подключен к вторым входам вычислителя 24 и пятого элемента И 29, выход последнего связан с третьим

5

0

5

разователя 14,

Кроме того, генератор содержит пятый элемент ИЛИ 49, вход которого соединен с выходом второго оперативного запоминаюптег о блока 40, а выход

связан с вторым входом формирователя 17е

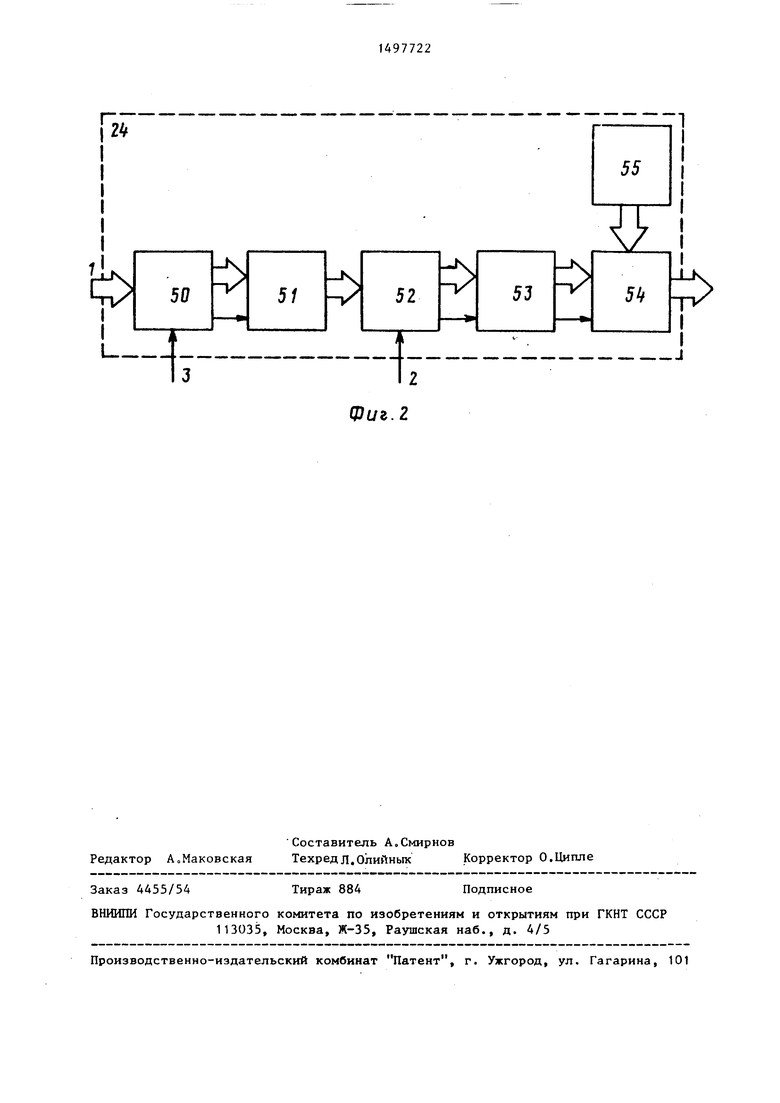

Вычислитель 24 (фигс2) содержит квадратор 50, накапливающий сумматор 51, блок 52 извлечений корня, делитель 53, умножитель 54 и задатчик 55 кода, причем вход квадратора 50 является первьм входом вычислителя 24, а выходы подключены к входам накапливающего сумматора 51, выход которого через блок 52 и делитель 53 связан с первым входом умножителя 54, второй вход которого подключен к выходу задатчика 55, а выход является выходом вычислителя 24 Входы управления блока 52 и квадратора.50 являются соответственно вторым и третьим входами вычислителя 24.

Умножители 9 и 54, квадратор 50 и делитель 53 реализованы на БИС умножителях типа КР1802ВР2о Выходной масштабньм преобразователь 14 может быть выполнен в виде перемножающего цнфроаналогового преобразователя, формирователь 17 - в виде одновибра- тора с несколькими равноправными входами запуска, например К15 АГЗ,, Блок 34 формирователей импульсов представляет собой набор отдельных формиро- вателей импульсов, входы которых соединены с выходами третьего блока 18, а выходы - с входами четвертого элемента ИЛИ 39.

Блок 52 реализован по схеме, предложенной в

Сущность изобретения заключается в том, что алгоритм з формирования сложного сигнала путем сложения огра- ниченн зго числа гармонических состав- ЛЯЮ1ТЦ1Х с задаваемыми амплитудами заменен на алгоритм формирования сложного сигнала по формуле

F(t) AnsinCnw t + (fu) , (1)

-номер гармоники,

-число суммируемых гармоник,

-частота.

где п

N U

АП

U - амплитуда и фаза соответст- п

венно п гармоники о

Алгоритм работы устройства-прототипа позволяет формировать только периодические сигналы, обладающие cвoйcтвa a симметрии первого или вто рого рода о

Алгоритм работы предлагаемого устройства позволяет сформировать перио

10

15

20

о25

35

40

45

50

55

дический сигнал любой формы со спектром не шире чем Nw,

Обобщенный алгоритм раббты генератора заключается в следующемсНа первом этапе работы в генератор вводится информация об амплитудах и фазах гармоник. В генераторе реализовано формирование сложного сигнала по формуле

N

F(t) Zl((nw t)(na; t) , (2)

аналогичной формуле (1) при

и tgLp --„

bn

После ввода соответствующих коэффициентов а,, и Ь начинается этап формирования сложного сигнала по формуле (2)о Этот этап состоит из трех основных частей: собственно синтез сложного сигнал,, по формуле (2), нормирование полученного цифрового сигнала по амплитуде и автоматическая установка коэффициента передачи масштабного преобразователя в зависимости от требуемого среднеквадратическо- го значения сформированного сигнала на выходе генератора с учетом амплитуды и формы синтезированного сигнала. На третьем этапе синтезированный цифровой сигнал выдается на выход ;енератора через цифроаналоговый преобразователь, фильтр нижних частот и масштабный преобразователь с заданной частотой.

Рассмотрим работу устройства Перед началом работы обнуляются накапливаюштий сумматор 51, счетчики 16,35,41 и 42, триггеры 31 - 33 и первый регистр 44 При этом первый счетчик 1j устанавливается в состояние единицы (все разряды, кроме двух старших, которые устанавливаются в состояние логического нуля путем записи соответствующей кодовой комбинации по входу параллельной записи) Работа генератора начинается с ввода коэ(|)фициентов разложения ряда Фурье а и Для этого четвертьй блок 43 переключателей устанавливается в положение ввод, при этом управляющий сигнад с его первого выхода поступает на управляюищй вход третьего коммутатора 7, который соединяет выход второго блока 6 с входом данных реверсивного счетчика 35 (кроме младшего разряда) и с адресным входом второго оперативного запоминающего блока (все разряды)40. Младший разряд выходного кода второго блока 6 подается с второго выхода третьего коммутатора 7 на второй вход первого счетчика 15, Выходной код второго блока 6 переключателей определяет вводимый коэффициент разложения, причем младший разряд, равный нулю, определяет ввод коэффициентов , 1(, ri равный единице - коэффи циентов bf, . Остальные разряды кода определяют номер гармоники п, при этом коду нуль соответстпует первая, коду один - вторая, коду два - третья гармоника и т.До

Значение вводимого коэффициента задается третьим блоком 18 и с его выхода подается на вход данных второго оперативного запоминающего блока 40 и вход блока 34 формирователей импульсов При изменении состояния любого разряда выходного кода третье

го блока 18 блок ЗД формирователей импульсов вырабатывает сигнал, который через четвертый элемент ИЛИ 39 подается на управляющий вход второго оперативного злпоми 1. 40 Этим обеспечивается яапись во второй оперативный запоминающий блок 40 требуемого значения коэффициента разложения ряда Фурье а или b „-.

После окончания ввода всех требуемых коэффициентов разложения ряда Фурье четвертый блок 43 устанавливают в положение Синтез, при этом па-втором выходе четвертого блока 43 формируется сигнал Синтез, который устанавливает в состояние Лог.1 первый и второй (через второй элемен ИЛИ 37) триггеры 20 и 30. При переходе к режиму Синтез с первого выхода четвертого блока 43 снимается сигнал Ввод, по заднему фронту которого третий коммутатор 7 соединяет выход третьего счетчика 41 с входами реверсивного счетчика 35, второго оперативного запоминающего блока 40 и первого счетчика 15о Выходной сигнал ЛоГо1 первого триггера 20 обнуляет второй регистр 45, при этом . выходной код сумматора 10 соответствует выходному коду умножителя 9 и не зависит от содержимого первого оперативного запоминающего блока 11 о Выходной сигнал второго триггера 30 разрешает прохождение импульсов с выхода генератора 1 импульсов через

0

5

0

5

0

5

д

5

0

5

первый элемент И 25 на nepubii i (с;мот- Hbtfi) вход первого счетчика 15 и на счетньи вход (вычитания) рснсрсипно- го счетчика 35. лмпуч с . ;ip - шедший через псрвьл ; э.кмеит , i 23, устанавливает первый счетчик 15 в состояние Все нули (кроме второго разряда) и формирует сигнал на выходе переноса реверсивного счетчика 35, по которому разрешается иьшача данных из постоянного запоминающего блока 8 по адресу, определяемому состоянием первого счетчика 15, ira первый вход умножителя 9. Выходной сигнал, реверсивного счетчика 35 также обнуляет второй триггер 30 (через первьпЧ элемент ИЛИ 36), запрещая прохождение импульсов через первый элемент И 25, и запускает первый г лемент 46 задержкио

Выходной сигнал первого элемента

46поступает на управляю1ций вход умножителя 9, разрешая умножение выходного кода постоянного запоминающего блока 8 на коэффициент а, поступающий на второй вход умножителя 9 с выхода-второго оперативного запоминающего блока 40о Выходной сигнал первого элемента 46 также поступас- т на вход загрузки реверсивного счетчика 35, при этом в последний записывается номер синтезируемой гармоники, определяемой состоянием счетчика 41 о

По окончании операции умножения умножитель 9 выдает произведение на первый вход сумматора 10 и формирует на своем втором выходе сигнал готовности, который через второй элемент

47задержки поступает на управляющий вход первого оперативного запоминающего блока 11 о По этому сигналу данные с выхода сумматора 10 записываются в первый оперативньп1 запоминающий блок 11. Второй регистр 45 обнуляется выходным сигналом первого триггера 20, поэтому сигнал готовности умножителя 9 не изменяет его состояния

Выходной сигнал второго элемента 47 запускает третий элемент 48 задержки, выходной сигнал последнего поступает на первый вход второго элемента ИЛИ 37 и второй вход третьего элемента ИЛИ 38 Через третий элемент ИЛИ 38 и второй коммутатор 4 этот сигнал поступает на счетный вход второго счетчика 16, который устанавливает на адресном входе первого onepcJTHBHoro запоминающего блока 1 1 а,п,рес с.г1едую1цей ячейки, Через лторой -злсмелт ИЛИ 37 выходной сигнал третьего элемента 48 задержки подается на второй вход второго триггера 30, устанавливая последний в состояние Лог, .

В результате выполненных операций в первой ячейке первого оперативного гзапоминающего блока 1 1 сформировано значение первой ординаты косинусои- дальной составляюп1ей первой гармоники а,. Далее описанная последовательность операций повторяется циклически до заполнения первого оперативного запоминающего блока 11 одним периодом косинусоидалыюй составляющей первой гармоники и появления на втором выходе (переноса) второго счетчика )6 сигнала переполнения, обнуляющего первыГ 20 и пятьй 33 триггеры и запускающего формирователь 17о Обнуление первого триггера 20 прекращает обнуление втордго регистра 45с Выходной сигнал формирователя 17 обнуляет третий триггер 31 и увеличивает на единицу содержимое третьего счетчика 41, при этом происходит обращение к следующей ячейке второго оперативного запоминающего блока 40 и на второй вход умножителя 9 из второго oneparHBHoi o запоминающего блока 40 выдается значение следующего коэффициента разложения рида Фурье (Ь)с

По заднему фронту выходного сигнала формирователя 17 импульсов в первый счетчик 15 записьшается информация по параллельному входу, причем два старщих разряда записываемого кода равны значению младщего разряда выходного кода третьего счетчика 41, а остальные равны логической единице с Эт1м обеспечивается опрос постоянного запоминающего блока 8 с нулевого адреса при формировании синуса и с адреса, равного одной чет- перти адресного пространства, при формирорашп косинуса с

Далее описанный вьпие процесс синтеза гармонических составляющих повторяется 1щклически до окончания синтеза всех членов ряда Фурье и появления на втором выходе третьего счетчика 41 сигнала переноса. Однако вновь синтезируемые гармонические составляю11и1е суммируются с предыдущими и результат накапливается в пер0

5

0

5

0

5

0

5

0

5

вом оперативном запоминающем блоке 11 с Это достигается записью во второй регистр 45 содержимого первого оперативного запоминающего блока 11 и выдачей этого содержимого на второй вход сумматора 10 но сиг)1алу готовности умножителя 9„

По окончании синтеза всех гармонических составляющих на втором выходе третьего счетчика 41 появляется сигнал переноса, устанавливающий третий триггер 31 в состояние Лог 1 Этим начинается процедура нормирования синтезированного сигнала по амплитуде „ Выходной сигнал третьего триггера 31 через первый элемент ИПИ 36 обнуляет триггер 30 и разрешает прохождение сигналов с выхода формирователя 17 импульсов через третий элемент И 27 и с одного из выходов делителя 2 частоты через второй элемент И 26, Первый вход второго элемента И 26 подключен к тому выходу делителя 2, интервал между импульсами частоты на котором достаточен для выполнения описанных ниже операций

Импульсы частот1)1 с выхода элемен- та И 26 поступают через третий эле-, мент ИЛИ 38 и кторсй коммутатор 4 на счетный вход второго счетчика 16, который начинает последовательно опра- мивать ячейки первого оперативного запоминающего блока 11е

Содержимое ячеек первого оперативного запоминающего блока 11 через преобразователь 21, осуществляющий преобразование обратного кода в прямой, поступает (без знаково1 о разряда) на первые входы блока 19 и первого регистра 44„ На второй вход блока 19 подается содержимое первого регистра 44. Если код на первом входе блока 19 больше кода на его втором входе, то выходной сигнал блока 19 разрешает запись больщего кода в первый регистр 44 по заднему фронту выходного сигнала второго элемента И 26 Описанный процесс повторяется с приходом-следующего импульса частоты с выхода второго элемента И 26 до тех пор, пока не будут опрошены все ячейки первого оперативного запоминающего блока 11. При этом в первом регистре 44 окажется записанным симальный по модулю код, имеющийся в первом оперативном запоминающем блоке 11. После опроса всех ячеек последнего на втором выходе второго

счетчика 16 появится сигнал переноса, запускающий формирователь 17. Его выходной сигнал подается на первый вход третьего элемента И 27 и обнуляет третий триггер 31, запрещая прохождение импульсов частоты через второй элемент И 26. При этом на выходе третьего элемента И 27 формируется короткий импульс, устанавливающий четвертый триггер 32 в состояние ЛоГо1 о Этот сигнал раэрещает прохождение импульсов частоты через четвертый элемент И 28 на счетньп вход четвертого счетчика 42с, Под воз действием выходного сигнала последнего ,i iTbrii коммутатор 23 начинает последовательно коммутировать на свой выход разряд) кода, написанного в первом регистре 44, начиная со старшего разряда. Процесс повторяется до обнаружения разряда, равного Лог.1, т„е„ до появления сигнала Лого1 на выходе пятого коммутатора 23, по которому устанавливается в состояние Лог. пятый триггер 33 и обнуляется четвертьгй триггер 32, запрещая прохождение импульсов частоты через четверть элемент И 28i, Четвертьи коммутат.ф 22 уста 1аили- вается выходным сигналом четвертого счетчика 42 в состояние, обеспечивающее сдвиг всех разрядов кодов, поступающих на четвертый коммутатор 22 с выхода преобразователя 21 кода, на число разрядов, равное количеству импульсов, пришедигих на счетный вход четвертого счетчика 42 При этом среди кодов, поступающих с выхода четвертого коммутатора 22 на вход цифроаналогового преобразователя 12, найдется хотя бы один, имеющий значение старщего разряда, равное логической 1 о Этим обеспечивается- полное использование разрядной сетки цифро- аналогового преобразователя 12о

Выходной сигнал пятого триггера 33 разрещает прохождение импульсов ча.стоты с выхода делителя 2 через пятый элемент И 29 на третий вход вычислителя 24 и через третий элемен ИЛИ 38 и второй коммутатор 4 на счетный вход второго счетчика 16, который начинает опрашивать первый опе- ративньш запоминающий блок 11. Выходные коды последнего через преобразователь 21 и четвертый коммутатор 22 поступают на вход квадратора 50, являющегося первым входом вычислите

ля 24. По заднему фронту импульса частоты, поступающего на TIXO;;, упрпр- леиия квадратора SO с выход;; питого члемеш а И 29, кходнсм кпп .т1Ч - ра возводится к 1а а;;рл- и к ту.мьтлт записывается в накапливакмний сумматор 51, причем данные I поступ 1 ;|.ие с первого выхода квадратора 50 на первьпч вход накапливающего сумматора 5,1 , сопровождаются сигналом готовности, вырабатываемУ:.1М квадратором 50 и поступающим с его второго выхода на второй вход накапливающего сумматора 51 „

0

5

5

После опроса всех ячеек первого оперативного запоминающего блока 11 сигнал псревб са с выхода второго счетчика 16 обнуляет пятый триггер 33. При этом задним фронтом выходного сигнала последнего запускается блок 52, вход управления которого является вторым входом вычислителя 24, Выходной код блока 52, равный квадратному корню из суммы квадратов кодов, поступающих на первый вход вычислителя 24, выдается с первого выхода блока 52 на первый вход делителя 53 и сопровождается сигналом готовности, вырабатываемым блоком 52 и поступающим с его второго выхода на вход управления делителя 53с, Последний под воздействием сигнала готовности делит код, равный квадратному корню из числа ячеек первого оперативного запоминающего блока 11, на выходной код блока 52 и выдает результат со своего первого выхода на первый вход умножителя 54, который по сигналу готовности, вырабатываемому делителем 53 и поступающему с его второго выхода на вход управле- ния умножителя 54, умножает этот код 5 па выходной код задатчика 55, которым устанавливается требуемое средне- квадратическое значение выход}1ого сигнала генератора. В результате выполненных операций на выходе вычислителя 24 появляется код N jnj( , равньв

/К

ZN 1-.

0

5

0

0

NBHX скэ

(3)

55 или

вш Nck

П i

(4)

где N(-, - иыходнон код задатчикаЗЗ К - число ячеек первого оперативного запоминающего блока 1 1 ,

N. - код, поступающий на пер- BbDi вход вычислителя 24 и ячейки первого оперативного запоминающего блока 11 с номером j о

Выражение в знаменателе дроби (4) Представляет собой вычисленное в цифровом В1оде среднеквадратическое значение синтезированного сигнала с учетом его амплитудного нормирования о Выходной код вычислителя 24 подается на второй вход выходного масштабного преобразователя 14с

После выполнения описанных операций четвертьш блок 43 устанавливают в положение Вывод „ При этом снимается сигнал с его второго выхода и на третьем выходе четвертого блока 43 устанавливается сигнал Вывод, по которому второй коммутатор 4 соединяет счетньп вход второго счетчика 16 с выходом первого коммутатора 3. Последний коммутирует на свой выход один из выходных сигналов делителя 2 в соответствии с кодом, по- ступаюпшм с выхода первого блока 5 на управляющий вход первого коммутатора 1 о Этот код определяет частоту выходного сигнала генератора Возможен выбор одного значения частоты из множества, определяемого количеством выходов делителя 2. частоты Коэс{х1)ициент деления частоты для каждого из выходов последнг-го различный о

Второй счетчик 16 периодически опрашивает ячейки первого оперативного запогминающего блока 11 Выходные коды последнего через преобразователь 21 и четвертый коммутатор 22 подаются на вход цифроаналогового преобразователя 12, выходной сигнал которого через фильтр 13 и выходной масштабньш преобразователь 14 поступает га выход генератора Учитывая, что коэффициент передачи выходного масштабного преобразователя 14 определяется выходным кодом вычислителя 24 и что этот код обратно пропорционален среднеквадратическрму значению выходного сигнала цифроаналогово I o преобразователя 12, среднежвадра- тическое значение выходного сигнала генератора определяется только кодом

0

5

0

5

0

5

задаваемым задатчиком 55, и не зависит от вида синтезированного сигнал а

Таким образом, описанньй генератор формирует периодические сигналы произвольной формы, задаваемые ограниченным рядом Фурье (2) и нормированные по уровню среднеквадратичес- кого значения

Введенный с целью уменьшения времени синтеза заданного сигнала пятьпЧ элемент ИЛИ 49 обеспечивает следующий режим.

Если в режиме синтеза происходит обращение к ячейке второго оперативного запоминающего блока 40, содержащей нулевой код, т се к нулевому коэффициенту разложения а; или Oj, то нулевой сигнал с выхода второго оперативного запо шнающе1 о блока 40 через пятый элемент ИЛИ 49 поступает на второй вход фор -мрбвателя 17 импульсов При этом последний формирует сигнал, изменяющир состояние третьего счетчика 41 на единицу Если следующий коэффициент разложения равен нулю, процесс повторяется. Если значение следующей ячейки второго оперативного запоминающего 40 отлично от нуля, начинается процесс синтеза соответствующей гармоники, описанный выше„

Так, для синтеза одной гармонической составляющей требуется время t, которое можно представить суммой времени l, и

4

(5)

где

время, необходимое для работы реверсивного счетчика

гармоники;

время работы остальных узлов генератора при синтезе гармоники с,

Время синтеза одной гармоники t составляет

Ч

п 4 +

,

(6)

где п - номер гармоники,

и - время работы реверсивного

счётчика 35 при синтезе первой гармоники

Таким образом, суммарное время работы генератора в режиме синтеза TC можно представить:

2p

2 у n J +

П; I

3

(7)

где p - максимальное число синтезируемых гармоник,

- время, необходимое для операций амплитудного fcopMnpo- вания и вычисления кода

NBMX

Масштабный коэффициент 2 перед р появляется за счет того, что каждая гармоника представлена синусной и косинусной составляющими, синтезируемыми независимое При введении в генератор пятого элемента ИЛИ 49 формула (7) примет вид:

,+(2p-p )1} +2 с/пл+Гз, (8)

h f

-1 М

где р - число отличных от нуля коэффициентов разложения, время анализа нуля коэффициента, причем .; о, , d - коэффициент, равный 1 (есл гармоническая составляющая не равна нулю) или О (если гармоническая составляющая равна нулю)

Из анализа формул (7) и (8) следует, что ускорение синтеза пропорционально числу нулевых коэффициентов разложения.

Таким образом, предлагаемое устройство позволяет формировать калиброванные по уровню среднеквадрати- ческого значения периодические сигналы произвольной формы с ограниченным и заданным спектром инфразвуко- вых частот, необходимые при поверке и аттестации измерительных приборов инфразвуковых частот, а также при Проведении научных исследований

Введенные в устройство элементы и их связи позволяют формировать сигналы сложной формы за малое время, что позволяет оперативно менять форму выходного сигнала генератора, что особенно важно при проведении автоматических испытаний серийной продукции„

Формула изобретени

1g Генератор периодических колебаний инфразвуковых частот с автоматической калибровкой, содержащий последовательно соединенные генератор импульсов, делитель частоты, первый и второй коммутаторы, а так-

0

5

0

5

же первый блок переклычателей, выход которого соединен с упрг1вляк; цим входом периого коммутаторп, второй блок перекпючателей, иыхсл KO i oiioro подключен к первому ь., чу riicro коммутатора, последоватьiiiiHO соединенные постоянный запоминающий блс),-, умножитель, сумматор и иервьм гпс ра- тивный запоминающий (.-лок, псследова- т.ельно соединенные 1у1фроаналоговьп1 преобразователь, фипьтр нижних частот и выходной масын-абньш преобразователь, причем ьыход последнего является выходом устройства, а также первый и второй счетчики, формирователь импульсов, третий блок переключателей, блок сравнения и первьш триггер, о т л и ч а ю щ и и с я тем, что, с целью расширения класса формируемых сигналов, в него введены преобразователь кода, четвертый и пятый коммутаторы, вычислитель, с первого по пятый элементы И, с второго по пятый триггеры, блок формирователей импульсов, реверсивный счетчик, .с первого по четвертый элементы ИЛИ, второй оперативный запоминающий блок, третий и четвертьй счетчи- 0 ки, четвертый блок перекпючателей, первый и второй регистры, первьй, второй и третий элементы задержки, причем выход первого счетчика соединен с адресным входом постоянного запоминающего блока, выход генератора импульсов соединен с первым входом первого элемента И, выход которого соединен с первым входом первого счетчика и счетным входом реверсивного счетчика, второй вход первого элемента И соединен с выходом второго триггера, выход одного из разрядов делителя частоты соединен с первыми входами второго, четвертого и пятого элементов И, выход второго элемента И соединен с первым входом третьего элемента ИЛИ и вторым входом первого регистра, выход реверсивного счетчика подключен к управляющему входу постоянного запоминающего блока, первому входу первого элемента ИЛИ и входу первого элемента задержки, выход которого соединен с управляющим входом умножителя и входом загрузки реверсивного счетчика, второй выход умножителя соединен с -первым входом второго регистра и входом второго элемента за:1,ержки, выход которого соединен с управляюишм вхо5

0

5

0

5

дом первого оперативного запоминающего блока и ИХОДОМ третьего элемента задержки, выход которого соединен с вторым входом третьего элемента ИЛИ и первым входом второго элемента ИЛИ, выход третьего элемента ИЛИ соединен с вторым входом второго коммутатора, выход которого соединен с входом второго счетчика, первый выход которого соединен с адресным входом первого оперативного запоминающего блока, выход которого соединен с входом преобразователя кода и с вторым входом второго регистра, третий вход которого соединен с выходом первого триггера, выход второго регистра соединен с вторым входом сумматора, при этом первый выход четвертого переключателей соединен с управляющим входом третьего коммутатора, второй выход - с вторым входом второго элемента ИЛИ и третий выход подключен к управляющему входу второго коммутатора, выход третьего блока переключателей соединен с входом данных второго оперативного запом1нающего блока и входом блока формирователей импульсов, выход которого подключен поразрядно к входу четвертого элемента ИЛИ, РЫХОД которого соединен с управляющим входом второго оперативного запоминающего блока, первый выход третьего коммутатора соединен с адреснЕ)1м входом второго оперативного запоминающего блока и входом данных реверсивного с гетчика, второй выход третьего коммутатора соединен с вторьм входом первого счетчика, выход второго опе- ративн.тго запоминающего блока подключен к второму входу умножителя, второй выход второго счетчика соединен с первыми входами первого и пятого триггеров и первым входом формирователя импульсов, выход которого соедине) с входом третьего счетчика, первыми входами третьего триггера и третьего элемента И и третьим входом первого счетчика, второй вход первого триггера соединен с вторым выходом четвертого блока переключателей, первый выход третьего счетчика сое0

5

0

5

0

5

0

5

0

динен с вторым входом третьего коммутатора, второй выход третьего счетчика соединен с вторым входом третьего триггера, выход которого подключен к вторым входам второго и третьего элементов Ник второму входу первого элемента ИЛИ, выход которого соединен с первым входом второго триггера, второй вход которого соединен с выходом второго элемента ИЛИ, выход четвертого триггера соединен с вторым входом четвертого элемента И, выход которого соединен с входом четвертого счетчика, выход которого подключен к упрапля- ющ1{м входам четвертого и пятого коммутаторов, выход преобразователя кода соединен с первыми входами первого регистра и блока сравнения, второй вход первого регистра соединен с выходом второго элемента И, а третий BXOjt - с выходом блока сравнения, выход преобразователя кода также соединен с входом четвертого коммутатора, выход которого С1)единен с первым входом вычислителя и входом циф- роаналогового преобразователя, выход первого регистра соединен с вторым входом блока сравнения и информаци- онныу.1 входом пятого коммутатора, выход которого соединен с первым вхо- цом четвертого триггера и вторым входом пятого триггера, второй вход четвертого триггера соединен с выходом третьего элемента И, а выход пятого триггера подключен к вторым входам вычислителя и пятого элемента И, выход которого соединен с тре- тьим входом вычислителя и третьим входом третьего элемента ИЛИ, а выход вычислителя соединен с вторьи - входом выходного масштаб ого преобразователя

Фиг. г

Составитель А.Смирнов Редактор А«Маковская Техред л.Олийнык Корректор О.Ципле

Заказ 4455/54

Тираж 884

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписное

| Беляков С.Ас, Чураков П,П | |||

| Функциональный генератор сигналов инфра- ниэкочастогного диапазона | |||

| - Приборы и техника эксперимента, 1985, № 2, Со142-145 | |||

| Устройство для вычисления квадратного корня | 1982 |

|

SU1103226A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой генератор периодических колебаний инфранизких частот | 1980 |

|

SU970631A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-07-30—Публикация

1987-06-15—Подача