Изобретение относится к технике статистических измерений случайных процессов.

Предлагаемый многоканальный цифровой коррелятор предназначен для вычисления оценок корреляционной и взаимокорреляционной функции реализаций центрированных станционарных на интервале наблюдения нроцессов в соответствии с алгоритмами

К, (IT,} V (liTMkT, - IT,) ftTo

(/Го) : -J- S ) - TO), Л k.u

где Л - объем выборки; (То - интервал задержки; , п - число анализируемых точек; Т -и /о -частота квантования вход/0

о

ных сигналов д:(/) и ij(f)

x(kT,), ), x(,)- y(kT,-iT - дискреты реализаций центрированных процессов x(t) и y(t) в моменты времени АГо и /гГо - гГоков. Последние обстоятельства значительно снижают коэффициент готовности устройства и стало быть уменьшают надежность аппаратуры в целом. Кроме того, устройству свойственно низкое быстродействие.

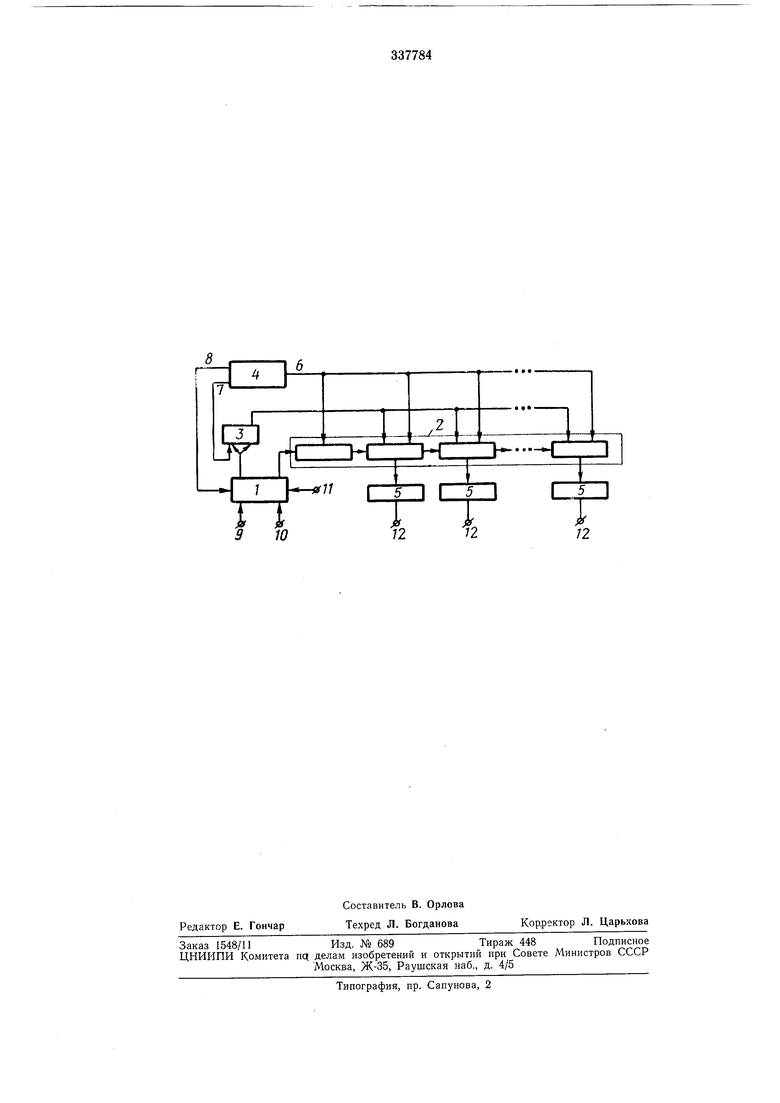

На чертеже приведена блок-схема предлагаемого цифрового многоканального коррелятора. Устройство содержит двухканальный время-имлульсный преобразователь типа аналогкод /, последовательно подключенный (rt+l)-каскадный регистр сдвига 2, триггер .7, синхронизатор 4 п накопителей 5. Каждый каскад регистра 2 состоит из ш+2 разрядов. Накопители 5 состоят из последовательно подключенных разрядного накапливающего сумматора со сквозным переносом и (/-2) разрядного двоичного счетчика (/ выбирается из условия N 2), причем

входы /п-|--2 младших разрядов накопителей 5 связаны с соответствующими выходами прямого кода регистров 2. Каждый накопитель 5 снабжен триггером знака, единичным выходом связанным с входом младшего разряда наконителя (указанные триггеры и их соответствующие связи на чертеже не отражены). Правый информационный выход преобразователя / подключен ко входу второго разряда первого аскада регистра 2, а левый

триггера 3, единичный выход которого связан с шиной опроса регистра 2, кроме первого каскада. Выход 6 синхронизатора 4 подключен к шине сдвига регистра 2, а выходы 7 и 8 связаны соответственно с входом установки пуля триггера 5 и с управляющим входом преобразователя /. В регистре 2 сдвиг двоичного кода осуществляется в правую сторону младшп1 разрядом. Первый (левый) каскад регистра 2 кроме сдвига кода должен осуществлять также прео.бразование числа, представленного в унитарном коде (последовательностью импульсов), в двоичный код. На входные клеммы 9 п 10, являющиеся информационными входами преобразователя /, соответственно подаются входные процессы

Сс

x(t) и y(t), а на входную клемму 11 подается смещение , равное максимальной отрицательной амплитуде входных сигналов. выходных клемм 12 каждого накопителя соответственно подключены к выходам прямого кода накопителей 5.

В исходном состоянии Ь(я-(-1) каскадах регистра 2 зафиксирован код нуля, триггер 3 находится в пулевом положении, в каждом из п накопителей 5 зафиксирован двоичный код

числа - NEcM

В предлагаемом устройстве процесс онределепия я точек корреляционной функции ССуществляется за /V циклов.

С )ачалом первого цикла анализа на выходе 7 сипхроппзатора 4 появляется импульс, который поступает на управляющий вход преобразователя 1 и дает команду на нреобраоо

зование сигналов л:(г) и /(() . На правом и левом выходах преобразователя / соответственно появляются две последовательности импульсов, число которых в первой последовательности соответствует дискрете

оО

x(kTo}+ЕСГ.Ь а , во второй-дискрете (/(Го). Последовательность имнульсов, соответствующая дискрете г/() преобразуется в первом каскаде регистра 2 в двоичпый код, а последовательность импульсов, соответствующая дискрете x(kTo),i, поступает на счетный вход триггера 3, в результате на единичном выходе триггера ноявx(kTo) + см

ляются импульсы, производящие

Zi

кратный опрос п старших каскадов регистра 2. После окончания обеих носледовательпостей на выходе 6 синхронизатора 4 появляется один импульс, который осуществляет

сдвиг кодов во всех каскадах регистра 2 вправо на один разряд. Далее на выходе 7 синхронизатора 4 появляется импульс, производящий установку нуля триггера . При этом если число импульсов в последовательности, соответствующей ординате х()гТ было нечетным, то на единичном выходе триггера 5 формируется импульс, осуществляющий дополнительную перепись кодов из п старших каскадов регистра 2 в младщих разрядов соответствующих накопителей 5. Если же число импульсов в последовательности было четным, то дополнительной перезаписи кодов из регистров 2 в накопители не производится.

После установки нуля триггера 5 на выходе б синхронизатора 4 появляются /п-|-1 импульсов, которые произведут перезапись кодов

чисел из каждого предыдущего каскада в последующий каскад регистра 2. При этом первый каскад регистра 2 полностью освобождается. Па этом завершается никл работы устройства. Последующий цикл анализа

осуществляется в иоследовательности, описанной выше.

Пз описания приннипа работы предлагаемого коррелятора видно, что в каждом цикле анализа нет необходимости отводить спецпальное время для производства п умножений. Эти умножения осуществляются автоматически одновременно с процессом преобразования ордипат и завершаются с окончанием преобразований.

Предмет изобретения

Многоканальный цифровой коррелятор, содержащий синхронизатор, многокаскадный

сдвиговый регистр, накопители, времяимпульсный преобразователь типа аналог-код, первый выход которого подключен ко входу первого каскада сдвигового регистра, а вход - к первому выходу синхронизатора, огличающийся тем, что, с целью новыщения быстродействия и упрощепия устройства, он содержит триггер, счетный вход которого соединен со вторым выходом время-импульсного преобразователя, а единичный выход-с шиной опроса каскадов, кроме нервого, сдвигового регистра, выходы опращиваемых каскадов нодключены ко входам соответствующих накопителей, а сдвиговая шина регистра связана со вторым выходом синхронизатора,

третий выход которого соединен с нулевым входом триггера.

f Т

/О

L:

Г5-| Г5

1

72

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ КОРРЕЛЯТОР | 1973 |

|

SU387370A1 |

| МНОГОКАНАЛЬНЫЙ ИНФРАНИЖОЧАСТОТНЫЙ ЦИФРОВШ КОРРЕЛЯТОР | 1972 |

|

SU433486A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| Многоканальное устройство дляВычиСлЕНия СТРуКТуРНОй фуНКции | 1977 |

|

SU840924A1 |

| ЦИФРОВОЕ УСТРОЙСТВО для ОПРЕДЕЛЕНИЯ ДИСПЕРСИИ ОРДИНАТ СЛУЧАЙНЫХ ПРОЦЕССОВ | 1973 |

|

SU369573A1 |

| Устройство для передачи измерительной информации | 1982 |

|

SU1062753A1 |

| ЦИФРОВОЙ КОРРЕЛЯТОР | 1970 |

|

SU275542A1 |

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

| Устройство определения местоположения подвижного транспортного средства | 1985 |

|

SU1310871A1 |

Авторы

Даты

1972-01-01—Публикация