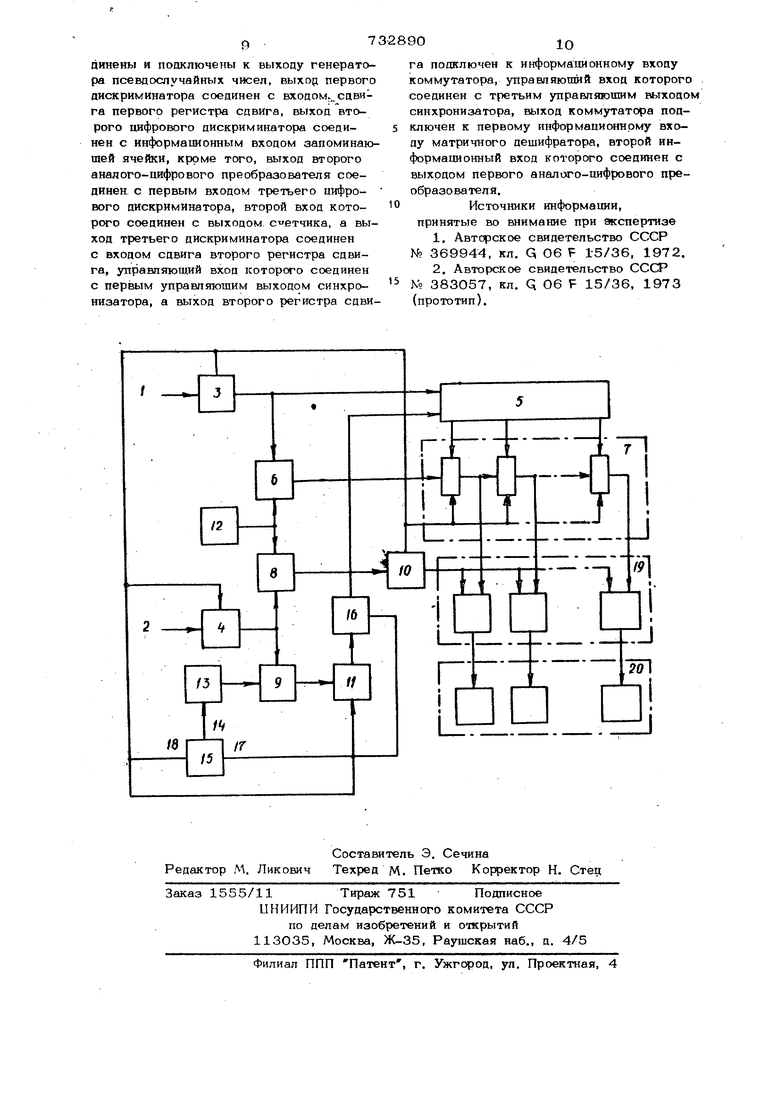

Изобретение относится к вычислительной и измерительной технике и может использЬватъся для анализа случайных т1роцессов. Известные статистические анализаторы случайных процессов с непосредственным вводом данных вычисляют или только знаковую корреляционную функцию, или только функцию распределений IJ . В известном статистическом анализаторе, содержащем два аналого-цифровых преобразователя, синхронизатор, регистр сдвиг два дешифратора, пересчетную схему, умн житель, четыре коммутатора и две группы накопителей, находятся оценки автои корреляционных Функций, одномерных и двумерных законов распределения. Однако большое количество оборудования и последовательное вычисление кор реляционных функций случайных сигналов снижает быстродействие устройства. Наиболее близким к изобретению по техническому решению является статисти ческий анализатор, содержащий синхровизатор, связанный первым выходом с управляющими входами запоминающей ячейки и регистра сдвига, поразрядно соеди- ненного по выходам с соответствующими дешифраторами соответствия, вторые входы которых подключены к выходу запоминаюшей ячейки, а выходы - к накопителям первой группы, и в каждом из двух каналов двоичный счетчик, связанный по выходам с дешифрирующей матрицей и цифроаналоговым преобразователем, выход которого подключен к сумматору, соединенного по выходу с первым и вторым огр аничитёлями, выходы которых подключены к схеме совпадения с триггерным выходом, соединенной по выходу с первым неподвижным контактом переключателя, второй неподвижный контакт которого подключен к выходу первого ограничителя, а подвижный контакт - ко входу запоминающей ячейки канала, связанной своими выходами со входом регистра сдвига и с первыми входами элементов И, вторые входы которых соединены с выходами дешиф- рирующей матрицы,а выходы - с сх ответствуюшими накопителями данного ка нала, ут1равл5пошиё входы ячейки и двоичного счетчика первого канала подключены ко второму выходу синхронизатора, треть им выходом соединенного с двоичным сче чиком и запоминающей ячейкой второго канала, и кроме того, выход запоминающей ячейки второго канала соединен с пе первым неподвижным контактом третьего переключателя, остальные неподвижные контакты которого подключены к соответствующим выходам регистра сдвига, а подвижный контакт соединен с третьими входами элементов И второго канала 2 , Недостатки данного анализатора большое количество оборудования и последовательный метод определения законов распределения, что снижает быстродействие устройству. Цель данного изобретения -сокращение оборудования и повышение быстродействия анализатора при вычислении оце нок законов распределения случайных пр цессов. Цель достигается тем, что он дополнительно содержит три цифровых дискриминатора, генератор псевдослучайных чисел, коммутатор, второй регистр сдвига и два аналого-цифровых преобразователя, информационные вхэды которых являются соответствующими входами ана лизатора, а управляющие подключены к первому управляющему входу синхронизатора, выходы аналого-цифровых преобразователей подключены к первому входу соответственно первого и второго цифровых дискриминаторов, вторые входы которых объединены и подключены к выходу генератора псевдослучайных чисел, выход первого дискриминатора соединен входом сдвиг;а первого регистра сдвига ;у выход второго цифрового дискриминатора соединен с информационным входом запоминающей ячейки, кроме того, выход второто аналого-цифрового преобразователя соединен с первым входом третьего цифрового дискриминатора, второй вхо которого соединен с выходом счетчика, выход третьего дискриминатора соединен с входом сдвига второго регистра сдЬига, управляющий вход которого соед нен с первым, управляющим выходом син хронизатора, а выход второго регистра сдвига подключен к информационному (рходу коммутатора, управляющий вход ко торого соединен с третьим управляющим выходом синхронизатора, выход коммутатора подключен к первому информационному входу матричного дешифратора, второй информационный вход которого соединен с выходом первого аналого-цифрового преобразователя. На чертеже приведена структурная схема многоканального статистического анализатора. Входы 1 и 2 анализатора являются входами аналого-цифровых преобразователей 3 и 4. Выход первого аналогоцифрового преобразователя 3 подключен к первым входам матричного дешифратора 5 и первого цифрового дискриминатора 6, выход которого соединен с входом первой го регистра 7 сдвига. Выход второго аналого-цифрового, преобразователя подключен к первым входам второго и третьего цифровых дискриминаторов 8 и 9, выходы которых подключены соответственно KD входу запоминающей ячейки 10 и ко входу втфого регистра 11 сдвига. Ко вторым входам первого и второго дискриминаторов 6 и 8 подключен выход генератора 12 псевдослучайных чисел, Ко второму входу третьего дискримина,тора 9 подключен выход счетчика 1.3, вход которого соединен с выходом 14 синхронизатора 15. Второй вход матричного дешифратора 5 подключен к выходу второго регистра 11 сдвига через коммутатор 16, управляющий вход которого соединен с - Третьим-j- выходом 17 синхронизатора-15. Первый выход 18 синхронизатора 15 подключен к управляющим входам преобразователей 3 и 4, регистров 7 и 11 сдвига и запоминающей ячейки 10, выход подключен к первому входу всех дешифраторов 19 соответствия, второй вход которых соединен с соответствующим выходом первого регистра 7 сдвига, выход подключен к соответствующему накопителю 20. К параллельным входам первого регистра 7 сдвига подключены соответствзгющие выходы матричного дешифратора 5. Устройство работает в пяти режимах. Первый режим - вычисление оценок корреляционных функций в реальном масштабе времени по знаковому методу с лрименением вспомогательных сигналов. Вычисление оценок корреляционных функций осуществляется параллельно за Ы циклов (где N -объем использованной ш.7борки). Период следования импульсов на вых1эде 18 синхронизатора 15 равен шагу задержки At. Регистр 7 сдвига работает в режиме псюлеповательного сдвига информашш поступающей с выхода первого цифрового дискриминатора 6. На входы 1 и 2 подаются исследуем случайные сигналы Х ( t ) и У (t ), которые преобразуютЬя в двоичный код аналого-цифровыми преобразователями 3 и 4j Цифровые дискриминаторы 6 и 8сравнивают коды, выдаваемые преобразователями 3 и 4, с кодами, поступающими от генератора 12 псевдослучайных чисел. Цифровые дискриминаторы 6 и 8 выдают логическую единицу, если код входного сигнала больше кода вспомогательного сигнала, и логический ноль в противном случае. Двоичная последовательность с выхода цифрового дискриминатора 6 задерживается регистром 7 сд га и подается на один из входов соотве ствующего дешифратора 19 соответствия на вторые входы которых подается двои ная 1последовательность, с выхода цифрового дискриминатора 8 через запоминаю щую ячейку 10, На выходе накопителей 20 в виде к точек (к-число разрядов регистра-7 сдвига, равное числу интервалов квантования преобразователи З), равносто5пдих вдоль а згумента с шагом i получаем оценку корреля1шонной функции RXV Второй режим - вычисление оценок и тегрального закона распределений Р(х) случайного процесса х( t ). Вычисление оценок Г (х) осуществляет ся параллельно за N циклов. Регистр 7 сдвига работает в режиме параллельной записи, а запоминающая ячейка 1О (три гер) и регистр 11 сдвига установлены в единичное состояние, которое не меняется в течение процесса измерения Р(х). Оценка-F(x) получается на выходе накопителей 20 в виде (п -число разрядов аяалог(41ифров6гопре обра -... -зователя; точек, равноотстоящих вдоль оси аргумента с шагом АХ , равного уровню квантования преобразователей 3. Получение-F(xj) на выходе v -го нако- пителя группы 20 обеспечивается за сче работы дешифратора 5 в соответствии с соотношением :/1 npH)t(iW Т Oppvv ДРУГИИ XW При этом на соответствующем выходе д шифратора 5 получается единичный сигнал в соответствующий разряд регистра сдвига и через соответствующий дешифратор 19 соответствия - в соответствующий накопитель 20, Таким образом, на выходе накопителей 20 после Ы циклов усреднения будет получена оценка 2 Р точек интегрального закона распределения F (х). Третий вычисление оценок дифференциального закона распределения W(x) Зтучайного процесса х{ t ). Данный режим отличается от предыдущего работой матричного дешифратора 5, который в данном случае работает в соответствии с соотношением . (AnpHX.-f.x(t)...f о ПРИ ДРУГИИ x(t) На выходе накопителей 2О после N циклов усреднения будет получена оценка 2 К точек дифференциального распределения W (х). Четвертый режим - вычисление оценсж интегрального двумерного aaicoHa распределения F(x;y; t ) случай1Ш1х процессов х( ) и у( I ). Оценка Г(х;у; т ) получается на выходах накопителей 20 в виде оценок 2 К точек сечения по Х пои . V-y, i const,C((-H) const, гне ,l,2,....„, () - состояние счетчика 13; V 0,1,2, Q номер разряда регистра 11 сдвига. Период д1 следования импульсов на выходе 14 синхронизатора 15 paBeii .., где 6 - время регистрации всех точек оценки с выходов накопителей 20 и установка их в исходное состояние. Период Д.- следования импульсов с выхода 17 синхронизатора 15 .равен , Вычисление оценок Т ) осуществляется в (9 +1) этапов, в каждом из которых находится оценка F(x;y; t ) при всех значениях х и при одном конкретном значении tr t о. 1 изменяющемся ступенчато с шагом дт:. Переход от одного этапа к другому, т.е. изменение аргумента , осуществляется автоматически, с помощью коммутатора 16, импульсами с выхода 17 синхронизатора 15, Регистр 11 сдвига и р;оммутатор 16 позволяют изменять Т; в пределах от О до ёд с шагом ut . Каждый этап состоит из К подэтапов-, в каждом из которых находится оценка f {х;у; f ) параллельно К точек, отстоящих равномерно вдоль оси х через ЛХ., npnV V -cons-l jT -c -con-bl Дрце УК - значение коаа входного сигнала V ( i ) при состоянии счетчика 13), Перехоп от одного подэтапа к другому, т.е. изменение уровня анализа v осуществляется импульсами с выхода 14 синхронизатора 15, Каждый поцэтап .состоит из Н циклов, совпадающих по длительности с циклами вычисления корреляционных функций. В каждом цикле в дешифрирующую матрицу 5 преобразователя 3 подается код сигнала X ( t ). Вход матрицы 5 открывается сигналом с выхода цифрового дискриминатора 9, который работает в таком же режиме, что и дешифратор 5. Уровень срабатывания- дискриминатора 9 задается счетчиком 13. Матричный дешифратор 5 и дискриминатор 9 работают в соответствии с соот ношением аналогичным второму режиму. За Н циклов вычисляется оценка F (х;у; t ) интегрального двумерного закона распределения случайных сигналов х( ) и У ( t ) в виде К точек, равноотстоящих по аргументу Л с шагом дх при У-Уц,с-(к-л)дг. Все же сечения оце11ки Г(х;у; t ) получаются последовательно за время (N-u-c-v0).Q.K Пятый режим - вычисление оценок дифференциального двумерного закона ра пределения W (х;у; t: ) случайных, процессов X { t ) и V (А ). Данный режим отличается от прецыду щего тем, что дешифратор 5 и дискрими натор 9 работают в соответствии с соо ношением аналогичным третьему режиму.. Таким образом, данный анализатор требует меньших аппаратурных затрат, так как для измерения нескольких характеристик случайных процессов используется одна группа накопителей, а также уменьшается число счетчиков и э ментов И. Аналоговые схемы задаьшя уровня анализа и получения сигналов сравнения заменены цифровыми, что повысило надежность устройства и позволяет использовать современную элемент ную базу на ИС. В каждом цикле одновременно измеряется К точек характеристики случайного процесса, что увеличивает быстродействие устройства и позволяет производить вычисления в реальном масштабе времени. Устройство также обеспечивает автоматическое изменение аргумента t при измерении двумерных законов распределения, что также повышает быстродействие устройства и его нiaдeжнocть. Ожидаемый экономический эффект от использования предлагаем ого изобретения может быть вычислен путем определения объема сокращаемого оборудования, определяется путем сопоставительного анализа предлагаемого и извесгного устройств и его примерной стоимости. Дополнительное оборудование, вводимое в предлагаемое устройство, по своему объему примерно равно оборудованию входной части известного анализатори. При вычислении 64 точек случайной функции объем сокращаемого оборудования равен 128-схемам совпадения (16 схем 133ЛАЗ и 22 схемы 133ЛА4) и 128 накопителям (примерно 256 схем 133ИЕ5), что составляет в стоимостном выражении примерно 1600 руб. Таким образом, ожидаемый экономический эффект на один анализатор составляет 1600 руб., при этом предлагаемое устройство имеет большое быстродействие и высокую надежность работы. Формула изобретения Многоканальный статистический анализатор, содержащий матричный дешифратор, синхронизатор, первый управляющий выход которого подключен к управляющим входам запоминающей ячейки и пер во,гЬ регистра сдвига, разрядные выходы которого через дешифраторы соответствия соединены с разрядными накопителями, выход запоминающей ячейки соединен с управляющим входом дешифраторов соответствия, второй управляющий выход синхронизатора соединен с входом счетчика, отличающийся тем, что, с целью сокращения оборудования и повышения быстродействия анализатора, в него введены три цифровых дискриминатора, генератор псевдослучайных чисел, коммутатор, второй регистр сдвига и два аналого-цифровых преобразователя, информационные входы которых являются соответствующими входами анализатора, а управляющие подключены к первому jmравляюшему выходу синхронизатора, выходы аналого-цифровых преобразователей подключены к первому входу соответственно первого и второго Цифровых дискриминаторов, вторые входы которых объе

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| АНАЛИЗАТОР СЛУЧАЙНЫХ ПРОЦЕССОВ | 1973 |

|

SU364944A1 |

| БИБЛИОТЕКА | 1973 |

|

SU383057A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Статистический анализатор | 1986 |

|

SU1411779A1 |

| Анализатор амплитудных распре-дЕлЕНий | 1979 |

|

SU798868A1 |

| Статистический анализатор | 1986 |

|

SU1394219A1 |

| Устройство для определения закона распределения случайной величины | 1986 |

|

SU1425713A1 |

| Устройство для параметрической оценки закона распределения | 1985 |

|

SU1283796A1 |

| Статистический анализатор | 1977 |

|

SU693398A1 |

Авторы

Даты

1980-05-05—Публикация

1977-11-01—Подача