Изобретение относится к радиотехнике и связи, в частности к передаче и приему звуковых сигналов, и может быть использовано в цифровых системах радиовещания с независимыми синхрогенераторами.

Цель изобретения - повышение точности согласования скоростей.

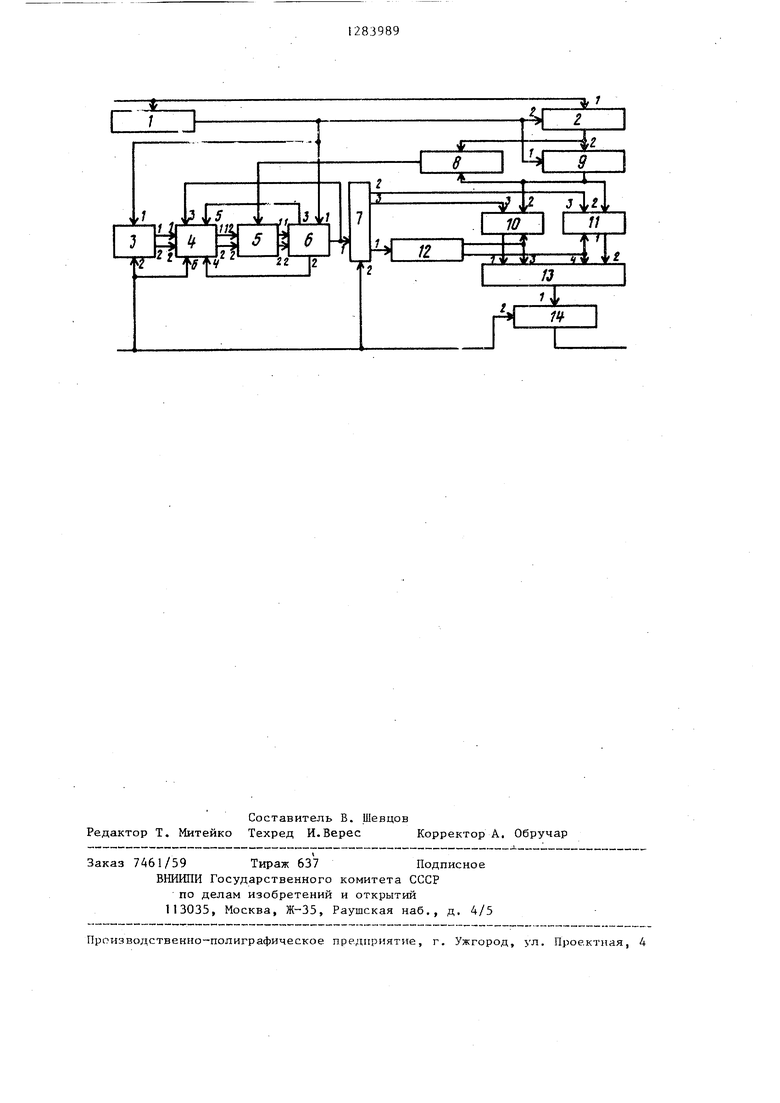

На чертеже приведена структурная электрическая схема устройства согласования скоростей цифровых потков при передаче сигналов цифрового радиовещания.

Устройство содержит выделитель 1 синхроимпульсов, блок 2 последовательно-параллельного преобразования, анализатор 3 рассинхронизации, счетчик 4, коммутатор 5, формирователь 6 синхроимпульсов, блок 7 синхронизации, анализатор 8 пауз, блок 9 задержки, первый и второй буферные регистры 10 и 11, переключатель 12, блок 13 уплотнения и блок 14 параллельно-последовательного преобразования.

Устройство согласования скоростей цифровых потоков при передаче сигналов цифрового радиовещания работает следующим образом.

При поступлении сигнала на вход . выделения . на его выходе образуется последовательность импульсов, которая подается на первые входы анализатора 3, формирователя 6, блока 9 и вход блока 2, На синхронизирующий вход анализатора 3 подается / последовательность эталонных синхроимпульсов. При отставании или опережении эталонной последовательности от входной на несколько полных тактов на первоМ или втором выходе анализатора 3 фopмиpyeтcя командный импульс, который фиксируется в счетчике, выполненном реверсивным, Анализатор 8, подключенный к входу и выходу блока 9, определяет наличие сигнала паузы в принятом сигнале и формирует на своем выходе сигнал разрешение трансформации паузы. Параметры блока 9 определяются минимально допустимым временем паузы в передаваемом сигнале с точки зрения качества его восприятия слушателем.

При опережении эталонной после- . довательности по отношению к входной число целых тактов опережения фиксир уется в счетчике 4, на первом выходе которого формируется ко- мандный сигнал Опережение, который 1ФИ наличии сигнала Разрешение трансформации паузы подается

с помощью коммутатора 5 на второй вход формирователя 6, Наличие командного сигнала на втором входе формирователя 6 при поступлении на его первый вход очефедного входного

импульса обеспечивает на первом выходе формирователя 6 формирование синхропоследовательности, Сформированная синхропоследовательность поступает на прямой вход счетчика

блока 7, обеспечивающего подачу ее на второй или третий выходы в зависимости от используемого в данный момент для записи информации первого или второго буферного регистра 10 или П, При этом в ячейки соответствующего первого или второго буферного регистра 10 или

11 производится запись избыточных

импульсов символа пауза с выхода

блока 9, Одновременно,синхропоследовательность с первого выхода формирователя 6 поступает на третий вход счетчика 4, а на его пятый вход - подается сигнал pesefpca счетчика

Опережение с третьего выхода формирователя 6, После компенсации тактов опережения, зафиксированных в счетчике 4, и обнуления всех его ячеек снимается сигнал Опережение

с первого выхода счетчика 4, что приводит к прекращению работы син- хрогенератора и записи дополнительных импульсов в один из буферных регистров 10 или Л2. В процессе дальнейшего считывания информации из буферного регистра длительность сигнала увеличивается за счет удлинения паузы на необходимое количество циклов,

При отставании эталонной синхро- последовательности от входной число целых тактов отставания фиксируется в счетчике 4, а на его втором выходе формируется сигнал Отставание, который в случае наличия сигнала Разрешение трансформаид1и паузы на третьем входе коммутатора 5 подается на третий вход формирователя

6, снимая синхроимпульс с его первого выгхода. В этом случае синхроим-: пульсы не попадают на вход блока 7 и, следовательно, на его второй и третий выходы. Запись символа паузы

i

3

в первый и второй буферные регистры

10и I1 не производится в течение времени, необходимого для компенсации. Одновременно с второго выхода формирователя 6 подается сигнал реверса счетчика 4 по его четвертому входу, а на вход этого счетчика подается эталонная синхропоследовател ность. После компенсации тактов отставания, зафиксированных в счетчике, и обнуления всех его ячеек сигнал Отставание снимается с второго выхода анализатора 3, и процесс компенсации прекращается.

Считывание информации с первого и второго буферных регистров 10 и

11производится под действием син- хропоследовательности, подаваемой одновременно на вход соответствующего счетчика 4, работающего в режиме реверса. По обнулении iscex его ячеек подается сигнал смены регистров и начинается считывание с второго буферного регистра 11 вне зависимости от его заполненности.

Таким образом, приоритетным является режим считывания, а для обеспечения возможности компенсации как опережения, так и отставания предусмотрено неполное заполнение первого и второго буферных регистро 10 и II в режиме синхронизма.

Информация с первого и второго буферных регистров 10 и II после .обработки в блоках 13 и 14 к виду, удобному для передачи, подается на выход устройства.

Формула изобретения

Устройство согласования скоростей цифровых потоков при передаче сигналов цифрового радиовещания, содержащее последовательно соединенные выделитель синхроимпульсов и блок последовательно-параллельного преобразования, входы которых объединены, а также последовательно соединенные блок синхронизации и переключатель, первый и второй выходы которого подключены к первым

839894

входам соответственно первого и второго буферных регистров, выходы которых подключены соответственно к первому и второму входам блока f уплотнения, выход которого подк-пю- чен к входу блока параллельно-последовательного преобразования, отличающееся тем, что, с целью повышения точности согласоваШ ния скоростей, введены анализатор рассинхронизации, счетчик, коммутатор, формирователь синхроимпульсов, анализатор пауз и блок задержки, первый вход которого сое15 динен с входом блока последовательно-параллельного преобразования, выход которого соединен с объединен- ными первым; входом анализатора пауз и вторым входом блока задерж20 ки, выход которого соединен с объединенными вторыми входами первого и второго буферного регистра и анализатора пауз, выход которого подключен к управляющему входу крммутато 5 ра, первый и второй входы которого подключены к первому и второму выходу счетчика, первый и второй входы которого соединены с первым и вторым выходами анализатора рассинхрониза30 ции, вход которого соединен с B{jxo- дом выделителя синхроимпульсов, и первым входом формирователя синхроимпульсов, первый, второй и третий выходы которого соединены соответст35 венно с третьим, четвертым и пятым входами счетчика, первый и второй выходы коммутатора соединены с первым и вторым входами формирователя синхроимпульсов, первый выход кОто40 рого подключен к входу блока синхронизации, второй и третий выходы которого подключены к третьим входам ч соответственно первого и второго буферных регистров, первые входы ко-

45 торых объединены соответственно с третьим и четвертым входами блока уплотнения, при этом синхрониз1Ч)у1о- щие входы анализатора рассинхрони- зации, счетчика, блока синхрониза0 ции и блока параллельно-последовательного преобразования объединены.

ClIZl

Составитель В. Шевцов Редактор Т. Митейко Техред И.Верес Корректор А. Обручар

Заказ 7461/59 Тираж 637Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

iL

Г

ri if

a

J

H

w

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство согласования скоростей цифровых потоков при передаче сигналов цифрового радиовещания | 1987 |

|

SU1444966A2 |

| Цифровой термометр | 1987 |

|

SU1571427A1 |

| Устройство цифровой передачи звукового сигнала | 1985 |

|

SU1338088A1 |

| Устройство для согласования цифровых потоков при передаче звукового сигнала | 1989 |

|

SU1698995A1 |

| Цифровой фазоразностный демодулятор | 1983 |

|

SU1113901A2 |

| Устройство для магнитной записи и воспроизведения цифровой информации | 1981 |

|

SU1007122A1 |

| Устройство для магнитной записи и воспроизведения информации | 1990 |

|

SU1714676A1 |

| Цифровой частотный демодулятор | 1991 |

|

SU1817249A1 |

| Цифровой фильтр | 1989 |

|

SU1695492A2 |

| Цифровой компенсационный фазометр | 1980 |

|

SU924611A1 |

Изобретение относится к радиотехнике и связи. Цель изобретения - повышение точности согласования скоростей. Устройство содержит выделитель I синхроимпульсов, блок 2 последовательно-параллельного преобразования, блок 7 синхронизации, два буферных регистра (БР) 10 и П, переключатель 12, блок 13 уплотнения и блок 14 параллельно-последовательного преобразования. Вновь введены анализатор 3 рассиихрониза- ции, счетчик 4, коммутатор 5, форми-, рователь 6 синхроимпульсов, анализатор 8 пауз, блок 9 задержки. Приоритетным является режим считывания, а для обеспечения возможности компенсации как опережения, так и отставания предусмотрено неполное заполнение БР 10 и 11 в режиме синхронизма. Информация с БР 10 и II после отработки в блоках 13 и 14 к виду, удобному для передачи, подается на выход устройства. 1 ил. 3 (Л

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Патент США № 4058682, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-01-15—Публикация

1985-07-11—Подача