Изобретение относится к электрической связи, а именно к технике передачи цифрового сигнала, и может быть использовано в цифровом радиовещании при согласовании взаимно несинхронизированной аппаратуры.

Целью изобретения является повышение точности передачи звукового сигнала путем уменьшения искажений амплитудно-частотного спектра этого сигнала.

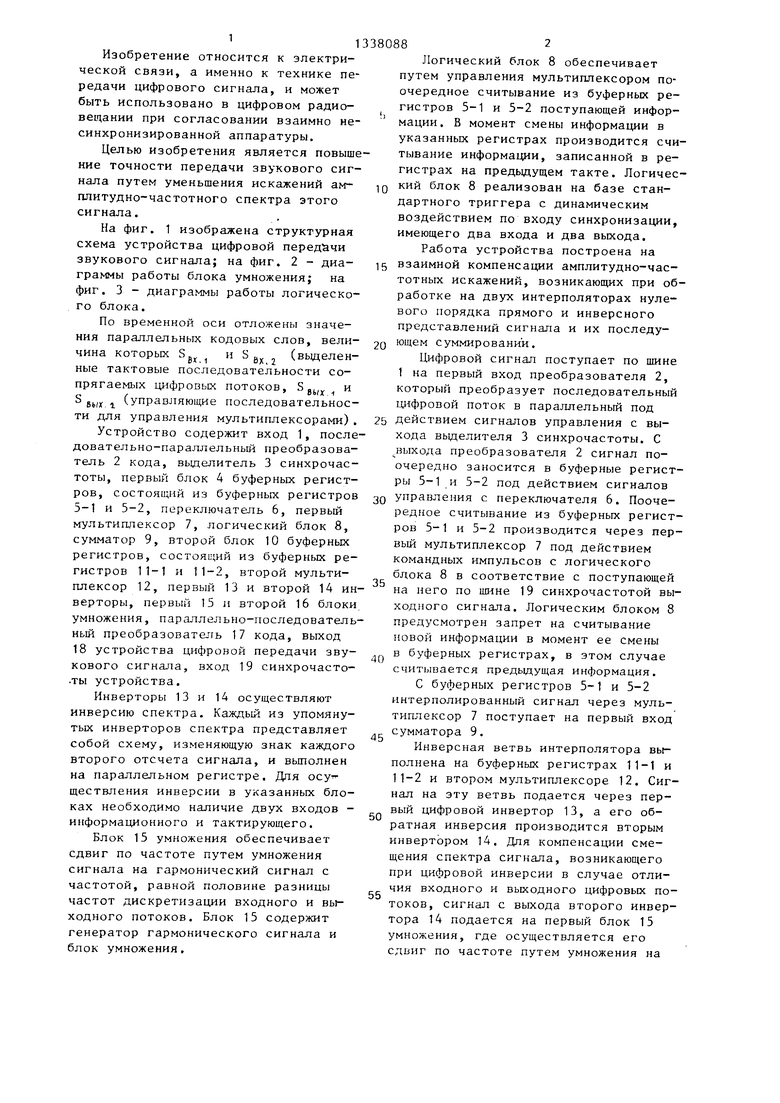

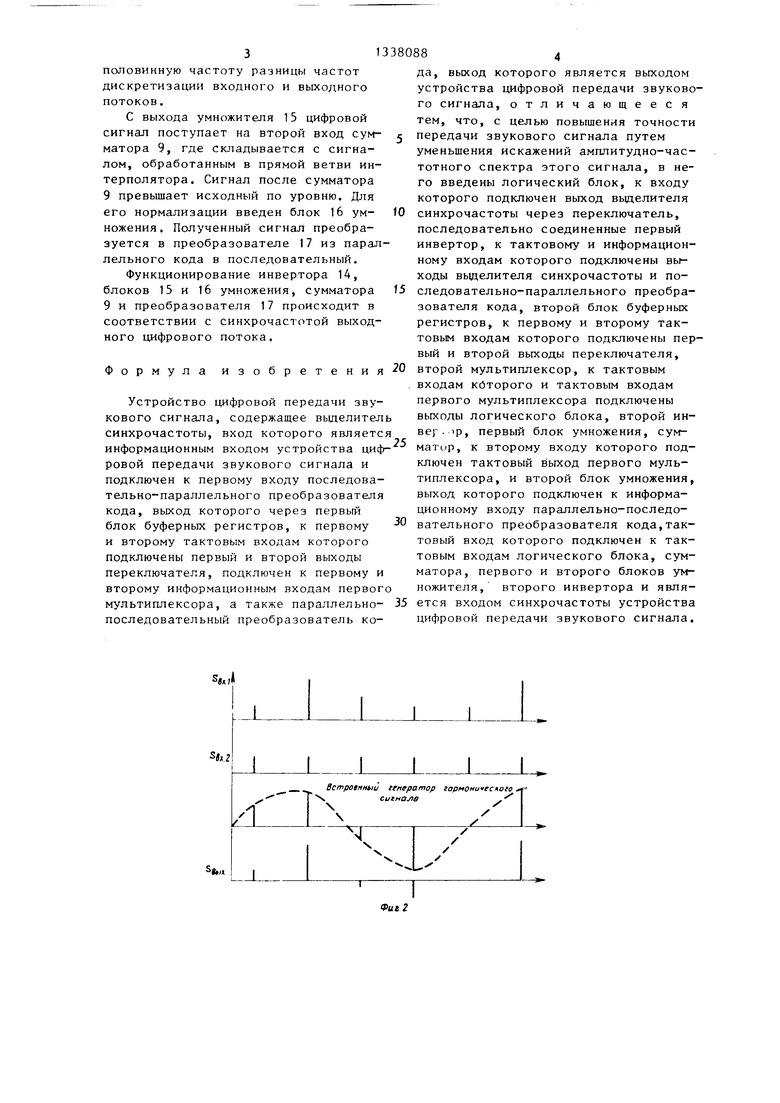

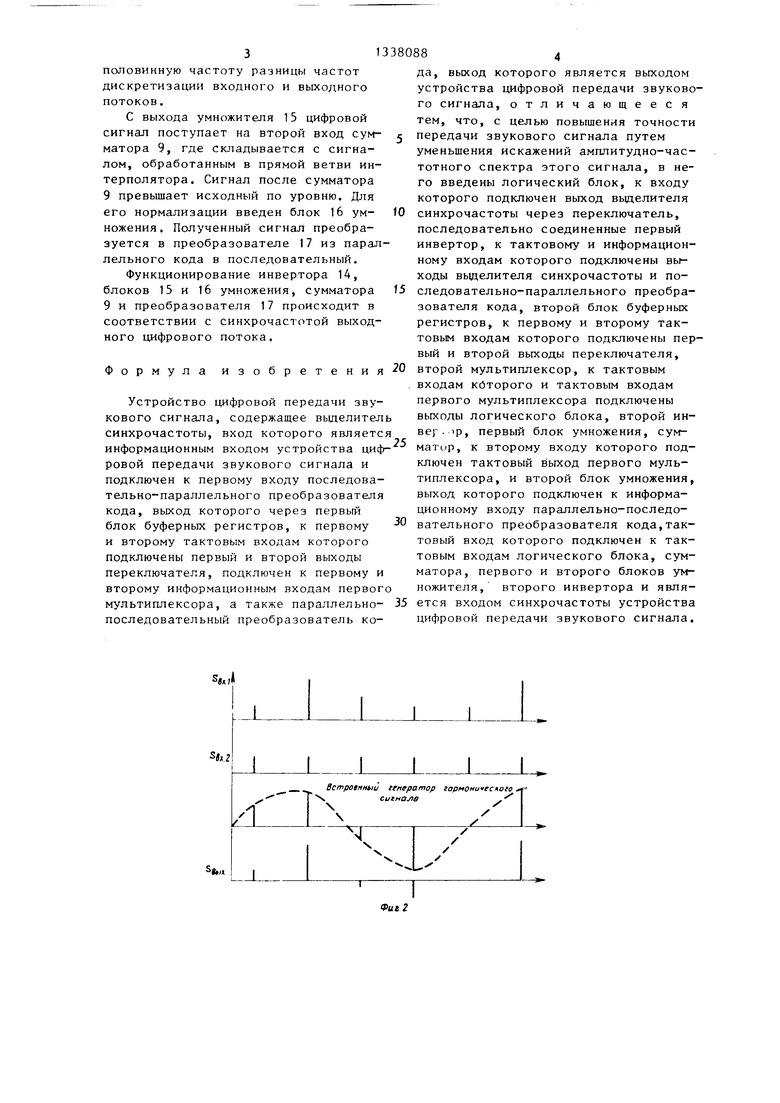

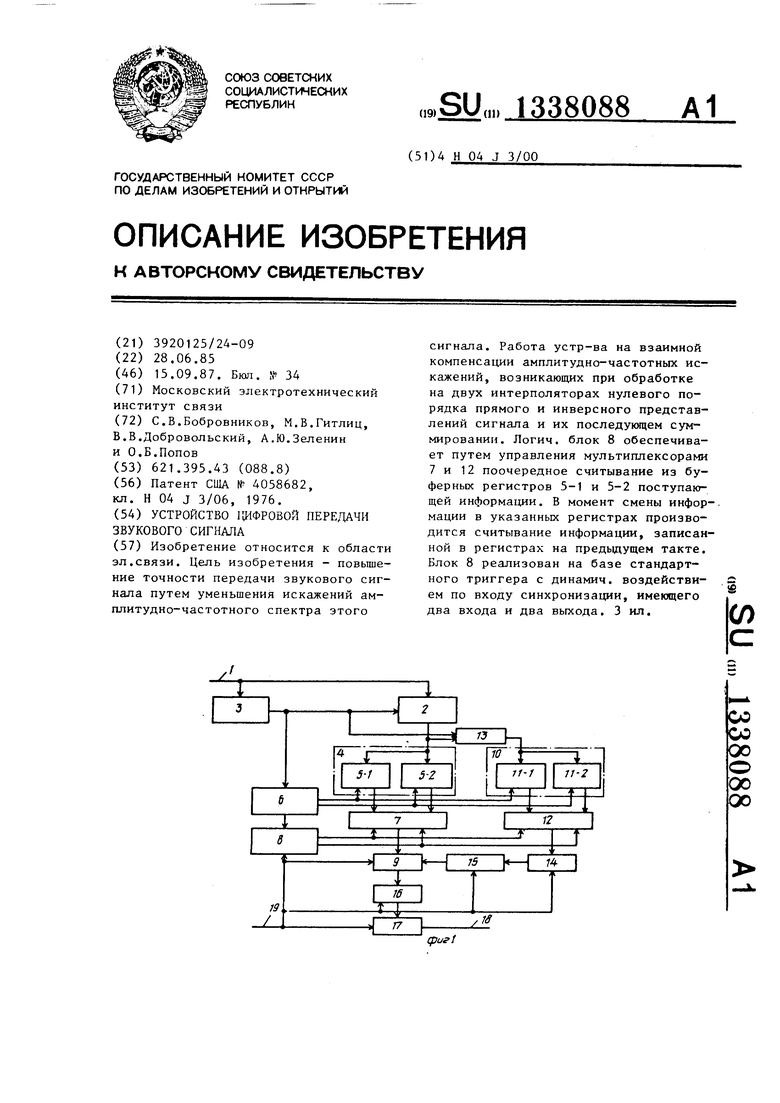

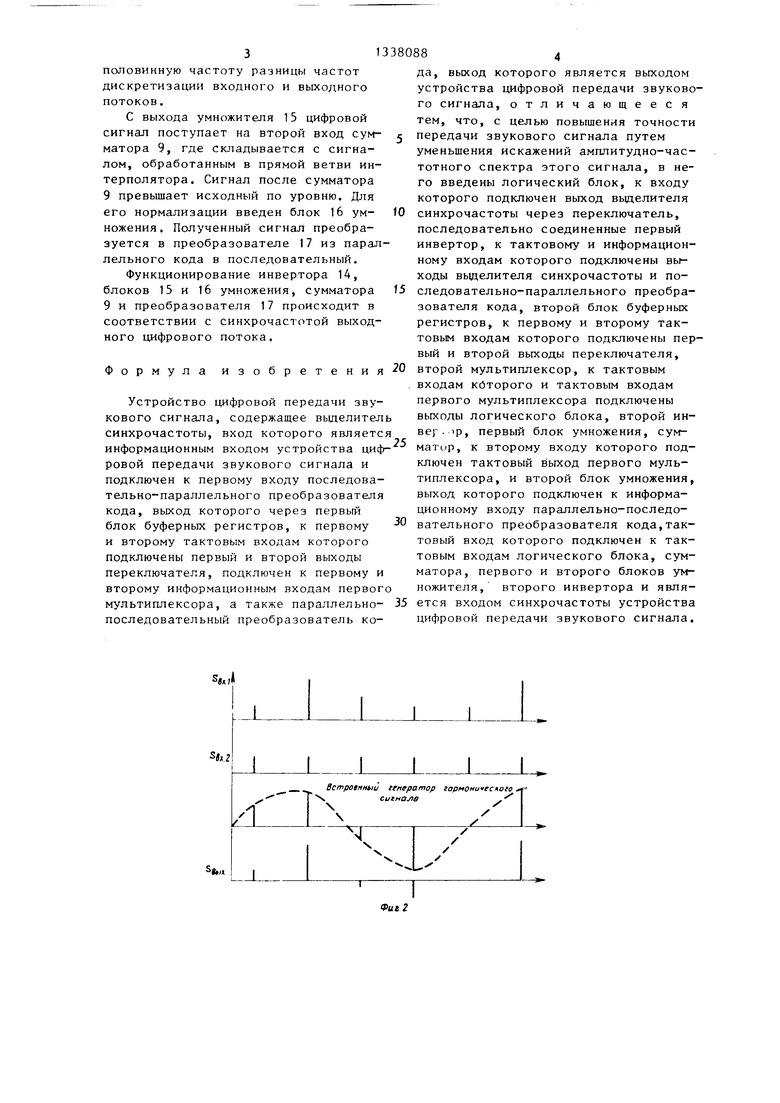

На фиг. 1 изображена структурная схема устройства цифровой передачи звукового сигнала; на фиг. 2 - диаграммы работы блока умножения; на фиг. 3 - диаграммы работы логического блока.

По временной оси отложены значения параллельных кодовых слов, величина которых Sgi вх 2 (выделенные тактовые последовательности сопрягаемых цифровых потоков, S g,, и S (управляюш;ие последовательности для управления мультиплексорами).

Устройство содержит вход 1, последовательно-параллельный преобразователь 2 кода, вьщелитель 3 синхрочас- тоты, первый блок 4 буферных регистров, состоящий из буферных регистров 5-1 и 5-2, переключатель 6, первый мультиплексор 7, логический блок 8, сумматор 9, второй блок 10 буферньк регистров, состояи;ий из буферных регистров 11-1 и 11-2, второй мультиплексор 12, первый 13 и второй 14 инверторы, первый 15 11 второй 16 блоки умножения, параллельно-последовательный преобразователь 17 кода, выход 18 устройства цифровой передачи звукового сигнала, вход 19 синхрочасто- ты устройства.

Инверторы 13 и 14 осуществляют инверсию спектра. Каждый из упомянутых инверторов спектра представляет собой схему, изменяющую знак каждого второго отсчета сигнала, и вьтолнен на параллельном регистре. Дпя осу ществления инверсии в указанных блоках необходимо наличие двух входов - информационного и тактирующего.

Блок 15 умножения обеспечивает сдвиг по частоте путем умножения сигнала на гармонический сигнал с частотой, равной половине разницы частот дискретизации входного и выходного потоков. Блок 15 содержит генератор гармонического сигнала и блок умножения.

Логический блок 8 обеспечивает путем управления мультиплексором поочередное считывание из буферньк регистров 5-1 и 5-2 поступающей информации. В момент смены информации в указанных регистрах производится считывание информации, записанной в регистрах на предыдущем такте. Логический блок 8 реализован на базе стандартного триггера с динамическим воздействием по входу синхронизации, имеющего два входа и два выхода. Работа устройства построена на

5 взаимной компенсации амплитудно-частотных искажений, возникающих при обработке на двух интерполяторах нулевого порядка прямого и инверсного представлений сигнала и их последу0 ющем суммировании.

Цифровой сигнал поступает по шине 1 на первый вход преобразователя 2, который преобразует последовательный цифровой поток в параллельный под

5 действием сигналов управления с выхода выделителя 3 синхрочастоты. С выхода преобразователя 2 сигнал поочередно заносится в буферные регистры 5-1 и 5-2 под действием сигналов

0 управления с переключателя 6. Пооче- считывание из буферных регистров 5-1 и 5-2 производится через первый мультиплексор 7 под действием командных импульсов с логического блока 8 в соответствие с поступающей на него по шине 19 синхрочастотой выходного сигнала. Логическим блоком 8 предусмотрен запрет на считывание новой информации в момент ее смены в буферных регистрах, в этом случае считывается предьодущая информация. С буферных регистров 5-1 и 5-2 интерполированный сигнал через мультиплексор 7 поступает на первый вход сумматора 9.

Инверсная ветвь интерполятора выполнена на буферных регистрах 11-1 и 11-2 и втором мультиплексоре 12. Сигнал на эту ветвь подается через первый цифровой инвертор 13, а его обратная инверсия производится вторым инвертором 14. Для компенсации смещения спектра сигнала, возникающего при цифровой инверсии в случае отличия входного и выходного цифровых потоков, сигнал с выхода второго инвертора 14 подается на первый блок 15 умножения, где осуществляется его сдвиг по частоте путем умножения на

5

0

5

0

5

31338088

оловинную частоту разницы частот искретизации входного и выходного отоков.

С выхода умножителя 15 цифровой игнал поступает на второй вход суматора 9, где Складывается с сигнадаус го те пе ум то го ко си по ин но хо 15 сл зо ре то вы вт вх пе вы ве ма кл ти вы ци ва то то ма но

лом, обработанным в прямой ветви интерполятора. Сигнал после сумматора 9 превышает исходный по уровню. Для его нормализации введен блок 16 умножения. Полученный сигнал преобразуется в преобразователе 17 из параллельного кода в последовательный. Функционирование инвертора 14, блоков 15 и 16 умножения, сумматора 9 и преобразователя 17 происходит в соответствии с синхрочастотой выходного цифрового потока.

Формула изобретения

Устройство цифровой передачи звукового сигнала, содержащее выделител синхрочастоты, вход которого являетс информационным входом устройства цифровой передачи звукового сигнала и подключен к первому входу последовательно-параллельного преобразователя кода, выход которого через первый блок буферных регистров, к первому и второму тактовым входам которого подключены первый и второй выходы переключателя, подключен к первому и

да, выход которого является выходом устройства цифровой передачи звуково го сигнала, отличающееся тем, что, с целью повышения точности передачи звукового сигнала путем уменьшения искажений амплитудно-частотного спектра этого сигнала, в него введены логический блок, к входу которого подключен выход выделителя синхрочастоты через переключатель, последовательно соединенные первый инвертор, к тактовому и информационному входам которого подключены выходы выделителя синхрочастоты и по- 15 следовательно-параллельного преобразователя кода, второй блок буферных регистров, к первому и второму тактовым входам которого подключены пер вый и второй выходы переключателя, второй мультиплексор, к тактовым входам кйторого и тактовым входам первого мультиплексора подключены выходы логического блока, второй ин- веу. ip, первый блок умножения, сумматор, к второму входу которого подключен тактовый выход первого мультиплексора, и второй блок умножения, выход которого подключен к информационному входу параллельно-последовательного преобразователя кода,тактовый вход которого подключен к тактовым входам логического блока, сумматора, первого и второго блоков умножителя, второго инвертора и явля-

второму информационным входам первого

мультиплексора, а также параллельно- 35 ется входом синхрочастоты устройства

последовательный преобразователь ко- цифровой передачи звукового сигнала.

л

-BcmpoiHHtiu генератор гармонического

Xcutnajta

/

да, выход которого является выходом устройства цифровой передачи звукового сигнала, отличающееся тем, что, с целью повышения точности передачи звукового сигнала путем уменьшения искажений амплитудно-частотного спектра этого сигнала, в него введены логический блок, к входу которого подключен выход выделителя синхрочастоты через переключатель, последовательно соединенные первый инвертор, к тактовому и информационному входам которого подключены выходы выделителя синхрочастоты и по- 5 следовательно-параллельного преобразователя кода, второй блок буферных регистров, к первому и второму тактовым входам которого подключены первый и второй выходы переключателя, второй мультиплексор, к тактовым входам кйторого и тактовым входам первого мультиплексора подключены выходы логического блока, второй ин- веу. ip, первый блок умножения, сумматор, к второму входу которого подключен тактовый выход первого мультиплексора, и второй блок умножения, выход которого подключен к информационному входу параллельно-последовательного преобразователя кода,тактовый вход которого подключен к тактовым входам логического блока, сумматора, первого и второго блоков умножителя, второго инвертора и явля-

0

5

0

Составитель В.Паницкий Редактор А.Маковская Техред В.Кадар Корректор В.Бутяга

Заказ 4147/57 Тираж 638Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Фиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ПРОВЕРКИ ЗАВЕРЕННОГО ЦИФРОВЫМ ВОДЯНЫМ ЗНАКОМ ЭЛЕКТРОННОГО ИЗОБРАЖЕНИЯ | 2009 |

|

RU2411579C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| Устройство для предварительной фильтрации входных сигналов узкополосных цифровых фильтров | 1990 |

|

SU1739481A1 |

| Устройство программного управления | 1984 |

|

SU1246055A1 |

| Многоканальное устройство для регистрации информации | 1984 |

|

SU1236452A1 |

| Кодирующее устройство | 1987 |

|

SU1510093A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Способ и устройство изменения скорости передачи цифрового звукового сигнала телерадиовещания с предыскажением | 2024 |

|

RU2830465C1 |

| Устройство для кодирования аналоговых сигналов | 1989 |

|

SU1624696A1 |

| СПОСОБ ИНДЕНТИФИКАЦИИ ТОНАЛЬНЫХ СИГНАЛОВ В СЕТЯХ СВЯЗИ И ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2004 |

|

RU2291405C2 |

Изобретение относится к области эл.связи. Цель изобретения - повышение точности передачи звукового сигнала путем уменьшения искажений амплитудно-частотного спектра этого сигнала. Работа устр-ва на взаимной компенсации амплитудно-частотных искажений, возникающих при обработке на двух интерполяторах нулевого порядка прямого и инверсного представлений сигнала и их последующем суммировании. Логич. блок 8 обеспечивает путем управления мультиплексорами 7 и 12 поочередное считывание из бу- ферньк регистров 5-1 и 5-2 поступакг- щей информации. В момент смены информации в указанных регистрах производится считывание информации, записанной в регистрах на предьщущем такте. Блок 8 реализован на базе стандартного триггера с динамич. воздействием по входу синхронизации, имеющего два входа и два выхода. 3 ил. i (Л 00 со 00 о 00 00

| Патент США № 4058682, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-09-15—Публикация

1985-06-28—Подача