Изобретение Относится к вычислиельной технике и может быть исполь- зовано при построении быстродействующих многоразрядных вычислительных устройств в позиционно-остаточной системе счисления.

Цель изобретения - уменьшение объема оборудования.

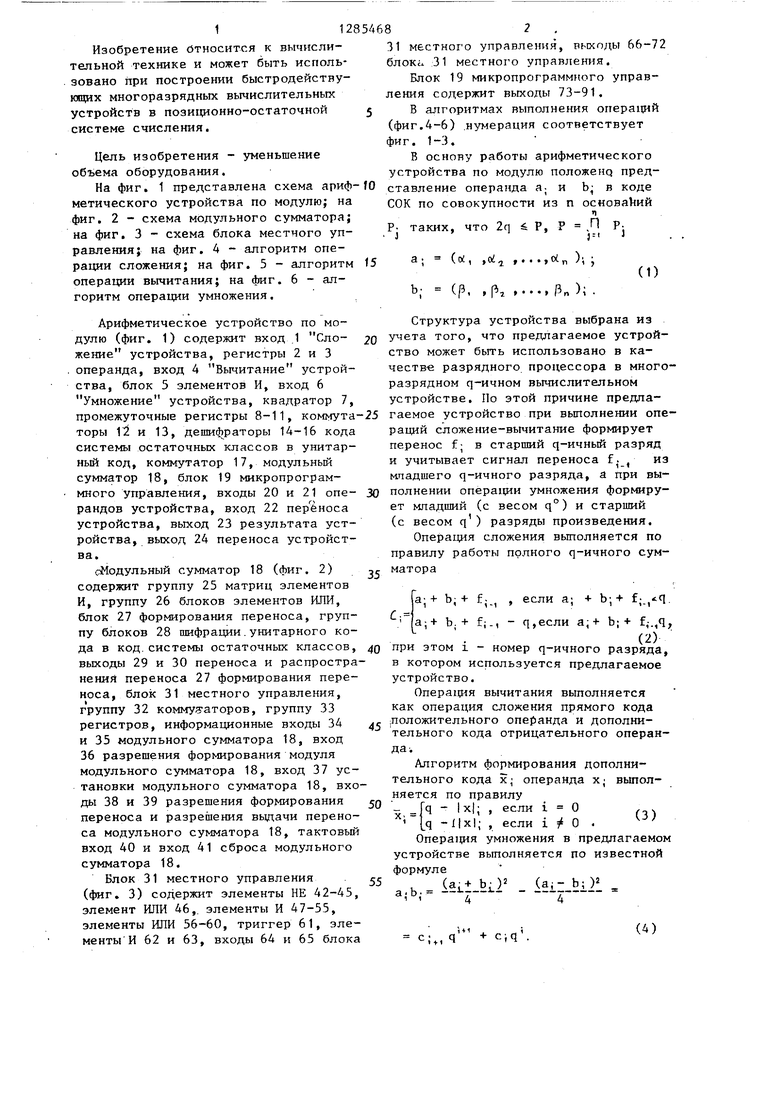

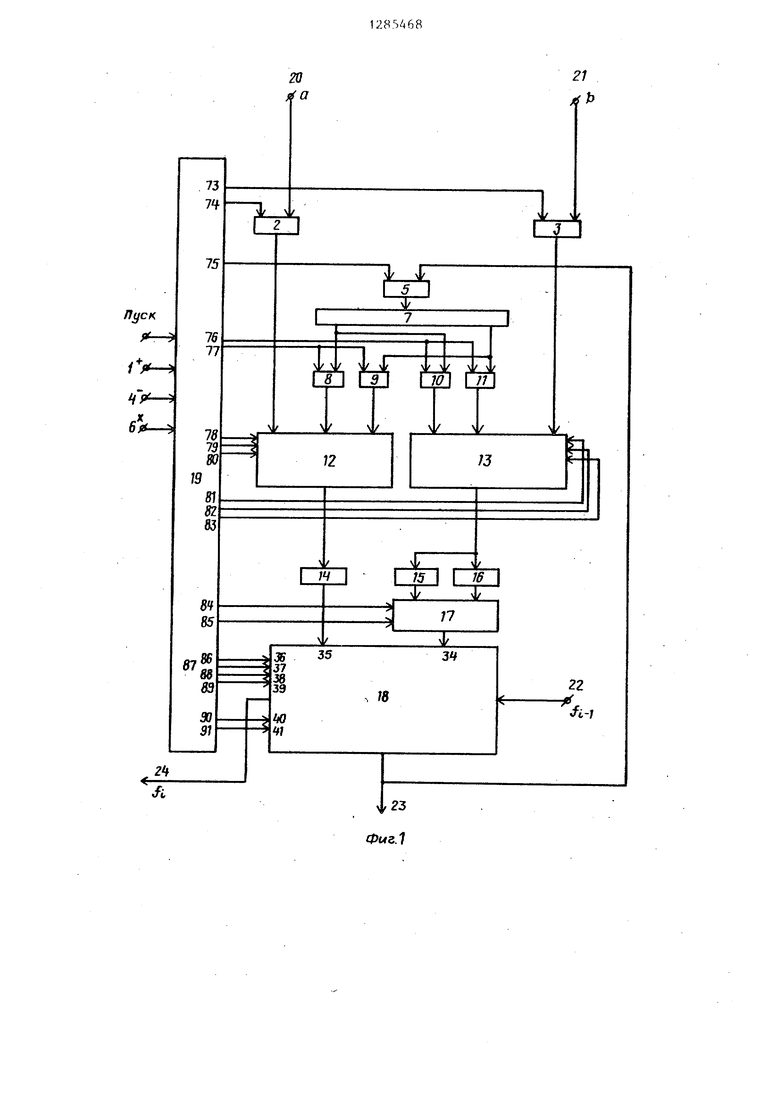

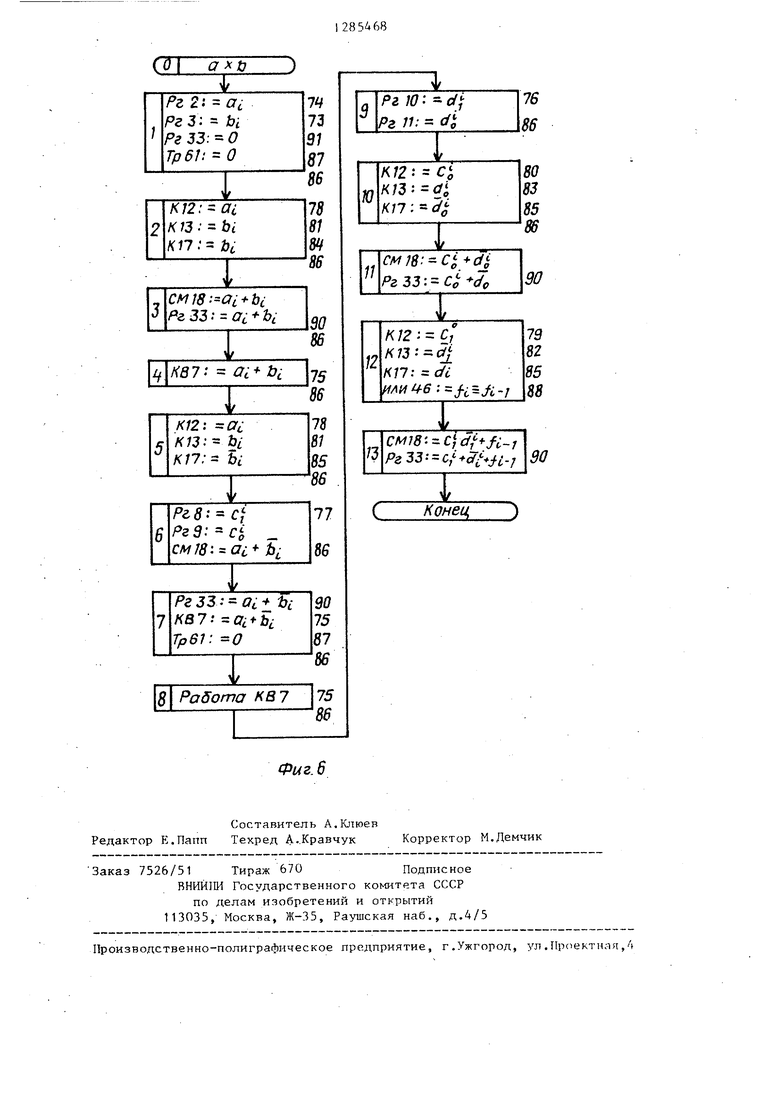

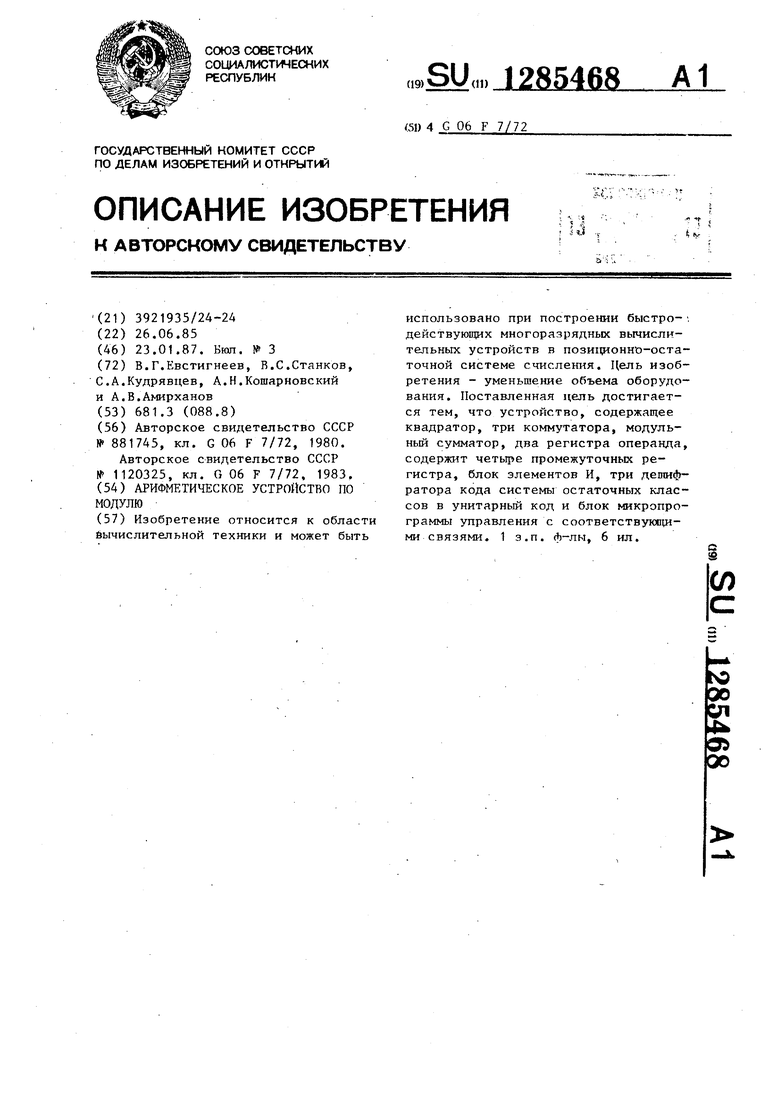

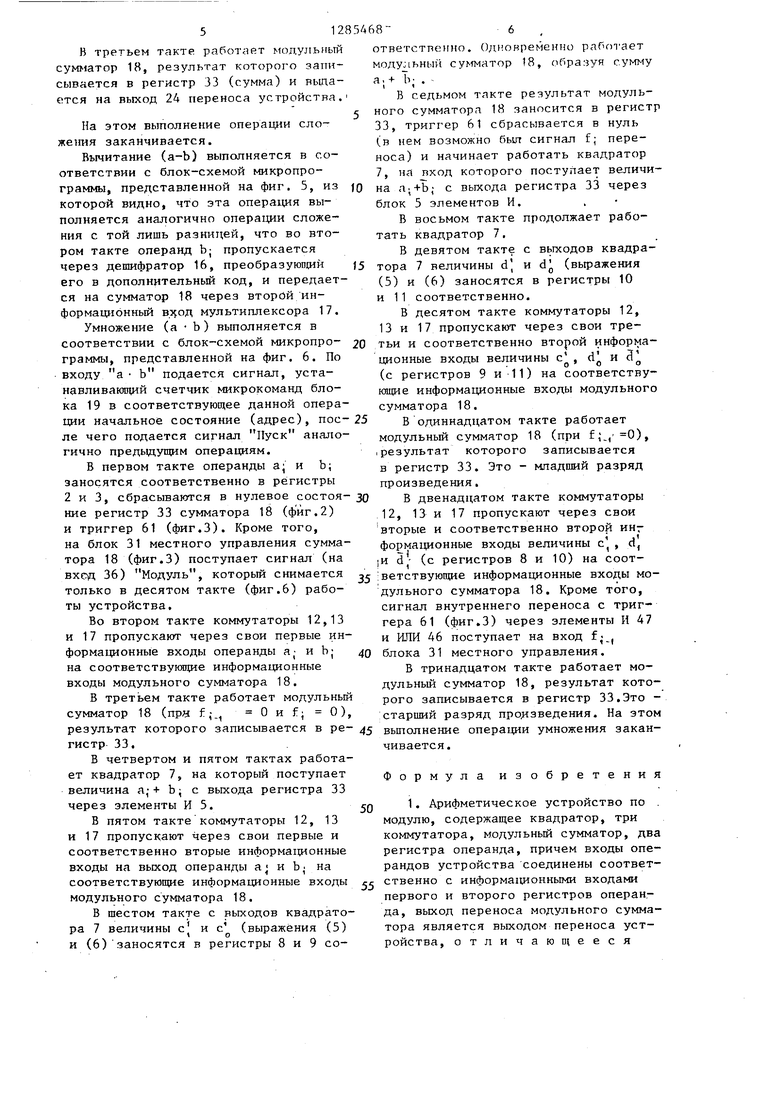

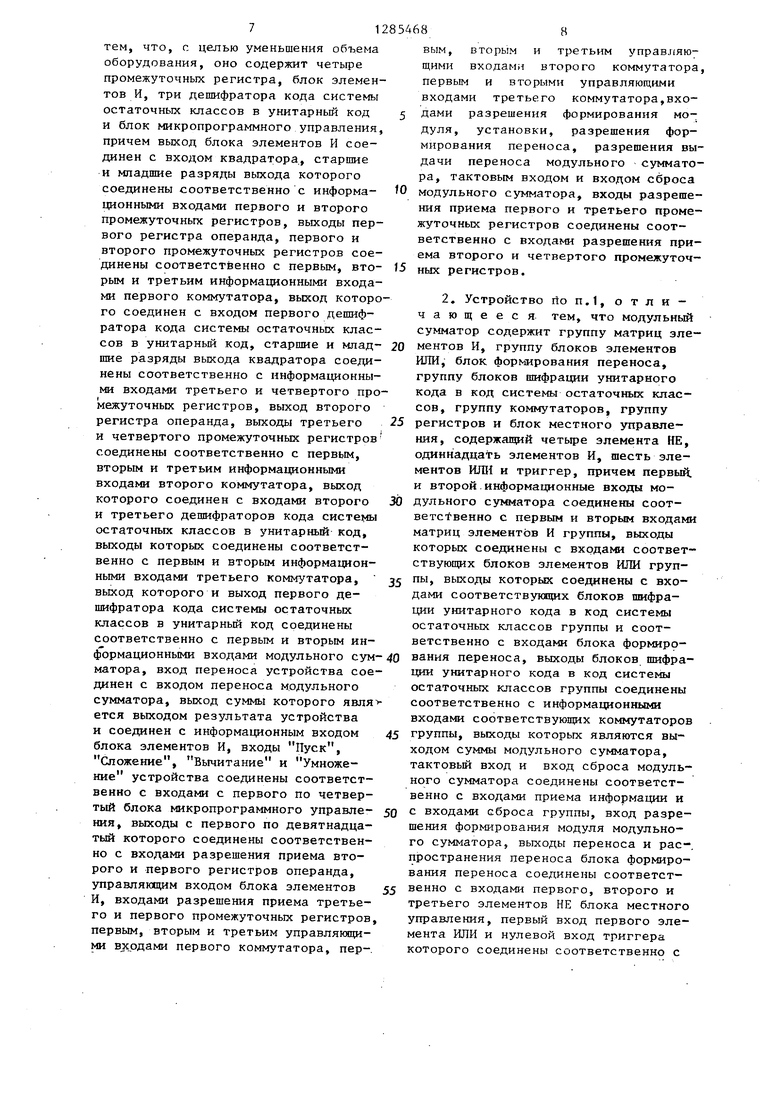

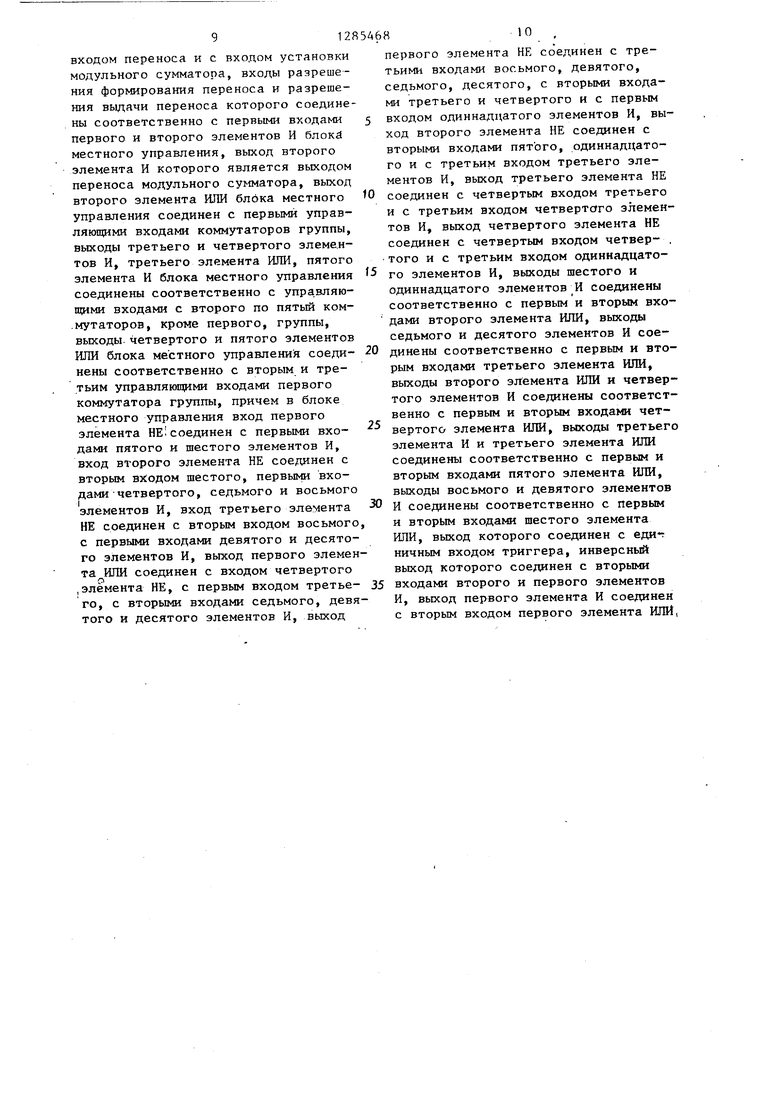

На фиг. 1 представлена схема арифметического устройства по модулю; на фиг. 2 - схема модульного сумматора; на фиг. 3 - схема блока местного управления; на фиг. 4 - алгоритм операции сложения; на фиг. 5 - алгоритм операции вычитания; на фиг. 6 - алгоритм операции умножения.

Арифметическое устройство по модулю (фиг. 1) содержит вход .1 Сло- жение устройства, регистры 2 и 3 операнда, вход 4 Вычитание устройства, блок 5 элементов И, вход 6 Умножение устройства, квадратор 7, промежуточные регистры 8-11, коммута торы 1 и 13, дешифраторы 14-16 кода системы остаточных классов в унитарный код, коммутатор 17, модульный сумматор 18, блок 19 микропрограммного управления, входы 20 и 21 one- рандов устройства, вход 22 пер ёноса устройства, выход 23 результата устройства, выход 24 переноса устройства.

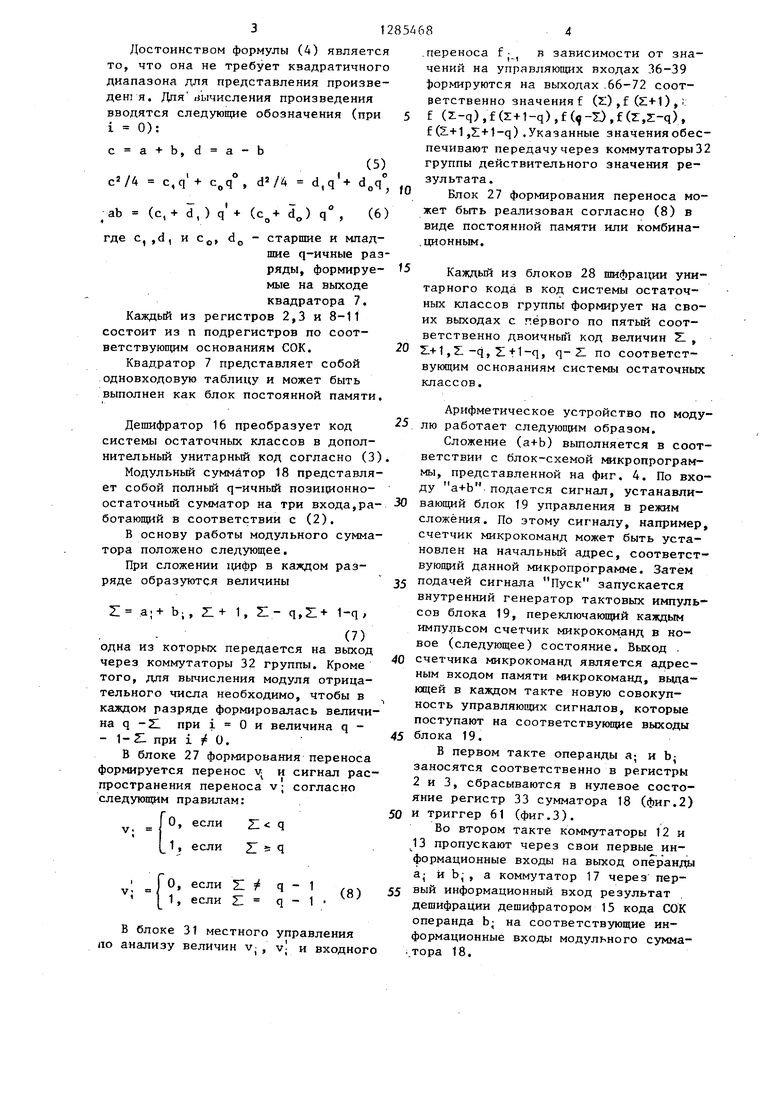

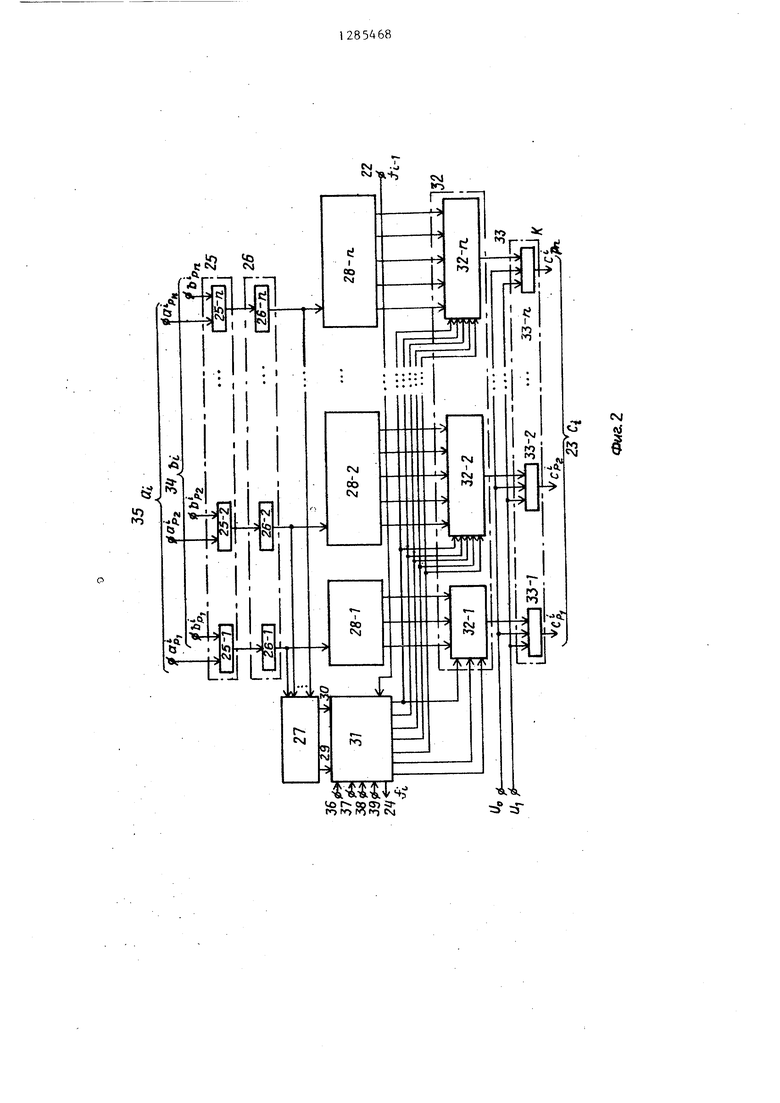

сМодульный сумматор 18 (фиг. 2) содержит группу 25 матриц элементов И, группу 26 блоков элементов ИЛИ, блок 27 формирования переноса, группу блоков 28 шифрации.унитарного кода в код. системы остаточных классов, выходы 29 и 30 переноса и распространения переноса 27 формирования переноса, блок 31 местного управления, группу 32 коммуз аторов, группу 33 регистров, информационные входы 34 и 35 модульного сумматора 18, вход 36 разрешения формирования модуля модульного сумматора 18, вход 37 установки модульного сумматора 18, входы 38 и 39 разрешения формирования переноса и разрешения выдачи переноса модульного сумматора 18, тактовый вход 40 и вход 41 сброса модульного сумматора 18.

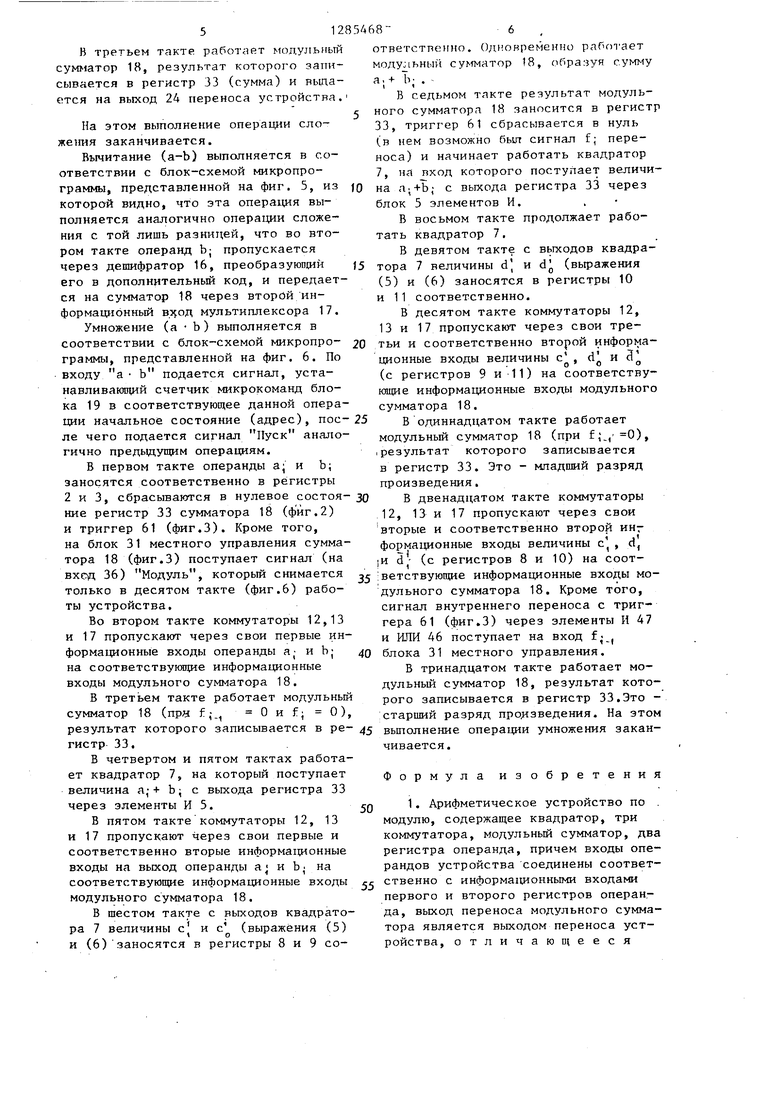

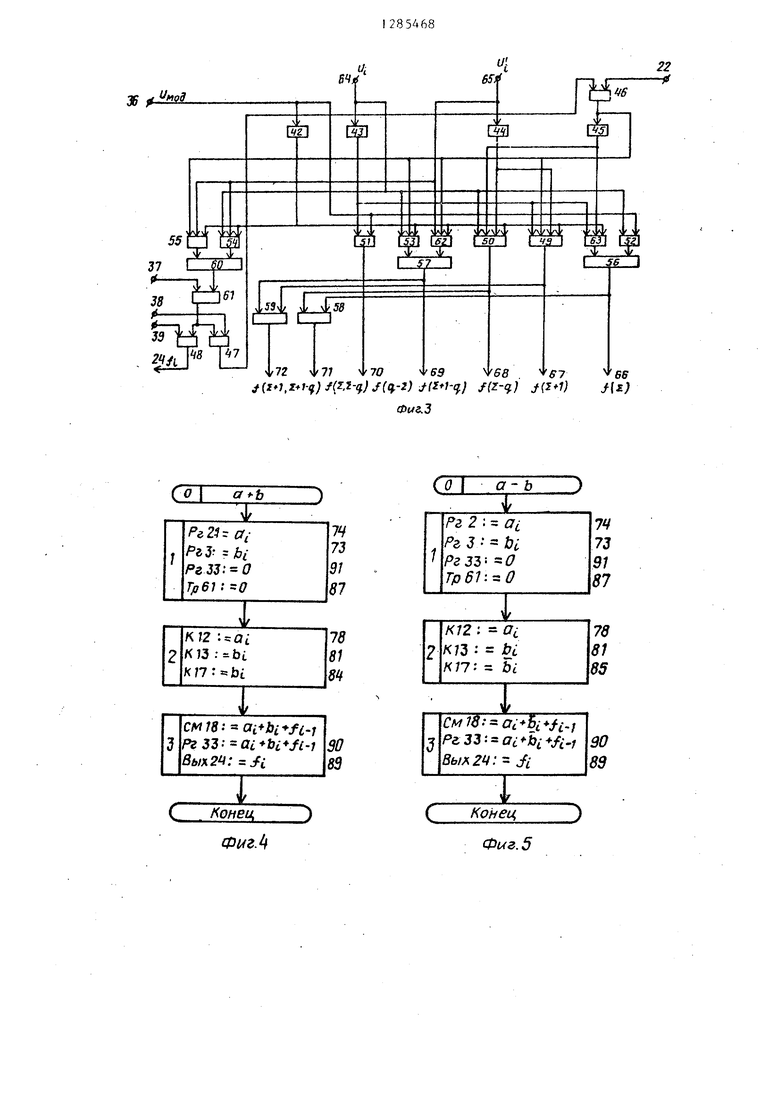

Блок 31 местного управления . (фиг. 3) содержит элементы НЕ 42-45, элемент ИЛИ 46,. элементы И 47-55, элементы ИЛИ 56-60, триггер 61, элементы И 62 и 63, входы 64 и 65 блока

31 местного управления, РЫХОДЫ 66-72 блока 31 местного управления.

Блок 19 микропрограммного управления содержит выходы 73-91. В алгоритмах выполнения операций (фиг.4-6) .нумерация соответствует фиг. 1-3.

В основу работы арифметического устройства по модулю положено пред- ставление операнда а; и Ь в коде

СОК по совокупности из п оснований

п

Р- таких, что 2q i Р, Р .П р. 3; )i ;

b; (р, ,р ,..., Э„ ); .

(1)

Структура устройства выбрана из учета того, что предлагаемое устройство может быть использовано в ка- честв-е разрядного процессора в многоразрядном q-ичном вычислительном устройстве. По этой причине предпа- гаемое устройство при выполнении операций сложение-вычитание формирует перенос f; в старший q-ичный разряд и учитывает сигнал переноса f. из мпадшего q-ичного разряда, а При выполнении операции умножения формирует младший (с весом q°) и старший (с весом q ) разряды произведения.

Операция сложения вьтолняется по правилу работы полного q-ичного сумматора

Га;+ Ь, + f, , если а; + Ь;+ f;./q. -; а;+ Ь. + fj., - q,ecли а;-t- b; + f,-.,q,

при этом i - номер q-ичного разряда, в котором используется предлагаемое устройство.

Операция вычитания выполняется как операция сложения прямого кода jПoлoжитeльнoгo операнда и дополнительного кода отрицательного операнда-.

Алгоритм формирования дополнительного кода X; операнда х; вьтолняется по правилу

г. q - 1х|; , если i О , . q -Ilxl; , если i 5 О .

Операция умножения в предлагаемом устройстве выполняется по известной формуле

(§i.) (а;- ЬО ,

а.Ь;

с;,, -н c,q

(4)

312

Достоинством формулы (4) является то, что она не требует квадратичного диапазона для представления произведет я, Дпя йычисления произведения вводятся следующие обозначения (при i 0):

c a + b, d a-b

cV4 c,q + , dV4 d,q +

;ab (c,-t- d,) q + ( d) q°, (6)

где с,,d, и Сд, dp - старшие и младшие q-ичные разряды, формируе- мые на выходе квадратора 7.

Каждый из регистров 2,3 и 8-11 состоит из п подрегистров по соответствующим основаниям СОК.

Квадратор 7 представляет собой одновходовую таблицу и может быть выполнен как блок постоянной памяти.

Дешифратор 16 преобразует код системы остаточных классов в дополнительный унитарный код согласно (3)

Модульный суммйтор 18 представляет собой полный q-ичный позиционно- остаточный сумматор на три входа,ра- ботающий в соответствии с (2).

В основу работы модульного сумматора положено следующее.

При сложении в каждом разряде образуются величины

Z а;+ Ь;, 21+ 1, 21- q,2:+ 1-q /

(7)

одна из которых передается на выход через коммутаторы 32 группы. Кроме того, для вычисления модуля отрицательного числа необходимо, чтобы в каждом разряде формировалась величина q -51 при i О и величина q - - 1- S. при i 0.

В блоке 27 формирования переноса формируется перенос v и сигнал распространения переноса v; согласно следуюпщм правилам:

V. q « I

1, если ZT Ч

- Го, если 21 i q - 1 55 « 1, если Z: q - 1

В блоке 31 местного управления по анализу величин Vj, vj и входного

5

jg

5

20

-30

35

0

5

0

5

684

.переноса f j, в зависимости от значений на управляющих входах 36-39 )ормируются на выходах .66-72 соот- ретственно значения f (Zl) ,f (+1) ,;. Е (2:-q),f(r+1-q),f(-l},f(2:,Z-q), f(S+1,Z+1-q).Указанные значенияобес- печивают передачу через коммутаторы 32 группы действительного значения результата.

Блок 27 формирования переноса может быть реализован согласно (8) в виде постоянной памяти или комбина,ционным.

Каждый из блоков 28 шиЛрации унитарного кода в код системы остаточных классов группы формирует на своих выходах с первого по пятый соответственно двоичный код величин 51, 51+1,51-q, Z t1-q, q-21 по соответствующим основаниям системы остаточных классов.

Арифметическое устройство по модулю работает следуюпщм образом.

Сложение (а+Ь) выполняется в соответствии с блок-схемой микропрограммы, представленной на фиг. 4. По входу а+Ь подается сигнал, устанавливающий блок 19 управления в режим сложения. По этому сигналу, например, счетчик микрокоманд может быть установлен на начальньй адрес, соответствующий данной микропрограмме. Затем подачей сигнала Пуск запускается внутренний генератор тактовых импульсов блока 19, переключающий каждым импульсом счетчик микрокоманд в новое (следующее) состояние. Выход . счетчика микрокоманд является адресным входом памяти микрокоманд, вьща- ющей в каждом такте новую совокупность управляющих сигналов, которые поступают на соответствующие выходы блока 19.

В первом такте операнды а; и Ь заносятся соответственно в регистры 2 и 3, сбрасываются в нулевое состояние регистр 33 сумматора 18 (фиг.2) и триггер 61 (фиг.З).

Во втором такте коммутаторы 12 и J3 пропускают через свои первые информационные входы на выход операнды а; и Ъ,- , а коммутатор 17 через первый информационный вход результат дешифрации дешифратором 15 кода СОК операнда Ь; на соответствующие информационные входы модульного сутчма- ..тора 18.

В третьем такте работает модульный сумматор 18, результат которого записывается в регистр 33 (сумма) и выдается на выход 24 переноса устройства.

ответственно. Одновременно работает моду 1ьный сумматор 8, образуя сумму а.+ TV . В седьмом такте результат модуль- 5 ного сумматора 18 заносится в регистр

На этом выполнение операции ело- зЗ, триггер 61 сбрасывается в нуль же1гия заканчивается.(в нем возможно был сигнал f; переВычитание (а-Ь) выполняется в со- носа) и начинает работать квадратор ответствии с блок-схемой микропро- 7, на вход которого поступает величи- граммы, представленной на фиг. 5, из jg „а а;+Ь; с вьгхода регистра 33 через

которой видно, что эта операция выполняется аналогично операции сложения с той лишь разницей, что во втором такте операнд Ь; пропускается через дешифратор 16, преобразуюп1ий его в дополнительный код, и передается на сумматор 18 через второй инблок 5 элементов И. .

В восьмом такте продолжает работать квадратор 7.

В девятом такте с вьгходов квадра- )5 тора 7 величины d и d (вьфажения (5) и (6) заносятся в регистры 10 и 11 соответственно.

о о о (с регистров 9 и 11) на соответствующие информационные входы модульного сумматора 18.

В одиннадцатом такте работает модульный сумматор 18 (при f;,), (результат которого записывается в регистр 33. Это - младший разряд произведения.

В двенадцатом такте коммутаторы 12, 13 и 17 пропускают через свои вторые и соответственно второй инг

формационный в.од мультиплексора 17. в десятом такте коммутаторы 12,

Умножение (а Ь) выполняется в 13 и 17 пропускают через свои тре- соответствии с блок-схемой микропро- 20 тьи и соответственно второй информа- граммы, представленной на фиг. 6. По ционные входы величины с , d), и 3 входу а Ь подается сигнал, устанавливающий счетчик микрокоманд блока 19 в соответствующее данной операции начальное состояние (адрес), пос-25 ле чего подается сигнал Пуск аналогично предыдущим операциям.

В первом такте операнды а; и Ь; заносятся соответственно в регистры 2 и 3, сбрасываются в нулевое состоя- ЗО ние регистр 33 сумматора 18 (фиг.2) и триггер 61 (фиг.З). Кроме того,

на блок 31 местного управления сумма- формационные входы величины с , , d , тора 18 (фиг.З) поступает сигнал (на |И d - (с регистров 8 и 10) на соот- вхед 36) Модуль, который снимается 5 ;ветствующие информационные входы мо- только в десятом такте (фиг.6) рабо- дульного сумматора 18. Кроме того, ты устройства,сигнал внутреннего переноса с тригВо втором такте коммутаторы 12,13 гера 61 (фиг.З) через элементы И 47 и 17 пропускают через свои первые ин- и ИЛИ 46 поступает на вход f,-, формационные входы операнды а; и h; 40 блока 31 местного управления, на соответствующие информационные g тринадцатом такте работает мо- входы модульного сумматора 18. дульный сумматор 18, результат котоВ третьем такте работает модульный рдго записывается в регистр 33.Это - сумматор 18 (пра f,- О и f; 0), старший разряд произведения. На этом результат которого записывается в ре- 5 выполнение операции умножения закан- гистр 33.чивается.

В четвертом и пятом тактах работает квадратор 7, на который поступает

Формула изобретения

величина а,-+ Ь- с выхода регистра 33 через элементы И 5.

В пятом такте коммутаторы 12, 13 и 17 пропускают через свои первые и соответственно вторые информа1щонные входы на выход операнды а и Ь,. на

50

Формула изобретения

1. Арифметическое устройство по . модулю, содержащее квадратор, три коммутатора, модульный сумматор, два регистра операнда, причем входы операндов устройства соединены соответсоответствующие информационные входы frственно с информащюнными входами

модульного сумматора 18.первого и второго регистров операнВ шестом такте с выходов квадрато-да, вьосод переноса модульного суммара 7 величины с| и с (выражения (5)тора является выходом переноса усти (6) заносятся в регистры 8 и 9 со-ройства, отличаюп1ееся

блок 5 элементов И. .

В восьмом такте продолжает работать квадратор 7.

В девятом такте с вьгходов квадра- тора 7 величины d и d (вьфажения (5) и (6) заносятся в регистры 10 и 11 соответственно.

о о о (с регистров 9 и 11) на соответствующие информационные входы модульного сумматора 18.

В одиннадцатом такте работает модульный сумматор 18 (при f;,), (результат которого записывается в регистр 33. Это - младший разряд произведения.

В двенадцатом такте коммутаторы 12, 13 и 17 пропускают через свои вторые и соответственно второй инг

13 и 17 пропускают через свои тре- тьи и соответственно второй информа- ционные входы величины с , d), и 3

формационные входы величины с , , d , |И d - (с регистров 8 и 10) на соот- ;ветствующие информационные входы мо- дульного сумматора 18. Кроме того, сигнал внутреннего переноса с триг

Формула изобретения

1. Арифметическое устройство по . модулю, содержащее квадратор, три коммутатора, модульный сумматор, два регистра операнда, причем входы операндов устройства соединены соответтем, что, с целью уменьшения объема оборудования, оно содержит четьфе промежуточных регистра, блок элементов И, три дешифратора кода системы остаточных классов в унитарный код и блок микропрограммного управления, причем выход блока элементов И соединен с входом квадратора., старшие и мпадшие разряды выхода которого соединены соответственно с информа- ционными входами первого и второго промежуточных регистров, выходы первого регистра операнда, первого и второго промежуточных регистров соединены соответственно с первым, вто- рым и третьим информационными входами первого коммутатора, выход которого соединен с входом первого дешифратора кода системы остаточных классов в унитарный код, старпие и млад- шие разряды выхода квадратора соединены соответственно с информационными входами третьего и четвертого промежуточных регистров, выход второго регистра операнда, выходы третьего и четвертого промежуточных регистров соединены соответственно с первьгм, вторым и третьим информащсонными входами второго коммутатора, выход которого соединен с входами второго и третьего дешифраторов кода системы остаточных классов в унитарный код, выходы которых соединены соответственно с первым и вторым информационными входами третьего коммутатора, выход которого и выход первого дешифратора кода системы остаточных классов в унитарный код соединены соответственно с первым и вторым информационными входами модульного сум-40 вания переноса, выходы блоков шифра- матора, вход переноса устройства соединен с входом переноса модульного сумматора, выход суммы которого явля ется выходом результата устройства и соединен с информационным входом 45 блока элементов И, входы Пуск, Сложение, Вычитание и Умножение устройства соединены соответственно с входами с первого по четвертый блока микропрограммного управле- 50 ния, выходы с первого по девятнадцатый которого соединены соответственно с входами разрешения приема второго и первого регистров операнда, управляющим входом блока элементов 55 И, входами разрешения приема третьего и первого промежуточных регистров, первьм, вторым и третьим управляющими взсрдами первого коммутатора, перции унитарного кода в код системы остаточных классов группы соединены соответственно с информационными входами соответствующих коммутаторов группы, выходы которых являются выходом суммы модульного сумматора, тактовьй вход и вход сброса модульного сумматора соединены соответственно с входами приема информации и с входами сброса группы, вход разрешения формирования модуля модульного сумматора, выходы переноса и рас-, пространения переноса блока формирования переноса соединены соответственно с входами первого, второго и третьего элементов НЕ блока местного управления, первый вход первого элемента ИЛИ и нулевой вход триггера которого соединены соответственно с

5 , О- 15 о- 20 о2530 35 2854688

вым, вторым и третьим управпяю- щими входами второго коммутатора, первым и вторыми управляющими входами третьего коммутатора,входами разрешения формирования модуля, установки, разрешения формирования переноса, разрешения выдачи переноса модульного сумматора, тактовым входом и входом сброса модульного сумматора, входы разрешения приема первого и третьего промежуточных регистров соединены соответственно с входами разрешения приема второго и четвертого промежуточных регистров.

2. Устройство rto п.1, отличающееся тем, что модульный сумматор содержит группу матриц элементов Pi, группу блоков элементов ИЛИ, блок формирования переноса, группу блоков шифрации унитарного кода в код системы остаточных классов, группу коммутаторов, группу регистров и блок местного управления, содержащий четыре элемента НЕ, одиннадцать элементов И, шесть элементов ИЛН и триггер, причем первый. и второй информационные входы модульного сумматора соединены соот- ветс венно с первым и вторым входами матриц элементов И группы, выходы которых соединены с вхрда№1 соответ- ствуюгщх блоков элементов ШШ группы, выходы которых соединены с входами соответствующих блоков шифра- ции унитарного кода в код системы остаточных классов группы и соответственно с входами блока формирования переноса, выходы блоков шифра-

ции унитарного кода в код системы остаточных классов группы соединены соответственно с информационными входами соответствующих коммутаторов группы, выходы которых являются выходом суммы модульного сумматора, тактовьй вход и вход сброса модульного сумматора соединены соответственно с входами приема информации и с входами сброса группы, вход разрешения формирования модуля модульного сумматора, выходы переноса и рас- пространения переноса блока формирования переноса соединены соответственно с входами первого, второго и третьего элементов НЕ блока местного управления, первый вход первого элемента ИЛИ и нулевой вход триггера которого соединены соответственно с

входом переноса и с входом установки модульного сумматора, входы разрешения формирования переноса и разрешения выдачи переноса которого соединены соответственно с первыми входами первого и второго элементов И блоки местного управления, выход второго элемента И которого является выходом переноса модульного сумматора, выход второго элемента ИЛИ блока местного управления соединен с первыми управляющими входами коммутаторов группы, выходы третьего и четвертого элементов И, третьего элемента ИЛИ, пятого элемента И блока местного управления соединены соответственно с упра.вляю- щими входами с второго по пятый ком- .мутаторов, кроме первого, группы, выходы, четвертого и пятого элементов ИЛИ блока местного управления соеди- иены соответственно с вторым и третьим управляющими входами первого коммутатора группы, причем в блоке местного управления вход первого элемента НЕ соединен с первыми входами пятого и шестого элементов И, вход второго элемента НЕ соединен с вторым входом шестого, первыми входами четвертого, седьмого и восьмого

элементов И, вход третьего элемента НЕ соединен с вторым входом восьмого, с первыми входами девятого и десятого элементов И, выход первого элемен- входом четвертого

та ИЛИ соединен с

.элемента НЕ, с первым входом третье- го, с вторыми входами седьмого, девятого и десятого элементов И, выход

10

20

15

,

35 5А68

первого элемента НЕ соединен с третьими входами восьмого, девятого, седьмого, десятого, с вторыми входами третьего и четвертого и с первым входом одиннадцатого элементов И, выход второго элемента НЕ соединен с вторыми входами пятого, одиннадцатого и с третьим входом третьего элементов И, выход третьего элемента НЕ соединен с четвертым входом третьего и с третьим входом четвертого элементов И, выход четвертого элемента НЕ соединен с четвертым входом четвер- . того и с третьим входом одиннадцатого элементов И, выходы шестого и одиннадцатого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выходы седьмого и десятого элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выходы второго элемента ИЛИ и четвертого элементов И соединены соответственно с первым и вторым входами четвертого элемента ИЛИ, выходы третьего элемента И и третьего элемента ИЛИ соединены соответственно с первым и вторым входами пятого элемента ИЛИ, выходы восьмого и девятого элементов И соединены соответственно с первым и вторым входами шестого элемента ИЛИ, выход которого соединен с ничным входом триггера, инверсный выход которого соединен с вторыми входами второго и первого элементов И, выход первого элемента И соединен с вторым входом первого элемента ИЛИ,

25

30

/t.

i .

(о г. со 5 5г

го fO С

:Г

Ф7; Ф7

67

66

(,)/(.-t)J{(-2)() ( /(г;

Фиг.

i

г

-а

fS3

68

67

() (

ф1Аг.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство по модулю | 1986 |

|

SU1425666A1 |

| Арифметическое устройство по модулю | 1983 |

|

SU1120325A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1998 |

|

RU2143723C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1998 |

|

RU2137181C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ | 1999 |

|

RU2157560C1 |

| Устройство для умножения в системе остаточных классов | 1980 |

|

SU962942A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1991 |

|

RU2018935C1 |

| Сумматор в системе остаточных классов | 1983 |

|

SU1111170A1 |

| Устройство для умножения по модулю | 1980 |

|

SU896620A1 |

Изобретение относится к области бычислительной техники и может быть использовано при построении быстро- . действующих многоразрядных вычислительных устройств в позиционно-оста- точной системе счисления. Цель изобретения - уменьшение объема оборудования. Поставленная цель достигается тем, что устройство, содержащее квадратор, три коммутатора, модульный сумматор, два регистра операнда, содержит четыре промежуточных регистра, блок элементов И, три депиф- ратора кода системы остаточных классов в унитарньш код и блок микропрограммы управления с соответствукжщ- ми связями. 1 з.п. ф-лы, 6 ил.

| Арифметическое устройство в системе остаточных классов | 1980 |

|

SU881745A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Арифметическое устройство по модулю | 1983 |

|

SU1120325A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-23—Публикация

1985-06-26—Подача