(21)4147269/24-24

(22)17.11.86

(46) 23.09.88.Бюл. № 35

(72) В.Г.Евстигнеев и А.Н.Кошарновский

(53) 681.3(088.8)

(56)Авторское свидетельство СССР № 1120325, кл. G 06 F 7/72, 1983.

Авторское свидетельство СССР № 1200278, кл. G 06 F 7/38, 1984.

Авторское свидетельство СССР № 1285468, кл. G 06 F 7/72, 1985.

(54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ

(57)Изобретение относится к области

вычислительной техники и может быть использовано при построении быстро- действующие многоразрядных вычислительных устройств в позиционно-ос- таточной системе счисления. Целью изобретения является повьааение быстродействия. В арифметическое устройство по модулю, содержащее квадратор 5, промежуточные регистры 6-9, коммутаторы 10,11,18, дешифраторы 12,13 и модульньш сумматор 14, введены сумматор 3 кодов системы остаточных классов, вычитатель 4 кодов системы остаточных классов, коммутатор 19 и квадратор 20 с соответствующими связями. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство по модулю | 1985 |

|

SU1285468A1 |

| Арифметическое устройство по модулю | 1983 |

|

SU1120325A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Процессор быстрых дискретных преобразований | 1989 |

|

SU1725227A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| Сумматор-умножитель | 1983 |

|

SU1173409A1 |

| Устройство для умножения в системе остаточных классов | 1984 |

|

SU1236472A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

С/)

Изобретение относится к вьшисли- тельной технике и может быть использовано нри построении быстродействующих многоразрядных вычислительных устройств в йозиционно-остаточной сис- ,теме счисления.

; Целью изобретения является повьше- ие быстродействия,

I На фиг.1 представлена схема ариф- етического устройства по модулю} fia фиг. 2 - временная диаграмма вы- холнения операции умножения. I Арифметическое устройство по модулю (фиг.1) содержит входы первого 1 и второго 2 операндов устройства, сумматор 3 кодов системы остаточных классов, вычитатель 4 кодов системы оста- Точных классов, первьй квадратор 5, |; первого по четвертый промежуточные регистры 6-9, первый коммутатор 10, второй коммутатор 11, первьй дешифратор 12, второй дешифратор 13, модуль1 ьм сумматор 14, вход 15 переноса 5 стройства, выход 16 переноса устройцтва, выход 17 результата устройства, третий коммутатор 18, четвертьш комму TJaTop 19, второй квадратор 20, с пер- 4ого по десятый тактовые входы 21-30 |стройства.

j Модульный сумматор 14 конструктивно аналогичен модульному сумматору, 1 спользованному в известном устройст- EJe,из которого, с целью упрощения,ис- к|лючен выходной регистр с соответст- Дующим управлением и работает идентичHJO.

; Каждый из регистров 6-9 состоит из ri подрегистров по соответствующим основаниям системы остаточных классов Квадраторы 5 и 20 аналогичны квадратору известного устройства, представляют собой одновходовую таблицу

и могут быть выполнены как блоки постоянной памяти.

Коммутаторы 10, 11, 18 и 19, сумматор 3, вычитатель 4, дешифрато- ры 12 и J3 реализованы идентично ана- логичньм узлам известного устройства.50

В основу работы арифметического устройства.по модулю положено представление каждого операнда а и b V Ь; в коде системы остаточных классов (СОК) по совокупности ия п основа- 55 НИИ Р- таких, что 2 р, р ПР: ,

где q - модуль арифметического устройства;

а; (oi|,6i2 , . .. ,); ;

Ь; (fi, ,f3, , ... ,pj;, )

где Pj - наименьшие неотрицательные вычеты чисел а; и Ь; поосновани- ям PJ .

Структура устройства выбрана из Учета того, что предложенное устройство может быть использовано в качестве разрядного процессора в многоразрядном q-вычислительном устройстве. По этой причине предложенное устройство при выполнении операций сложение-вычитание формирует перенос ; в старший q-й разряд и учитывает сигнал переноса f;, из младшего q-ro разряда,: а при выполнении операции У1.1ножения формирует младший (с весом q°) и старший (с весом q) разряды произведения.

Операция сложения вьтолняется по правилу работы полного q-ro сумматора

Га.., , если а- + Ь;+i; q а;+b;+,-.,-q, если а; + Ь;+f,-.,5:q

(2)

где i - номер q-ro разряда, в котором используется предлагаемое устройство.

Операция вычитания выполняется как операция сложения прямого кода положительного операнда и дополнительного кода отрицательного операнда.

Алгоритм формирования дополнитель-. ного кода, Xj операнда Х.имеет вид

гг q - /(Х;)/,если /,, i q - 1 - /(X;)/, если i 0.

Операция умножения в предлагаемом устройстве вьтолняется по формуле

а.-ь. l5il- L l lElI-bLl.

с; + l. + с; . q . W

Для вычисления произведения введем обозначения (при ) С а, + Ь( , d а;- Ь; ,

С 2/4 с,- q + Co-q,

d 2/4 d, . q + d . q°. (5)

a-b (c,. -H d,)-q + (с„ H- d J.q /e)

где С,,d, и GO, do - старшие и младшие разряды, формируемые на выходах первого и второго квадраторов 5 и 20.

Анализ выражения С,+ п, показывает, что его величина всегда q, т.е.

при его вычислении переноса не никает, более того всегда С, + . Это означает, что это выражение может быть вычислено на вычитателе 4 в виде С,- d,.Пpи вычислении же выражения d возможно возникновение сигнала переноса (заема) в старший q-й разряд, поэтому его целесообразно вычислять на модульном сумма- ю торе 14.

Арифметическое устройство по модулю работает следующим образом.

Сложение (а + Ь) вьтолняется за один такт, в течение которого посту- 15 паят тактовые сигналы на входы 23 и 28 устройства. На входы 1 и 2 устройства перед началом операции подаматора 14 сигнала с входа 26 устройства.

первом такте подаются тактовые сигналы на входы 29 и 21. Коммутаторы 16 и 19 пропускают значения а; и ь-, на входы сумматора 3 и вычитателя 4, с входов которых сумма, и разность соответственно поступают на входы квадраторов 5 и 20, с выходов которых в регистры 6-9 заносятся соответственно величины С, С,, d, и do (dp- дополнительньш код величины do).Во втором такте подаются тактовые сигналы на входы 30 и 22 устройства. Содержимое регистров 6 (С,) и 8 (d,) через вторые инфорются операнды а- и Ь- , на вход 15

мационные входы коммутаторов 18 и 19 соответственно поступает на входы вычитателя 4, вычисляющего d,. устройства поступает перенос. По вхо- 20 Ядновременно содержимое регистров ду 26 устройства производится предва- 7(Сд) и 9 (d) поступает через ком- рительная установка модульного сум- мутаторы 10 и 11 соответственно и де- матора 14. Коммутаторы 10 и 11 про- шифраторы 12 и 13 на модульный сумпускают через свои вторые информационные входы на выход операнда а, и Ь которые, пройдя дешифраторы 12 и 13, поступают на соответствующие информационные входы модульного сумматора 14 который формирует согласно (2) значения суммы и переноса, поступающие на выходы 17 и 16 устройства соответственно.

Вычитание (а - Ь) может быть вы- полнено двумя способами. При первом способе считаем, что операнд Ь; поступает на вход 2 в дополнительном (обратном) коде. Тогда операция вычитания полностью аналогична операции сложения.

При втором способе сначала производится формирование дополнительного кода второго операнда Ь; , а затем выполняется операция сложения. Формирование дополнительного кода производится в течение одного такта, в котором подаются сигналы на входы 23 и 25 устройства. На вход 2 устройства перед началом операции подается Ь; , на вход 26 - установочный сигнал. Яосле получения в модульном сумматоре 14 дополнительного кода Ь; , производится сложение а. с дополнительным кодом Ь так как это было описано выше.

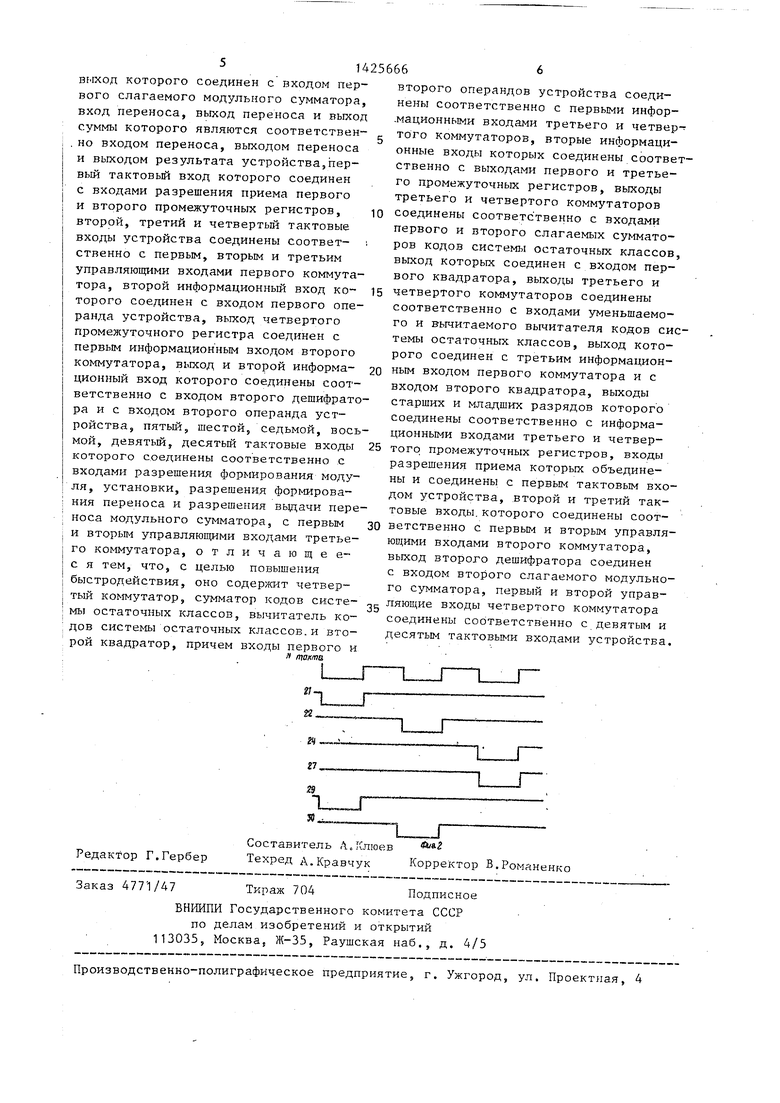

Умножение (а х Ь) выполняется в соответствии с временной диаграммой (фиг.2), Перед началом умножения на входах 1 и 2 устройства устанавливаются операнды а; и Ь; , производится начальная установка модульного сумматора 14 сигнала с входа 26 устройства.

первом такте подаются тактовые сигналы на входы 29 и 21. Коммутаторы 16 и 19 пропускают значения а; и ь-, на входы сумматора 3 и вычитателя 4, с входов которых сумма, и разность соответственно поступают на входы квадраторов 5 и 20, с выходов которых в регистры 6-9 заносятся соответственно величины С, С,, d, и do (dp- дополнительньш код величины do).Во втором такте подаются тактовые сигналы на входы 30 и 22 устройства. Содержимое регистров 6 (С,) и 8 (d,) через вторые информатор 14, вычисляющий значение млад- шего разряда произведения ( с. поступающее на выход 17 и внутренний перенос, сохраняющийся в модульном сумматоре 14. Б третьем такте подаются сигналы на входы 24 и 27 устройст- sa.

Через третий информационный вход коммутатора 10 величина С,- d, с выхода вычитателя 4 через дешифратор 12 поступает на первый информационный вход модульного сумматора 14, на втором информационном входе которого - нуль. Величина C,-dj суммируется с сигналом внутреннего переноса модульного сумматора 14, полученным в пре- дыдзпдем такте, и поступает на выход 17 устройства как старший разряд про-.- изведения. На этом выполнение операции умножения заканчивается.

Формула изобретения

Арифметическое устройство по модулю, содержащее первьй квадратор, четыре промежуточных регистра, три коммутатора, два дешифратора и модуль- ньй сумматор, причем выходы старших и младших разрядов первого квадратора соединены соответственно с информационными входами первого и второго промежуточных регистров,выход второго промежуточного регистра соединен с первым информационным входом первого коммутатора, выход которого соединен с входом первого дешифратора.

Редактор Г.Гербер

Составитель А„Клюев

Техред А.Кравчук Корректор В.Романенко

Авторы

Даты

1988-09-23—Публикация

1986-11-17—Подача