классов, группу из п коммутаторов и элемент НЕ, причем соответстзующи.е входы J-X ( j 1j2,....,n) сумMaropqB первой и второй групп попарно об1 единены и являются ссютветственно первым и вторьгм входами второго модульного сумматора, выходы J-X сумматоров первой и второй групп подключены соответственно к первым и вторьм информационным входам j-x коммутаторов В группы, выходы которь являются выходом второго модульного сумматора, первые Я вторые управляющие входы коммутаторов группы соответственно объединены и подключены соответственно к выходу элемента НЕ и входу переноса второго модульного iсумматора, к которому подключен вход элемента НЕ.

3. Устройство по п. 1, о т л ичающееся тем, что третий модульный сумматор содержит группу из h сумматоров по основаниям системы остаточных классов, дополнительный сукиаТор по первому основанию системы остаточных классов, коммутатор, блок хранения констант нулевизации, сумматор нулевиэации, два элемента ИЛИ, причем первые и вторые входы сумматоров группы являются соответственно первым и вторым входами третьего модульного сумм

20325

тора, первьм и второй входы дополнительного сумматора по первому основанию системы остаточных классов подключены к соответствующим входам первого cyi-iMaTopa группы, выход дополнительного сумматора подключен к первому информационному входу коммутатора, второй информационньй вход которого объединен с первым входом сумматора нулевиэации и подключен к выходу первого сумматора группы, выходы коммутатора и В-х (В 2 J .... h ) сумматоров группы являются -выходом третьего модульного сумматора, входы блока хранения констант нулевиэацш подключены соответственно к вьпсодам В-хсумматоров группы, выход блока хранения констант нулевизации подключен к второму входу сумматора нулевизации, группа

( 1 О, рт-1, Рт-2, +1) выходов которого подключена к соответствующим входа - первого элемента ИЛИ, группа t--x ( 1,2,,.., р /2) выходов с мматора нулевиэации подключена к соответствующим входам второго элемента ИЛИ, выхода первого и второго элементов ИЛИ соединены соответственно с первьв4 и втор.ьа входами коммутатора, выход второго элемента ИЛИ является выходом переноса третьего модульного суг-гматора,

| название | год | авторы | номер документа |

|---|---|---|---|

| @ -Ичный сумматор | 1983 |

|

SU1166097A1 |

| Устройство для сложения многоразрядных @ -ичных чисел | 1983 |

|

SU1163321A1 |

| Сумматор в системе остаточных классов | 1983 |

|

SU1111170A1 |

| Арифметическое устройство по модулю | 1985 |

|

SU1285468A1 |

| Арифметическое устройство по модулю | 1986 |

|

SU1425666A1 |

| Устройство для умножения одноразрядных @ -ичных чисел в системе остаточных классов | 1982 |

|

SU1100619A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1983 |

|

SU1121670A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для определения альтернативной совокупности чисел в системе остаточных классов | 1983 |

|

SU1151970A1 |

1.АРИСМЕТИЧЕСКОЕ УСТРОЙСТВО . ГЮ МОДУЛЮ, содержащее первый модульный сумматор, модульный вычитатель, первый и второй квадраторы, причем входы первого и второго квадраторов подключены соответственно к выходам первого модульного сумматора и модульного вычитателя, входы которых соответственно объединены и являются: входами соответственно первого и второго операндов устройства, о т л ичающееся тем, что, с целью расширения функциональных возможностей путем выполнения устройством операций сложения и дополнения, оно содержит первьй, второй и третий коммутаторы, элемент ИЛИ, второй и третий модульные сумматоры, причем первые выходы первого и второго квадраторов подключены соответственно к первому и второму входам второго модульного сумматора, выход которого является выходом старшего «у-ичного разряда результата ( Ч, - модуль) арифметического устройства, вход переноса второго модульного сумматора подключен к выходу переноса третьего модульного сумматора и является выходом переноса арифметического устройства, первые информационные входы первого и второго коммутаторов подключены соответственно к входам первого и второго операндов арифметического устройства, вторые информационные входы первого и второго KOMNryTaTopoB подключены соответственно к вторым выходам первого и второго квадраторов, выходы первого и второго коммутаторов подключены соответственно к первому и второму входам третьего модульного/ сумматорй, выход которого подключен СП к первому информационному входу трес тьего коммутатора, второй информационный вход которого подключен к выходу модульного вычитателя, а выход является выходом младшего « -ичного разряда результата арифметического устройства, первый и второй ю управляющие входы первого и второго о 00 коммутаторов соответственно объединены, подключены к входам элемента ШШ Iv9 СП и являются входами операций Умножение и Сложение ари(|н етического устройства, выход элемента ИЛИ подключен к первому управляющему входу третьего коммутатора, второй управляющий вход которого является входом операций Дополнение арифметического устройства. 2. Устройство по п. 1, о т л ичающееся тем, что второй модульный сумматор содержит первую и вторую группы из гт сумматоров по основаниям системы остаточных

Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных машин высокого быстродействия,

Известно арифметическое устройство в системе остаточных классов, содержащее регистры первого и второго операндов, регистры контрольных кодов первого и второго операндов, блок модульных сумматоров, три сумматора, три блока постоянной памяти, блок умножения, три группы элементоБ и, блок управления и соответствующие связи С О Недостатки данного устройства большой объем оборудования и невысокое быстродействие, связанное со слоностью алгоритма контроля.

Наиболее близким к изобретению является арифметическое устройство по модулю, содержащее модульный сумматор, первый и второй модульные вычитатели, первый и второй квадраторы, блок деления на константу, выход которого является выходом устройства, а вход подключен к вьтходу второго модульного вычитателя, входы которого подключены к выходам соответственно первого и второго квадраторов, входы KOTopioc подключены соответственно к выходам модульного сумматора и первого модульного вычитателя, входы которых соответственно объединены и являются входами операндов устройства 2 .

Недостаток известного арифметического устройства - ограниченные функциональные возможности. 31 Целью изобретения является расширение функциональных возможностей путем выполнения устройством дополнительно операций сложения и дополнения. Поставленная цель достигается тем что арифметическое устройство по мо.дулю, содержащее первый, модульньй сумматор, модульный вычитатель, первый и второй квадраторы, причем входы первого и второго квадраторов подключены соответственно к выходам первого модульного сумматора и модульного вычитателя, входы которых соответственно объединены и являются входами соответственно первого и второго операндов устройства, содержит первый, второй и третий коммутаторы, элемент ИЛИ, второй и третий модульные сумматоры, причем первые выходы первого и второго квадраторов / подключены соответственно к первому и второму входам второго модульного сумматора, выход которого является выходом старшего е,-ичного разряда результата (я,- модуль) арифметического устройства, вход переноса второго модульно го сумматора подключен к выходу переноса третьего модульного сумматора и является выходом переноса арифмети

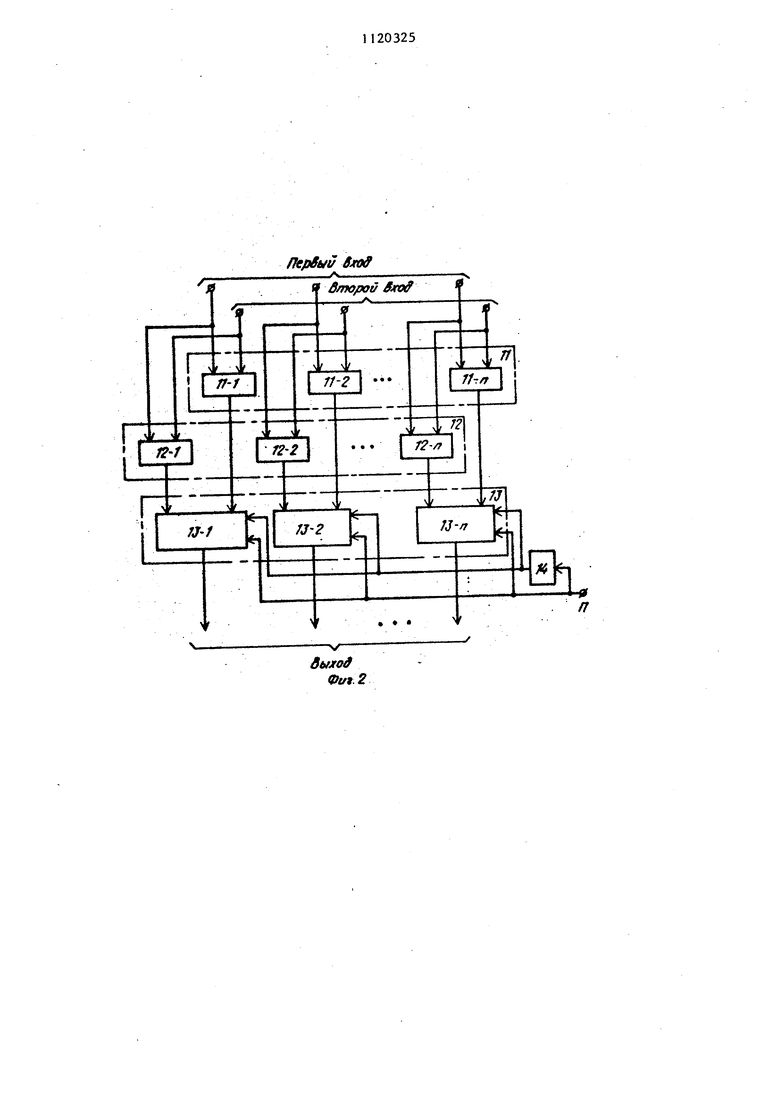

ческого устройства, первые информационные входы первого и второго коммутаторов подключены соответственно к входам первого и второго операндов арифметического устройства, вторые информационные входы первого и второго коммутаторов подключены соответственно к вторьм выходам первого и второго квадраторов, выходы первого и второго коммутаторов подключены соответственно к первому и второму входам третьего модульного сумматора выход которого подключен к первому информационному входу третьего коммутатора, второй информационный вход которого подключен к выходу модульного вычитателя, а выход является выходом младшего с}, -ичного разряда результата арифметического устройства, первый и второй управляющие входы первого и второго коммутаторов соотвественно объединены, подключены к соответственно к первому и второму входам элемента ИЛИ и являются входами операций Умножение и Сложемне арифметического устройства, выход элемента ИЛИ подключен к первому управляющему входу третьего коммуклассов, коммутатор, блок хранения констант нулевизации, сумматор нулевизации, два элемента ШШ, причем первые и вторые входы сумматоров группы являются соответственно первьи и вторым входами третьего модульного сумматора, первый и второй входы дополнительного сумматора по первому основанию системы остаточных классов подключены к соответствующим входам первого думматора груп.пы, выход дополнительного сумматора подключен к перхвому информационному входу коммутатора, второй информационный вход которого объединен с первым входом сумматора нулевизации и подключен к , выходу первого сумматора группы, выходы коммутатора и В-х ( В 2,..., п) сумматоров группы являются выходом третьего модульного сумматора, входы блока хранения констант нулевизации подключены соответственно к выходам В-х сумматоров группы, выход блока хранения констант нулевизации подключен к второму входу сумматора нулевизации, группа k-х (X О, р,-1, р -2,..., р /2+1) выходов которого подключена к соответ25татора, второй управляющий вход которого является входом операции Дополнение арифметического устройства. При этом второй модульньй сумматор содержит две группы по м сумматоров по основаниям системы остаточных классов, группу из п коммутаторов и элемент НЕ, причем соответствующие входы j -X ( J 1 , 2п ) сумматоров первой и второй групп попарно объединены и являются соответственно первыми и вторыми входами второго модульного сумматора, выходы j-x сумматоров первой я второй групп подключены соответственно к первьм и вторым информационным входам j-x коммутаторов В группы, выходы которых являются вькодом второго модульного сумматора, первые и вторые управляющие входы коммутаторов группы соответственно объединены и подключены соответственно к выходу элемента НЕ и входу переноса второго модульного сумматора, к которому подключен вход элемента НЕ. Кроме того, третий модульньй сумматор содержит группу из п сумматоров, по основаниям системы остаточных классов, дополнительный сумматор по первому основанию системы остаточных 511 ствующим входам первого элемента ИЛИ группа -X ( Ь 1,2,,.., ) выходов сумматора нулевиэаций подключена к соответствуюгцкм входам второго элемента ИЛИ, выходы первого и второго элементов ИЛИ соединены соответственно с первым и вторым входами коммутатора, выход второго элемента ИЛИ является выходом переноса третьего модульного сумматора. На фиг. 1 представлена структурная схема арифметического устройства по модулю, на фиг, 2 и 3 - функциональные схемы второго и третьего модульных сумматоров соответственно. Устройство содержит первый модуль ньй сумматор 1, модульный вычитатель 2, первьй 3 и второй 4 квадрато ры, первьй 5 и второй 6 коммутаторы, второй 7 и третий 8 модульные сумматоры, третий коммутатор 9 и элемент ИЛИ 10. Второй модульный сумматор 7 содер )жит первую 11 и вторую 12 группы сумматоров, группы коммутаторов 13 и элемент НЕ 14, а третий модульный су матор 8 - группу сумматоров 15, дополнительный сумматор 16, коммутатор 17, блок 18 хранения констант нулевизации, сумматор 19 нулевизации и элементы ИЛИ 20 и 21. В основу работы арифметического устройства по модулю положено представление каждого операнда в коде системы остаточных классов СОК по совокупности из h оснований р- таких, что 24, Р. , H,,ci,-.,,lB ((b,ft,...,b,, где 5/., /3; - наименьшие не отрицательные вычеты чисел А и В по основа ниям Р; . При сложении операндов А и В, лежащих в диапазоне с , результат 5 мо жет достигать величины Факт переполнения при Р 2 обнаруживается с помощью нулевизации, в процессе которой и результата суммирования вычитаются такие константы чтобы в результате получился либо О, либо с . Если результат нулевизации О, то 5 С, П 0. Если результат нулевизации 1, тогда S С- ,, П 1 . Вычитание с эквивалентно изменению значения вычета по основанию Р- 2 на противоположное (С сумма, П - ) , 5 При Р 2 нулевизацию проводят по основаниям р. р, а факт переполнения определяют по вычету основания Р.. Это приводит к значительному повышению быстродействия. Для повышения скорости нулевизацию проводят за один шаг сразу по всем основаниям, кроме первого. При этом блок хранения констант нулевиг.ации имеет р. р, -.. р слов. Операция вычитания в данном устройстве вьшолняется как сложение. прямого кода первого операнда и дополнительного кода второго операнда, подаваемых на входы первого и второго операндов устройства. Модульные сумматоры 1, 11 и 15 формируют сумму поступающих на них операндов по основаниям СОК, а модульный вычитатель 2 и сумматор 19 нулевизации разность поступающих на них операндов по основаниям СОК. Модульные сумматоры 12 и 16 формируют величины сумм, уменьшенных на а по соответствующему основанию, Сумматор 19 нулевизации работает п основанию р, результат, представленньш в коде 1 из р , поступает с его выхода на элементы ИЛИ 20 и 21 для формирования переноса. Блок 18 хранения констант нулевизации предтавляет постоянную память, содержащую минимальные числа нулевизации. Все модульные сумматоры и вычитатели могут быть выполнены комбинационными 3J, Операция у шожения в предлагаемом устройстве вьшолняется по формуле . () 4 . 4 Достоинством данной формулы является то, что она не требует квадратичного диапазона для представления произведения. . Введем обозначения: С А + В, d А -В, В результате возведения в квадрат и деления на 4 имеем , 0, Ис,-,)г(с,г,)я.% гдеС и сЗ - старшие с -ичные разряды квадрато.в, С и d - младшие с -ичные разряды квадратов. Арифметическое устройство по модулю работает следующим образом. По одному из управляющих входов на коммутаторы 5,6 или 9 подается сигнал, соответствующий вьшолняемой устройством операции: Умножение, Сложение или Дополнение. Затем исходные числа А и В р виде двоичных кодов вычетов по.основаниям СОК поступают на входы первого модульного сумматора 1 и модульного вычитателя которые- формируют их сумму и разност соответственно. При выполнении операции Дополнение (-) результат вычитания с модульного вычитателя 2 поступает на второй информационный вход третьего коммутатора 9, который открыт по вто рому управляющему входу, а с выхода снимается код дополнения § При этом выход второго модульного сумматора 7 и выхрд переноса третьего модульного сумматора 8 не опрашиваются При вьшолнении операции .Сложение (+) по вторым управляющим входам открыты второй 5 и третий 6 коммутаторы и по первому управляющем входу через элемент ИШ 10 открыт третий коммутатор 9. Операнды через первые информационные входы.первого и второго 6 коммутаторов поступают на вход третьего модульного сумматора 8, с выхода которого результат поступает на первый информационный вход третьего коммутатора 9, с выход которого снимается результат сложени С выхода переноса третьего модульногозз сумматора 8 снимается сигнал переноса. Выход второго модульного сумматора 7 не опрашивается. При вьтолнении операции Умножение (х) по nepBbW управляющим вхо- 40 дам открыты первый 5 и второй 6 комЫутаторы и через элементы ИЛИ 10 по первому управляющему входу открыт третий коммутатор 9. Операнды, поступившие на входы первого модульного сум- 45 матора 1 и модульного вычитателя 2 в виде + Ви , поступают на входы соответственно первого 3 и второго 4 квадраторов, на выходе которых результаты появляются в виде величин , Ср, d и Эд. Величины Э d. поступают на второй модульный сумматор 7, величины С и 5 через первый 5 и второй 6 коммутаторы - на входы третьего модульного сумматора 8, формирующего младший с, -ичньш разряд произведения с весом °, который, пройдя третий коммутатор 9, появляется на выходе последнего. Одновременно третий сумматор 8 формирует сигнал переноса, который поступает на выход переноса устройства и на выход переноса второго модульного сумматора 7. Если П О, то на выход через коммутаторы 13 поступает результат суммирования С и d с сумматоров 1 1. Если П 1, то на выход через коммутаторы 13 поступает результат С + 5.., + 1 с выходов сумматоров 12. Результат на выходе второго модульного сумматора 7 представляет .собой старший с -ичный разряд произведения . При выполнении операции Умножение выход переноса третьего модульного сумматора 8 не опрашивается. Предложенное арифметическое устройство по модулю может быть использовано и просто как арифметическое устройство в системе остаточных классов, если при вьтолнении всех трех операций опрашивать только выход третьего коммутатора 9. Таким образом, предложенное арифметическое устройство по модулю по сравнению с известньм, вьтолняющим только одну модульную операцию умножения, выполняет сложение и вычитание в системе остаточных классов, сложение и умножение а-ичных цифр. вычисляет дополнительный код второго операнда, т.е. выполняет вместо одной шестБ различных операций.

/7

Фи.1

Пе/зВыи ffjTOff

SjToff

.,, ..

f dfTfopoi jco

f-n

//

/ /

/7

I . I Imr-..i4.

/

/

NTI

/f

/ -/7-/;

a

Si)

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Арифметическое устройство в системе остаточных классов | 1980 |

|

SU881745A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ получения смеси хлоргидратов опийных алкалоидов (пантопона) из опийных вытяжек с любым содержанием морфия | 1921 |

|

SU68A1 |

| Способ получения борнеола из пихтового или т.п. масел | 1921 |

|

SU114A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Машинная арифметика в остаточных классах | |||

| И., Советское радио, 1968, с | |||

| УСТРОЙСТВО ПАРОПЕРЕГРЕВАТЕЛЯ | 1920 |

|

SU295A1 |

Авторы

Даты

1984-10-23—Публикация

1983-07-07—Подача