(54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО В СИСТЕМЕ ОбТАТОЧНЫХ

КЛАССОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство по модулю | 1985 |

|

SU1285468A1 |

| Арифметическое устройство в системе остаточных классов | 1981 |

|

SU999050A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Арифметическое устройство в системе остаточных классов | 1983 |

|

SU1107122A1 |

| Устройство для сложения и вычитания чисел по модулю | 1990 |

|

SU1755275A1 |

| Устройство для умножения в системе остаточных классов | 1978 |

|

SU922731A1 |

| Арифметическое устройство по модулю | 1983 |

|

SU1120325A1 |

| Устройство для умножения чисел по модулю | 1981 |

|

SU976440A2 |

| Устройство для умножения чисел в системе остаточных классов | 1983 |

|

SU1149254A1 |

| Устройство для умножения и сложения чисел по модулю | 1979 |

|

SU885999A1 |

Изобретение относится к вычислительной технике и предназначено для ис1 ользования в дифровых вычислительных машинах, использующих форму представления шсел в системе остаточных классов (СОК).

Известно устройство, содержащее п схем суммирования, схему контроля по модулю три, схему управления коммутацией, схему коррекции и логические элементы, обеспечивает контроль правильности выполнения операций двоичного сумматора по модулю три и вьщачу информации об ошибке 1.

Недостатками устройства является низкая вероятность обнаружения ошибок, невозможность коррекции обнаружеилыл ошибок, поскольку в устройстве не определяется величина и местонахождение обнаруженных ошибок.

Наиболее близким к изобретению является арифметическое устройство с контролем по модулю, содержащее блок управления, группу элементов И записи операндов и контрольных кодов операндов, регистры операндов и регистры контрольных кодов операндов, выходы которых подключены ко входам схемы контроля по модулю и сумматору, а также элементы ИЛИ и элемент И, причем выход первого элемента ИЛИ соединен с управляющими входами одной группы элементов И записи опершадов и контрольных кодов операндов, выход второго элемента ИЛИ - с управляющими входами второй группы элементов И записи операндов и контрольных кодов операндов, выходы третьего элемента ИЛИ - со входами сброса первого регистра операндов и соответствующего регистра контрольного кода, выход четвертого элемента ИЛИ - со входами сброса другого регистра операнда и соответствующего регистра контрольного кода, первые входы первого и второго элементов ИЛИ соединены с первым выходом блока управления, вторые входы первого, второго, третьего и четвертого элементов ИЛИ соединены соответственно с третьим, четвертым, пятым и шестым выходами блока управления, входы элемента И соединены с выходами разрядов первого регистра

кода операнда, а выход элемента И подключен ко входу блока управления 2.

Для известного устройства присущи низкая вероятность обнаружения ошибок и невозможность коррекции обнаруженных ошибок.

Цель изобретения - повышение надежности работы устройства за счет повышения вероятности обнаружения ошибок и их коррекции.

Поставленная цель достигается тем, что устройство, сГодержащее регистры первого и второго операндов и регистры контрольных кодов операндов, входы которых являются информационными входами устройства, блок модульных сумматоров, первая группа информационных входов которого соединена с выходами регистра первого операнда и ргегистра контрольного кода первого операнда, три группы элементов И, блок управления, оно содержит три блока памяти, четвертую группу элементов И, три сумматора, блок умножения, причем выходы регистра второго операнда и регистра контрольного кода второго операнда соединены с адресными входами первого блок памяти и с первыми входами элементов И певой группы, вторые входы которых соединены между собой и с первым выходом блока управления, выходы элементов И первой группы соединены со второй группойинформационных входов блока модульных сумматоров, первая группа входов блока умножения соединена с информационными выходами первого блока памяти, вторая группа входов блока умножения соединена с выходами регистра первого операнда и регистра контрольногб кода первого операнда, выходы блока умножения соединены с первыми входами элементов И второй группы, вторые входы которых соединены между собой и со вторым выходом блока управления, выходы элементов И второй группы и выходы элементов И третьей группы соединены со входами первого сумматора, выходы которого и выходы блока модульных сумматоров и третьего сумматора соединены с соответствующими входами второго сумматора и с первыми входами соответствующих элементов И третьей группв, с выходами третьего сумматора и с соответствующими входами регистра первого операнда и регистра контрольного кода первого операнда, первые входы элементов И третьей группы соединены с соответствующими выходами блока I модульных сумматоров,, вторые входы объединены и подключены . к третьему выходу блока управления, выходы элементов И четвертой гругаты соединены с соогветсгвзоощими входами регистра первого операнда и регистра контрольного кода первого операнда, а также с адресными входами второго, блока памяти, информационные выходы которого соединены

с соответствующими входами третьего сумматора, выходы второго сумматора соединены с адресными входами третьего блока памяти, информационные выходы которого соединЬны

с соответствующими входами второй группы входов блока модульных сумматоров, вторые входы элементов И четвертой группы объединены и подключены к четвертому выходу блока управления, выходы регистра первого

операнда и регистра контрольного кода первого операнда являются выходом устройства, пятый, шестой и седьмой выходы блока управления соединены с соответствующими управляющими входами блока модульных сумматоров, первый, второй и третий входы блока управления являются соответственно входами Умножение, Вычитание и Сложение устройства, а также тем, что блок управления содержит пять элементов И, четыре элемента ИЛИ, узел задержки, вход которого соединен с выходом первого элемента ИЛИ, первый вход которого является первым входом блока и соединен с первыми входами первого и четвертого элементов И, первый вход второго элемента ИЛИ соединен с первым входом второго элемента И и является вторым входом блока, второй вход второго элемента ИЛИ соединен с первым входом третьего элемента И и третьим входом первого элемента ИЛИ и является третьим вхйдом блока, вторые входы первого, второго и третьего элементов И объединены и подключены к первому выходу узла задержки, выходы первого, второго элементов И и третьего элемента ИЛИ являются соответственно пятым, шестым и седьмым выходами блока, выход третьего элемента И соединен с первым входом третьего элемента ИЛИ, первый вход элемента И соединен с выходом второго элемента ИЛИ, вто;рые входы четвертого, и пятого элементов И соединены с первым входом четвертого элемента ИЛИ и со вторым выходом узла задержки, вторые входы третьего и четвертого элементов ИЛИ соединены соответственно с третьим и четвертым выходами узла задержки, выходы пер5 вого элемента ИЛИ, четвертого и пятого элементов И, четвертого элемента ИЛИ являются соответственно первым, вторым, третьим и четвертым выходами блока управления.

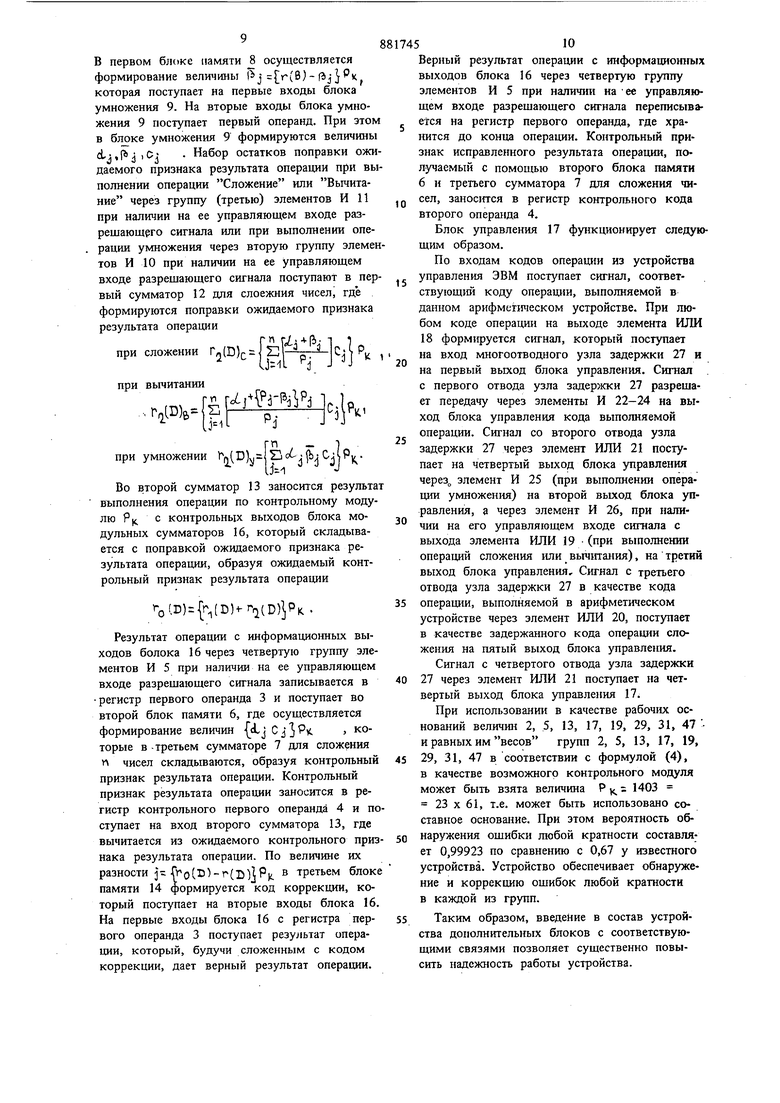

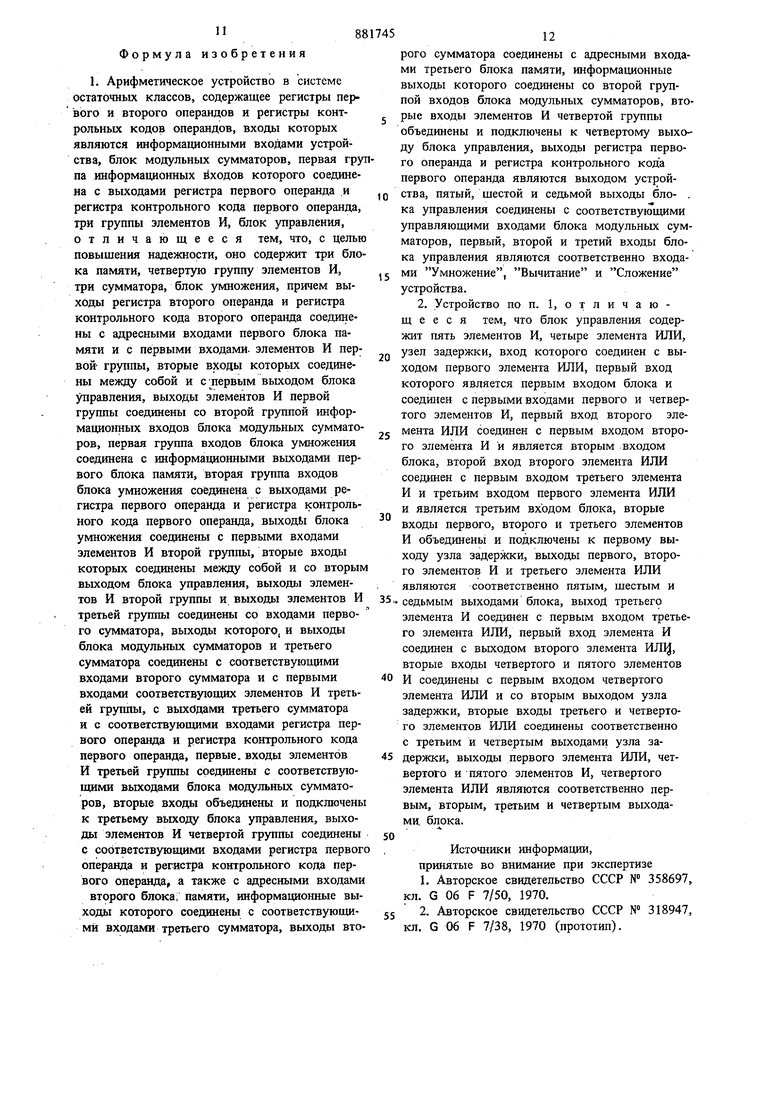

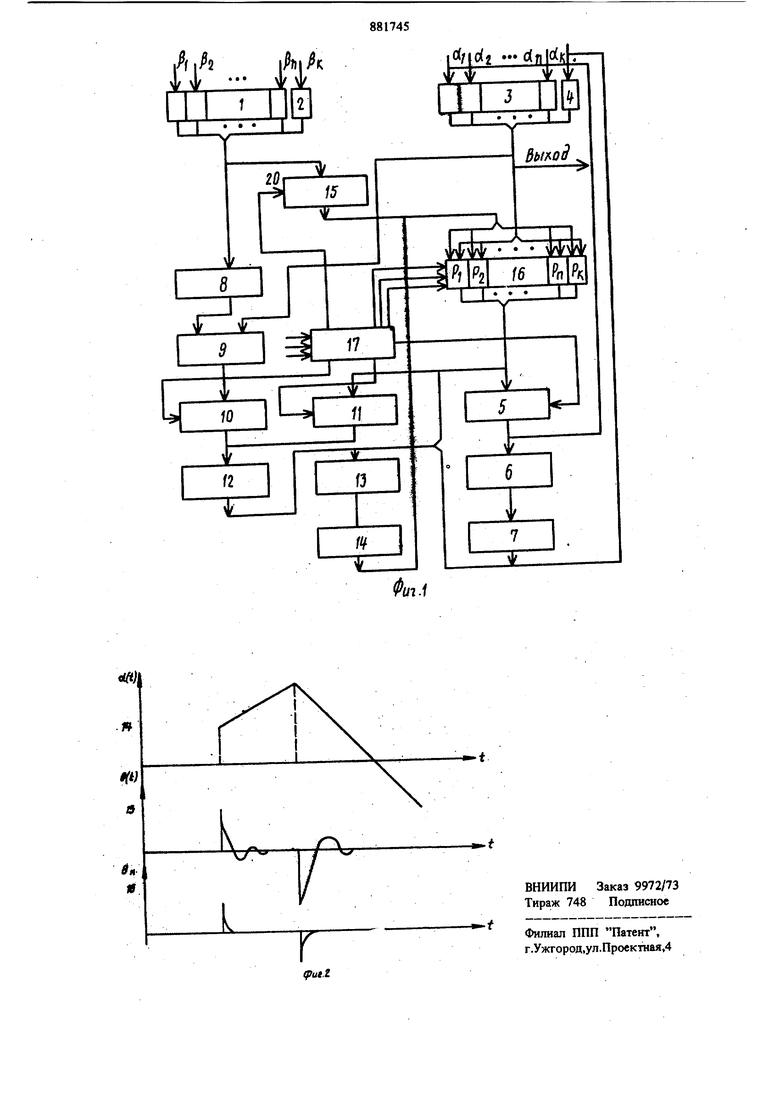

На фиг. 1 представлена блок-схема устрой0 ства; на фиг. 2 - блок-схема блока управления..

Устройство содержит регистр первого операнда 1, регистр контрольного кода первого опершада 2, регистр второго операнда 3, регистр

5 контрольного кода второго операнда 4, четвертая группа элементов И 5, второй блок памяти 6, третий сумматор 7, первый блок памяти 8, блок умножения 9, вторая и третья группы элементов И 10 и 11, первый и второй сумматоры 12 и 13, третий блок памяти 14, первая группа элементов И 15, блок модульных сумматоров 16, блок управления 17 первый-четвертый элементы ИЛИ 18-21, первый-пятый элементы И 22-26, узел задержки 27. Устройство реализует алгоритмы обнаружения ошибок способом взвешенных групп, который заключается в следующем. Каждый из операндов и результат операции сопровождаются контрольным признаком. Контрольный признак получается следующим образом. Код операнда разбивается на группы определенной разрядности- в соответствии с представлением информации в СОК в виде набора остатков по выбранной совокупности оснований. Код группы, рассматриваемый как некоторое число d. , умножается на соответствующий вес 0 От суммы полученных произведений вычисляется остаток по контрольному модулю в соответствии с выражением.|l где п - число оснований в СОК, обеспечивающих рабочий Диапазон; - контрольный модуль, знак обозначает вычисление остатка величины X по модулю РКВ качестве весовых коэффигщентов с-/ бе рутся числа, выбираемые Из приведенного ниже выражения (3), либо величины соответству щих рабочих оснований Р . Величина контрольного модуля выбирается из следующих условий. Для условия однознач ного соответствия мехсду величиной ошибки представления и контрольным признаком операнда (1) необходимо, чтобы величина модул превышала число всевозможных сбоев, обнару жение и исправление которых возможно для данного способа, т.е. п ... РК , где К, - разрядность i -ой группы. Для обеспечения однозначности необходимо соблюдать условие неравенства между собой контрольных признаков при возникновении сбоев в любой из групп, т.е. ) где GH (.Sj)- величина ошибок в i -ой ( j -той) группах, или в общем виде АЛ ,.-оислр; 40, (г) lil Л О где знак Л % i оз ачает вычисление конъюкци величин х Выражение (3) малоудобио, ввиду сложноси решения неравенств в булевой алгебре, потому для практических расчетов можно испольовать выражение б С -йхС; , , РК а W где а - любое из натурального ряда чисел. К величинам веса и контрольного 1одуля могут быть предъявлены следующие требования. При равных значениях ошибок по разным основаниям, т.е. npHQ, , выражение (2) преобразуется к виду. {Q(C.-Cj)}P,, Т.е. контрольный модуль Рц. должен быть величиной взаимно простой с разностями выбранных весов, так как в противном случае возможно невыполнение условия (2), либо величина контрольного модуля должна удовлетворять условию p vncni С(С:;-&р. Величина Q (с - Oi) меньше произведения двух наибольших оснований, в то время как в СОК для целей контроля необходимо обеспечить-выбор контрольного основания в соответствии с выражением (4) р аРп-Рп-.. где PVI и - мakcимaльныe из рабочих оснований. Следовательно, способ взвешенных групп потенциально требует меньших контрольных оснований, чем известные, и позволяет использовать параллельный способ формирования и обработки соответствующих констант, что приводит к возможности получення высокой скорости выполнения операции контроля. При выполнении арифметических операций каждый операнд сопровождается контрольным признаком, вычисленным в соответствии с выражением (1), т.е., если А и В операнды некоторой арифметической операции, то При выполнении операции над кодами этих чисел из контрольных признаков чисел формируется величина r,(D){r(A)r(b)PK, где - знак вьшолнения соответствующей операции. При сложении и вычитании по рабочим основаниям получают clj tcL5 lij}PKи при cl-.j fb ; 7 РО происходит Потеря необходимой для правильного вычисления контро ного признака результата операции, т.е. потеря величины I ilA Jtгде знак Г - целая часть величины X. Следовательно VD){r-,(DHr(D)}PK , Ь При выполнении операции умножения фор мируется величина (iic.jC)%(i: ibjCj)i: (. ..,-c rfba-|;tijCj.-jij-|.jib.,c + SJ.jC(p(b.). IiJ.-lb-Ci Аиб-Г (-Ь ) 3 I 3 Jjr,j J 3 | J J 3 или по контрольному основанию в сок ro(Ax0),i.,}P,(,, -,D)(r:(A),4 D)4P,- IP j С j{r (Б)- . ,(8) Следовательно, вычисление контрольных признаков результатов операций по контроль ным признакам операндов заключается в вы числении результата операции над контроль.ными признаками ir(D) ,в вычислении в со ответствии с формулами (5) или (8) поправок контрольных признаков результатов операции (D), а также в вычислении ожидаемых контрольных признаков VQ D) р зультатов операции в соответствии с форму лами (6) или (7). При произведении вычисления контрольно признака результата операции в соответствии с формулой (1) ..„ r(5,){H(jCj}p,. и. затем сравнении величины r(D) и Гр(1з величина их разности несет информацию о величине и месте ошибки, что позволяет ле ко ее скорректировать. Регистры операндов 1 и 3 и регистры контрольных кодов операндов 2 и 4 предназначены для хранения операндов арифметического устройства и их контрольных кодов. Группы элементов И 5, 10, 11 и 15 обеспечивают передачу информации при наличии на их управляющих входах разрешающих сигналов. Блок моду;п ных сумматоров 16 в зависимости от кода операции на управляющим входе реализует соответствующую арифметическую операцию над кодами операндов, их контрольными кодами и формирует поправку ожидаемого признака результата операции (при выполнении операций Сложение и Вычитание). Второй блок памяти 6 по кодам групп результата операции выдает остатки по контрольному модулю произведений кодов групп на соответствующие коды весовых коэффициентов групп. Первый блок памяти 8 вьщает модифицированный код первого операнда, остатки которого по каждому рабочему основанию равны разности по контрольному модулю меясду контрольным кодом первого операнда и кодом соответствующего остатка. Третий блок памяти 14 по коду разности по контрольному модулю меисду контрольным признаком результата операции, и его ожидаемой величиной выдает код коррекции результата операции, первый и третий сумматоры 12 и 7 для сложения п чисел обеспечивают суммирование по контрольному модулю кодов всех п групп обрабатываемого числа. Блок умножения 9 обеспечивает перемножение по контрольному модулю соответствующих кодов групп первого модифицированного и второго операндов. Второй сумматор 13 обеспечивает последовательное сложение чисел, подаваемых на его входы, и хранение полученных сумм. Блок управле ния 17 в соответствии с кодом операции формирует на выходах управляющие сигналы, обеспечивающие вьтполнение операции и коррекцию ее результата. Устройство работает следующим образом. Операнды хранятся на регистрах операндов 1 и 2, а юс. контрольные признаки на регистрах 2 и 4. При выполнении операции второй операнд непосредственно, а первый операнд через группу элементов И 15 при наличии на ее управляющем входе разрешающего сигнала поступает в блок 16, в котором в зависимости от кода операции вьшолняется требуемая операция по всем основаниям СОК, включая контрольные. В результате этого на информационных выходах блока 16 формируются наборы остатков, поправки по контрольному модулю ожидаемых контрольных признаков результатов операции Сложение или Вьиитание и результаты соответствующих операций в СОК. в первом блоке памяти 8 осуществляется формирование величины 1 j {|г(6)-(3j Рк которая поступает на первые входы блока умножения 9. На вторые входы блока умножения 9 поступает первый операнд. При это в блоке умножения 9 формируются величины cL-,(.:, С: . Набор остатков поправки ожи даемого признака результата операции при вы полнении операции Сложение или Вычитание через группу (третью) элементов И 11 при наличии на ее управляющем входе разрешающего сигнала или при выполнении операции умножения через вторую группу элеме тов И 10 при наличии на ее управляющем входе разрешающего сигнала поступают в пер вый сумматор 12 для слоежния чисел, где формируются поправки ожидаемого признака результата операции при сложении )-:: (а PJ при вычитании . ,„, г -4№ -fel-р-при умножении МО)(Ь CjsP(,. U-1Во второй сумматор 13 заносится результа выполнения операции по контрольному моду лю Р| с контрольных выходов блока модульных сумматоров 16, который складывается с поправкой ожидаемого признака результата операции, образуя ожидаемый контрольный признак результата операции ofD) {r(D)r(D)JPK Результат операции с информационных выходов болока 16 через четвертую группу эле ментов И 5 при наличии на ее управляющем входе разрешающего сигнала записывается в регистр первого операнда 3 и поступает во второй блок памяти 6, где осуществляется формирование величин cLj , которые в -третьем сумматоре 7 для сложения п чисел складываются, образуя контрольный признак результата операции. Контрольный признак результата операции заносится в регистр контрольного первого операнда 4 и по ступает на вход второго сумматора 13, где вычитается из ожидаемого контрольного приз нака результата операции. По величине их разности третьем блок памяти 14 формируется код коррекции, который поступает на вторые входы блока 16 На первые входы блока 16 с регистра первого операнда 3 поступает результат операции, который, будучи сложенным с кодом коррекции, дает верный результат операции. 10 Верный результат операции с информацношгых выходов блока 16 через четвертую группу элементов И 5 при налнч1ш на ее управляющем входе разрешающего сигнала перепнсывается на регистр первого операнда, где хранится до конца операции. Контрольный признак исправленного результата операции, получаемый с помощью второго блока памяти 6 и третьего сумматора 7 для сложения чисел, заносится в регистр контрольного кода второго операнда 4. Блок управления 17 функционирует следующим образом. По входам кодов операции из устройства управление ЭВМ поступает сигнал, соответствующий коду операщ1н, выполняемой в данном арифметическом устройстве. При любом коде операции на выходе элемента ИЛИ 18 форм1фуется сигнал, который поступает на вход многоотводного узла задержки 27 и на первый выход блока управления. Сигаал с первого отвода узла задержки 27 разрешает передачу через элементы И 22-24 на выход блока управления кода выполняемой операции. Сигнал со второго отвода узла задержки 27 через элемент ИЛИ 21 поступает на четвертый выход блока управления через элемент И 25 (при выполнении операции умножения) на второй выход блока управления, а через элемент И 26, при наличии на его управляющем входе сигнала с выхода элемента ИЛИ 19 (при выполнении операций сложения или вычтания), на третий выход блока управления. Сигнал с третьего отвода узла задержки 27 в качестве кода операции, выполняемой в арифметическом устройстве через элемент ИЛИ 20, поступает в качестве задержанного кода операции сложения на пятый выход блока управления. Сигнал с четвертого отвода узла задержки 27 через элемент ИЛИ 21 поступает на четвертый выход блока управления 17. При использовании в качестве рабочих оснований величин 2, 5, 13, 17, 19, 29, 31, 47 и равных им весов групп 2, 5, 13, 17, 19, 29, 31, 47 в соответствии с формулой (4), в качестве возможного контрольного модуля может быть взята величина Р к. 1403 23 X 61, т.е. может быть использовано составное основание. При этом вероятность обнаружения ощибки любой кратности составляет 0,99923 по сравнению с 0,67 у известного устройства. Устройство обеспечивает обнаружение и коррекцию ошибок любой кратности в каждой из групп. Таким образом, введение в состав устройства дополнительных блоков с соответствующими связями позволяет существенно повысить надежность работы устройства. 118 Формула изобретения 1. Арифметическое устройство в системе остаточных классов, содержащее регистры первого и второго операидов и регистры контрольных кодов операндов, входы которых являются информационными входами устройства, блок модульных сумматоров, первая гру па информационных йходов которого соединена с выходами регистра первого операнда и регистра контрольного кода первого операнда, три группы элементов И, блок управления, отличающееся тем, что, с целью повыщения надежности, оно содержит три бло ка памяти, четвертую группу элементов И, три сумматора, блок умножения, причем выходы регистра второго операнда и регистра контрольного кода второго операнда соединены с адресными входами первого блока памяти и с первыми входами, элементов И первой группы, вторые входы которых соединены между собой и с первым выходом блока управления, выходы элементов И первой группы соединены со второй группой информационных входов блока модульных сумматоров, первая грзшпа входов блока умножения соединена с информационными выходами первого блока памяти, вторая группа входов блока умножения соединена с выходами регистра первого операнда и регистра контрольного кода первого операнда, выходЬ блока умножения соединены с первыми входами элементов И второй группы, вторые входы которых соединены между собой и со вторым выходом блока управления, выходы элементов И второй группы и выходы элементов И третьей группы соединены со входами первого сумматора, выходы которого, и выходы блока модульных сумматоров и третьего сумматора соединены с соответствующими входами второго сумматора и с первыми входами соответствующих элементов И третьей группы, с выходами третьего сумматора и с соответствующими входами регистра первого операнда и регистра контрольного кода первого операнда, первые, входы элементов И третьей группы соединены с соответствующими выходами блока модульных сумматоров, вторые входы объединены и подключены к третьему выходу блока управления, выходы элементов И четвертой группы соединены с соответствующими входами регистра первог операнда и регистра контрольного кода первого операнда, а также с адресными входами второго блока; памяти, информационные выходы которого соединены с соответствующимй входами третьего сумматора, выходы второго сумматора соединены с адресными входами третьего блока памяти, информационные выходы которого соединены со второй группой входов блока модульных сумматоров, вторые входы элементов И четвертой группы объединены и подключены к четвертому выходу блока управления, выходы регистра первого операнда и регистра контрольного кода первого операнда являются выходом устройства, пятый, шестой и седьмой выходы бло- , ка управления соединены с соответствующими управляющими входами блока модульных сумматоров, первый, второй и третий входы блока управления являются соответственно входами Умножение, Вычитание и Сложение устройства. 2. Устройство по п. 1, отличающее с я тем, что блок управления содержит пять элементов И, четыре элемента ИЛИ, узел задержки, вход которого соединен с выходом первого элемента ИЛИ, первый вход которого является первым входом блока и соединен с первыми входами первого и четвертого элементов И, первый вход второго элемента ИЛИ соединен с первым входом второго элемента И и является вторым входом блока, второй вход второго элемента ИЛИ соединен с первым входом третьего элемента И и третьим входом первого элемента ИЛИ и является третьим входом блока, вторые входы первого, второго и третьего элементов И объединены и подключены к первому выходу узла задержки, выходы первого, второго элементов И и третьего элемента ИЛИ являются соответственно пятым, шестым и седьмым выходами блока, выход третьего элемента И соединен с первым входом третьего элемента ИЛИ, первый вход элемента И соединен с выходом второго элемента ИЛЦ, вторые входы четвертого и пятого элементов И соединены с первым входом четвертого элемента ИЛИ и со вторым выходом узла задержки, вторые входы третьего и четвертого элементов ИЛИ соединены соответственно с третьим и четвертым выходами узла задержки, выходы первого элемента ИЛИ, четвертого и пятого элементов И, четвертого элемента ИЛИ являются соответственно первым, вторым, третьим и четвертым выходами, блока. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 358697, кл. G 06 F 7/50, 1970. 2.Авторское свидетельство СССР № 318947, кл. G 06 F 7/38, 1970 (прототип).

./г

;

Авторы

Даты

1981-11-15—Публикация

1980-01-09—Подача