выходы первых (n-1) мультиплексоров и второй выход Л-го мультиплексора соединены с соответствующими входами блока коррекции результата, выходы которого соединены с управляющими входами мультиплексоров второй групп при этом блок выравнивания номера контролируемого разряда содержит л групп элементов И, выходы которых соединены с входами элементов ИЛИ группы, выходы которых соединены с входами блока хранения констант выравнивания, первые входы элементов ИИ групп соединены с первыми выходами соответствукнцих входных регистров группы, вторые входы элементов И п групп соединены с соответствующими выходами дешифратора, а третьи входы объединены и соединены с выходом схемы сравнения, выход блока хранени констант всфавнивания соединен с третьим входом входного регистра кон рольньЕК разрядов, блок коррекции контрольного разряда содержит группу из 2п-1 элементов И, группу из элементов ИЛИ, элемент ИЛИ, элемент НЕ, причем первый, второй и (и+1)-й входы элемента ИЛИ подключены соответственно к выходам первого, второго и ()-го элементов И группы, выходы Й-го и (С+1)-го элементов И группы (И 3,5,...,2п-3) подключены соответственно к входам C()/2J-x элементов ИЛИ группы, выход элемента ИЛИ непосредственно и через элемент НЕ соединен соответственно с третьим и четвертым входами сумматора контрольных разрядов, первые входы элементов И группы соединены с выходами переносов и возможных переносов соответствующих сумматоров

170

рабочиз разрядов, вторые входы li-x и (К.+ 1)-х элементов И группы (,3,..., 2vi-3) попарно объединены и подключены к соответствующим выходам дешифратора, второй вход (2п-1)го элемента И группы соединен с соответствующим выходом дешифратора, выходы элементов ШШ группы соединены ,с третьими входами (t-l)-x элементов И группы и с соответствующ Ф1н входами

элемента ШШ, блок обнаружения ошибки содержит ;И групп элементов JH, rpyriny элементов ИЛИ, блок хранения констант нулевизации, сумматор нулевизации, блок хранения поправок и сумматор поправок, при этом выходы ул групп элементов И соединены с входами

соответствующих элементов ИЛИ группы, выходы которых соединены с входами блока хранения констант нулевизацни

и первым.входом сумматора поправок, выход блока хранения констант нулевизации соединен с первым входом Сумматора нулевизации, первый выход которого соединен с входом блока хранения поправок, выход которого соединен с вторым входом суЮ(1атора поправок, группа выходов которого соединена с вторыми группами инфо1 1ационных входов соответствующих мультиплексоров первой группы, а третий вход сумматора поправок и второй вход сумматора нулевизации объединены и подключены к выходу сумматора контрольных разрядов, вькод сумматора нулевизации соединен с вторыми входами элементов И-НЕ группы, первые и вторые входы элементов И п групп соединены соответственно с выxoдa я сумм суьматоров. рабочих разрядов группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения многоразрядных @ -ичных чисел | 1983 |

|

SU1163321A1 |

| Арифметическое устройство по модулю | 1983 |

|

SU1120325A1 |

| @ -Ичный сумматор | 1983 |

|

SU1166097A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для резервирования | 1983 |

|

SU1168947A1 |

| Устройство для обнаружения и исправления ошибок в системе остаточных классов | 1980 |

|

SU888124A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Устройство для умножения S-ичных цифр в позиционно-остаточной системе счисления | 1991 |

|

SU1837284A1 |

СУММАТОР В СИСТЕМЕ ОСТАТОЧ-: НЫХ КЛАССОВ, содержащий группу из П входных регистров ( п- количество рабочих С), -ичных разрядов) , входы которых являются входами слагаемых сумматора, блок коррекции результата, группу из п сумматоров рабочих разрядов, входы которых подключены к выходам соответствующих входных регистров группы, отличающийся тем, что, с целью повышения достоверности суммирований, он содержит входной регистр контрольных разрядов, регистр номеров контролируемых разрядов, сумматор контрольных разрядов, схему сравнения, дешифратор, первую изИ+1 и вторую из п-1 группы мультиплексоров, группу элементов И-НЕ,блок. обнаружения ошибки, блок выравнивания номера .контролируемого разряда и блок коррекции контрольного разряда, причем первьй и второй входы входного регистра контрольных разрядов являются входами контрольных разрядор слагаемых, а первый и второй выходы соединены с первым и вторым входами сумматора контрольных разрядов, выход которого соединен с первой группой информационных входов- (п+1)-го мультиплексора первой группы, первые группы информационных входов с первого по (л-1)-й мультиплексоров первой группы соединены соответственно с выходами сумм, сумм, увеличенных на единицу, переносов и возможных переносов с первого по (i.-l)-H сумматоров рабочих разрядов группы, первая группа информационных входов п-го мультиплексора первой группы соединена соответственно с выходами суммы и суммы, увеличенной на единицу, ц-го сумматора рабочих разрядов группы, первый и второй входы регисто S ра номеров контролируемых разрядов О) являются входами номеров контролируемых разрядов слагаемых суиматора, а первый и второй выходы соединены с соответствующими входами схемы сравнения, второй выход регистра номеров контролируемых разрядов яв ляется выходом номера контролируемого разряда сумматора и соединен с входом дешифратора, выходы которого соединены с первьми входами эле-, ментов И-НЕ группы, выходы которых соединены с управляющими входами мультиплексоров первой группы, первьй и второй выходы с первого по ()-й мультиплексоров первой группы соединены с информационными входами соответствуюпрпс мультиплексоров второй группы, выходы которых являются выходами результата сумматора, первый выход к-го и выход (И + 1)-го мультиплексоров первой группы являются соответственно выходом разряда результата и выходом контрольного разряда сумматора, третий и четвертый

I.

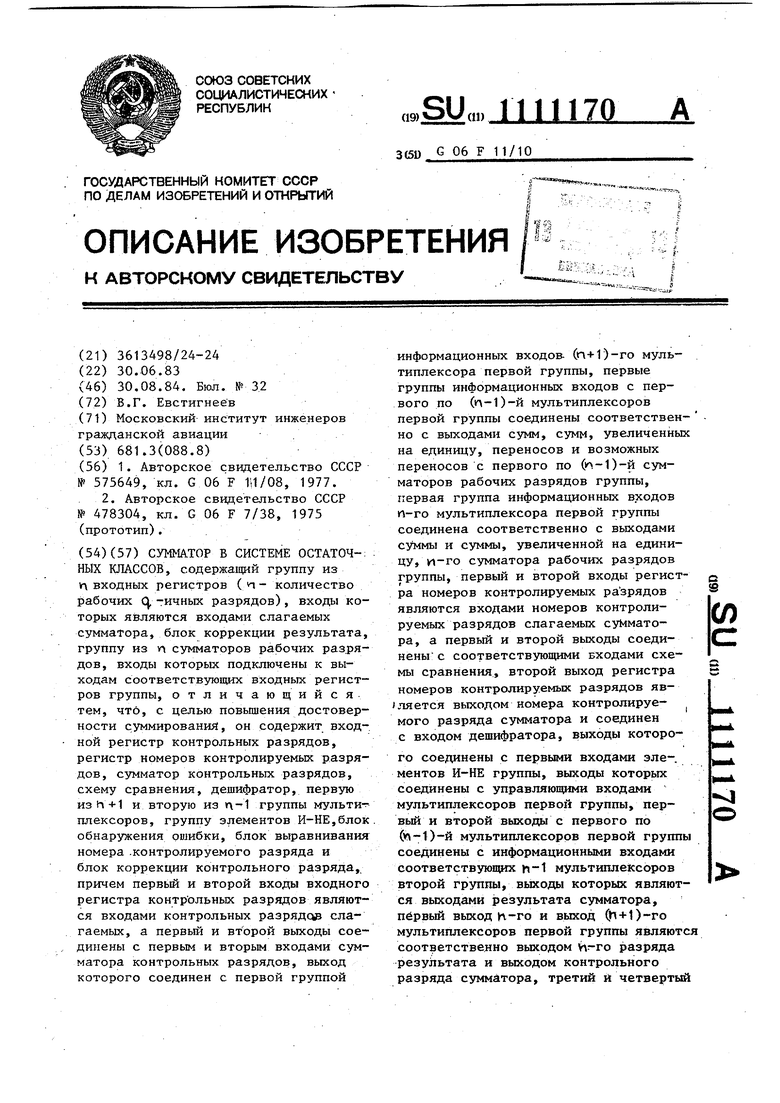

Изобретение относится к области вычислительной техники и может быть использовано при разработке быстродействующих арифметических устройств современных цифровых вычислительных машин.

Известен сумматор m-рядных )«-ичных чисел, содержащий w групп по и суммирующих блоков, коммутаторы,входные регистры, блоки обнаружения ошибок кратности +1, индикаторы неисправности, блок разрешения обмена,.

блок перебора сочетаний и соответствующие связи Г11.

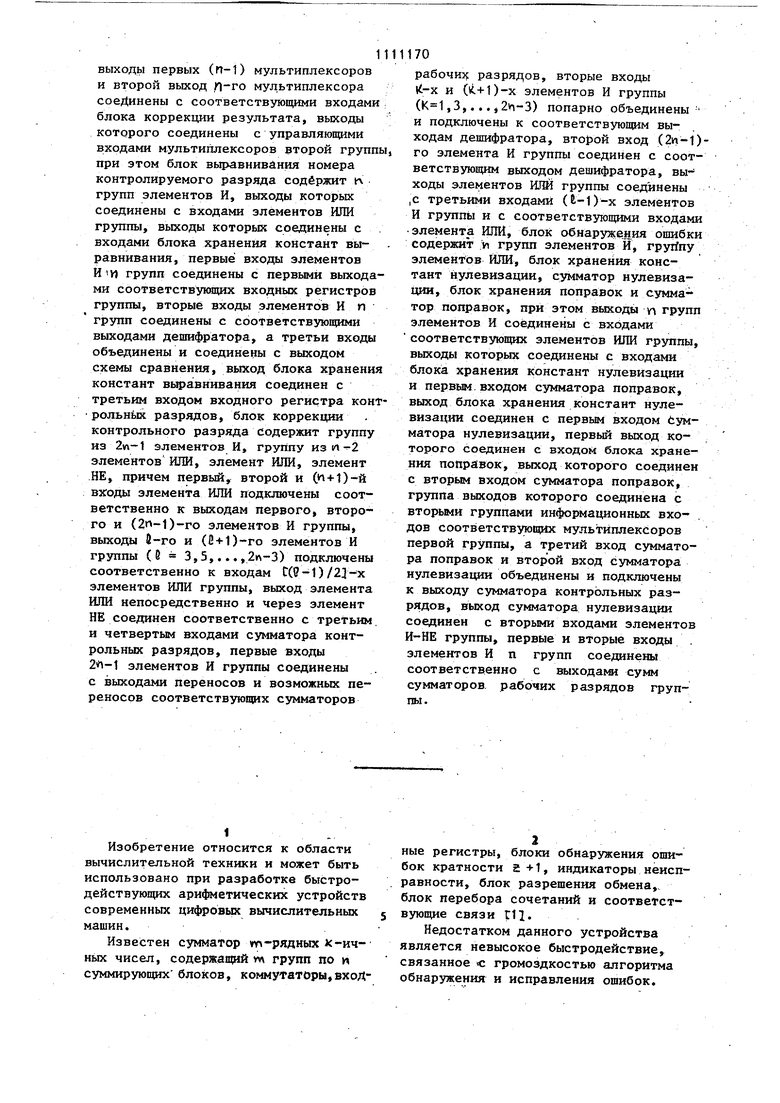

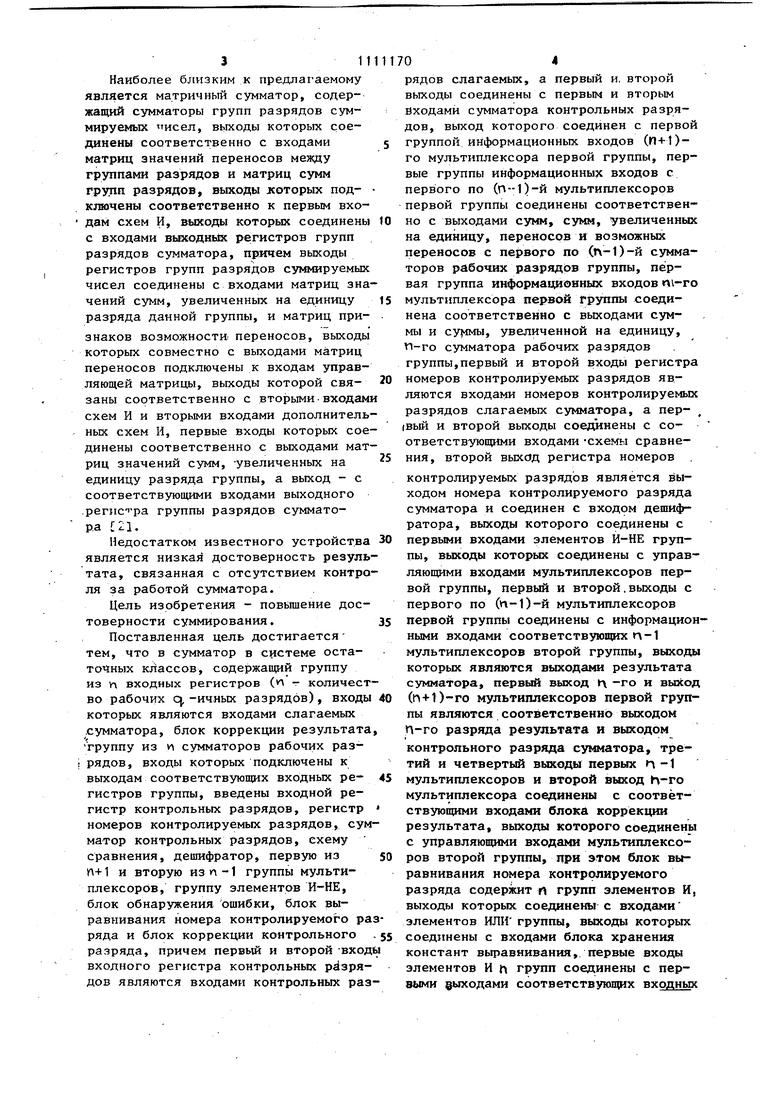

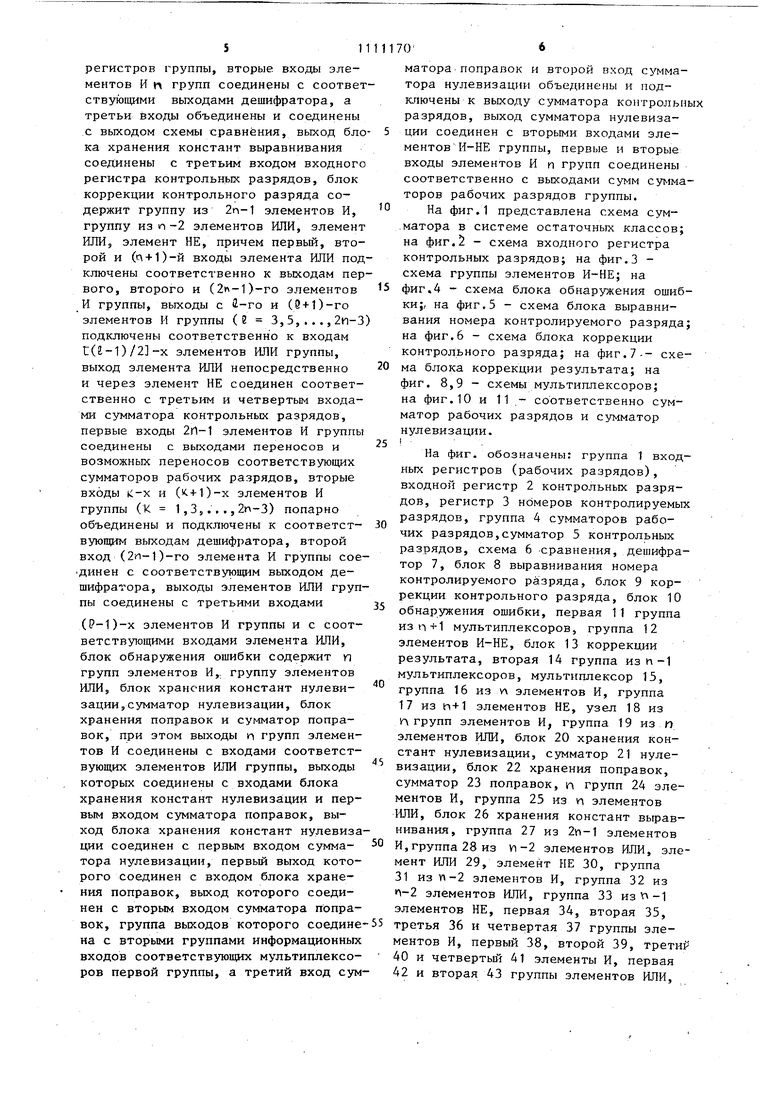

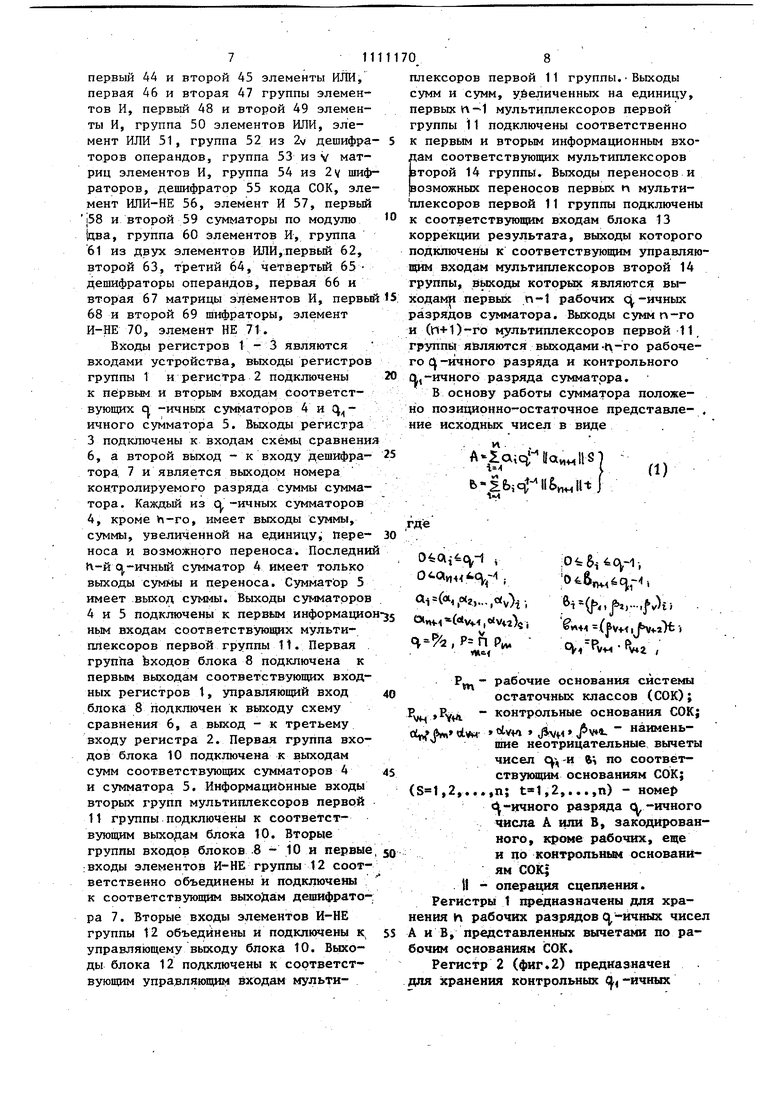

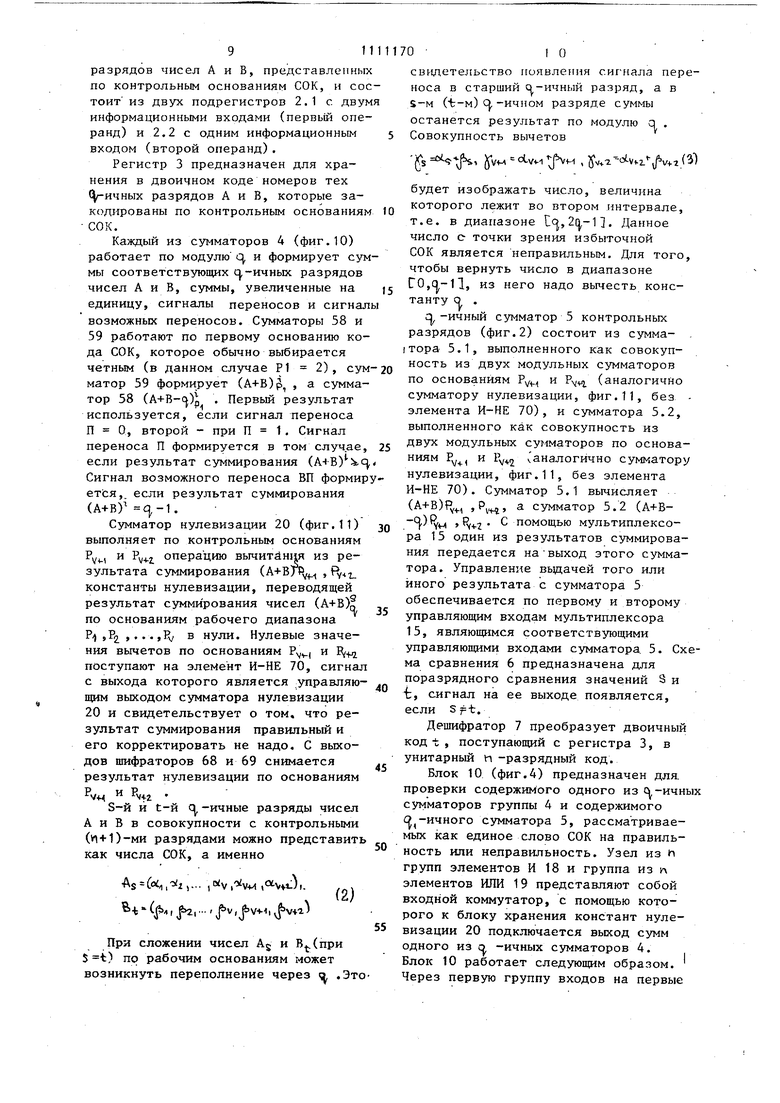

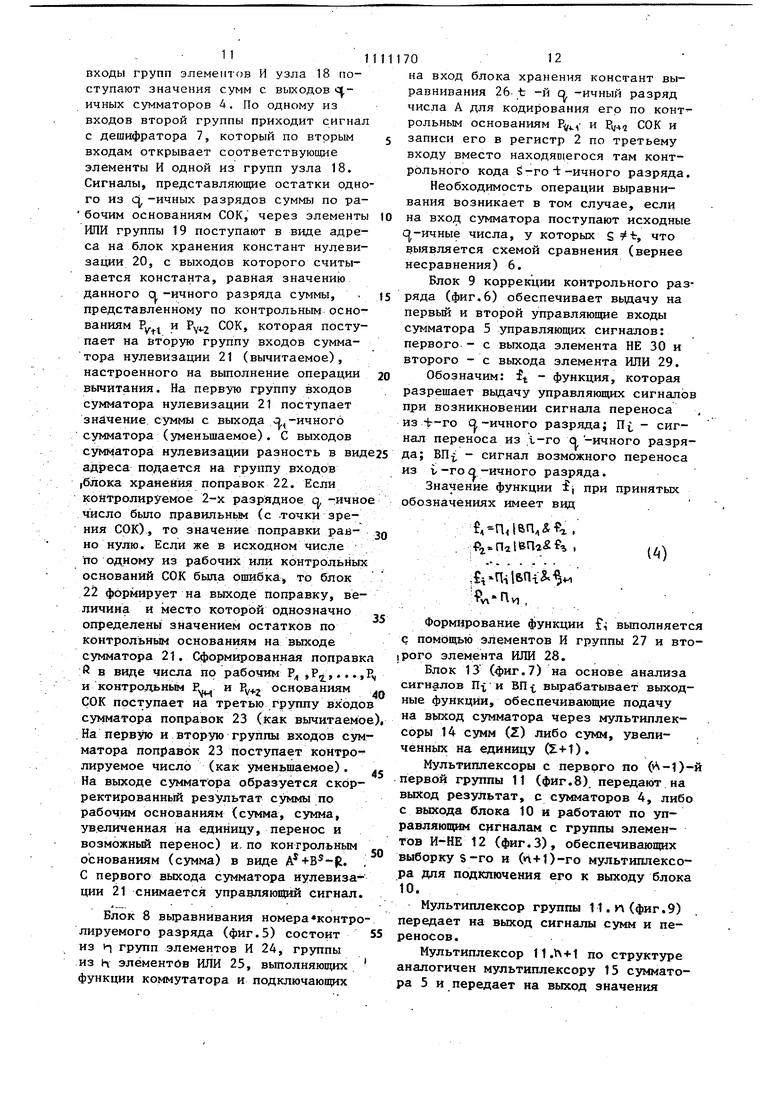

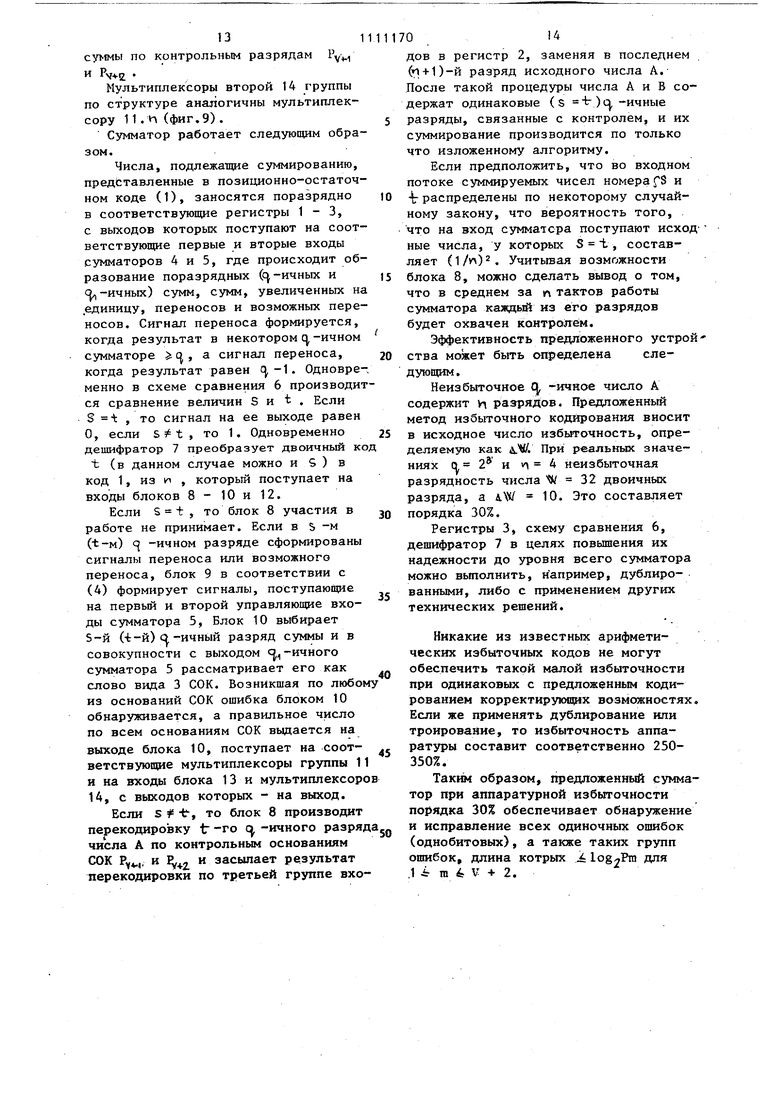

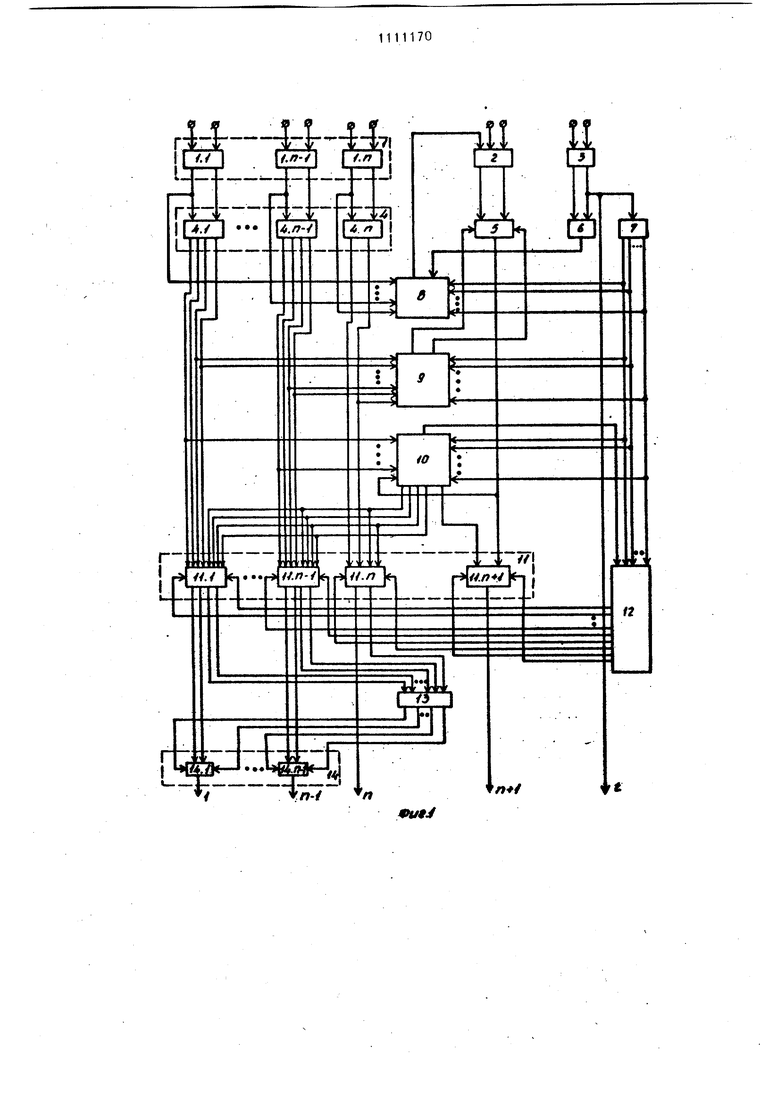

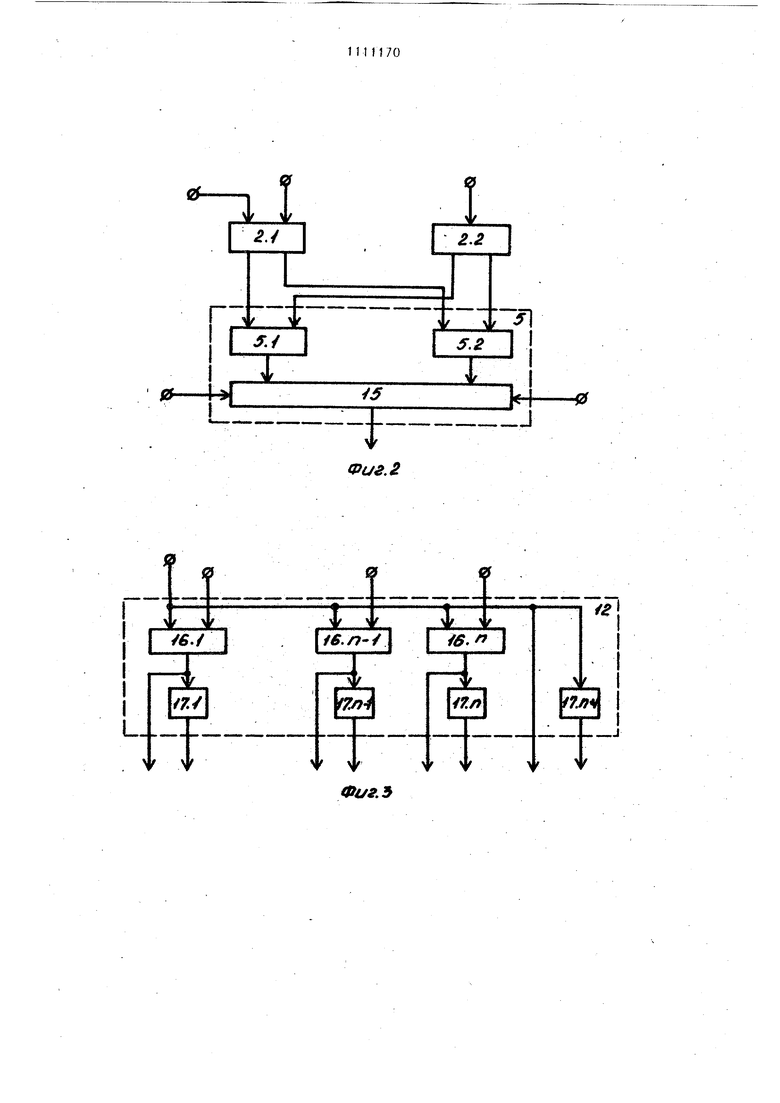

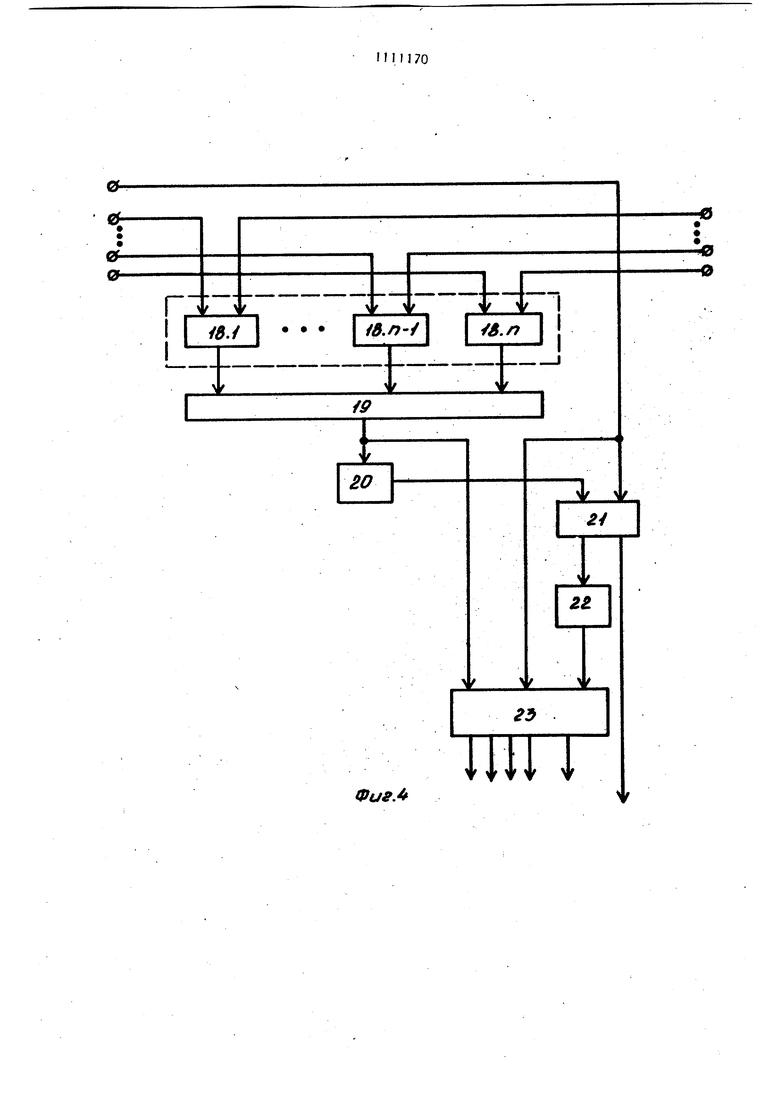

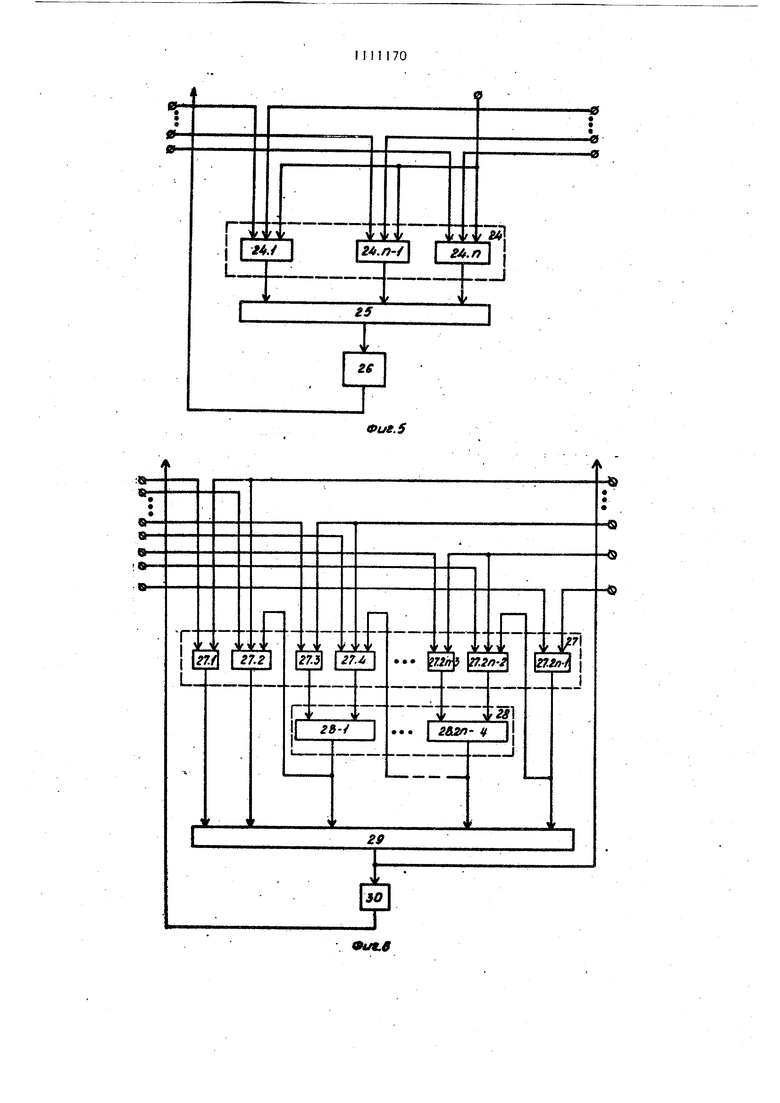

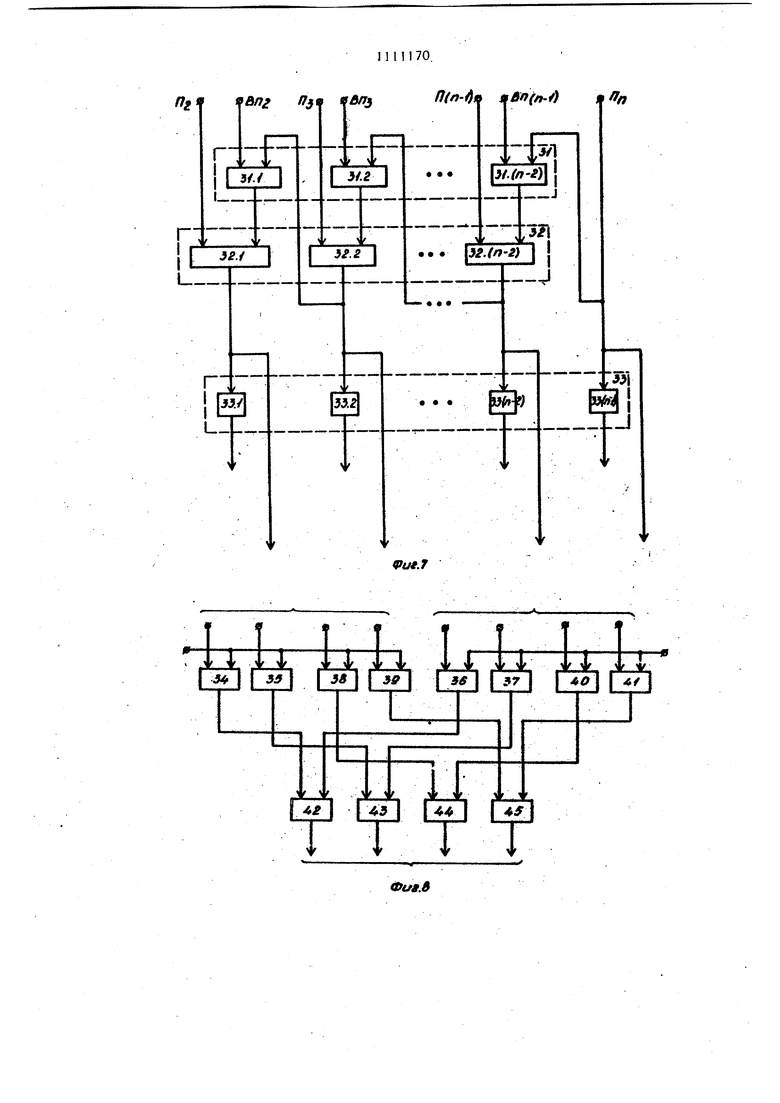

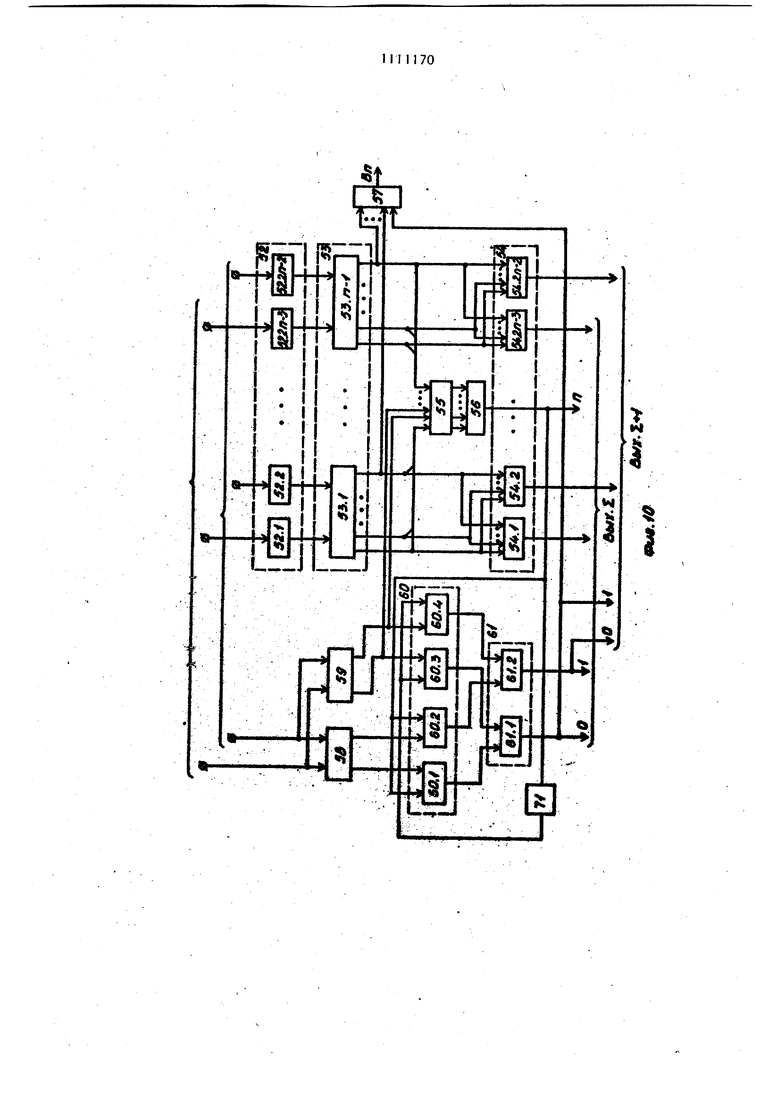

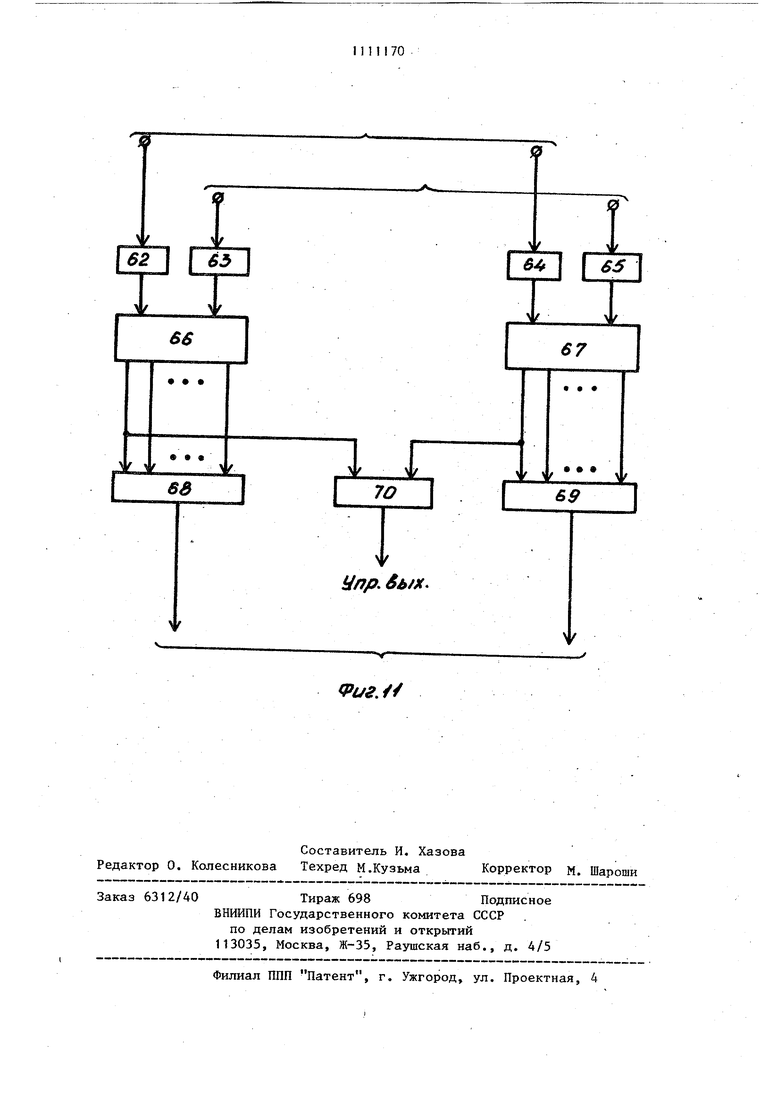

Недостатком данного устройства является невысокое быстродействие, связанное -с. громоздкостью алгоритма обнаружения и исправления ошибок. 31 Наиболее близким к предлагаемому является матричный сумматор, содержащий сумматоры групп разрядов сумMHpyei H ix исел, вьгходы которых соединены соответственно с входами матриц значений переносов между группами разрядов и матриц сумм групп разрядов, выходы которых подключены соответетвенно к первым входам схем И, выходы которьк соединены с входами выходных регистров групп разрядов сумматора, причем выходы регистров групп разрядов суммируемых чисел соединены с входами матриц зна чений сумм, увеличенных на единицу разряда данной группы, и матриц признаков возможности переносов, выходы которых совместно с выходами матриц переносов подключены к входам управляющей матрицы, выходы которой связаны соответственно с вторь№1И входам схем И и вторыми входами дополнитель ных схем И, первые входы которых сое динены соответственно с выходами мат риц значений сумм, -увеличенных на единицу разряда группы, а выход - с соответствующими входами выходного .регистра группы разрядов сумматора 21. Недостатком известного устройства является низкая достоверность резуль тата, связанная с отсутствием контро ля за работой сумматора. Цель изобретения - повышение достоверности суммирования. Поставленная цель достигается тем, что в сумматор в системе остаточных классов, содержащий группу из ул входных регистров { т количест во рабочих q,-ичных разрядов), входы которых являются входами слагаемых сумматора, блок коррекции результата группу из у сумматоров рабочих разрядов, входы которых подключены к выходам соответствующих входных регистров группы, введены входной регистр контрольных разрядов, регистр номеров контролируемых разрядов, сум матор контрольных разрядов, схему сравнения, дешифратор, первую из п+1 и вторую из л -1 группы мультиплексоров, группу элементов И-НЕ, блок обнаружения ошибки, блок выравнивания номера контролируемого ра ряда и блок коррекции контрольного разряда, причем первый и второй -вход входного регистра контрольных р зрядов являются входами контрольных раз 04 рядов слагаемых, а первый и. второй выходы соединены с первым и вторым входами сумматора контрольных разрядов, выход которого соединен с первой группой информационных входов ()го мультиплексора первой группы, первые группы информационных входов с перв1ого по (П--1)-й мультиплексоров первой группы соединены соответственно с выходами сумм, сумм, увеличенных на единицу, переносов и возможных переносов с первого по (л-1)-й сумматоров рабочих разрядов группы, первая группа информационных входов мультиплексора первой группы соединена соответственно с выходами суммы и суммы, увеличенной на единицу, vi-ro сумматора рабочих разрядов группы,первый и второй входы регистра номеров контролируемых разрядов являются входами номеров контролируемых разрядов слагаемых сумматора, а пер(вый и второй выходы соединены с соответствующими входами -схемы сравнения, второй выход регистра номеров контролируемых разрядов является выходом номера контролируемого разряда сумматора и соединен с входом дешифратора, выходы которого соединены с первыми входами элементов И-НЕ группы, выходы которых соединены с управляющими входами мультиплексоров первой группы, первый и второй.выходы с первого по (п-1)-й мультиплексоров первой группы соединены с информационными входами соответствующих п-1 мультиплексоров второй группы, выходы которых являются выходами результата сумматора, первый выход Y -го и выход (n+t)-ro мультиплексоров первой группы являются соответственно выходом П-го разряда результата и выходом контрольного разряда сумматораf третий и четвертый выходы первых л -1 мультиплексоров и второй выход h-ro мультиплексора соединены с соотвётствз щими входами блока коррекции результата, выходы которого соединены с управляющими входами мультиплексоров второй группы, при этом блок выравнивания номера контролируемого разряда содержит г групп элементов И, выходы которых соединены с входами элементов ИЛИ группы, выходы которых соединены с входами блока хранения констант выравнивания,, первые входы элементов И h групп соединены с первыми выходами соответствующих входных регистров группы, вторые входы элементов И групп соединены с соотве ствующими выходами дешифратора, а третьи входы объединены и соединены с выходом схемы сравнения, выход бл ка хранения констант выравнивания соединены с третьим входом входног регистра контрольных разрядов, блок коррекции контрольного разряда содержит группу из 2п-1 элементов И, группу из п-2 элементов ИЛИ, элемент ИЛИ, элемент НЕ, причем первьй, второй и ((Л + 1)й входы элемента ИЛИ под ключены соответственно к выходам пер вого, второго и (2л-1)-го элементов И группы, выходы с й-го и (б+1)-го элементов И группы (И 3,5,...,2п-3 подключены соответственно к входам ll(S-1) элементов ИЛИ группы, выход элемента ИЛИ непосредственно и через элемент НЕ соединен соответственно с третьим и четвертым входами сумматора контрольных разрядов, первые входы 2)1-1 элементов И группы соединены с выходами переносов и возможных переносов соответствующих сумматоров рабочих разрядов, вторые входы ц-х и ( элементов И группы (К 1,3,...,2п-3) попарно объединены и подключены к соответствующим выходам дешифратора, второй вход (2п-1)-го элемента И группы сое динен с соответствующим выходом дешифратора, выходы элементов ИЛИ груп пы соединены с третьими входами (Р-1)-х элементов И группы и с соответствутощими входами элемента ИЛИ, блок обнаружения ошибки содержит п групп элементов И,, группу элементов ИЛИ, блок хранения констант нулевизации5 сумматор нулевизации, блок хранения поправок и сумматор поправок, при этом выходы п групп элементов И соединены с входами соответствующих элементов ИЛИ группы, выходы которых соединены с входами блока хранения констант нулевиза;ции и первым входом сумматора поправок, выход блока хранения констант нулевиза ции соединен с первым входом сумматора нулевизации, первый выход которого соединен с входом блока хранения поправок, выход которого соединен с вторым входом сумматора поправок, группа выходов которого соедине на с вторыми группами информационных входов соответствующих мультиплексоров первой группы, а третий вход сум матора поправок и второй вход сумматора нулевизации объединены и подключены к выходу сумматора контрольных разрядов, выход сумматора нулевизации соединен с вторыми входами элементов И-НЕ группы, первые и вторые входы элементов И п групп соединены соответственно с выходами сумм сумматоров рабочих разрядов группы. На фиг.1 представлена схема сум.матора в системе остаточных классов; на фиг.2 - схема входного регистра контрольных разрядов; на фиг.З схема группы элементов И-НЕ; на фиг,4 - схема блока обнаружения ошибки;/ на фиг.З - схема блока выравнивания номера контролируемого разряда; на фиг.6 - схема блока коррекции контрольного разряда; на фиг.7-- схема блока коррекции результата; на фиг. 8,9 - схемы мультиплексоров; на фиг.10 и 11,- соответственно сумматор рабочих разрядов и сумматор нулевизации. I . На фиг. обозначены: группа 1 входных регистров (рабочих разрядов), входной регистр 2 контрольных разрядов, регистр 3 номеров контролируемых разрядов, группа 4 сумматоров рабочих разрядов,сумматор 5 контрольных разрядов, схема 6 -сравнения, дешифратор 7, блок 8 выравнивания номера контролируемого разряда, блок 9 коррекции контрольного разряда, блок 10 обнаружения ошибки, первая 11 группа из vT-i-l мультиплексоровJ группа 12 элементов И-НЕ, блок 13 коррекции результата, вторая 14 группа изп-1 мультиплексоров, мультиплексор 15, группа 16 из лл элементов И, группа 17 из h+1 элементов НЕ, узел 18 из г групп элементов И, группа 19 из п элементов ИЛИ, блок 20 хранения констант нулевизации, сумматор 21 нулевизации, блок 22 хранения поправок, сумматор 23 поправок, п групп 24 элементов И, группа 25 из ул элементов ЛИ, блок 26 хранения констант выравнивания, группа 27 из 2ц-1 элементов И, группа 28 из Vi-2 элементов ИЛИ, элеент ИЛИ 29, элемент НЕ 30, группа 31 из элементов И, группа 32 из 1-2 элементов ИЛИ, группа 33 элементов НЕ, первая 34, вторая 35, ретья 36 и четвертая 37 группы элеентов И, первый 38, второй 39, третир 0 и четвертый 41 элементы И, первая 2 и вторая 43 группы элементов ИЛИ,

711

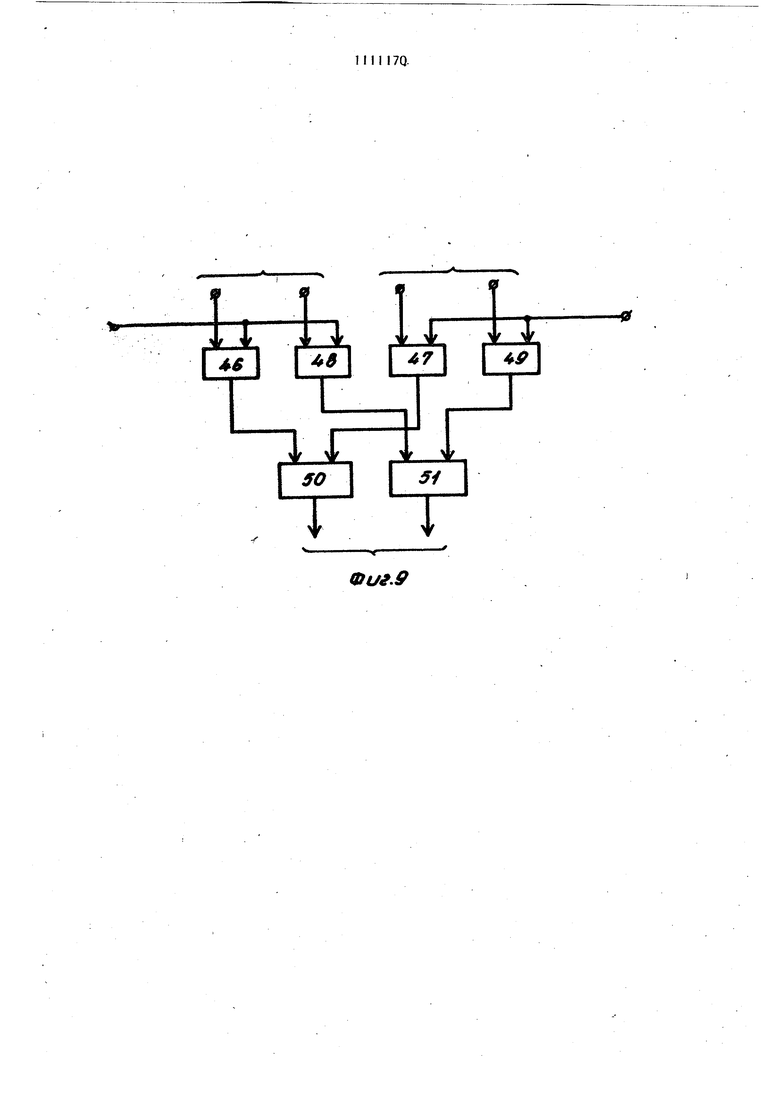

первый 44 и второй 45 элементы ИЛИ, первая 46 и вторая 47 группы элементов И, первый 48 и второй 49 элементы И, группа 50 элементов ИЛИ, элемент ИЛИ 51, группа 52 из 2v деюифраторов операндов, группа 53 из v матриц элементов И, группа 54 из 2 у шифраторов, дешифратор 55 кода СОК, элемент ИЛИ-НЕ 56, элемент И 57, первый и второй 59 сумматоры по модулю |цва, группа 60 элементов И, группа 61 из двух элементов ИЛЙ,первый 62, второй 63, третий 64, четвертый 65 дешифраторы операндов, первая 66 и вторая 67 матрицы элементов И, первый 68 и второй 69 шифраторы, элемент И-НЕ 70, элемент НЕ 71.

Входы регистров 1 - 3 являются входами устройства, выходы регистров группы 1 и регистра 2 подключены к первым и вторым входам соответствующих Q -ичных сум1 аторов 4 и С ичного сумматора 5. Выходы регистра

3подключены к входам схёмь сравнения

6, а второй выход - к входу дешифратора 7 и является выходом номера контролируемого разряда суммы сумматора. Каждый из ( -ичных сумматоров 4, кроме , имеет выходы суммы, суммы, увеличенной на единицу; переноса и возможного переноса. Последний h-й с -ичный сумматор 4 имеет только выходы суммы и переноса. Сумматор 5 имеет выход суммы. Выходы сумматоров

4и 5 подключены к первым информацион ным входам соответствующих мультиопексоров первой группы 11. Первая rpynha входов блока 8 подключена к первым выходам соответствующих входных регистров t, управляющий вход блока 8 подключен к выходу схему сравнения 6, а выход - к третьему входу регистра 2. Первая группа входов блока 10 подключена к выходам

сумм соответствующих сумматоров 4 и сумматора 5. Информацибнные входы вторых групп мультиплексоров первой И группы подключены к соответствующим выходам блока VO. Вторые группы входов блоков .8 - 10 и первые : входы элементов И-НЕ группы 12 соответственно объединены и подключены к соответствующим выхода м дешифратора 7. Вторые входы злемен-гов И-НЕ группы 12 объединены и подключены к управляющему выходу блока tO. Выходы блока 12 подключены к соответствующим управляющим входам мульти08

плексоров первой 11 группы. Выходы сумм и сумм, убеличенных на единицу, первых мультиплексоров первой группы 11 подключены соответственно к первым и вторым информационным вхоЕам соответствующих мультиплексоров торой 14 группы. Выходы переносов и озможных переносов первых п мультиплексоров первой 11 группы подключены к соответствующим входам блока 13 коррекции результата, выходы которого подключены к соответствующим управляющим входам мультиплексоров второй 14 группы, вькоды которых являются выходаЦ первых п-1 рабочих с -ичных разрядов сумматора. Выходы сумм п-го и (п+1)-го мультиплексоров первой 11 группы являются выходами -fv-ro рабочего (-ичного разряда и контрольного а,-ичного разряда сумматора.

В основу работы сумматора положено позиционно-остаточное представле- . ние исходных чисел в виде

VI

A-Iaicj;-||av,«llS

s

где

:04r& 4(Y-1 6nv46C i-(f/.j5i)-,fv)ii + (f v+ I wi ,

-f M/-M

P - рабочие основания системы остаточных классов (СОК); Р ,Ру - контрольные основания СОК;

(О ftm dvH otvw jivH наимень, шие неотрицательные вычеты чисел -я Ъ по соответствукнцим основаниям СОК; (,2,, ,,,п; ,2,...,n) - номер

с -ичного разряда С( -ичного числа А или В, закодированного, кроме рабочих, еще и по контрольным основаниям СОК;

.11 - операция сцепления. Регистры t предназначены для хранения h рабочих разрядов с -ичных чисе А и В, представленных ш гчетами по рабочим основаниям СОК.

Регистр 2 (фиг.2) предназначен для хранения контрольных -ичных разрядов чисел А и В, представленны по контрольным основаниям СОК, и со тоит из двух подрегистров 2.1 с дву информационньми входами (первьй опе ранд) и 2.2 с одним информационным входом (второй операнд). Регистр 3 предназначен для хранения в двоичном коде номеров тех (ичных разрядов А и В, которые закодированы по контрольным основания СОК. Каждый из сумматоров 4 (фиг.10) работает по модулю q, и формирует су мы соответствующих с|,-ичных разрядов чисел А и В, суммы, увеличенные на единицу, сигналы переносов и сигнал возможных переносов. Сумматоры 58 и 59 работают по первому основанию ко да СОК, которое обычно выбирается четным (в данном случае Р1 2), сум матор 59 формирует (А+В)р , а сумма тор 58 (А+В-с)р . Первый результат используется, если сигнал переноса П О, второй - при П 1. Сигнал переноса П формируется в том случае если результат суммирования ( Сигнал возможного переноса ВП формир ется,, если результат суммирования (A-fB) q,-1. Сумматор нулевизации 20 (фиг.11) выполняет по контрольным основаниям Р,, и операцию вьгчитйния из результата суммирования (А+В/Р , f константы нулевизации, переводящей результат суммирования чисел (А+В) по основаниям рабочего диапазона Р/) ,Р2 ,... ,Цу в нули. Нулевые значения вычетов по основаниям Р,., и поступают на элемент И-НЕ 70, сигнал с выхода которого является управляющим выходом сумматора нулевизации 20 и свидетельствует о том, что результат суммирования правильный и его корректировать не надо. С выходов шифраторов 68 и 69 снимается результат нулевизации по основаниям PV V4-2 S-й и t-й с -ичные разряды чисел А и В в совокупности с контрольными (и+1)-ми разрядами можно представить как числа СОК, а именно AS «1,i 1 - 1 V ,)I. S -fc(4,,... Jbv, При сложении чисел Aj и В(при S t) по рабочим основаниям может возникнуть переполнение через «Это 1 0-10 свидетельство ггоявлеиня сигнала переноса в старший с -ичный разряд, а в S-M (-Ь-м) С},-ичиом разряде суммы останется результат по модулю q . Совокупность вычетов (Cs , V oi-Vv1 , Jfv.-Otv.(3) будет изображать число, величина которого лежит во втором интервале, т.е. в диапазоне Ccj,2q,-1l. Данное число с точки зрения избыточной СОК является неправильным. Для того, чтобы вернуть число в диапазоне ГО,с|,-11, из него надо вычесть константу о . с -ичный сумматор 5 контрольных разрядов (фиг.2) состоит из сумматора 5.1, выполненного как совокупность из двух модульных сумматоров по основаниям Ру и Р (аналогично сумматору нулевизации, фиг.11, без элемента И-НЕ 70), и сумматора 5.2, выполненного как совокупность из двух модульных сумматоров по основаниям Ру, и аналогично сумматору нулевизации, фиг.11, без элемента И-НЕ 70). Сумматор 5.1 вычисляет (АН-В)З, Pi4 S сумматор 5.2 ()уи Цч-г С помощью мультиплексора 15 один из результатов суммирования передается навыход этого сумматора. Управление вьщачей того или иного результата с сумматора 5 обеспечивается по первому и второму управляющим входам мультиплексора 15, являющимся соответствующими управляющими входами сумматора. 5. Схема сравнения 6 предназначена для поразрядного сравнения значений S и fc, сигнал на ее выходе появляется, если Sft. Дешифратор 7 преобразует двоичный код t, поступающий с регистра 3, в унитарный и -разрядный код. Блок 10 (фиг.4) предназначен для. проверки содержимого одного из с -ичных сумматоров группы 4 и содержимого cj -ичного сумматора 5, рассматриваемых как единое слово СОК на правильность или не.правштьность. Узел из tn групп элементов И 18 и группа из п элементов ИЛИ 19 представляют собой входной коммутатор, с помощью которого к блоку хранения констант нулевизации 20 подключается выход сумм одного из ( -ичных сумматоров 4. Блок 10 работает следующим образом. Через первую группу входов на первые и входы групп элементов И узла 18 поступают значения сумм с выходов oj.ичных сумматоров 4. По одному из входов второй группы приходит сигнал с дешифратора 7, который по вторым входам открывает соответствующие элементы И одной из групп узла 18. Сигналы, представляющие остатки одно го из q, -ичных разрядов суммы по ра бочим основаниям СОК, через элементы ИЛИ группы 19 поступают в виде адреса на блок хранения констант нулевизации 20, с выходов которого считывается константа, равная значению данного о, -ичного раэряда суммы, . представленному по контрольным основаниям Ру.1 и Ру4.2 СОК, которая поступает на вторую группу входов сумматора нулевизации 21 (вычитаемое), настроенного на выполнение операции вычитания. На первую группу входов сумматора нулевизации 21 поступает значение суммы с выхода с{.-ичного сумматора (уменьшаемое). С выходов сумматора нулевизации разность в вид адреса подается на группу входов (блока хранения поправок 22. Если контролируемое 2-х разрядное q, -ично число быпо правильньм (с .точки зрения сок), то значение поправки равно нулю. Если же в исходном числе по одному из рабочих или контрольных оснований СОК была ошибка, то блок 22 формирует на выходе поправку, величина и место которой однозначно определены значением остатков по контрольным основаниям на выходе сумматора 2t. Сформированная поправк R в виде числа по рабочим Р ,Р,. .. и контрольньй Р. и Ру+2 основаниям СОК поступает на третью группу входо сумматора поправок 23 (как вычитаемо На nepB3W и вторую группы входов сум матора поправок 23 поступает контролируемое число (как уменьшаемое). На выходе сумматора образуется скорректированньй результат суммы по рабочим основаниям (сумма, сумма, увеличенная на единицу, перенос и возможный перенос) и. по контрольным основаниям (сумма) в виде A+B-|i. С первого выхода сумматора иулевизации 21 снимается управляющий сигнал Блок 8 вьфавнивания номера«контро лируемого разряда (фиг.5) состоит из у- групп элементов И 24, группы из к элементов ИЛИ 25, выполняющих функции коммутатора и подключающих 7012 на вход блока хранения констант выравнивания 26 tr -и о, -ичный разряд числа А для кодирования его по контрольным основаниям и Ру СОК и записи его в регистр 2 по третьему входу вместо находящегося там контрольного кода S-го t-ичного разряда. Необходимость операции выравнивания возникает в том случае, если на вход сумматора поступают исходные с -ичные числа, у которых S Ь, что выявляется схемой сравнения (вернее несравнения) 6. Блок 9 коррекции контрольного разряда (фиг.6) обеспечивает вьщачу на первый и второй управляющие входы сумматора 5 управляющих сигналов: первого - с выхода элемента НЕ 30 и второго - с выхода элемента ИЛИ 29. Обозначим: ft функция, которая разрешает выдачу управляющих сигналов при возникновении сигнала переноса из -t-ro сэ-ичного разряда; 1Т, - сигнал переноса из л-го о -ичного разряда; ВП - сигнал возможного переноса из i-гоо-ичного разряда. Значение функции f j при принятых обозначениях имеет вид f..&fa .P nilBHa f ,t n-il6n-i&V , Формирование функции , вьтолняется с помощью элементов И группы 27 и втоporo элемента ИЛИ 28. Блок 13 (фиг.7) на основе анализа сигналов ВП- вырабатывает выходные функции, обеспечивающие подачу на выход сумматора через мультиплексоры 14 сумм (Z) либо сумм, увеличенньк на единицу (Z+1). Мультиплексоры с первого по (-1)-й первой группы 11 (фиг.8). передают на выход результат, с сумматоров 4, либо с выхода блока 10 и работают по управляющим сигналам с группы элементов И-НЕ 12 (фиг.З), обеспечивающих выборку S-го и (п+1)-го мультиплексора для подключения его к выходу блока 10. Мультиплексор группы 11.п(фиг.9) передает на выход сигналы сумм и переносов. Мультиплексор 11.4-1 по структуре аналогичен мультиплексору 15 сумматора 5 и передает на выход значения 13 суммы по контрольным разрядам Р,,;.;, и Ру+г Мультиплексоры второй 14 группы по структуре аналогичны мультиплексору 11.П (фиг.9). Сумматор работает следующим обра зом. Числа, подлежащие суммированию, представленные в позиционно-остаточ ном коде (1), заносятся поразрядно в соответствующие регистры 1-3, с выходов которых поступают на соот ветствующие первые и вторые входы сумматоров 4 и 5, где происходит об разование поразрядных (с -ичных и с -ичных) сумм, сумм, увеличенных н единицу, переносов и возможных пере носов. Сигнал переноса формируется, когда результат в некотором ( -ичном сумматоре Q, а сигнал переноса, когда результат равен -1 Одновре менно в схеме сравнения 6 производи ся сравнение величин S и t , Если S -k , то сигнал на ее выходе равен О, если S эt , то 1. Одновременно дешифратор 7 преобразует двоичный к t (в данном случае можно и 5 ) в код 1, из и , который поступает на входы блоков 8 - 10 и 12. Если S t, то блок 8 участия в работе не принимает. Если в S -м (t-м) Cj -ичном разряде сформированы сигналы переноса или возможного переноса, блок 9 в соответствии с (4) формирует сигналы, поступающие на первый и второй управляющие входы сумматора 5, Блок 10 выбирает 5-и (-ё-й) о-ичный разряд суммы и в совокупности с выходом CJ, -ичного сумматора 5 рассматривает его как слово вида 3 СОК. Возникшая по любом из оснований СОК ошибка блоком 10 обнаруживается, а правильное число по всем основаниям СОК выдается на выходе блока 10, поступает на соответствующие мультиплексоры группы 1 и на входы блока 13 и мультиплексоро 14, с выходов которых - на выход. Если S f ±-f то блок 8 производит перекодировку t-го с -ичного разряд числа А по контрольным основаниям СОК Ру4.,, и 2. засылает результат перекодировки по третьей группе вхо0 4дов в регистр 2, заменяя в последнем (1 + 1)-й разряд исходного числа А. После такой процедуры числа А и В содержат одинаковые (s Ь)с: -ичные разряды, связанные с контролем, и их суммирование производится по только что изложенному алгоритму. Если предположить, что во входном потоке суммируемых чисел номера f8 и t распределены по некоторому случайному закону, что вероятность того, что на вход сумматора поступают исход ные числа, у которых S t, составляет (1/v). Учитьшая возможности блока 8, можно сделать вывод о том, что в среднем за г тактов работы сумматора каждый из его разрядов будет охвачен контролем. Эффективность предложенного устройства может быть опз&еделена следующим. Неизбыточное -ичное число А содержит и paзpя oв. Предложенный метод избыточного кодирования вносит в исходное число избыточность, определяемую как i.W. При реальных значениях о 2 и VI 4 неизбыточная разрядность числа W 32 двоичных разряда, а A.W 10. Это составляет порядка 30%. Регистры 3, схему сравнения 6, дешифратор 7 в целях повышения их надежности до уровня всего сумматора можно выполнить, например, дублированными, либо с применением других технических решений. Никакие из известных арифметических избыточных кодов не могут обеспечить такой малой избыточности при одинаковых с предложенным кодированием корректир5П(Щ1Х возможностях. Если же применять дублирование или троирование, то избыточность аппаратуры составит соответственно 250350%. Такю образом, предложенный сумматор при аппаратурной избыточности порядка 30% обеспечивает обнаружение и исправление всех одиночньп : ошибок (однобитовых), а также таких групп ошибок, длина котрых t для .1 ir m 4 V + 2.

fui.i

Ф1/г.Ь

I I /./7-/I I /g /7 I j

W V

w w

Y t Ф Ф У

Фиг,

i LA

I 4S I e I I

L IT

5

T

%

m T

ФLfг.9

;

f

162 I L

66

f

V V

ea

I 6 65 I

67

0, 0, M,

f

B9

Упр. Вь/х

иг. //

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Сумматор -разрядных к-ичных чисел | 1974 |

|

SU575649A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Матричный сумматор | 1972 |

|

SU478304A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-30—Публикация

1983-06-30—Подача