выход которого соединен с первым входом триггера, выход второго дополнительного элемента И соединен с первым входом дополнительного счетчика, вькод управляющего триггера соединен с третьими входами информационного и управляющего мультиплексоров, вторыми входами основного счетчика, дополнительного счетчика, триггера и входом генератора тактовых импульсов, первый и второй входы управляющего триггера соединены с пятым и шестым входами формирователя соответственно, выход элемента И соединен с третьим входом оперативного запоминающего устройства, выход триггера соединен со вторыми входами второго и третьего дополнительных элемен тов И

| название | год | авторы | номер документа |

|---|---|---|---|

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Многоканальное аналого-цифровое устройство задержки | 1983 |

|

SU1256150A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 2000 |

|

RU2170444C1 |

| Формирователь сложной функции | 1982 |

|

SU1075400A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Устройство для измерения характеристик сверхпроводящих образцов | 1989 |

|

SU1675789A1 |

| Устройство для воспроизведения запаздывающих функций | 1985 |

|

SU1249546A1 |

ФОРМИРОВАТЕЛЬ СЛОЖНОЙ ФУНКЦИИ, содержащий элемент задержки, элемент И, генератор тактовых импульсов, оперативное запоминающее устройство, основной счетчик, дополнительный счетчик, триггер, цифроаналоговый преобразователь, причем выход элемента задержки соединен с первым входом элемента И, выход цифроаналогового преобразователя соединен с выходом формирователя, о тличающийся тем, что, с целью расширения его функциональных возможностей путем обеспечения режима управления задержки, в формирователь введоны аналого-цифровой преобразователь, управляющий триггер, цифровой элемент сравнения, первый, второй и третий дополнительные элементы И, информационный мультиплексор, управляющий мультиплексор, регистр, адресный мультиплексор, причем первые входы информационного и управляющего мультиплексоров соединены с первым и вторым входами формирователя соответственно, первый выход аналого-цифрового преобразователя соединен с первым входом оперативного запоминающего устройства, выход которого соединен со вторым входом информационного мультиплексора, а выход информационного мультиплексора соединен с первым входом .регистра, выход которого соединен со входом цифроаналогового преобразователя, первый вход аналого-цифрового преобразователя соединен с третьим входом формирователя, выход основного счетчика соединен с первыми входами адресного мультиплексора и цифрового элемента сравнения, выход дополнительного счетчика соединен с вторым входом адресного мультиплексора, выход которого соединен с вторым входом оперативного запоминающего устройства, второй выход аналого-цифрового преобразователя соединен со входом элемента задержки, с вторым входом элемента И, первыми входами основного счетчика, первого и второго дополнительных элементов И и третьим входом адресного мультиплексора, выход генератора тактовых импульсов соединен со вторым входом аналого-цифрового преобразователя и с первым входом третьего дополнительного элемента И, выход которого соединен с вторым входом управляющего мультиплексора, а его вход соединен с вторым входом регистра, второй вход цифрового элемента сравнения соединен с четвертым входом устройства, а выход - с вторым входом первого дополнительного элемента И,

Изобретение относится к аналогоцифровой вычислительной технике и может быть использовано в аналого-цифровых вычислительных комплексах и устройствах автоматики.

Известно устройство постоянного запаздывания, содержащее два инвертора, два интегратора, сумматор, выполненные на определенных усилителях Cl 1.

Недостатком данного устройства является ограниченное время запаздывания (не более 25 с) и сложность установки времени запаздывания, связанная со сложностью установки масштабных коэффициентов интеграторов.

Наиболее близким к предлагаемому является формирователь сложной функции, содержащий элемент задержки, элемент И, генератор тактовых импульсов (ГТИ), оперативное запоминающее устройство, основной счетчик, дополнительный счетчик, триггер, цифроаналоговый преобразователь (ЦАП), блок формирования адреса, блок управления, блок формирования .информации, блок установки начального адреса, дискриминатор, первый и второй блоки элементов И, блок элементов ИЛИ, элемент ИЛИ, элемент И-НЕ, причем выход элемента задержки соединен с первым входом элемента И, выход ЦАП соединен с выходом устройства, выход основного счетчика соединен с первым выходом оперативного запоминающего устройства, выход которого соединен со входом ЦАП, второй и третий входы оперативного запоминающего устройства соединены с первым входом блока управления и с выходом блока формирования информации соответственно, первый выход триггера соединен с первым входом элемента И и вторым входом, первого блока элементов И, выход 5 элемента И соединен с первым входом основного счетчика, выход генератора тактовых импульсов соединен с первым входом дополнительного счетчика, второй выход триггера соединен с вто0 рым входом дополнительного счетчика, выход которого через дискриминатор соединен с первыми входами дополнительных первого блока элементов ИЛИ и элемента ИЛИ, второй выход блока

5 управления соединен с вторым входом элемента ИЛИ, выход которого соединен с вторым входом основного счетчика, третий вход первого блока элементов И соединение первым входом устройства,

0 а выход - с первым входом блока элемента ИЛИ, первый выход вт&рого блока элементов И соединен с вторым выходом триггера, второй вход второго блока элементов И соединен с

выходом блока формирования адреса, а выход - с вторьм входом блока элементов ИЛИ, второй вход устройства соединен с первым входом триггера и первым входом элемента И-НЕ, выход которого соединен с вторым входом триггера, второй вход элемента И-НЕ соединен с выходом генератора тактовых импульсов, третьи входы дополнительного счетчика и основного счетчика соединены соответственно с выходами блока установки начального адреса и выходом блока элементов ИЛИС2.

Недостатком известного устройства является невозможность реализации

режима управляемой задержки.

Целью изобретения является расширение функциональных возможностей устройства путем обеспечения режима управляемой задержки.

Поставленная цель достигается тем, что в формирователь сложной фунции, содержащий элемент задержки, элемент И, генератор тактовых импульсов, оперативное запоминающее устройство, основной счетчик, дополнительный счетчик, триггер, цифроаналоговый преобразователь, причем выход элемента задержки соединен с первым входом элемента И, выход цифроаналогового преобразователя соединен с выходом формирователя, дополнительно введены аналого-цифровой пробразователь, управляющий триггер, цифровой элемент сравнения, первый, второй и третий дополнительные элементы И, информационный мультиплексор, управляющий мультиплексор, регистр, адресный мультиплексор, причем первые входы информационного и управляющего мультиплексоров соединены с первым и вторым входами формирователя соответственно, первый выход аналого-цифрового преобразователя соединен с первым входом оперативного запоминающего устройства, выход которого соединен с вторым входом информационного мультиплексора, а выход информационного мультиплексора соединен с первым входом регистра, всхоД которого соединен с входом цифроаналогового преобразователя, первьш вход аналого-цифрового преобразователя соединен с третьим входом формирователя, выход основног счетчика соединен с первыми входами адресного мультиплексора и цифрового элемента сравнения, выход дополнительного счетчика соединен с вт рым входом адресного мультиплексора, выход Kotoporo соединен с вторым входом оперативного запоминающего устройства, втцрой выход аналого-цифрового преобразователя соединен со входом элемента задержки, с вторым входом элемента И, первыми входами основного счетчика, первого и второг дополнительных элементов И и третьим входом адресного мультиплексора, выход генератора тактовых импульсов соединен со вторым входом аналого-ци рового преобразователя и с первым входом третьего дополнительного элемента И, выход которого соединен с

вторым входом управляющего мультиплексора, а его выход соединен со вторым входом регистра, второй вход цифрового элемента сравнения соединен с четвертым входом устройства, а выход - с вторым входом первого дополнительного элемента И, выход которого соединен с первым входом триггера, выход второго дополнительного элемента И соединен с первым входом дополнительного счетчика, выход уп- . равляющего триггера соединен с .третьими входами информационного и управляющего мультиплексоров, вторыми входами основного счетчика, дополнительного счетчика, триггера и входом генератора тактовьк импульсов, первый и второй входы управляющего триггера соединены с пятым и шестым входами формирователя соответственно, выход элемента И соединен с третьим входом оперативного запоминающего устройства, выход триггера соединен со вторыми входами второго и третьего дополнительных элементов И.

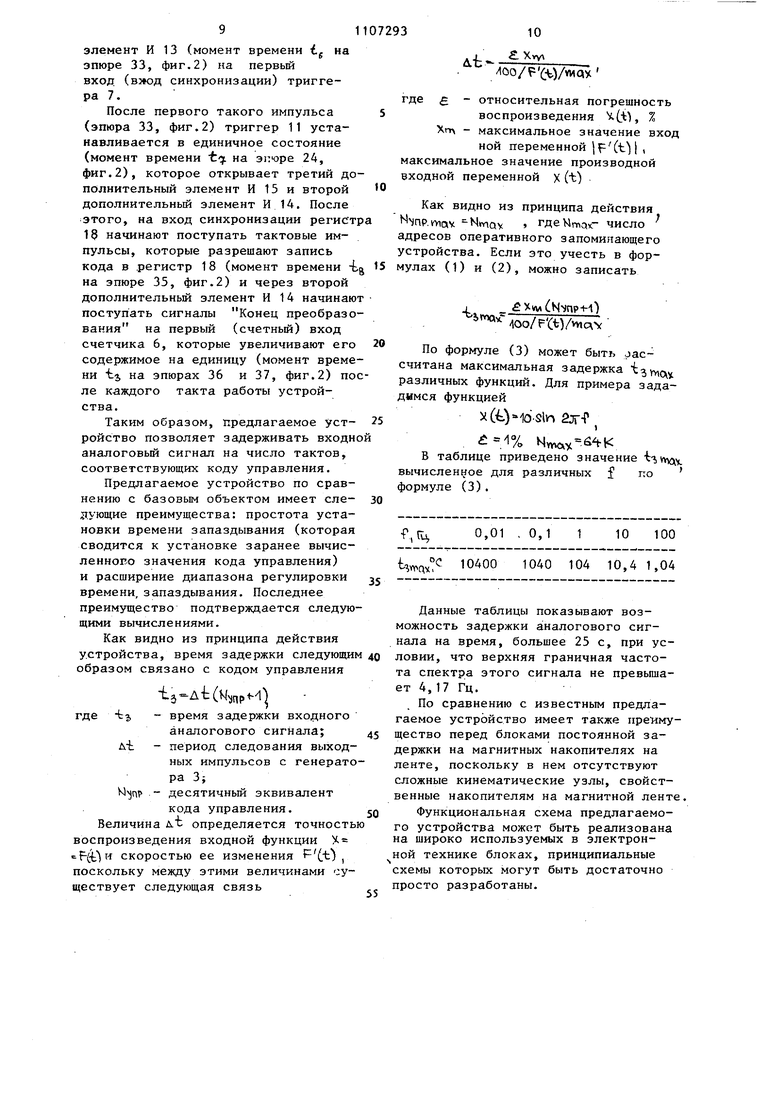

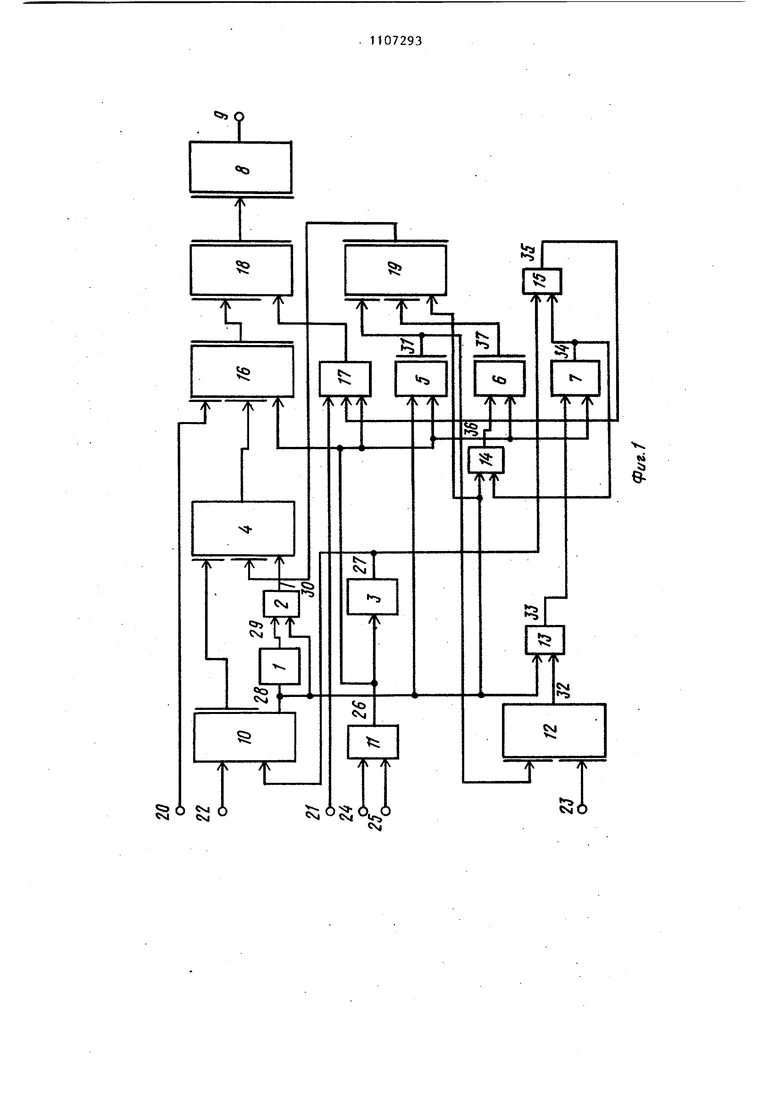

На фиг.1 показана функциональная .схема предлагаемого устройства; на фиг.2 - эпюры напряжений, которые поясняют принцип действия устройства обозначены сигналы, которые действую в соответствующих проводниках и шина

Формирователь сложной функции содержит элемент 1 задержки, эле- . мент И2; генератор тактовых импульсо (ГТИ) 3, оперативное запоминающее устройство 4, основной счетчик 5, дополнительный счетчик 6, триггер 7, цифроаналоговый преобразователь (ЦАП) 8, подключенный выходом к выходу 9 устройства, аналого-цифровой преобразователь (АЦП) 10, управляющий триггер 11, цифровой элемент 2 сравнения, первый дополнительный элемент И13, второй дополнительный элемент И14, третий дополнительный элемент И15, информационный мультиплектор 16, управляющий мультиплексор 17, регистр 18, адресный мультиплексор 19, причем выход элемента 1 задержки соединен с первым входом элемента И 2, первые входы информационного 16 и управляющего 17 мультиплексоров соединены с первым 20 и вторым 21 входами устройства соответственно, первый выход АЦП 10 соединен с первым входом оперативног запоминающего устройства 4, выход которого соединен с вторым входом S1 информационного мультиплексора 16, ход которого соединен с первым входом регистра 18, выход которого соединен с входом ЦАП 8, первый вхо АЦП 10 соединен с третьим входом 22 устройства, выход основного счетчик 5 соединен с первыми входами адресного мультиплексора 19 и цифро вого элемента 12 сравнения, вьгход дополнительного счетчика 6 соединен с вторым входом адресного мультипле сора 19, выход которого соединен с входом оперативного запоминающего устройства 4, второй выход соединен с первыми входами адресного мультиплексора 19 и цифрового элемента уравнения 12, выход дополнительного счетчика б соединен с вторым входом адресного мультиплексора 19, выход которого соединен со вторым входом оперативного запоминающего устройства 4, второй выход АЦП 10 соединен со входом элемента 1 задержки со вторым входом элемента И 2, перв ми входами основного счетчика 5, пе вого дополнительного элемента И 13 и второго, дополнительного элемента И 14 и третьим входом адресного мультиплексора 19, выход генератора тактовых импульсов 3 соединен со вторым входом АЦП 10 и с первым вхо дом третьего дополнительного элемента И 15, выход которого соединен с вторым входом управляющего мультиплексора 17, а его выход сое динен со вторым входом регистра 18, второй вход цифрового элемента сра нения 12, соединен с четвертым входом 23 устройства, а выход с вторым входом первого дополнительного элемента И 13, выход которого соединен с первым входом триггера 7, выход второго дополнительно го элемента И 14 соединен с первым (ВХОДОМ дополнительного счетчика 6, а выход управляющего триггера 11 соединен с третьими входами информационного 16 и управляющего 17 мультиплексоров вторыми входами основного 5 и дополнительного 6 счетчиков, триггера 7 и входом гене ратора тактовых импульсов 3, первый и второй входы управляющего триггера соединены с пятым 24 и шестым 25 входами устройсттза соответственно, выход элемента И 2 соединен с третьи входом оперативного запоминающего устройства 4, выход триггера 7 сое3динен со вторыми входами второго 14 и третьего 15 дополнительных элементов И. На фиг.2 представлены эпюры (26-37) сигналов на выходах блоков управляющего триггера 11, генератора 3 тактовых импульсов, АЦП 10, элемента 1 задержки, элемента И 2, основного счетчика 5, цифрового элемента 12 сравнения, первого дополнительного элемента И 13, триггера 7, третьего дополнительного элемента И 15,-второго дополнительного элемента И 14 и дополнительного счетчика 6 соответственно. Устройство функционирует в двух режимах Подготовка и Воспроизведение. Первые входы счетчиков 5 и 6 являются счетными входами, вторые входами обнуления, первые и вторые входы мультиплексоров 16-19 являются информационными, а третьи входами управления. I В режиме Подготовка сигнал Стоп по шестому входу 25 устройства поступает на второй вход управляющего триггера 11 и обнуляет его, сигнал с его выхода обнуляет по вторым (входам обнуления) входам счетчиков 5 и 6 и по второму (входу обнуления) входу триггер 7. Тот же сигнал блокирует работу ГТИ 3, открывает мультиплексоры 17 и 16 по первому входу, сформированный к этому времени на первом входе 20 устройства код:-начальных условий поступает на первьй (информационный) вход регистра 18. По второму входу 21 устройства поступает сигнал Запись начальных условий, который через мультиплексор 17 поступает на второй вход (вход синхронизации) регистра 18 поступает на ЦАП 8, который на своем выходе формирует напряжение начальных условий, В режиме Воспроизведение сигнал Старт поступает на пятый вход 24 устройства и устанавливает управляющий триггер 11 в единичное состояние и разрешает работу генератора 3 (эпюры 26 к 21 момент времени i;/) на фиг. 2), открывает мультиплексоры 16 и 17 по вторым информационным входам, т.е. первый (информационный) вход регистра 18 соединяется с выходом устройства 4, а второй вход (вход синхронизации) регистра 18 соединяется с выходом третьего дополнительного элемента И 15. Единичный сигнал на выходе управляющего триггера 11 также прекращает блокировать работу счетчиков 5 и 6 и триггера 7. Тактовые импульсы с генератора 3 поступают на второй вход (вход запуска) АЦП 10, при этом АЦП 10 начинает преобразование.аналогового напряжения, которое поступает на тре тий вход 22 устройства в цифровой код. Когда этот код полностью сформируется.на втором выходе АЦП 10 появляется сигнал Конец преобразова ния (момент времени t2. на эпюре 28 фиг.2). Этот сигнал на время своего действия открывает мультиплексор 19 по первому информационному входу (с момента времени -t по момент времени -t-i , эпюра 28, фиг. 2), при этом выход счетчика 5 соединяется со вторым (адресным) входом блока 4. Кроме этого, сигнал Конец преобразования поступает на третий вход (вход Запись-считывание) 4 через устройства 4.через элемент И 2 (по второму его входу), элемент 1 задержки и первый вход элемента И 2. :Это обеспечивает запись сформированного на первом выходе АЦП 10 кода в запоминающем устройстве 4 по адресу, который определяется содержимым счетчика 5 (в -первом такте записи - по нулевому адресу, момент времени iT, на эпюре, фиг.2). Передача сигнала Конец преобразо вания на третий вход (вход Запись считывание) устройства 4 через элемент 1 задержки и элемент И 2 обусЛо лена необходимостью задержать сигнал записи на время задержки кода адреса записи в мультиплексоре 19, а также необходимостью окончить запись до изменения состояния счетчика 5, которое происходит по срезу сигнала Конец преобразования (момент времени t, на эпюрах 28 и 30, фиг.2). Таким образом, по фронту сигнала на выходе элемента И 2 происходит з пись цифрового кода входной аналого вой величины в оперативное запомина щее устройство 4 по адресу, определ емому текущим состоянием счетчика 5 (момент времени i-j, на зпюре 30, фиг а по срезу сигнала Конец преобразо вания происходит увеличение текущего состояния счетчика на единицу 1 38 (момент времени эпюре 31,фиг.2), Таким образом обеспечивается запись j цифровых кодов входной аналоговой величины в последовательные ячейки запоминающего устройства 4. Считывание информации из устройства 4 происходит также из последовательных ячеек, начиная с нулевой, но с задержкой на число тактов, определяемое цифровым кодом, подаваемым на четвертый вход 23 устройства. Этот код далее будет называться кодом управления Njnp (на фиг.2 показан случай, когда ). Информация из устройства 4 поступает на первый (информационный) вход регистра 18 через второй вход мультиплексора 16, а ее прием в регистр 18 синхронизируется выходными импульсами третьего дополнительного элемента И 15, которые проходят через второй вход мультиплексора 17 на второй вход (вход синхронизации) регистра 18. Адрес ячейки запоминающего устройства 4, из которой считывается информация, определяется содержимым счетчика 6, выход которого через второй вход мультиплексора 19 соединен с вторым (адресным) входом устройства 4. Импульсы с выхода третьего дополнительного элемента И 15, по срезу которых происходит внесение информации в регистр 18 синхронны и синфазны импульсам генератора 3 (эпюры 27 и 35, фиг.2), но начинаются с задержкой, определяемой кодом управления (можно сравнить момент времени ir/ на эпюре 28 и момент времени ig эпюре 35, фиг.2). Такая задержка осуществляется следующим образом. Выходные импульсы постоянно подаются на первый вход третьего дополнительного элемента И 15, но до момента начала считывания из блока 4 (момент времени на эпюре 32 (фиг.2). Этот элемент закрыт нулевым сигналом, поступающим на его второй вход с выхода триггера 7. Цифровое запоминающее устройство 12 при равенстве кода управления и кода текущего адреса записи (выход счетчика 5) формирует на своем выходе единичный сигнал (момент времени Нг5 на эпюре 26, фиг.2), который разрешает прохождение сигнала Конец преобразования через первый дополнительный 9 элемент И 13 (момент времени i.g на эпюре 33, фиг.2) на первый вход ( синхронизации) триггера 7. После первого такого импульса (эпюра 33, фиг.2) триггер 11 устанавливается в единичное состояние (момент времени . на эпюре 24, фиг.2), которое открывает третий до полнительный элемент И 15 и второй дополнительный элемент И 14. После этого, на вход синхронизации регист 13 начинают поступать тактовые импульсы, которые разрешают запись кода в .регистр 18 (момент времени -t на эпюре 35, фиг.2) и через второй дополнительный элемент И 14 начинаю поступать сигналы Конец преобразо вания на первый (счетный) вход счетчика 6, которые увеличивают его содержимое на единицу (момент време ни tj, на эпюрах 36 и 37, фиг.2) по ле каждого такта работы устройства. Таким образом, предлагаемое устройство позволяет задерживать входн аналоговый сигнал на число тактов, соответствующих коду управления. Предлагаемое устройство по сравнению с базовым объектом имеет еледующие преимущества: простота установки времени запаздывания (которая сводится к установке заранее вычисленного значения кода управления) и расширение диапазона регулировки времени, запаздывания. Последнее преимущество подтверждается следую щими вычисл е н иями. Как видно из принципа действия устройства, время задержки следующи образом связано с кодом управления t3-A-b(,pM где -tj время задержки входного аналогового сигнала; At - период следования выходных импульсов с генерато ра 3; Klvjnp - десятичный эквивалент кода управления. Величина Д.Ь определяется точность воспроизведения входной функции Х F(Vf скоростью ее изменения (.1: , поскольку между этими величинами существует следующая связь 3 д-Ь « Hoo/F(;t)/wqx где - относительная погрещность воспроизведения V,(i), % Хп - максимальное значение вход ной переменной jf( , максимальное значение производной входной переменной X (t) Как видно из принципа действия biMnp.may -HtYiQy , гдеЫтах- число адресов оперативного запоминающего устройства. Если это учесть в формулах (1) и (2), можно записать ) Хщ {N-jnp-t-Q lOo/F(:t) По формуле (3) может быть рассчитана максимальная задержка ,« различных функций. Для примера зададимся функцией x(t)io-sln 2лг-Р % Nwcxy t-K В таблице приведено значение t-iwy y вычисленное для различных f по формуле (3). 0,01 {, 10400 104 10,4 1,04 Данные таблицы показывают возможность задержки aiHanoroBoro сигнала на время, большее 25 с, при условии, что верхняя граничная частота спектра этого сигнала не превьш1ает 4,17 Гц. По сравнению с известным предлагаемое устройство имеет также преимущество перед блоками постоянной задержки на магнитных накопителях на ленте, поскольку в нем отсутствуют сложные кинематические узлы, свойственные накопителям на магнитной ленте. Функциональная схема предлагаемого устройства может быть реализована на широко используемых в электроной технике блоках, принципиальные хемы которых могут быть достаточно росто разработаны.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Щеголев Л.И., Давьщов А.Ф | |||

| Основы вычислительной техники и программирования | |||

| Л., Энергоиздат, 1981, с.64, рис.5-6 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3335838/18-21, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-08-07—Публикация

1982-11-12—Подача