1

Изобретение относится к вычислительной технике и может быть использовано в.аналого-цифровых вьиислитель- ных комплексах и устройствах автоматики.

Целью изобретения является упрощение устройства.

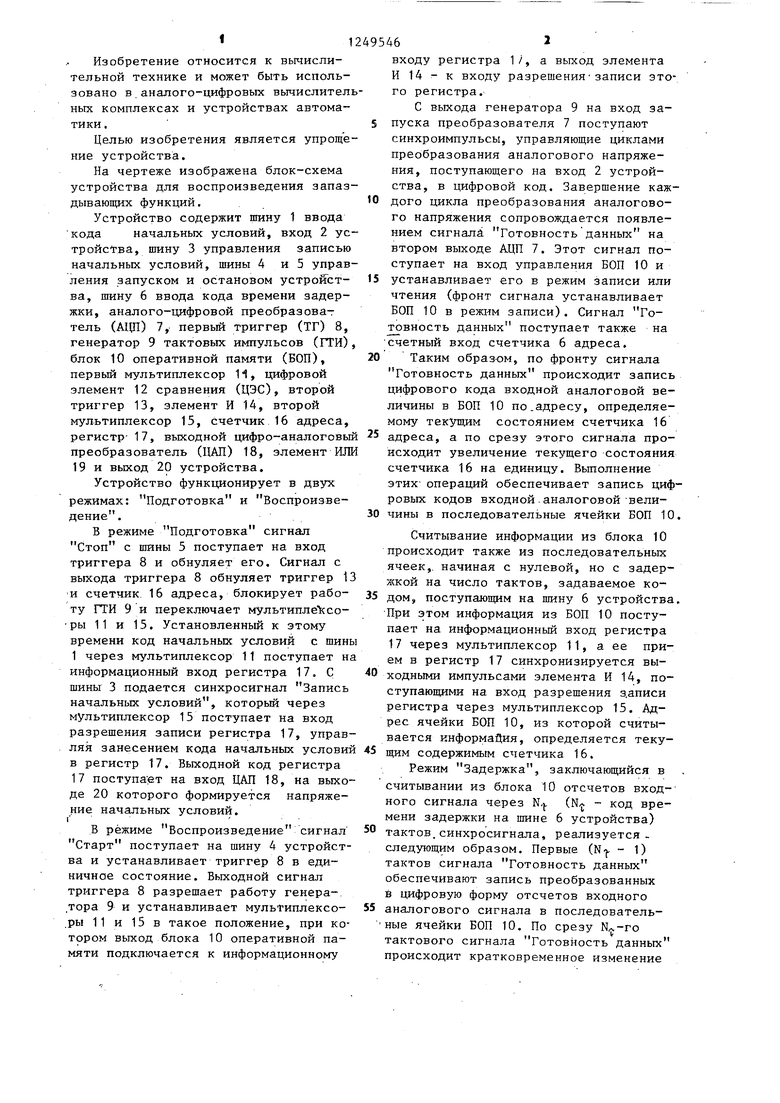

На чертеже изображена блок-схема устройства для воспроизведения запаздывающих функций.

Устройство содержит шину 1 ввода кода начальных условий, вход 2 устройства, шину 3 управления записью начальных условий, шины 4 и 5 управления запуском и остановом устройства, шину 6 ввода кода времени задержки, аналого-цифровой преобразова-г тель (А1Ц1) 7, первьй триггер (ТГ) 8, генератор 9 тактовых импульсов (ГТИ),

блок 10 оперативной памяти (БОП), первый мультиплексор 11, цифровой элемент 12 сравнения (ЦЭС), второй триггер 13, элемент И 14, второй мультиплексор 15, счетчик 16 адреса, регистр- 17, выходной цифро-аналоговый преобразователь (ДАЛ) 18, элемент ИЛИ 19 и выход 20 устройства.

Устройство функционирует в двух режимах: Подготовка и Воспроизведение.

В режиме Подготовка сигнал Стоп с шины 5 поступает на вход триггера 8 и обнуляет его. Сигнал с выхода триггера 8 обнуляет триггер 13 и счетчик 16 адреса, блокирует работу ГТИ 9 и переключает мультипле ссо- ры 11 и 15. Установленный к этому времени код начальных условий с шины 1 через мультиплексор 11 поступает на информационный вход регистра 17. С шины 3 подается синхросигнал Запись начальных условий, который через мультиплексор 15 поступает на вход разрешения записи регистра 17, управ

Считывание информации из блока 10 происходит также из последовательных ячеек,, начиная с нулевой, но с задержкой на число тактов, задаваемое кодом, поступающим на шину 6 устройства При этом информация из БОП 10 поступает на информационный вход регистра 17 через мультиплексор 11, а ее прием в регистр 17 синхронизируется выходными импульсами элемента И 14, поступающими на вход разрешения з.аписи регистра через мультиплексор 15. Адрес ячейки БОП 10, из которой считывается информация, определяется текуляя занесением кода начальных условий 45 щим содержимым счетчика 16.

в регистр 17. Выходной код регистра Режим Задержка, заключающийся в

17 поступа ет на вход ЦАП 18, на выходе 20 которого формируется напряжение начальных условий.

В режиме Воспроизведение сигнал 50 Старт поступает на шину 4 устройства и устанавливает триггер 8 в единичное состояние. Выходной сигнал триггера 8 разрешает работу генера- .тора 9 и устанавливает мультиплексо- 55 .ры 11 и 15 в такое положение, при котором выход блока 10 оперативной памяти подключается к информационному

считывании из блока 10 отсчетов входного сигнала через N.j, (N - код времени задержки на шине 6 устройства) тактов.синхросигнала, реализуется - следующим образом. Первые (Nf- - 1) тактов сигнала Готовность данных обеспечивают запись преобразованных в цифровую форму отсчетов входного аналогового сигнала в последовательные ячейки БОП 10. По срезу Нл-го тактового сигнала Готовность данных происходит кратковременное изменение

ь-

12495462

входу регистра 1/, а выход элемента И 14 - к входу разрешениязаписи этого регистра.

С выхода генератора 9 на вход запуска преобразователя 7 поступают синхроимпульсы, управляющие циклами преобразования аналогового напряже

ния, поступающего на вход 2 устройства, в цифровой код. Завершение каж

дого цикла преобразования аналогового напряжения сопровождается появлением сигнала. Готовность данных на втором выходе АЦП 7. Этот сигнал поступает на вход управления БОП 10 и устанавливает его в режим записи или чтения (фронт сигнала устанавливает БОП 10 в режим записи). Сигнал Готовность данных поступает также на счетный вход счетчика 6 адреса.

Таким образ-ом, по фронту сигнала Готовность данных происходит запись цифрового кода входной аналоговой величины в БОП 10 по.адресу, определяемому текущим состоянием счетчика 16 адреса, а по срезу этого сигнала происходит увеличение текущего состояния счетчика 16 на единицу. Выполнение этих операций обеспечивает запись цифровых кодов входной.аналоговой вели- чины в последовательные ячейки БОП 10.

Считывание информации из блока 10 происходит также из последовательных ячеек,, начиная с нулевой, но с задержкой на число тактов, задаваемое кодом, поступающим на шину 6 устройства. При этом информация из БОП 10 поступает на информационный вход регистра 17 через мультиплексор 11, а ее прием в регистр 17 синхронизируется выходными импульсами элемента И 14, поступающими на вход разрешения з.аписи регистра через мультиплексор 15. Адрес ячейки БОП 10, из которой считывается информация, определяется теку

щим содержимым счетчика 16.

считывании из блока 10 отсчетов входного сигнала через N.j, (N - код времени задержки на шине 6 устройства) тактов.синхросигнала, реализуется - следующим образом. Первые (Nf- - 1) тактов сигнала Готовность данных обеспечивают запись преобразованных в цифровую форму отсчетов входного аналогового сигнала в последовательные ячейки БОП 10. По срезу Нл-го тактового сигнала Готовность данных происходит кратковременное изменение

Состояния счетчика

3

16

адреса. Значение выходного кода счетчика 16 становится равным коду, установленному на шине 6 устройства. Срабатывает цифровой элемент 12 сравнения, выходной сигнал которого устанавливает в единичное состояние триггер 13 и через элемент ИЛИ 19 поступает на счетчик 16, обнуляя его. В результате выходной код сч етчика 16 задает адрес первой считываемой ячейки БОП 10.

Блок 10 переходит в режим считывания данных, запись которых в регистр 17 синхронизируется импульсами генератора 9, поступающими через открытый триггером 13.элемент И 14 и мультиплексор 15 на вход разрешения записи регистра 17 i После завершения считы-. ванйя из блока 10 в регистр 17 производится запись следующего (N.+l)-ro отсчета входного аналогового сигнала ,.в блок ,10 по адресу только что считанной ячейки. ...

Таким образом, предлагаемое устройство позволяет упростить техническую реализацию задержки входного аналогового сигнала за счет использования только одного адресного счетчика и исключения адресного коммутатора.

Фор.мула изобретения

Устройство для воспроизведения запаздывающих функций, содержащее аналого-цифровой преобразователь, подключенный информационным входом к входу устройства, входом запуска - к выходу генератора тактовых импульсов и первому вхо ду элемента И, кодовым выходом - к информационному входу блока оперативной памяти, а выходом сигнала окончания преобразования Редактор Л.Гратилло

Заказ 4327/51Тираж 671Подписное

ВНИШИ Государственного комитета СССР

по делам изобретений и открытий. 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

1249546

10

15

0

5

0

5

к счетному входу счетчика адреса, соединенного выходом с первым входом цифрового элемента сравнения, второй вход которого подключен к шине вводи кода времени задержки устройства, причем вход запуска генератора тактовых импульсов соединен с выходом первого триггера, входом сброса второго триггера и с управляющими входами , двух мультиплексоров, первый из которых подключен первым и вторым информационными входами к шиМе ввода кода начальных условий устройства и выходу блока оперативной памяти соответственно, а выходом - к информационному входу регистра, соединеннного выходом с входом выходного цифроаналого- вого преобразователя, а входом разрешения записи - с выходом второго . . мультиплексора,, подключенного первым информационным входом к шине управления записью начальных условий устройства, а вторым информационным входом - к выходу элемента И, второй вход которого соединен с выходом второго тригге ра, при этом входы уста, новки и сброса первого триггера подключены к шинам управления запускс М . и остановом устройства, отличающееся тем, что, с целью упрощения устройства оно содержит элемент ИЖ, соединенный первым входом с выходом первого триггера, вторым входом - с выходом цифрового элемента сравнения и входом установки второго триггера, а выходом - с входом обнуления счетчика адреса, подключенного выходом к адресному входу блока оперативной памяти, соединенного входом управления записью и чтением с выходом сигнала окончания преобразования аналого-цифрового преобразователя.

Составите Гъ С.Казинов Техред В.Кадар

Корректор М.Самборская

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения функций | 1986 |

|

SU1561075A1 |

| Цифровой компандер | 1986 |

|

SU1427575A1 |

| Многоканальное аналого-цифровое устройство задержки | 1983 |

|

SU1256150A1 |

| Устройство для ввода информации от аналоговых датчиков | 1985 |

|

SU1298734A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Устройство для воспроизведения запаздывающих функций | 1985 |

|

SU1285493A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| ЦИФРОВОЙ ДАЛЬНОМЕР | 1992 |

|

RU2069003C1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1991 |

|

SU1837303A1 |

Изобретениеотносится к вычислительной технике.Устройство содержит аналого-цифровойпреобразователь 7, триггеры 8 и 13,генератор 9 тактовых импульсов, блок 10 оперативной памяти, мультиплексоры 11 и 15, цифровой элемент 12 сравнения, элементы И 14 и ИЛИ 19, счетчик 16 адреса, регистр 17 и цифроаналоговый преобразователь 18, Работа устройства основана на записи в блок to оперативной памяти последовательности -цифровьис отсчетов входной аналоговой величины, поступающей на вход 2, и считывания в регистр 17 информации из ячеек блока 10, выбираемых с соответствующим сдвигом по коду адреса. Упрощение устройства достигается на основе использования общего счетчика t6 адреса, который в начальные моменты времени формирует адреса записи отсчетов в блок 10 оперативной памяти, а после достижения необходимого запаздывания используется для формирования адресов записи и считывания отсчетов. Такая организация процесса работы позв-оляет исключить второй счетчик адреса и адресный ком мутатор. 1 ил. W 1C i со ел

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для воспроизведения запаздывающих функций | 1984 |

|

SU1168973A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Формирователь сложной функции | 1982 |

|

SU1107293A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-07—Публикация

1985-01-29—Подача