Изобретение относится к импульсной технике и может быть использовано для контроля импульсных последовательностей.

Цель изобретения - упрощение конструкции.

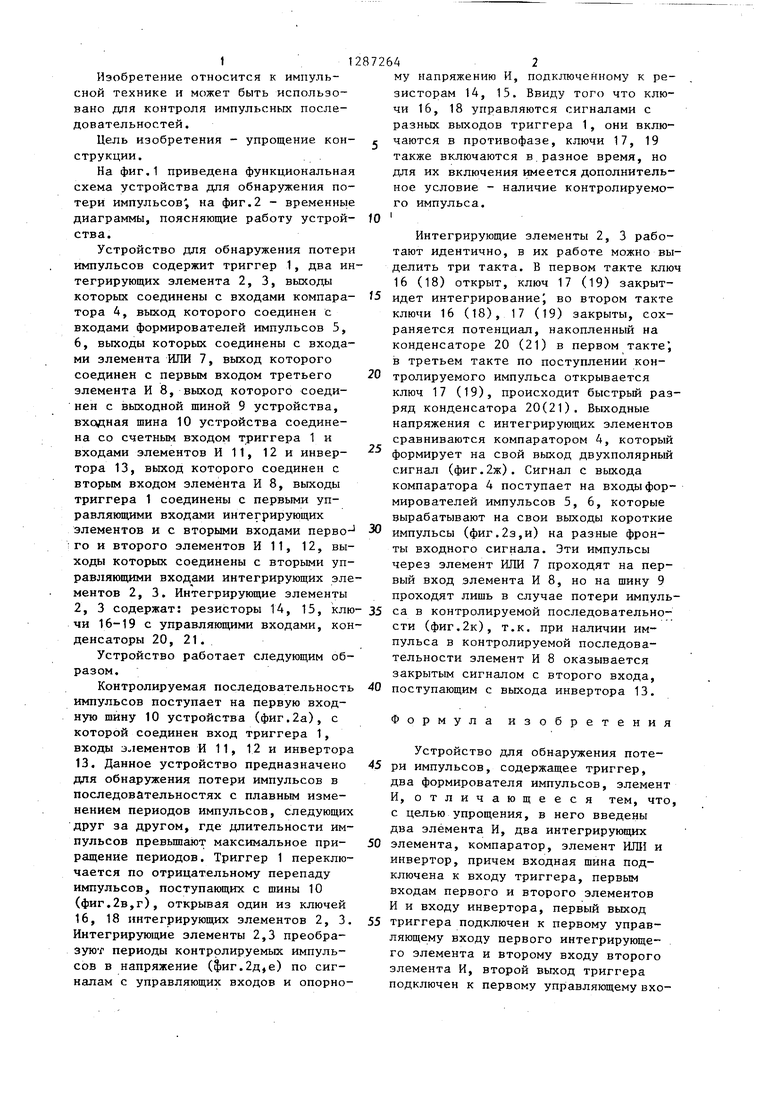

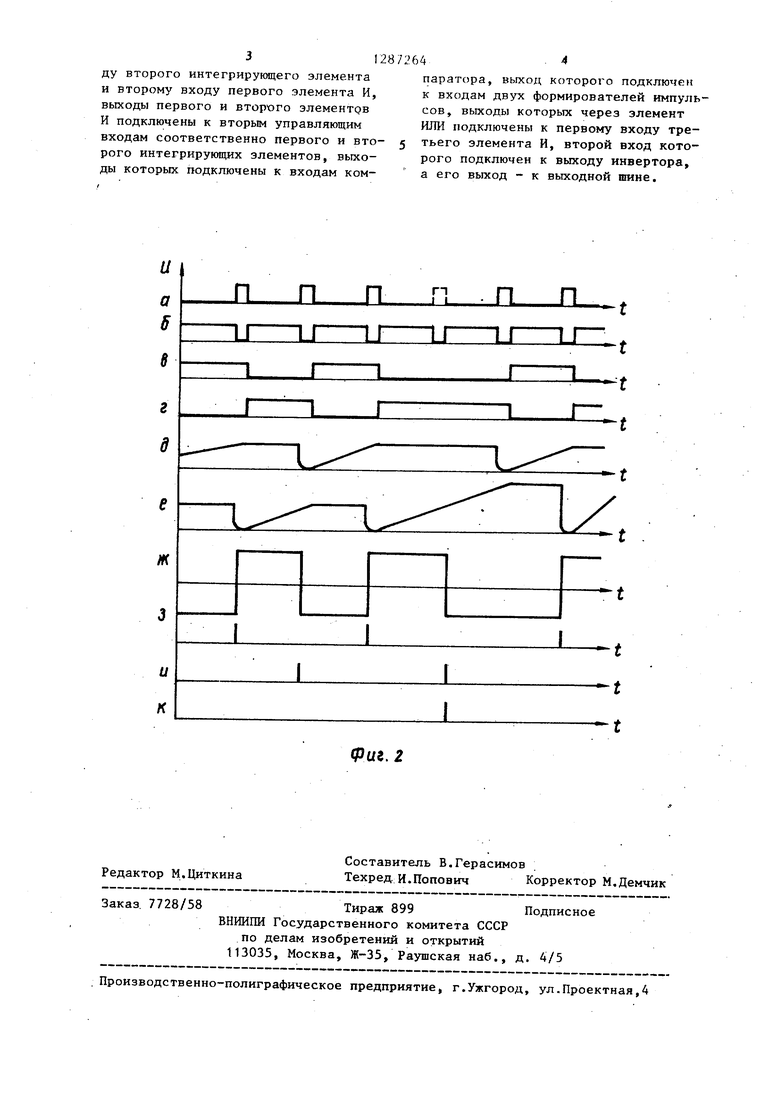

На фиг,1 приведена функциональная схема устройства для обнаружения потери импульсов; на фиг.2 - временные диаграммы, поясняющие работу устройства.

Устройство для обнаружения потери импульсов содержит триггер 1, два интегрирующих элемента 2, 3, выходы которых соединены с входами компара- тора 4, выход которого соединен с входами формирователей импульсов 5, 6, выходы которых соединены с входами элемента ИЛИ 7, выход которого соединен с первым входом третьего элемента И 8, выход которого соединен с выходной шиной 9 устройства, входная шина 10 устройства соединена со счетным входом триггера 1 и входами элементов И 11, 12 и инвертора 13, вькод которого соединен с вторым входом элемента И 8, выходы триггера 1 соединены с первыми управляющими входами интегрирующих элементов и с вторыми входами перво:го и второго элементов И 11, 12, выходы которых соединены с вторыми уп- равляюпщми входами интегрирующих элементов 2, 3. Интегрирующие элементы

2, 3 содержат: резисторы 14, 15, клю- 35 са в контролируемой последовательно- чи 16-19 с управляющими входами, кон- сти (фиг.2к), т.к. при наличии им- денсаторы 20, 21.пульса в контролируемой последовательности элемент И 8 оказывается закрытым сигналом с второго входа.

Устройство работает следующим образом.

Контролируемая последовательность импульсов поступает на первую входную шину 10 устройства (фиг.2а), с которой соединен вход триггера 1, входы элементов И 11, 12 и инвертора 13. Данное устройство предназначено для обнаружения потери импульсов в последовательностях с плавным изменением периодов импульсов, следующих друг за другом, где длительности импульсов превьшзают максимальное приращение периодов. Триггер 1 переключается по отрицательному перепаду импульсов, поступающих с шины 10 (фиг,2в,г), открывая один из ключей 16, 18 интегрирующих элементов 2, 3. Интегрирующие элементы 2,3 преобразуют периоды контролируемых импульсов в напряжение (5)иг.2д,е) по сигналам с управляющих входов и опорно40

поступающим с выхода инвертора 13.

Формула изобретения

Устройство для обнаружения поте- 45 ри импульсов, содержащее триггер, два формирователя импульсов, элемент И, отличающееся тем, что, с целью упрощения, в него введены два элемента И, два интегрирующих 50 элемента, компаратор, элемент ИЛИ и инвертор, причем входная шина подключена к входу триггера, первым входам первого и второго элементов И и входу инвертора, первый выход 55 триггера подключен к первому управляющему входу первого интегрирующего элемента и второму входу второго элемента И, второй выход триггера подключен к первому управляющему вхо872642

му напряжению И, подключенному к резисторам 14, 15. Ввиду того что ключи 16, 18 управляются сигналами с разных выходов триггера 1, они включаются в противофазе, ключи 17, 19 также включаются в.разное время, но для их включения имеется дополнительное условие - наличие контролируемого импульса.

Интегрирующие элементы 2, 3 работают идентично, в их работе можно выделить три такта. В первом такте ключ 16 (18) открыт, ключ 17 (19) закрыт- идет интегрированиеJ во втором такте ключи 16 (18), 17 (19) закрыты, сохраняется потенциал, накопленный на конденсаторе 20 (21) в первом такте , в третьем такте по поступлении контролируемого импульса открывается ключ 17 (19), происходит быстрьй разряд конденсатора 20(21). Выходные напряжения с интегрирующих элементов сравниваются компаратором 4, который формирует на свой выход двухполярный сигнал (фиг.2ж). Сигнал с выхода компаратора 4 поступает на входы формирователей импульсов 5, 6, которые вырабатывают на свои выходы короткие импульсы (фиг.2э,и) на разные фронты входного сигнала. Эти импульсы через элемент ИЛИ 7 проходят на первый вход элемента И 8, но на шину 9 проходят лишь в случае потери импуль

тельности элемент И 8 оказывается закрытым сигналом с второго входа.

40

поступающим с выхода инвертора 13.

Формула изобретения

Устройство для обнаружения поте- ри импульсов, содержащее триггер, два формирователя импульсов, элемент И, отличающееся тем, что, с целью упрощения, в него введены два элемента И, два интегрирующих элемента, компаратор, элемент ИЛИ и инвертор, причем входная шина подключена к входу триггера, первым входам первого и второго элементов И и входу инвертора, первый выход триггера подключен к первому управляющему входу первого интегрирующего элемента и второму входу второго элемента И, второй выход триггера подключен к первому управляющему вхо3128

ду второго интегрирукяцего элемента и второму входу первого элемента И, выходы первого и второго элементов И подключены к вторым управляющим входам соответственно первого и второго интегрирующих элементов, выходы которых подключены к входам ком7264

паратора, выход которого подключен к входам двух формирователей импульсов, выходы которых через элемент ИЛИ подключены к первому входу третьего элемента И, второй вход которого подключен к выходу инвертора, а его выход - к выходной шине.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь синусно-косинусных сигналов в последовательность импульсов | 1988 |

|

SU1737731A1 |

| Интегрирующий аналого-цифровой преобразователь | 1985 |

|

SU1279069A1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1991 |

|

SU1785075A1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1989 |

|

SU1695503A1 |

| УСТРОЙСТВО ОХРАННОЙ СИГНАЛИЗАЦИИ | 1991 |

|

RU2031445C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Интегрирующий аналого-цифровой преобразователь | 1986 |

|

SU1410274A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1552377A1 |

| ФОРМИРОВАТЕЛЬ КОМАНД УПРАВЛЕНИЯ | 2003 |

|

RU2244960C2 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

Изобретение относится к импульсной технике. Цель - упрощение конструкции. Она достигается тем, что в устройство для обнаружения потери импульсов, содержащее триггер 1, формирователи импульсов 5, 6, элемент И 8, выходную и входную шины 9, 10, введены интегрирующие элементы (ИЭ) 2, 3, компаратор А, элемент ИЛИ 7, элементы И 11, 12 и инвертор 13, при этом ИЭ 2, 3 содержит резисторы 14, 15, ключи 16-19 с управляющими входами, конденсаторы 20, 21. Изобретение может быть использовано для контроля импульсных последовательностей. 2 ил. с & (Л CPUS. 7

П

И

П

11

г

ж

n

I I

Пп.

и

11

t

-t

и к

Редактор М.Циткина

Заказ. 7728/58Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

фиг. 2

Составитель В.Герасимов

Техред И.Попович Корректор М.Демчик

| Устройство для обнаружения потерииМпульСОВ | 1979 |

|

SU834877A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для обнаружения сбоев в импульсной последовательности | 1981 |

|

SU1039024A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-01-30—Публикация

1985-06-03—Подача