Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством.

Целью изобретения является повышение достоверности и быстродействия преобразователя.

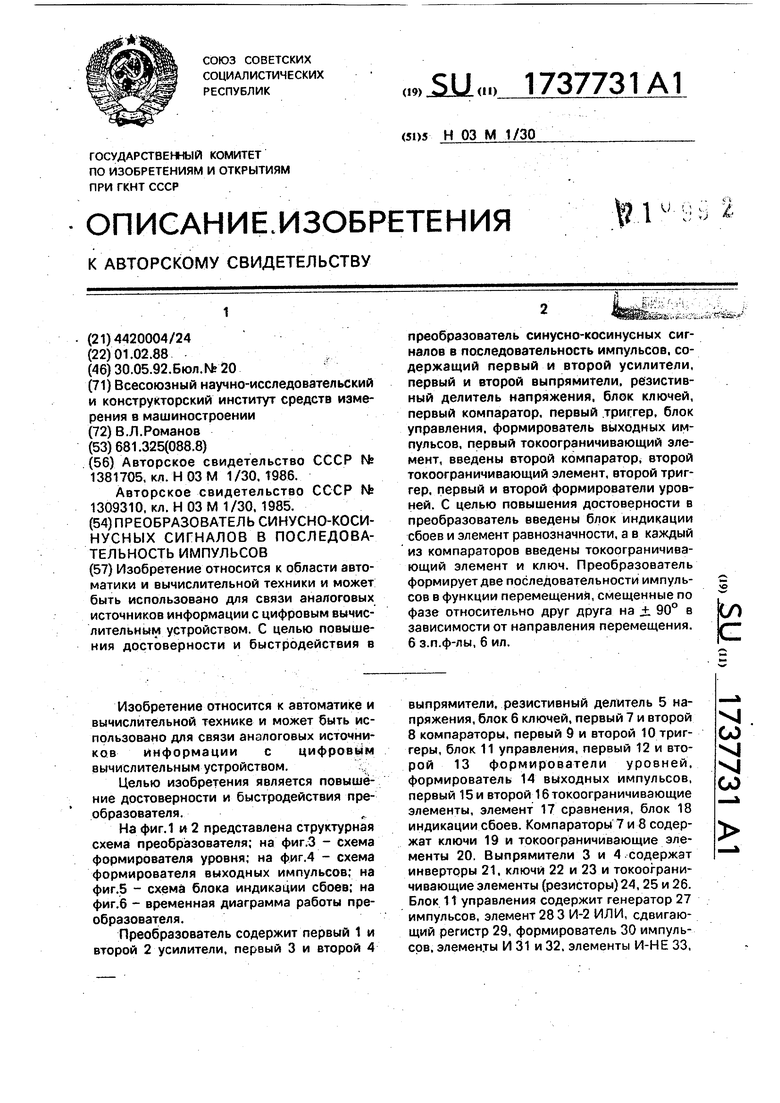

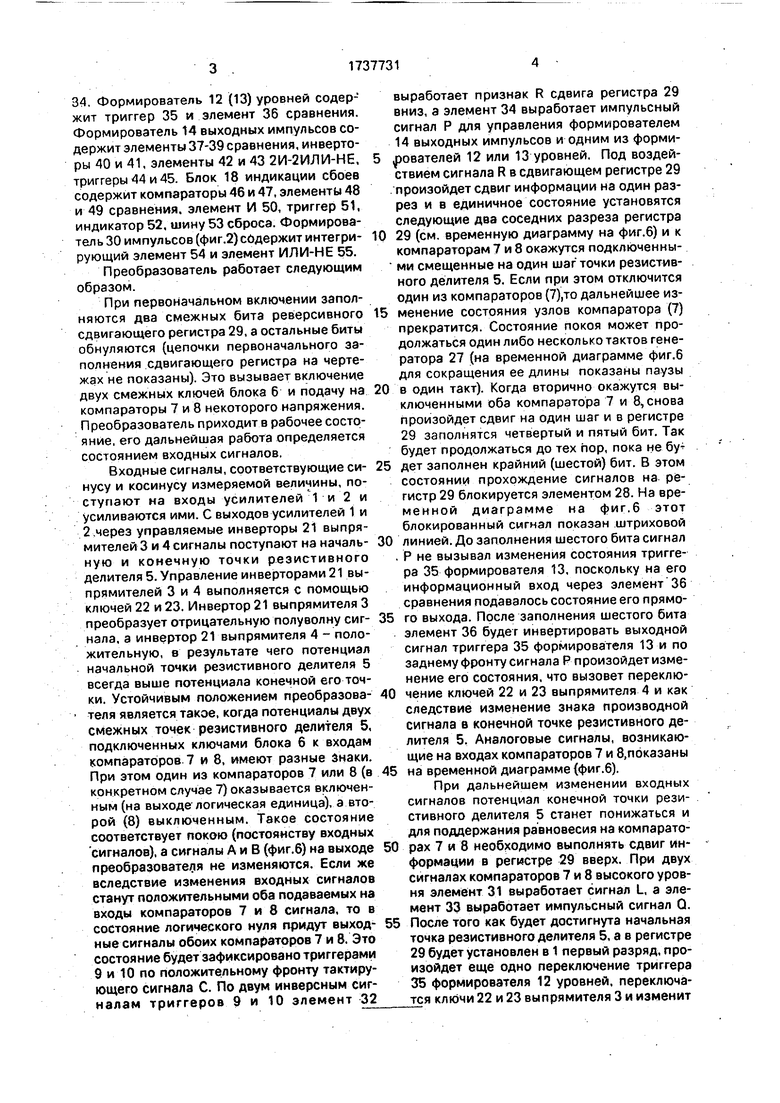

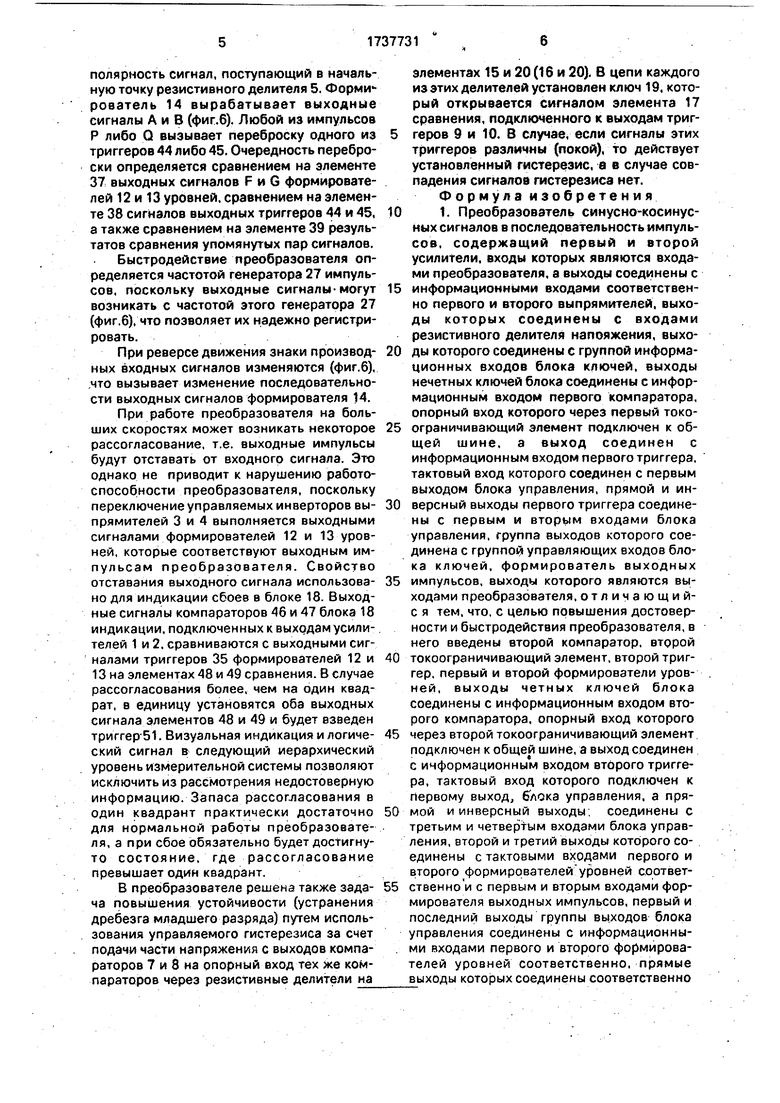

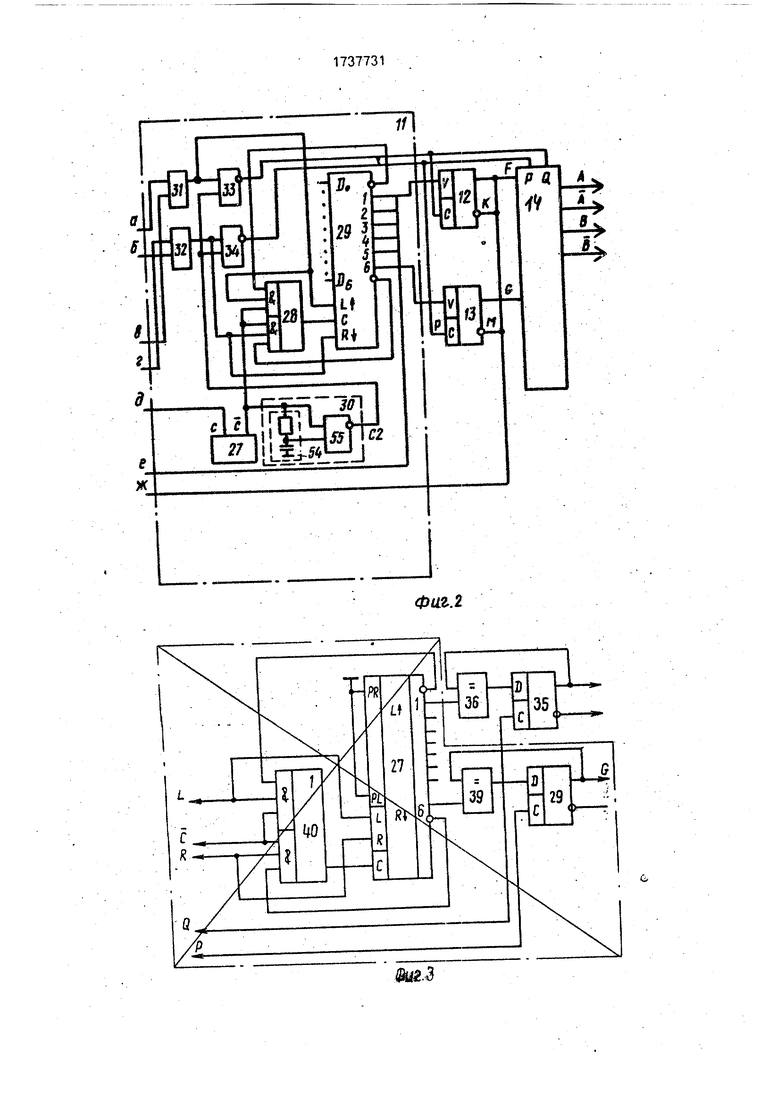

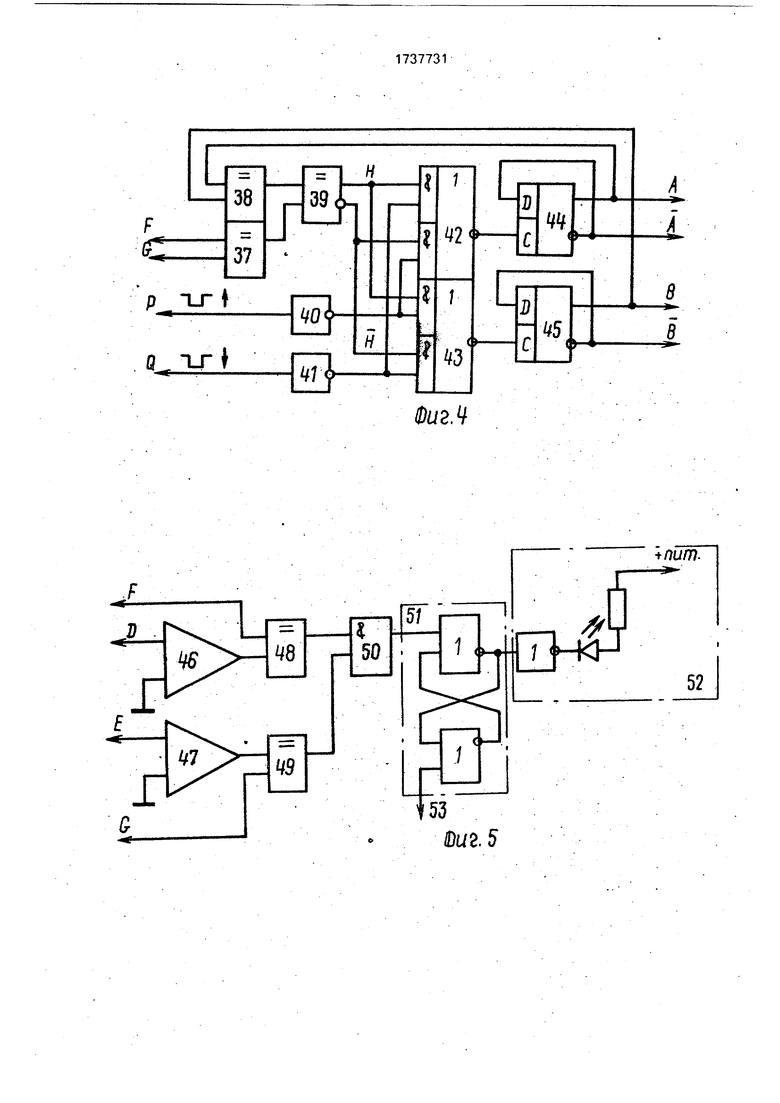

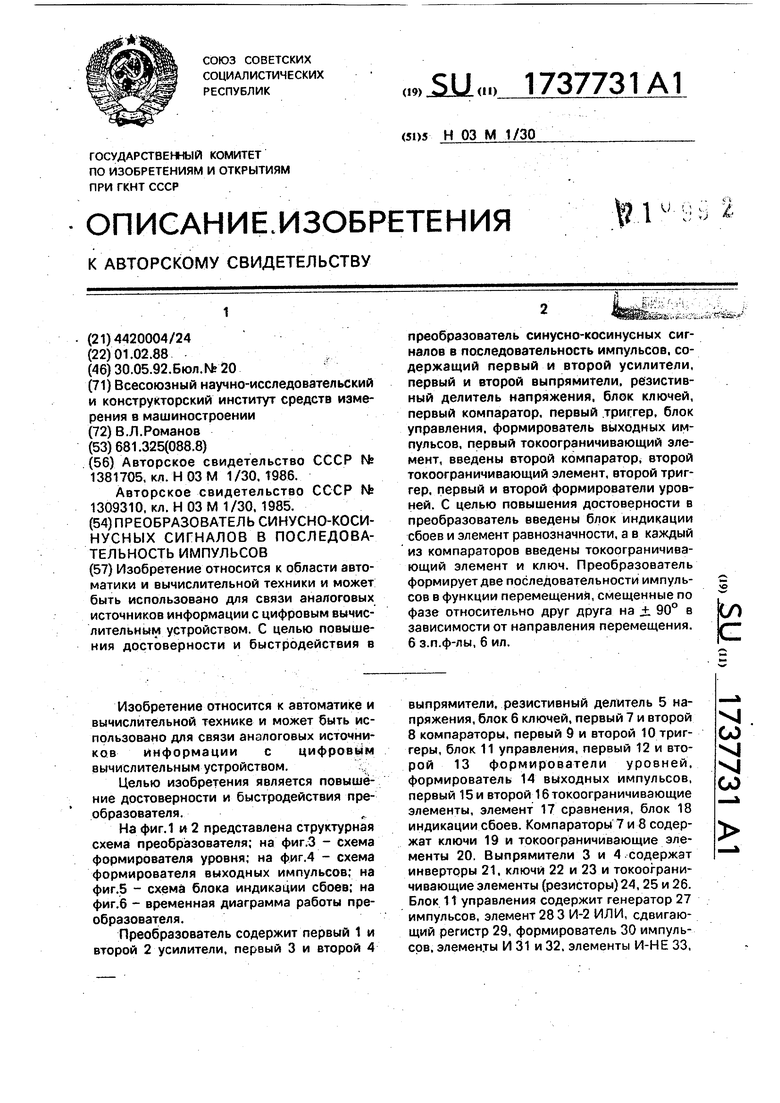

На фиг.1 и 2 представлена структурная схема преобразователя; на фиг.З - схема формирователя уровня; на фиг.4 - схема формирователя выходных импульсов; на фиг.5 - схема блока индикации сбоев; на фиг.6 - временная диаграмма работы преобразователя.

Преобразователь содержит первый 1 и второй 2 усилители, первый 3 и второй 4

выпрямители, резистивный делитель 5 напряжения, блок 6 ключей, первый 7 и второй 8 компараторы, первый 9 и второй 10 триггеры, блок 11 управления, первый 12 и второй 13 формирователи уровней, формирователь 14 выходных импульсов, первый 15 и второй 16токоограничивающие элементы, элемент 17 сравнения, блок 18 индикации сбоев. Компараторы 7 и 8 содержат ключи 19 и токоограничивающие элементы 20. Выпрямители 3 и 4 содержат инверторы 21, ключи 22 и 23 и токоограничивающие элементы (резисторы) 24, 25 и 26. Блок 11 управления содержит генератор 27 импульсов, элемент 283 И-2 ИЛИ, сдвигающий регистр 29, формирователь 30 импульсов, элементы И 31 и 32, элементы И-НЕ 33,

VI

CJ

VI VI со

34. Формирователь 12 (13) уровней содержит триггер 35 и элемент 36 сравнения. Формирователь 14 выходных импульсов содержит элементы 37-39 сравнения, инверторы 40 и 41, элементы 42 и 43 2И-2ИЛИ-НЕ, триггеры 44 и 45. Блок 18 индикации сбоев содержит компараторы 46 и 47, элементы 48 и 49 сравнения, элемент И 50, триггер 51, индикатор 52, шину 53 сброса. Формирователь 30 импульсов (фиг.2) содержит интегрирующий элемент 54 и элемент ИЛИ-НЕ 55.

Преобразователь работает следующим образом.

При первоначальном включении заполняются два смежных бита реверсивного сдвигающего регистра 29, а остальные биты обнуляются (цепочки первоначального заполнения сдвигающего регистра на чертежах не показаны). Это вызывает включение двух смежных ключей блока 6 и подачу на компараторы 7 и 8 некоторого напряжения. Преобразователь приходит в рабочее состояние, его дальнейшая работа определяется состоянием входных сигналов.

Входные сигналы, соответствующие синусу и косинусу измеряемой величины, поступают на входы усилителей 1 и 2 и усиливаются ими. С выходов усилителей 1 и 2 через управляемые инверторы 21 выпрямителей 3 и 4 сигналы поступают на начальную и конечную точки резистивного делителя 5. Управление инверторами 21 выпрямителей 3 и 4 выполняется с помощью ключей 22 и 23. Инвертор 21 выпрямителя 3 преобразует отрицательную полуволну сигнала, а инвертор 21 выпрямителя 4 - положительную, в результате чего потенциал начальной точки резистивного делителя 5 всегда выше потенциала конечной его точки. Устойчивым положением преобразователя является такое, когда потенциалы двух смежных точек резистивного делителя 5, подключенных ключами блока 6 к входам компараторов 7 и 8, имеют разные знаки. При этом один из компараторов 7 или 8 (в конкретном случае 7) оказывается включенным (на выходе логическая единица), а второй (8) выключенным. Такое состояние соответствует покою (постоянству входных сигналов), а сигналы А и В (фиг.6) на выходе преобразователя не изменяются. Если же вследствие изменения входных сигналов станут положительными оба подаваемых на входы компараторов 7 и 8 сигнала, то в состояние логического нуля придут выходные сигналы обоих компараторов 7 и 8. Это состояние будет зафиксировано триггерами 9 и 10 по положительному фронту тактирующего сигнала С. По двум инверсным сигналам триггеров 9 и 10 элемент 32

выработает признак R сдвига регистра 29 вниз, а элемент 34 выработает импульсный сигнал Р для управления формирователем 14 выходных импульсов и одним из формирователей 12 или 13 уровней, Под воздействием сигнала R в сдвигающем регистре 29 произойдет сдвиг информации на один разрез и в единичное состояние установятся следующие два соседних разреза регистра

29 (см. временную диаграмму на фиг.6) и к компараторам 7 и 8 окажутся подключенны- ми смещенные на один шаг точки резистивного делителя 5. Если при этом отключится один из компараторов (7),то дальнейшее изменение состояния узлов компаратора (7) прекратится. Состояние покоя может продолжаться один либо несколько тактов генератора 27 (на временной диаграмме фиг.6 для сокращения ее длины показаны паузы

в один такт). Когда вторично окажутся выключенными оба компаратора 7 и 8, снова произойдет сдвиг на один шаг и в регистре 29 заполнятся четвертый и пятый бит. Так будет продолжаться до тех пор, пока не будет заполнен крайний (шестой) бит. В этом состоянии прохождение сигналов на регистр 29 блокируется элементом 28. На вре- менной диаграмме на фиг.6 этот блокированный сигнал показан штриховой

линией. До заполнения шестого бита сигнал . Р не вызывал изменения состояния триггера 35 формирователя 13, поскольку на его информационный вход через элемент 36 сравнения подавалось состояние его прямого выхода. После заполнения шестого бита элемент 36 будет инвертировать выходной сигнал триггера 35 формирователя 13 и по заднему фронту сигнала Р произойдет изменение его состояния, что вызовет переключение ключей 22 и 23 выпрямителя 4 и как следствие изменение знака производной сигнала в конечной точке резистивного делителя 5. Аналоговые сигналы, возникающие на входах компараторов 7 и 8,показаны

на временной диаграмме (фиг.6).

При дальнейшем изменении входных сигналов потенциал конечной точки резистивного делителя 5 станет понижаться и для поддержания равновесия на компаратоpax 7 и 8 необходимо выполнять сдвиг информации в регистре 29 вверх. При двух сигналах компараторов 7 и 8 высокого уровня элемент 31 выработает сигнал L, а элемент 33 выработает импульсный сигнал Q.

После того как будет достигнута начальная точка резистивного делителя 5, а в регистре 29 будет установлен в 1 первый разряд, произойдет еще одно переключение триггера 35 формирователя 12 уровней, переключатся ключи 22 и 23 выпрямителя 3 и изменит

полярность сигнал, поступающий в начальную точку резистивного делителя 5. Форми- рователь 14 вырабатывает выходные сигналы А и В (фиг.б). Любой из импульсов Р либо Q вызывает переброску одного из триггеров 44 либо 45. Очередность переброски определяется сравнением на элементе 37 выходных сигналов F и G формирователей 12 и 13 уровней, сравнением на элементе 38 сигналов выходных триггеров 44 и 45, а также сравнением на элементе 39 результатов сравнения упомянутых пар сигналов.

Быстродействие преобразователя определяется частотой генератора 27 импульсов, поскольку выходные сигналы-могут возникать с частотой этого генератора 27 (фиг.б), что позволяет их надежно регистрировать.

При реверсе движения знаки производных входных сигналов изменяются (фиг.б), что вызывает изменение последовательности выходных сигналов формирователя 14.

При работе преобразователя на больших скоростях может возникать некоторое рассогласование, т.е. выходные импульсы будут отставать от входного сигнала. Это однако не приводит к нарушению работоспособности преобразователя, поскольку переключение управляемых инверторов выпрямителей 3 и 4 выполняется выходными сигналами формирователей 12 и 13 уровней, которые соответствуют выходным импульсам преобразователя. Свойство отставания выходного сигнала использовано для индикации сбоев в блоке 18. Выходные сигналы компараторов 46 и 47 блока 18 индикации, подключенных к выходам усилителей 1 и 2, сравниваются с выходными сигналами триггеров 35 формирователей 12 и 13 на элементах 48 и 49 сравнения. В случае рассогласования более, чем на один квадрат, в единицу установятся оба выходных сигнала элементов 48 и 49 и будет взаеден триггер 51. Визуальная индикация и логический сигнал в следующий иерархический уровень измерительной системы позволяют исключить из рассмотрения недостоверную информацию. Запаса рассогласования в один квадрант практически достаточно для нормальной работы преобразователя, а при сбое обязательно будет достигнуто состояние, где рассогласование превышает один квадрант.

В преобразователе решена также задача повышения устойчивости (устранения дребезга младшего разряда) путем использования управляемого гистерезиса за счет подачи части напряжения с выходов компараторов 7 и 8 на опорный вход тех же компараторов через резистивные делители на

элементах 15 и 20 (16 и 20). В цепи каждого из этих делителей установлен ключ 19, который открывается сигналом элемента 17 сравнения, подключенного к выходам триг- 5 герое 9 и 10. В случае, если сигналы этих триггеров различны (покой), то действует установленный гистерезис, а в случае совпадения сигналов гистерезиса нет. Формула изобретения

10 1. Преобразователь синусно-косинус- ных сигналов в последовательность импульсов, содержащий первый и второй усилители, входы которых являются входами преобразователя, а выходы соединены с

5 информационными входами соответственно первого и второго выпрямителей, выходы которых соединены с входами резистивного делителя напояжения, выхо0 ды которого соединены с группой информационных входов блока ключей, выходы нечетных ключей блока соединены с информационным входом первого компаратора, опорный вход которого через первый токо5 ограничивающий элемент подключен к общей шине, а выход соединен с информационным входом первого триггера, тактовый вход которого соединен с первым выходом блока управления, прямой и ин0 версный выходы первого триггера соединены с первым и вторым входами блока управления, группа выходов которого соединена с группой управляющих входов блока ключей, формирователь выходных

5 импульсов, выходы которого являются выходами преобразователя, отличающий- с я тем, что, с целью повышения достоверности и быстродействия преобразователя, в него введены второй компаратор, второй

0 токоограничивающий элемент, второй триггер, первый и второй формирователи уровней, выходы четных ключей блока соединены с информационным входом второго компаратора, опорный вход которого

5 через второй токоограничивающий элемент подключен к общей шине, а выход соединен с информационным входом второго триггера, тактовый вход которого подключен к Первому выход, блока управления, а пря0 мой и инверсный выходы соединены с третьим и четвертым входами блока управления, второй и третий выходы которого соединены с тактовыми входами первого и второго формирователей уровней соответ5 ственно и с первым и вторым входами формирователя выходных импульсов, первый и последний выходы группы выходов блока управления соединены с информационными входами первого и второго формирователей уровней соответственно, прямые выходы которых соединены соответственно

с третьим и четвертым входами формирова-- теля выходных импульсов, прямой и инверсный выходы первого формирователя уровней соединены с управляющими входами первого выпрямителя, прямой и инверс- ный выходы второго формирователя уровней соединены с управляющими входами второго выпрямителя, выходы первого и второго выпрямителей соединены с дополнительными информационными входами блока ключей.

2.Преобразователь по п. 1, о т л и ч а ю- щ и и с я тем, что, с целью повышения достоверности, в него введены элемент сравнения, третий и четвертый токоограни- чивающие элементы и первый и второй ключи, входы элемента сравнения подключены к прямым выходам первого и второго триггеров, а выход соединен с управляющими входами первого и второго ключей, выходы первого и второго ключей соединены с опорными входами соответственно первого и второго компараторов, а информационные входы подключены к выходам одноименных компараторов соответственно через третий и четвертый токоограничиваю- щие элементы,

3.Преобразователь по п.1. о т л и ч а ю- щ и и с я тем, что блок управления содержит генератор импульсов, формирователь импульсов, два элемента И, два элемента И-НЕ, элемент ЗИ-2ИЛИ, сдвигающий регистр, первый выход генератора импульсов является первым выходом блока управления, второй выход генератора импульсов соединен с входом формирователя импульсов и первыми входами первой и второй групп входов элемента ЗИ-2ИЛИ, входы первого элемента И являются первым и третьим вхо- дами блока управления, входы второго элемента И являются вторым и четвертым входами блока управления, выход первого элемента И соединен с первым входом первого элемента И-НЕ, вторым входом первой группы входов элемента ЗИ-2ИЛИ и первым управляющим входом сдвигающего регистра, выход второго элемента И соединен с первым входом второго элемента И-НЕ, вторым входом второй группы входов элемента ЗИ-2ИЛИ и вторым управляющим входом сдвигающего регистра, выход формирователя импульсов соединен с вторыми входами первого и второго элементов И-НЕ, выходы которых являются соответственно вторым и третьим выходами блока управления, выход элемента ЗИ-2ИЛИ соединен с тактовым входом сдвигающего регистра, прямые выходы разрядов которого являются группой выходов блока управления, а инверсные выходы первого и последнего

разрядов соединены с третьими входами соответственно первой и второй групп входов элемента ЗИ-2ИЛИ.

4.Преобразовательпоп.1,отличаю- щ и и с я тем, что формирователь уровней

Содержит триггер и элемент сравнения, первый вход которого является информационным входом формирователя уровней, выход элемента сравнения соединен с информа0 ционным входом триггера, тактовый вход которого является тактовым входом формирователя уровней, прямой -выход триггера соединен с вторым входом элемента сравнения, а прямой и инверсный выходы триг5 гера являются прямым и инверсным выходами формирователя уровней.

5.Преобразователь по п.1, о т л и ч а ю- щ и и с я тем, что формирователь выходных импульсов содержит три элемента сравне0 ния, два инвертора, два элемента 2И-2ИЛИ- НЕ, два триггера, входы первого и второго инверторов являются соответственно первым и вторым входами формирователя выходных импульсов, а входы первого

5 элемента сравнения являются третьим и четвертым входами формирователя выходных импульсов, выходы первого и второго элементов сравнения соединены с входами третьего элементу сравнения, прямой вы0 ход которого соединен с первыми входами , первых пар входов первого и второго элементов 2И-2ИЛИ-НЕ, а инверсный выход соединен с первыми входами вторых пар входов первого и второго элементов 2И5 2ИЛИ-НЕ, выход первого инвертора соединен с вторыми входами второй пары входов первого элемента 2И-2ИЛИ-НЕ и.первой пары входов второго элемента 2И-2ИЛИ-НЕ, выход второго инвертора соединен с вторы0 ми входами первой пары входов первого элемента 2И-2ИЛИ-НЕ и второй пары входов второго элемента 2И-2ИЛИ-НЕ, выходы первого и второго элементов 2И-2ИЛИ-НЕ соединены со счетными входами соответст5 венно первого и второго триггеров, прямые выходы которых соединены с входами второго элемента сравнения, а прямые и инверсные выходы триггеров являются прямыми и инверсными выходами формирователя вы0 ходных импульсов.

6.Преобразователь по п.1, о т л и ч а ю- щ и и с я тем, что, с целью повышения достоверности преобразователя, в него введен блок индикации сбоев, первый и второй

5 входы которого подключены к выходам первого и второго усилителей, а третий и четвертый входы - к прямым выходам первого и второго формирователей уровней соответственно, при этом блок индикации сбоев содержит два компаратора, два элемента

сравнения, элемент И, триггер и индикатор, информационные входы первого и второго компараторов являются первым и вторым входами блока индикации сбоев, первые входы первого и второго элементов сравнения являются третьим и четвертым входами блока индикации сбоев, выходы первого и второго компараторов соединены с вторыми входами первого и второго элементов сравнения, выходы которых соединены с входами элемента И, выход элемента И соединен с первым входом триггера, второй вход .которого соединен с шиной сброса, а

0

выход триггера соединен с входом индикатора.

7. Преобразователь по пп.1 и 3, о т л и ч а- ю щ и и с я тем, что формирователь импульсов содержит интегрирующий элемент и элемент ИЛИ-НЕ, первый вход которого является входом формирователя импульсов и соединен с входом интегрирующего элемента, выход интегрирующего элемента соединен с вторым входом элемента ИЛИ-НЕ, выход которого является выходом формирователя импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Аналого-цифровой преобразователь неэлектрических величин | 1985 |

|

SU1403374A1 |

| Преобразователь синусно-косинусных сигналов в последовательность импульсов | 1986 |

|

SU1381705A1 |

| Устройство для определения междуфазных замыканий и замыканий на землю в сетях с изолированной нейтралью напряжением 6-10 кВ | 2022 |

|

RU2788035C1 |

| Многоканальное устройство для управления вентильным преобразователем | 1990 |

|

SU1777216A1 |

| Устройство для управления преобразователем постоянного напряжения,включающем резонансный тиристорный инвертор с транзисторным ключем на входе | 1982 |

|

SU1030945A1 |

| Устройство для управления группой N статических преобразователей частоты,включенных параллельно по входу и выходу | 1986 |

|

SU1388973A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Самонастраивающееся устройство управления | 1983 |

|

SU1130830A1 |

| Устройство для измерения параметров дыхания | 1990 |

|

SU1803037A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью повышения достоверности и быстродействия в 1. преобразователь синусно-косинусных сигналов в последовательность импульсов, содержащий первый и второй усилители, первый и второй выпрямители, резистив- ный делитель напряжения, блок ключей, первый компаратор, первый триггер, блок управления, формирователь выходных импульсов, первый токоограничивающий элемент, введены второй компаратор, второй токоограничивающий элемент, второй триггер, первый и второй формирователи уровней. С целью повышения достоверности в преобразователь введены блок индикации сбоев и элемент равнозначности, а в каждый из компараторов введены токоограничивающий элемент и ключ. Преобразователь формирует две последовательности импульсов в функции перемещения, смещенные по фазе относительно друг друга на +. 90° в зависимости от направления перемещения. 6 з.п.ф-лы, 6 ил. сл с

Фиг.1

Фаг. 2

ФигМ

Ш2.5

Tj / 1 :

s 1

i e ai g 9 .

| Преобразователь синусно-косинусных сигналов в последовательность импульсов | 1986 |

|

SU1381705A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь синусно-косинусных сигналов в последовательность импульсов | 1985 |

|

SU1309310A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-05-30—Публикация

1988-02-01—Подача