очередности коммутируемых каналов. Устройство содержит блок 1 управления, два счетчика 2, 6, элемент ИЛИ 3, элемент И 4, блок 5 элементов ИЛИ, блок 7 памяти, регистр 8, дешифратор 9. В устройства введены блок 10 ввода, генератор 11 импульсов, блок 12 памяти, блок 13 анализа, триггеры 14-16, элементы И 17-19, элемент ИЛИ 20, формирователи 21-23

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах для программного управления и коммутации каналов с заданной очередностью.

Целью изобретения йвляется повышение достоверности работы устройства путем, контроля на каждом шаге коммутации очередности коммутируемых каналов.

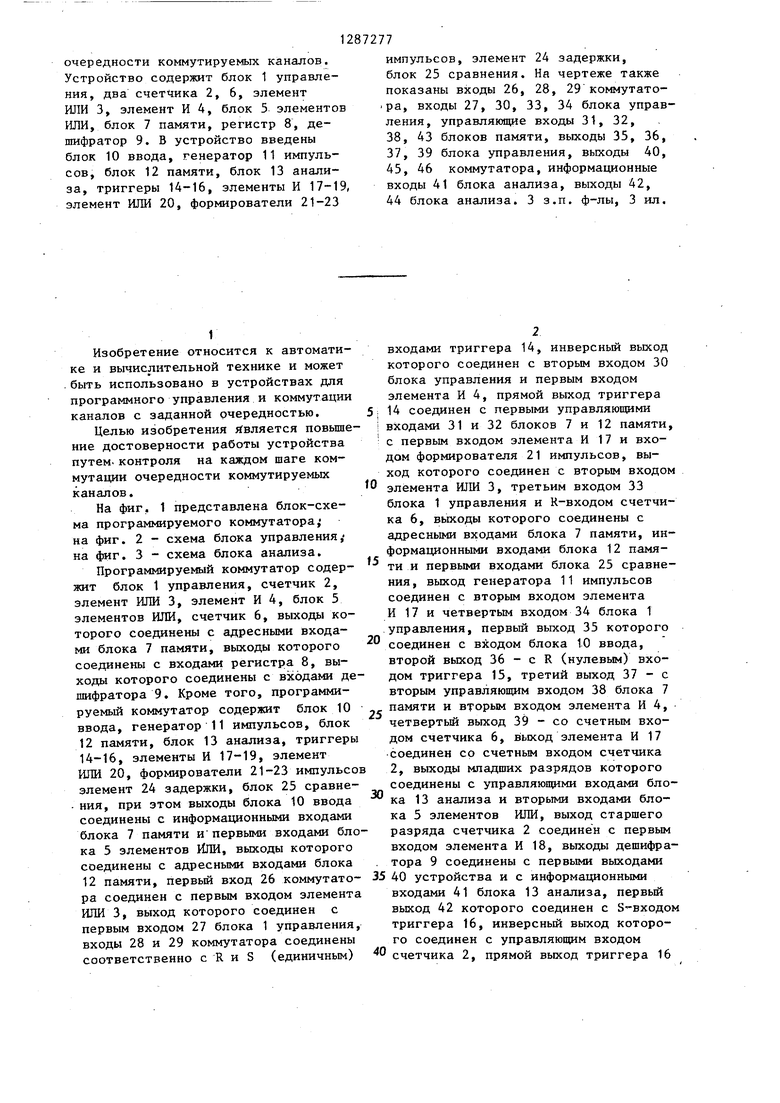

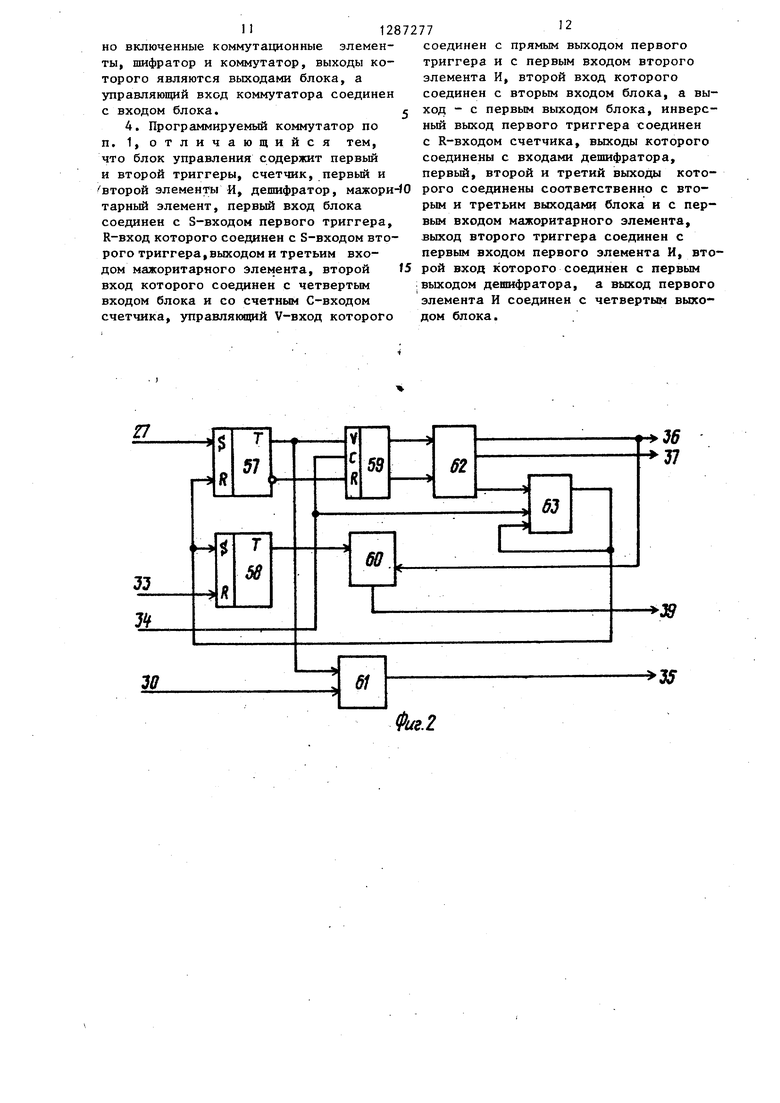

На фиг. 1 представлена блок-схема программируемого коммутатора; на фиг. 2 - схема блока управления,- на фиг. 3 - схема блока анализа.

Программируемый коммутатор содержит блок 1 управления, счетчик 2, элемент ИЛИ 3, элемент И 4, блок 5 элементов ИЛИ, счетчик 6, выходы которого соединены с адресными входами блока 7 памяти, выходы которого соединены с входами регистра 8, выходы которого соединены с входами дешифратора 9. Кроме того, программируемый коммутатор содержит блок 10 ввода, генератор 11 импульсов, блок 12 памяти, блок 13 анализа, триггеры 14-16, элементы И 17-19, элемент ИЛИ 20, формирователи 21-23 импульсо элемент 24 задержки, блок 25 сравне- - ния, при этом выходы блока 10 ввода соединены с информационными входами блока 7 памяти и первыми входами блока 5 элементов ИЛИ, выходы которого соединены с адресными входами блока 12 памяти, первый вход 26 коммутато- ра соединен с первым входом элемента ИЛИ 3, выход которого соединен с первым входом 27 блока 1 управления, входы 28 и 29 коммутатора соединены соответственно с R и S (единичным)

7277

импульсов, элемент 24 задержки, блок 25 сравнения. На чертеже также показаны входы 26, 28, 29 коммутато- .ра, входы 27, 30, 33, 34 блока управления, управляющие входы 31, 32, 38, 43 блоков памяти, выходы 35, 36, 37, 39 блока управления, выходы 40, 45, 46 коммутатора, информационные входы 41 блока анализа, выходы 42, 44 блока анализа. 3 з.п. ф-лы, 3 ил.

5

5

0

5

0

0

входами триггера 14, инверсный выход которого соединен с вторым входом 30 блока управления и первым входом элемента И 4, прямой выход триггера 14 соединен с первыми управляющими входами 31 и 32 блоков 7 и 12 памяти, с первым входом элемента И 17 и входом формирователя 21 импульсов, выход которого соединен с вторым входом элемента ШШ 3, третьим входом 33 блока 1 управления и R-входом счетчика 6, выходы которого соединены с адресными входами блока 7 памяти, информационными входами блока 12 памяти и первыми входами блока 25 сравнения , выход генератора 11 импульсов соединен с вторым входом элемента И 17 и четвертым входом 34 блока 1 управления, первый выход 35 которого соединен с входом блока 10 ввода, второй выход 36 - с R (нулевым) входом триггера 15, третий выход 37 - с вторым управляющим входом 38 блока 7 памяти и вторым входом элемента И 4, четвертый выход 39 - со счетным входом счетчика 6, выход элемента И 17 соединен со счетным входом счетчика 2, выходы младших разрядов которого соединены с управляющими входами блока 13 анализа и вторыми входами блока 5 элементов ИЛИ, выход старшего разряда счетчика 2 соединен с первым входом элемента И 18, выходы дешифратора 9 соединены с первыми выходами 40 устройства и с информационными входами 41 блока 13 анализа, первый выход 42 которого соединен с S-входом триггера 16, инверсный выход которого соединен с управляющим входом счетчика 2, прямой выход триггера 16

соединен через последовательно включенные формирователь 22 импульсов и элемент 24 задержки с первым входом элемента ШШ 20, второй вход которого соединен с выходом элемента И 4, выход элемента ИЛИ 20 соединен с. вторым .управляющим входом 43 блока 12 памяти, выходы которого соединены с вторыми входами блока 25 сравнения, выход .которого соединен с первым входом элемента И 19, второй вход которого соединен с вторым выходом 44 блока 13 анализа, выход элемента И 19 соединен с S-входом триггера 15, прямой выход которого является вторым выходом 45 коммутатора, и соединен с входом формирователя 23 импульсов, инверсный выход триггера 15 соединен с вторым входом элемента И 18, выход которого является третьим выходом 46 устройства, выход формирователя 23 импульсов соединен с R-входами регистра 8, триггера 16, счетчика 2 и третьим входом элемента ИЛИ 3. Кроме того, блок 13 анализа содержит группы 47 и 48 элементов И, группу 49 элементов ИЛИ, инверторы 50, 51, элементы ИЛИ 52, 53, дешифратор 54, причем первый информационный вход 41.1 блока 13 анализа соединен с вторым входом элемен- иа 49.1 ИЛИ из группы 49 элементов ИЛИ, вторым входом элемента 47.1 И из первой группы 47 элементов И и первьм входом элемента 48.1 И из группы 48 элементов И, информационные входы 41.2-41.N блока соединены с первыми входами соответствующих элементов ИЛИ из группы 49 элементов ИЛИ и элементов И из групп 47 и 8 элементов И, выход каждого предыдущего элемента ИЛИ из группы 49 элементов ИЛИ соединен с вторыми входами последующих элементов ИЛИ из группы 9 элементов ИЛИ и элемента И из группы 47 элементов И, выходы элеентов И группы 47 элементов И и выход элемента 49.N-1 ИЛИ из группы 49 элементов ИЛИ через инвертор 50 соединены с входами элемента ИЛИ 52, вьпсод которого через инвертор 51 сое- инен с вторым выходом 44 блока 13 анализа, управляющие входы блока 13 нализа соединены с входами дешифраора 54, выходы которого соединены с торыми входами элементов И из груп ы 48 элементов И, выходы которых оединены с входами элемента ШШ 53, ыход которого соединен с первым выодом 42 блока 13.

Кроме того, блок 10 ввода содержит последовательно включенные коммутационные элементы, шифратор 55 и коммутатор 56, выходы которого явля- -ются выходами блока 10 ввода, а управляющий вход коммутатора 56 - входом блока 10 ввода. Блок 1 управления содержит триггеры 57 и 58, счетчик 59, элементы И 60 и 61, дешифратор 62,

O мажоритарный элемент 63, вход 27

блока 1 управления соединен с S-входом триггера 57, R-вход которого соединен с S-входом триггера 58, выходом и третьим входом мажоритарного эле5 мента 63, второй вход которого соединен с входом 34 блока 1 управления и со счетным С-входом счетчика 59, управляющий V-вход которого соединен с прямым выходом триггера 57 и с пер0 вым входом элемента.И 61, второй вход которого соединен с входом 30 блока 1 управления, а выход - с выходом 35 блока 1 управления, инверсный выход триггера 57 соединен с R-входом

5 счетчика 59, выходы которого соединены с входами дешифратора 62, первый, второй и третий выходы которого соединены соответственно с выходами 36 и 37 блока 1 управления и с первым

0 входом мажоритарного элемента 63, выход триггера 58 соединен с первым входом элемента И 60, второй вход которого соединен с первым выходом дешифратора 62, а выход элемента

5 И 60 соединен с выходом 39 блока 1 управления.

0

5

0

5

Программньй коммутатор работает следующим образом.

В исходном состоянии триггеры, регистр, счетчики, блоки памяти находятся в нулевом состоянии. Работа устройства разделяется на р ежимы записи и чтения. В режиме записи в блоки памяти 7 и 12 с помощью блока 10 вводится программа коммутации каналов. В этом режиме триггер 14 устанавливается внешним сигналом ЗАПИСЬ с входа 28 в нулевое состояние и подготавливает к открыванию элементы И 4, 61. В блоке 10 ввода каждая клавиша (коммутационный элемент) соответствует определенному каналу, а очередность нажатия клавиш соответствует заданной программируемой очередности коммутации каналов. Клавиши взаимоисключающие. При нажатии одной клавиши на выходе шифратора 55 формируется код данной клавиши, который подается на входы коммутатора

56. По импульсному сигналу BBOfl j который затем подается оператором, по входу 26 через элемент ИЛИ 3 срабатывает триггер 57 в блоке 1. Триггер 57 включает счетчик 59, на кото- рый поступают тактовые импульсы от генератора 11, Счетчик 59 образует с дешифратором 62 распределитель Кроме того,, триггер 57 открывает элемент И 61 сигнал с выхода которо- tO го разрешает подачу кода нал-сатой клавиши с выхода коммутатора 56 на информационньй вход блока 7 памяти и через блок 5 элементов ИЛИ на адресньш вход блока 12 памяти. Счет- 15 чик 6 находится в нулевом состоянииj и с его выходов нулевой код подаемся на адресные входы блока 7 памяти, и на информационные входы блока 12 памяти, Лри нулевом состоянии триг- 20 гера 14 на управляюа ие входы резки- -мов блоков 7, 12 памяти подаются низкие уровни, соответствуюаще режиму записи, Б блоке 1 управления импульс с первого выхода дешифратора 62 обнуляет триггер 15 и подается на элемент И 60 Импульс с второго выхода дешифратора 62 подается на второй вход 38 управления блока 7 памяти и через элемент И 4 и элемент ИЛИ 20 на второй вход 43 управления блока 12 памяти, В блоке 7 памяти по нулевому адресу записывается код . клавиши5 нажатой первой, В блоке 12 памяти по а,цресу5 которьп является код нажатой ютавипш, записывается

12872776

очередной клавиши 5 и следующей подачи сигнала Ввод по входу 26 в блоке 1 управления снова включается распределитель. При этом сигнал с , первого выхода дешифратора 62 открывает элемент И 60.с выхода которого и myльc подается на счетный вход счетчикд 6 и увеличивает его состояние на единицу с Код очередной нажатой клавиши записывается в блок 7 па мяти по следующему адресу, а в блок 12 памяти, записывается код со счетчи ка 6 по адресу,, заданному кодом очередной клавиши. Таким образом, после очередного нажатия одной из клавиш в ;блоке 7 памяти формируется очередь и кодов коммутируемых каналов, а в бло

ке 12 памяти будут очередей каналов.

записаны номера

Режим коммутации задается сигнало Чтение,, подаваемым на вход 29, триггер 14 устанавливается в единичное состояние л подает высокий потен 25 циал на управляющие входы режимов блоков 7 и 12 памяти, что соответствует режиму чтения, и снимает сигнал разрешения с входов элементов И 4 и 61, тем самьп-4 блок 10 ввода отключа3; ется от входов блоков 7 и 12 П:амяти, При срабатывании триггера 14 на выходе формирователя 21 формируется импульс5 который устанавливает в нулевое состояние счетчик 6, триггер

:з 58 в блоке 1 управления и через элемент /иШ 3 - в единичное состояние триггер 57 в блоке 1 управления. В блоке 1 аналогично включается счетчи 59 и на выходах дешифратора 62 снова

код счетчика б т,е„ номер очереди комгчутации данного канала, И /ц1ульс с третьего выхода дейшфратора 62 поступает на первьй вход мажоритарного элемента 63,, на второй вход которого подаются тактовые импульсы от генератора 11 Мажоритарный элемент 63 открьшается при созпадении двух сигналов на любых из его трех входов. Сигнал с вьвсода малсоритарног элемента 63 подается по цепи обратной связи на его третий вход, что обеспечивает полное прохождение импульсного сигнала через этот элемент Выходной сигнал элемента 63 обнуляет триггер 57 и устанавливает в единичное состояние триггер 58. Триггер 57 отключает распределитель (счетчик 59 и депшфратор 62), триггер 58 подготавливает к открытию элемент 60, По окончании записи кода первого в очереди канала оператор записывает код следующего канала.После нажатия

дачи сигнала Ввод по входу 26 в блоке 1 управления снова включается распределитель. При этом сигнал с , первого выхода дешифратора 62 открывает элемент И 60.с выхода которого и myльc подается на счетный вход счетчикд 6 и увеличивает его состояние на единицу с Код очередной нажатой клавиши записывается в блок 7 памяти по следующему адресу, а в блок 12 памяти, записывается код со счетчика 6 по адресу,, заданному кодом очередной клавиши. Таким образом, после очередного нажатия одной из клавиш в ;блоке 7 памяти формируется очередь из кодов коммутируемых каналов, а в бло-.

ке 12 памяти будут очередей каналов.

записаны номера

Режим коммутации задается сигналом Чтение,, подаваемым на вход 29, триггер 14 устанавливается в единичное состояние л подает высокий потен- циал на управляющие входы режимов блоков 7 и 12 памяти, что соответствует режиму чтения, и снимает сигнал разрешения с входов элементов И 4 и 61, тем самьп-4 блок 10 ввода отключается от входов блоков 7 и 12 П:амяти, При срабатывании триггера 14 на выходе формирователя 21 формируется импульс5 который устанавливает в нулевое состояние счетчик 6, триггер

58 в блоке 1 управления и через элемент /иШ 3 - в единичное состояние триггер 57 в блоке 1 управления. В блоке 1 аналогично включается счетчик 59 и на выходах дешифратора 62 снова

Форг.1ируются управляющие импульсы. Импульс с второго выхода дешифратора 62 подается только на второй вход 38 управления блока 7 памятиj происходит чтение по нулевому адресу, заданному

счетчиком 6. Считанный код канала, коммутируемого первым, записывается в регистр 8 и затем декодируется дешифратором 9, Выходы дешифратора 9 подклюг:;ены к входам 13 анализа

и к выходам 40 коммутатора. Поэтому сигкаг; с возбужденного вькода дешифратора 9 подается в цепь соответствующего канала, но к исполнению не принимается до тех пор, пока не будет

выдан сигнал исправности с выхода триггера 15. Паралллельно триггер 14 через элемент И 17 подключает генератор 11 импульсов к счетному входу счетчика 2, который начинает последо вательно заполняться. Коды с выходов счетчика 2 через дешифратор 54 и элементы И 48 блока 13 анализа последовательно опрашивают выходы дешифратора 9, При наличии сигнала на одном из выходов дeDJифpaтopa 9 соответствующий элемент И 48 открывается и сигнал с его выхода через элемент ИЛИ 53 устанавливает в единичное состояние триггер 16, который останав- Ю выходах, в блоке 13 также отсутст- ливает счетчик 2, состояние которого представляет собой код коммутируемого канала. Этот код через блок 3 элементов ИЛИ подается на адресные входы блока 12 памяти. После срабатывания триггера 16 на выходе формирователя 22 появляется импульс, задержанный элементом 24 на время установки адреса на адресньпс входах блока 7 памяти. Этот И1 тульс через элемент ИЛИ 20 20 подается на второй вход 43 управления блока 12 памяти. Считанный код очереди данного канала подается па входы блока сравнения 25, который сравнивуют сигналы на выходах элементов ИЛИ 49 и, соответственно, на выходе инвертора 51, триггер 16 остается в нулевом состоянии и устройство

5 формнруе т сигнал ошибки на вьпход 46 В случае неисправности дешифратора 9j, например наличии сигналов одновременно на двух и более его выхода в блоке 13 анализа на выходах соот ветствующих элементов И 47 формируются сигналы, которые через элемент ИЛИ 52 закрывают инвертор 51. Аналогично триггер 16 остается в нулевом состоянии, и устройство формиру

ет сигнал ошибки.

вает его с кодом, записанным в счетчике 6. При исправной работе устройства элемент И 19 подготовлен к открыванию сигналом с выхода инвертора 51 блока 13 анализа, коды на вход ах блока 25 сравнения совпадают и сиг- нап с выхода блока 25 сравнения через элемент И 19 устанавливает в единичное состояние триггер 15, Триггер 15 выдает сигнал исправности на внешнее устройство, которое принимает к исполнению сигнал с выхода дешифратора 9 и коммутирует цепь соответствующего канала. После срабатывания триггера 15 на выходе формирователя 23 формируется импульс, которьш обнуляет регистр 8, триггер 16, счетчик 2, через элемент ИЛИ 3 снова включает триггер 57 в блоке 1 управления, и описанный процесс повторяется. Таким образом, из блока 7 памяти последовательно в заданной очередности считываются коды номеров каналов, коммутируемых дешифратором 9 в соответствии с программой, а из блока 12 памяти - номера очередей этих каналов, которые сравниваются с кодами счетчика 6, также соответствующими: этим номерам.

В случае неисправности, связанной с неправильно считанными кодаг-ш из. блоков памяти или отказами в регистре 8, дешифраторе 9, коды на входах блока 25 сравнения не совпадают, триггер 15 остается в нулевом состоянии. Сигнал с инверсного выхода триггера 15 подготавливает к открыванию элемент И 18, После заполнения счетчика 2 на выходе его старшего разряда формируется сигнал, который сч;- тывает через элемент И 18 сигнал ошибки во внешнюю цепь. В случае неисправности дешнфратора 9, например отсутствия сигналов на его

Ю выходах, в блоке 13 также отсутст- 20

вуют сигналы на выходах элементов ИЛИ 49 и, соответственно, на выходе инвертора 51, триггер 16 остается в нулевом состоянии и устройство

5 формнруе т сигнал ошибки на вьпход 46. В случае неисправности дешифратора 9j, например наличии сигналов одновременно на двух и более его выходах в блоке 13 анализа на выходах соответствующих элементов И 47 формируются сигналы, которые через элемент ИЛИ 52 закрывают инвертор 51. Аналогично триггер 16 остается в нулевом состоянии, и устройство формиру-

ет сигнал ошибки.

Расширение функциональных возможностей программного коммутатора заключается в автоматическом контроле очередности коммутации каналов, обна30 ружении ошибки в кодах каналов, выявлений ошибки одновременной коммутации двух и более каналов, что исключает с высокой вероятностью возможность вьщачи сигналов коммутации при

35 неисправности устройства, повышает достоверность его работы, исключает аварийные ситуации.

40

Формула изобретения

1, Программируемый коммутатор, содержащий блок управления, первый счетчик, первый элемент ИЛИ, первый элемент И, блок элементов ИЛИ, вто45 рой счетчик, выходы которого соединены с адресными входами первого блока памяти, выходы которого соединены с входами регистра, выходы которого соединены с входами первого

50 дешифратора, отличающийся тем, что, с целью повышения достоверности комм тации, в него введены блок ввода, генератор импульсов, второй блок памяти, блок анализа, пер55 Bboi, второй, третий триггеры, второй, третий, четвертый элементы И, второй элемент ИЛИ, первый, второй, третий, фopмIipoвaтeли импульсов, элемент задержки, блок сравнения, причем выходы

9128

блока ввода соединены с информационными входами первого блока памяти и первыми входами блока элементов ИЛИ, выходы которого соединены с адресными входами второго блока памяти, пер- вый вход коммутатора соединен с первым входом первого элемента ИЛИ, выход которого соединен с первым входом блока управления, второй и третий

входы коммутатора соединены соответ- fO дом коммутатора и соединен с входом

ственно с R-входом и S-вкодом первого триггера, инверсный выход которого соединен с вторым входом блока управления и первым входом первого элемента И, прямой вькод первого триггера соединен с первыми управляющими входами первого и второго блоков памяти, с первым входом второго элемента И и входом Первого формирователя импульсов, выход которого соединен 20 с вторым входом первого элемента ИЛИ, третьим входом блока управления и R-входом первого счетчика, выходы которого соединены с информационньми

третьего формирователя импульсов, инверсный выход второго триггера соединен с вторым входом третьего элемента И, выход которого является 15 третьим выходом устройства, выход

третьего формирователя импульсов сое динен с R-входами регистра, третьего триггера,второго счетчика и третьим входом первого элемента ИЛИ.

2. Программируемьй коммутатор по п. 1, отличающийся тем, что блок анализа содержит первую и вторую группы элементов И, группу элементов ИЛИ, первый и второй инвер

входами второго блока.памяти и пер- 25 торы, первый и второй элементы ИЛИ, выми входами блока сравнения, выход дешифратор, причем первый информа- генератора импульсов соединен с вторым входом второго элемента И и четвертым входом блока управления, первый

цйонный вход блока соединен с вторым входом первого элемента ИЛИ группы элементов ИЛИ, вторым входом элеменвыход которого соединен с входом бло- 30 та И из первой группы элементов И и |Ка ввода, второй выход - с R-входом второго триггера, третий выход - с вторым управляющим входом первого блока памяти и вторым входом первого элемента И, четвертый выход - со счетным входом первого счетчика, выход второго элемента И соединен со счетным входом второго счетчика, выходы младших разрядов которого соединены с управляющими входами блока анализа и вторыми входами блока элементов ИЛИ, выход старшего разряда второго счетчика соединен с первым входом третьего элемента И, выходы дешифратора соединены с первыми выходами коммутатора и соединены с информационными входами блока анализа, первый выход которого соединен с S-входом третьего триггера, инверсный выход которого соединен с управляющим входом второго счетчика, прямой выход третьего триггера соединен через последовательно включенные второй формирователь импульсов и

первым входом элемента И из второй группы элементов И, второй и последующие информационные входы блока соединены с первыми входами соответзг ствующих элементов ИЛИ из группы элементов ИЛИ и элементов И первой и второй групп элементов И, выход каждого предыдущего элемента ИЛИ из группы элементов ИЛИ соединен с вто40 рыми входами последующего элемента ИЛИ группы элементов ИЛИ и элемента И из первсж группы элементов И, выходы элементов И первой группы элементов И и выход последнего элемента ИЛИ

45 из группы элементов ИЛИ через первый инвертор соединены с соответствующи- ми входами первого элемента ИЛИ, выход которого через второй инвертор соединен с вторым выходом блока, уп50 равляющие входы блока соединены с входами дешифратора, выходы которого соединены с вторыми входами элемент И из второй группы элементов И, выходы которых соединены с входами вто

элемент з.адержки с первым входом вто- рого элемента ИЛИ. выход которого рого элемента ИЛИ, второй вход кото- соединен с первым выходом блока, рого соединен, с выходом первого эле- 3. Программируемый коммутатор по Ыента И, соединен

выход второго элемента ИЛИ с вторым управляющим входом

п. 1, отличающийся тем, что блок ввода содержит последовател

7

10

второго блока памяти, выхоДы которого соединены с вторыми входами блока сравнения, выход которого соединен с первым входом четвертого элемента И, второй вход которого соединен с вторым выходом блока анализа, выход четвертого элемента И соединен с S-входом второго триггера, прямой выход которого соединен с вторым выхо

третьего формирователя импульсов, инверсный выход второго триггера соединен с вторым входом третьего элемента И, выход которого является . третьим выходом устройства, выход

третьего формирователя импульсов соединен с R-входами регистра, третьего триггера,второго счетчика и третьим входом первого элемента ИЛИ.

2. Программируемьй коммутатор по п. 1, отличающийся тем, что блок анализа содержит первую и вторую группы элементов И, группу элементов ИЛИ, первый и второй инверторы, первый и второй элементы ИЛИ, дешифратор, причем первый информа-

цйонный вход блока соединен с вторым входом первого элемента ИЛИ группы элементов ИЛИ, вторым входом элемента И из первой группы элементов И и

первым входом элемента И из второй группы элементов И, второй и последующие информационные входы блока соединены с первыми входами соответствующих элементов ИЛИ из группы элементов ИЛИ и элементов И первой и второй групп элементов И, выход каждого предыдущего элемента ИЛИ из группы элементов ИЛИ соединен с вторыми входами последующего элемента ИЛИ группы элементов ИЛИ и элемента И из первсж группы элементов И, выходы элементов И первой группы элементов И и выход последнего элемента ИЛИ

из группы элементов ИЛИ через первый инвертор соединены с соответствующи- ми входами первого элемента ИЛИ, выход которого через второй инвертор соединен с вторым выходом блока, управляющие входы блока соединены с входами дешифратора, выходы которого соединены с вторыми входами элементов И из второй группы элементов И, выходы которых соединены с входами второго элемента ИЛИ. выход которого соединен с первым выходом блока, 3. Программируемый коммутатор по

п. 1, отличающийся тем, что блок ввода содержит последовательно включенные коммутационные элементы, шифратор и коммутатор, выходы которого являются выходами блока, а управляющий вход коммутатора соединен с входом блока.

4. Программируемый коммутатор по п. 1, отличающийся тем, что блок управления содержит первый и второй триггеры, счетчик, первый и

второй элементы И, дешифратор, мажори- 0 рого соединены соответственно с втотарный элемент, первый вход блока соединен с S-входом первого триггера, R-вход которого соединен с S-входом второго триггера,выходом и третьим входом мажоритарного элемента, второй f5 вход которого соединен с четвертым входом блока и со счетным С-входом счетчика, управляющий V-вход которого

соединен с прямьм выходом первого триггера и с первым входом второго элемента И, второй вход которого соединен с вторым входом блока, а выход - с первым выходом блока, инверсный выход первого триггера соединен с R-входом счетчика, выходы которого соединены с входами дешифратора, первый, второй и третий выходы которым и третьим выходами блока и с первым входом мажоритарного элемента, выход второго триггера соединен с первым входом первого элемента И, второй вход которого соединен с первым выходом дешифратора, а выход первого элемента И соединен с четвертым выходом блока.

Фиг.2

HI itlZ

Ш

Редактор М.Циткина

Составитель A.Чеховский

Техред И.Попович Корректор М.Демчик

7728/58

Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля срабатывания клавиш наборного поля | 1986 |

|

SU1432524A1 |

| Устройство для контроля клавиатуры | 1980 |

|

SU881755A1 |

| Устройство для управления вызовом информации | 1987 |

|

SU1439670A2 |

| Устройство для решения задачи синхронизации работы объектов в сети связи | 1989 |

|

SU1777150A1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ КОЛЕБАНИЙ | 1991 |

|

RU2018911C1 |

| Селектор импульсов по длительности | 1990 |

|

SU1758866A2 |

| Устройство для оценки профессиональной пригодности оператора | 1989 |

|

SU1714646A1 |

| Устройство для управления процессом передачи сигналов управления в иерархической автоматизированной системе управления | 1988 |

|

SU1525679A2 |

| Устройство для программного управления | 1986 |

|

SU1335933A1 |

| Устройство для контроля параметров | 1985 |

|

SU1291930A1 |

Изобретение относится к автоматике и вычислительной технике. Может быть использовано в устройствах для программного управления и коммутации каналов с заданной очередностью. Цель изобретения - повьЕшение достоверности работы устройства за счет контроля на каждом шаге коммутации 3 W ч ч

| Коммутатор | 1981 |

|

SU1018244A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Программируемый коммутатор | 1982 |

|

SU1075410A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-01-30—Публикация

1985-08-29—Подача