управления записью в регястг; -1, четвертый выход которого сое,т,кнеы с четвертым входом блока управ;7екия памятью, 1 1ес:той выкод которого соединен с вторым входом запо ллншощего устройства, входная шина Kci-чальная установка сое,11.инена с: пятым входом 6jJOKa управления ;г;5;- мятью, шестой вход которого подключей к шине Скккроаизацкя уст-ройства, входная шина Повторить которого соединена с оедьмым входом блока управления память 0; восьмой вход которогО подключая к Пуск устройогва, ишна Сбро программы KOTOpoio соединена о дBHTHff/i входом блокг управления памятью, десятый вход, которого ооедкиен с шиной устройства Сброс команды, причем пяХый ВЕ.-;ход блока управления записью в регистры подключен к входу регистра ком-дутации выходных каналов, а шестой вы-ход соединен с первыми входами дешифратора KOMiv-гутации входных канал и дешифратора коммутации выходных каналов, группа выходов статического регистра соединена с первыми входами соответствующих элементов первой группы элементов И и вторыг ш входами второй группы элементов И, первый выход регистра коммута ции входных каналов соединен с вторым входом элемента И-НЕ, второй выход - с вторьвчи входами первой группы элементов И, выходы cc-i.oрых соединены с третьими входами группы канальных злементов.. третий выход регистра коммутации входных /налов подклгсЧен к вторым входг м группы элементов МЛИ, выход рггистра коммутации выходных каналов соединен с первым входом элемента И. выход которого соединен с вторым входом элемента ИЛИ, седвкгж. восьмой, девятый и десятый выходк блок управления памятью соединеньз с вторым и третьим выгодами блока управления записью в регистры, с третьим входом счетчика времени коммутации и с входом элемента И соответственно,

2. Коммутатор по п, 1, о т л ичающийся тем, что блок управления памятью содержит три триггера, девять элементов ИЛИ, десять элементов И, пять элементов задержки и один элемент НЕ, причем первый вход блока соедиь:ен с первым входом первого элемента ИЛИ выход которого подключен к десятому выходу устройства, к первым входам первого и второго элементов И и к первому входу второго элемента ИЛИ, выход которого является пятым выходом блока, второй вход которого соединен с nepBbUvi вхо.дом третЙего элемента И, выход .которог -о соеД1нек L: jepBMM вг;:г;.щ-)Ь; ;;:)гтьего элемента H/IH, выхо.1. коЕ-орого яь.пяется вторы / выхо;:.ог.. 5;:ока и подключен к первым четвертого элзманта Н н четвертого .з,те1-/:ен1 а Или, BKXoi:i. ;:оторого язляе с-п третьП ; выходом б.аока и под1слю-1ен , зторому вхо.цу второго элемента ИЛИ и первому вкоду г.ято:1о элемента МЛК, аыхо.у Koioporo сое/идеч с первым входом первого трипера.,. В1.;ход которого является шестью/ выхо.дом блока и по.дключен к входу первого элемектс. эа..цержки, и с первыми входами Г1ЯТОГО и шестого элементов И, выход которого является седь.:-.;ыг.- выходом блока и подключен к входу седьмого элемента И, выход :сторого соединен с вторым входом тг-:vj i:T -o элемента ИЛИ, а группа .: с группой входов блска, :;.,---;.: вход которого соединен с BTOph vi ;4.xo,i;iOM третьего элемента И л ., входрм восьмого элемента И, выкод ;;отс;рого соединен с вторьтми входами чет1зертого и первого элементов ИЛИ, третий вход которого соед1-1ке:-: с выходом четвертого элемента И, второй вход которого соединен с сед.1ьмь-:м входом блока ,четвертыми вход которого соединен с первым входом шестого элемента ИЛИ, выход которого подключен к первому входу второго т.риггер выход которого соединен с первьм вхо.дом девятого элемента И, выход которого сое.цинен с первым входом седьмого эле;лента ИЛИ, выход которого соединен с входом второго э./зе1- ектЕ задержки и первым вхс::-.ом восьмого) элемента ИЛИ. выход которого подключен к второму входу первсэго триггера, пятый вход блока соединен с третьим входом четвертого элимзнта ИЛИ и первым входом девялого й.помента ИЛИ, выход которогс; с-;еди1-;е:Н с первым входом третьегс триггера, выход которого соединен с вторым входом восьмого элементе. И и с входом третьего элемента задерл(ки, выход, которого подключен к вто-рому входу девятого элемента ИЛИ, шестой вхо.в. блока соединен с вторым входом восьмого элементе, ИЛИ, восьмой вход блока соединен с вторым входом третьего триггера, девятый вход блока соединен с входом ин вертора и с вторым входом первого элемента И, выход которого соединен с четвертьм входом четвертого элемента ИЛИ и первыг выходом блока, десятый вход которого подключен к четвертому входу первого элемента ИЛИ, четвертый выход блока соединен с выходом первого элемента задержки, с вторым входом пятого эл мента И и входом четвертого элемента задержки, выход которого соединен свторым входом девятого элемента И, восьмой выход блока соединен с выходом десятого элемента И, девятый выход блока соединен с вторым входом седьмого элемента ИЛИ, вторым входом второго триггера и выходом пятого элемента задержки, вход которого соединен с выходом второго элемента И, второй вход которого соединен с выходом первогэлемента НЕ, причем выход второго элемента задержки соединен с вторым входом шестого элемента И, второй вход шестого элемента ИЛИ подключен к выходу четвертого элемента ИЛИ, первый вход десятого элемента И соединен с выходом первого элемента задержки, а второй вход с третьим входом блока, выход пятого элемента И соединен с вторым входом пятого элемента ИЛИ.

ч

3. Коммутатор по п. 1, о т л ичающийся тем, что блок управления записью в регистры содержит регистр, триггер, генератор и четыре элемента И, причем генератор по выходу соединен с первым входом первого элемента И, выход которого соединен с вторым выходом блока, третий вход которого соединен с первым входом регистра, первый выход которого соединен с первым входом второго элемента И, выход которого соединен с пятым выходом блока, первый вход которого соединен с вторым входом регистра и первым входом первого триггера, выход которого соединен с вторым входом первого элемента И и шестым выходом блока, второй вход которого соединен с вторым входом второго элемента И и с первыми входами третего и четвертого элементов И, выход которого соединен с первым выходом блока, а второй вход - с вторым выходом регистра, третий- выход которого соединен с вторым входом третьего элемента И, выход которого соединен с третьим выходом блока, четвертый выход которого-соединен с четвертым выходом регистра и вторым входом первого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Устройство для сопряжения | 1983 |

|

SU1124277A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1983 |

|

SU1140125A1 |

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1108460A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

1

Изобретение относится к автоматике и коммутационной технике.

Известен коммутатор, содержащий статический регистр, информационные входы которого соединены с информационными входными шинами, вход установки - с шиной сброса, вход записи - с шиной записи, а каждый из единичных выходов подключен к первому входу одноименного канального элемента, выход которого соединен с соответствующей выходной шиной 1.

Наиболее близким к изобретению по технической сущности является коммутатор, содержащий статический регистр, информационные входы которого соединены с информационными входами устройства, вход записи с шиной записи, группу канальных элементов, каждый из входов которой соединен с соответствующей выходной информационной шиной устройства Г2,

Недостатком таких устройств являются узкие функциональные возможности.

Целью изобретения является расширение функциональных возможностей коммутатора.

Указанная цель достигается тем, что в программируемый коммутатор, содержащий статический регистр.

информационные входы которого соединены с информационными входами устройства, вход записи - с шиной записи, группу канальных элементов,каждый из выходов которой соединен с соответствующей выходной информационной шиной устройства, введены счетчик адреса, запоминающее устройство, блок управления памятью,

Q три регистра, счетчик, два дешифратора, блок управления записью в регистры, две группы элементов И, группа элементов ИЛИ, один элемент И, один элемент И-НЕ, один элемент ИЛИ

с и один элемент ИЛИ-НЕ, причем выход элемента ИЛИ-НЕ подключен к первому входу элемента И-НЕ, выход которого подключен к первым входам группы канальных элементов, вторые входы каждого из которых подключены к

0 соответствующему выходу накопительного регистра, группа входов которого соединена с группой выхо- дов дешифратора коммутации выходных каналов, группа входов которого сое5 динена с группой выходов запоминающего устройства, с группой входов блока управления памятью, с группой входов регистра коммутации входных каналов и с группой входов счетчика

0 времени коммутации, выход которого соединен с первым входом блока управления памятью, первый выход которого соединен с шиной устройства Ожидание, шина Конец программы которого подключена к второму выхо блока управления памятью, третий ход которого соединен с первым вх j,OM счетчика адреса и первым вход элемента ИЛИ, выход которого соед нен с входом накопительного регистра, первый вход счетчика времени коммутации соединен с первым выходом блока управления записью.. в регистры, второй выход которого подключен к второму входу с-четчика времени коммутации, а третий выход - к входу регистра коммутации входных каналов, группа выходов которого соединена с группой входов дешифратора коммутации входных каналов, группа выходов которого подключенная к первым входам соответствующих элементов группы элементов ИЛИ, выходы которых соеди нены с первыми входами соответствующих элементов второй группы эле ментов И, выходы которых соединены с входами элемента ИЛИ-НЕ, шина Конец загрузки устройства соединена с выходом счетчика адреса и вторым входом блока управления памятью, четвертый выход которого соединен с вторым входом счетчика адреса, группа выходов которого соединена с первой группой входов запоминающего устройства, вторая группа входов которого соединена с второй группой информационных входов устройства, входная шина Загрузка которого соединена с первы входом запоминающего устройства и третьим входом блока управления памятью, пятый выход которого соединен с первым входом блока управления записью в регистры, четвертый выход которого соединен с четвертым входом блока управления памятью, шестой выход которого сое динен с вторым входом запоминающего устройства, входная шина Начальная установка соединена с пятым входом блока управления памя шестой вход которого подключен к шине Синхронизация устройства, входная шина Повторить которого соединена с седьмым входом блока управления памятью, восьмой вход которого подключен к шине Пуск устройства, шина Сброс программы которого соединена с девятым входом блока управления памятью, деся тый вход которого соединен с шиной устройства Сброс команды, причем пятый выход блока управления записью в регистры подключен к входу регистра коммутации выходных каналов, а шестой выход соединен с первыми входами дешифратора коммут ции входных каналов и дешифратора коммутации выходных каналов, группа выходов статического регистра соединена с первыми входами соответствующих элементов первой группы элементов И и вторыми входами второй группы элементов И, первый выход регистра коммутации входных каналов соединен с вторым входом элемента И-НЕ, второй выход - с вторыми входами первой группы элементов И, выходы которых соединены с третьими входами группы канальных элементов, третий выход регистра коммутации входных каналов подключены к вторым входам соответствующих элементов группы элементов ИЛИ, выход регистра коммутации выходных каналов соединен с первым входом элемента И, выход которого соединен с вторым входом элемента ИЛИ, седьмой, восьмой, девятый и десятый выходы блока управления памятью соединены с вторым и третьим входами блока управления записью в регистры, с третьим входом cieTчика времени коммутации и с вторым входом элемента Исоответственно. Кроме того, блок управления памятью содержит три триггера, девять элементов ИЛИ,десять элементов И,пять элементов задержки и один элемент НЕ, причем первый вход блока соединен с первым входом первого элемента ИЛИ, выход которого подключен к десятому выходу устройства, к первым входам первого и второго элементов И и к первому входу второго элемента ИЛИ, выход которого является пятым выходом блока, второй вход которого соединен с первым входом третьего элемента И, выход которого соединен с первым.входом третьего элемента ИЛИ, выход которого является вторым выходом блока и подключен к первым входам четвертого элемента И и четвертого элемента ИЛИ, выход которого является третьим выходом блока и подключен к второму входу второго элемента ИЛИ и первому входу пятого элемента ИЛИ, выход которого соединен с первым входом первого триггера, выход которого является шестым выходом блока и под|Ключен к входу первого элемента задержки и к первым входам пятого и шестого элементов И, выход которого является седьмым выходом блока и подключен ко входу седьмого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, а группа входов - с группой входов блока, третий вход которого соединен с вторым входом третьего элемента И и первым входом восьмого элемента И, выход которого соединен с вторыми входами четвертого и первого элементов ИЛИ, третий вход

которого соединен с выходом четвертого элемента И, второй вход которо го соединен с седьмым входом блока, четвертый вход которого соединен с первым входом шестого элемента ИЛИ, выход которого подклюнен к первому входу второго триггера, выход которого соединен с первым входом девятого элемента И, выход которого соединен с первым входом седьмого элемента ИЛИ, выход которого соединен с входом второго элемента задержки и первым входом восьмого элемента ИЛИ, выход которого подключен к второму входу первого триггера, пятый вход блока соединен с третьим входом четвертого элемента ИЛИ и первым входом девятого элемента ИЛИ, выход которого соединен с первым входом третьего триггера, выход которого соединен с вторым входом восьмого элемента И и с входом третьего элемента задержки , выход которого подключен к второму входу девятого элемента ИЛИ шестой вход блока соединен с вторым входом восьмого элемента ИЛИ, восьмой вход блока соединен с вторым входом третьего триггера, девятый вход блока соединен, с входом ин-вертора и с вторым входом первого элемента И, выход которого соединен с четвертым входом четвертого элемента ИЛИ и первым выходом блока, десятый вход которого подключен к четвертому входу первого элемента ИЛИ, четвертый выход блока соединен с выходом первого элемента задержки, с вторым входом пятого элемента И и входом четвертого элемента задержки, выход которог соединен с вторым входом девятого элемента И, восьмой выход блока соединен с выходом десятого элемента И, девятый выход блока соединен с вторым входом седьмого элемента ИЛИ, с вторым входом второго триггера и выходом пятого элемента задержки, вход которого соединен с выходом второго элемента И, второй вход которого соединен с выходом первого элемента НЕ, причем вЫход второго элемента задержки соединен с вторым входом шестого элемента И, второй вход шестого элемента ИЛИ подключен к выходу четвертого элемента ИЛИ, первый вход десятого элемента И соединен с выходом nej вого элемента задержки, а второй вход - с третьим входом блока, выход пятого элемента И соединен с вторым входом пятого элемента ИЛИ.

При этом блок управления записью в регистры содержит регистр, триггер генератор и четыре элемента И; причем генератор по выходу соединен с . первым входом первого элемента И,

выход которого соединен с вторым выходом блока,третий вход которого соединен с первым входом регистра, первый выход которого соединен с первым входом второго элемента И, выход которого соединен с пятым выходом блока, первый вход которого- соединен с вторым входом регистр и первым входом первого триггера, выход которого соединен с вторым входом первого элемента И и шестым выходом блока, второй вход которого соединен с вторым входом второго элемента И и с первыми входами третьего и четвертого элементов И, выход которого соединен с первым выходом блока, а второй вход - с вторым выходом регистра, третий выход которого соединен с вторым входом третьего элемента И, выход которого соединен с третьим выходом блока, четвертый выход которого соединен с четвертым выходом регистра и вторым входом первого триггера.

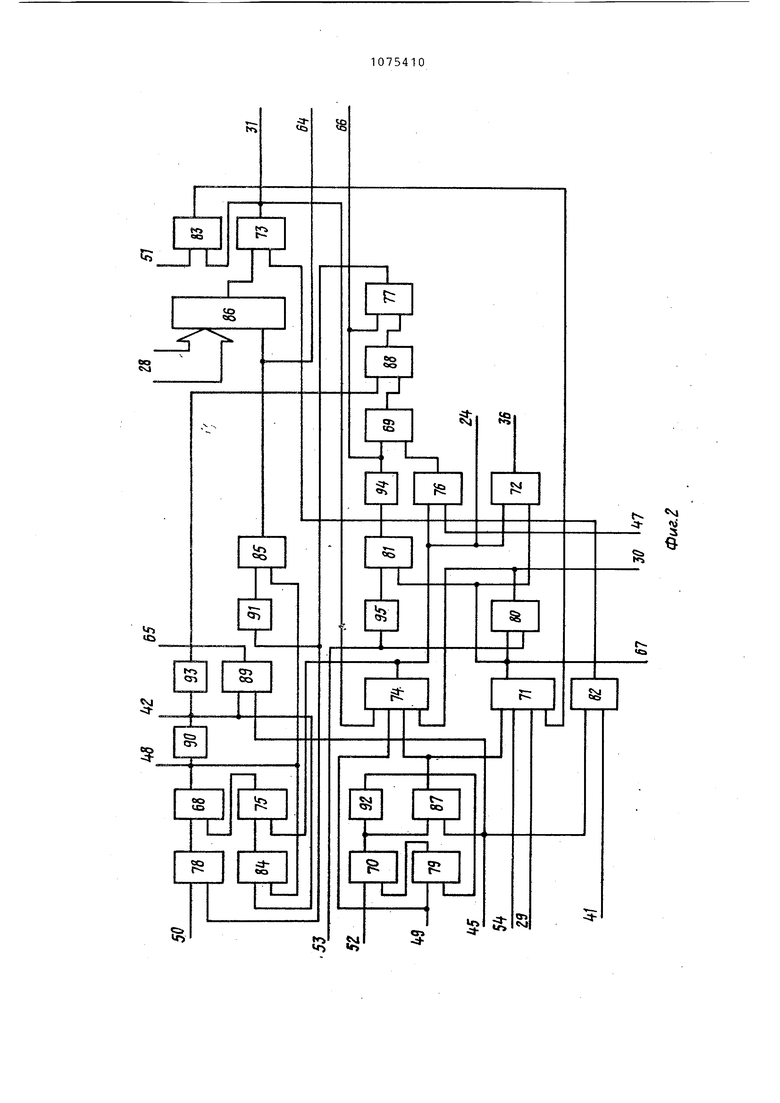

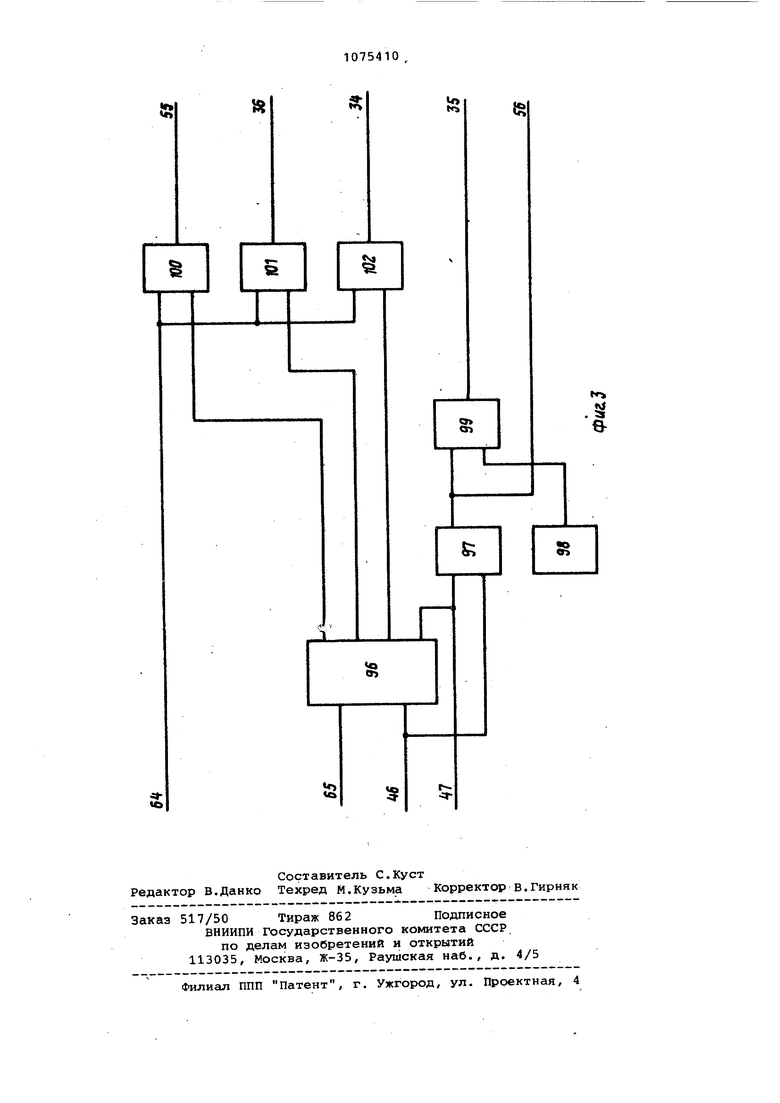

На фиг. 1 представлена функциональная схема программируемого коммутатора; на фиг. 2 - функциональная схема блока управления памятью на фиг. 3 - функциональная схема блка управления записью в регистры.

Программируемый коммутатор содержит статический регистр 1, инфор мационные входы 2 (входные каналы) которого соединены с информационным входами устройства, вход 3 записи с шиной записи устройства, группу 4 канальных элементов, каждый из выходов 5 (выходных каналов) которой соединен с соответствующей выходной информационной шиной устройства счетчик б адреса, запоминающее устройство 7, блок 8 управления памят регистр 9 коммутации выходных каналов, регистр 10 коммутации входных каналов, накопительный регистр 11, счетчик 12, дешифратор 13 коммутации выходных каналов, дешифратор

14коммутации входных каналов, блок

15управления записью в регистры, первую группу 16 элементов И, вторую группу 17 элементов И, группу

18 элементов КЛИ, один элемент И 19 один элемент И-НЕ 20,один элейент ИЛ 21 и один элемент ИЛИ-НЕ 22,. причем ылход 23 элемента ИЛИ-НЕ 22 . подключен к первому входу элемента И-нк 20, выход 24 которого подключен к первым входам группы 4 канальных элементов, вторые входы каждого из которых подключены к соответствующему выходу 25 накопительного регистра 11, группа входов которого соединена с группой выходов 26 дешифратора 13 коммутации выходных каналов, группа входов которого соединена с группой выходов 27 регистр 9 коммутации выходных каналов, группа входов которого соединена с группой выходов 28 запоминающего ( устройства 7, с группой входов бло ка 8 управления памятью, с группо входов регистра 10 коммутации вход ных каналов и с группой входов сч чика 12, выход 29 которого соедине с первым входом блока 8 управлени памятью, первый выход 30 которого соединен с шиной устройства Ожидание, шина 31 Конец программы которого подключена к второму вход блока 8 управления памятью, третий выход 32 которого соединен с первы входом счетчика б адреса и первым входом элемента ИЛИ 21, выход 33 которого соединен с входом накопительного регистра 11, первый вход счетчика 12 времени коммутации соединен с первым выходом 34 блока 15 управления записью в регистры, второй выход 35 которого подключен к второму входу счетчика 12 времени коммутации, а третий выход 36 - к входу регистра 10 коммутации входных каналов, группа выходов 37 которого соединена с группой входов дешифратора 14 коммутации входных каналов, группа выходов 38 которого подключена к первым входам соответствующих элементов группы элементов ИЛИ 18, выходы 39 которых соединены.с первыми входами соответствующих элементов второй группы элементов И 17, выходы 40 которых соединены с входами элемента ИЛИ-НЕ-22, шина 41 Конец загрузки устройства соединен с вы ходом счетчика б адреса и вторым входом блока 8 управления па1 1ятью четвертый выход 42 которого соединен с вторым входом счетчика б адреса, группа выходов 43 которого соединена с первой группой вхо дов запоминающего устройства 7, вторая группа входов 44 которого соединена с второй группой информационных входов устройства, входная шина 45 Загрузка которого соединена с первы л входом зап минающего устройства 7 и третьим входом блока 8 управления памятью пятый выход 46 которого соединен с первым входом блока 15 управления записью в регистры, четвертый выход 47 которого соединен с чет- вертым входом блока 8 управления памятью, шестой выход 48 которого соединен с вторым входом запоминающего устройства 7, входная шина 49 Начальная установка соединена с пятым входом блока 8 управления памятью, шестой вход которого подключен к шине 50 Синхронизация устройства, входная иш на 51 Повторить которого соединеыа с седьмым вхо,цом блока В уг;.равления памятью, восьмой вход коюрого подключен к шине 52 Пуск устройства, шина 53 Сброс программы которого сое/динена с девятым входом блока 8 управления памятью, десятый вход которого соединен с шиной 54 устройства Сброс ко анды, причем пятый выход 55 блоке управления записью в регистры 1Ь подключен к входу регистра 9 ком-мутации выходных каналов, а иестой выход 56 соединен с первыми входами дешифратора 14 KONLMyxauKK входных каналов и дешифратора 13 коммутации выходных каналов, группа выходов 57 статического регистра 1 соединена с перВЕ ми входами соответствующих элементов первой группы элементов И 16 и вторыми вхсгам второй группы элементов И 17, парвый выход 58 регистра 10 иомк-утации входных каналов соединен с .зторымвходом элемента И-НЕ 20, второй выход 59 - с вторыми входами первой . . группы элементов И 16, выходы 60 которых соединены с третьими входами группы 4 канальных элементов, третий выход 61 регистра 10 комд;1утацик входных каналов подключен к вторым входам группы элементов ИЛИ 18, выход 62 регистра 9 ко1 мутации выходных каналов соединен с первым входом элемента И 19, выход 63 которого соединен с вторым входом элемента ИЛИ 21, седьмой 64, восьмой 65, девятый 66 и десятый 67 выходы блока 8 управления памятью соединены с вторым и третьим входами блока 15 управления записью в регистры, с третьим Е.;.ОДОМ счетчика 12 времени коммутации ::; с BTOpbHvj входом элемента И 19 соответственно. Блок 8 управления паглятью содержит первый 68,второй 69 и третв - 70 триггеры, первый 71, второй 72, третий 73, четвертый 74, пятый 75, шестой 76f седьмой 77, восьмой 78 и девятый 79 элементы . И, первый 80, второй 81, третий 82, четвертый 83, пятый 84, шестой 85, седьмой 86,восьмой 87, девятый 88 и десятый 89 элементы И, первый 90, второй 91, третий 92, четвертый 93 и пятый 94 элементы задержки и элемент ИЕ 95, Блок 15 управления записью в регистры содержит регистр 96, триггер 97, генератор 98, первый 99, второй 100, третий 101 и четвертый 102 элементы И. Программируемый коммутатор работает следующим образом. В исходном состоянии по импульсу на входной шине 49 Начальная установка через элемент ИЛИ 79 установится в нулевое состояние триггер 70, через элементы ИЛИ 74 и 75 приггер 68, через элементы ИЛИ 76 74 - триггер 69 блока 8 упранлени ii,::HiLR,. Одновременно на выходах блока 8 управления памятью появляйгся сигнал на выходе 32 облуче счегчика 6 адреса и накопительног pei.jCipa 11 и сигнал на выходе 46 установки в начальное состояние блока 15 записи в регистры. Сдвиг вый регистр 96 блока 15 записи в регистры по сигналу на выходе 4 устанавливается в состояние, при котором на первом его выходе нахо длтся уровень логической единицы на остальных - уровни логического нуля. Триггер 97 устанавливается сигналом на выходе 46 в состояние логического нуля. Перед началом работы программн го коммутатора в запоминающее уст ройство 7 записывается программа работы. Программа определяет после довательность и время коммутации входных и выходных каналов. В процессе выполнения программы из запоминающеео устройства считываются управляющие слова, функциональное назначение которых следующее:1-е слово - первЕле разряды пред ставляют собой код коммутируемого выходного канала, последний разряд определяет режим накопления; 2-е слово - первые разряды пред ставляют собой код коммутируемого входного канала, предпоследний раз ряд определяет режим мультиплексирования сигналов, поступающих по входным каналам, последний разряд режим суммирования сигналов, посту пающих по входным каналам; 3-е слово определяет время ко глутации и представляет собой обратный код необходимого времени ко1 лглутации, Режим загрузки запоминающего устройства -.осуществляется при наличии уровня логического нуля на входной шине 45 загрузки. Каждое слово загружаемой программы поступает на группу входных шин 44 программируемого коммутатора, а затем на информационные входы запоминающего устройства при наличии уровня логического нуля на входной шине 45 Загрузка. Каждое слово загружаемой программы поступает на груп пу входных шин программируемого коммутатора, а затем на информационные входы запоминающего устройства 7. Слово сопровождается си хроимпульсом на входной шине 50 Синхронизация блока 8 управления памятью. Период поступления с должен быть не менее длительности цикла записи используемой памяти. Синхроимпульс поступает на вход элемента ИЛИ.78, устанавливая триггер 68 в состояние логической единицы. На единичном выходе триггера.68 формируется сигнал выбора для запоминающего устройства 7. По сигналу с выхода элемента 90 задержки, определяющего время записи информации в запоминающее устройство 7, срабатывает элемент И |84, устанавливая в состояние логического нуля триггер 68 через элемент ИЛИ 75. Сигнал с выхода 42 элемента 90 задержки увеличивает содержимое счетчика 6 адреса на единицу. Схема готова к записи информации в следующую ячейку. Запись производится по синхроимпульсам до появления на выходной шине 41 Конец загрузки сигнала переполнения со счетчика 6 адреса. После окончания загрузки программируемый коммутатор переводится в режим чтения информации сигналом уровня логической единицы на входной шине 45 Загрузка. Запуск коммутаторй, находящегося в режиме чтения, осуществляется сигналом уровня логической единицы на входной шине 52 Пуск. По этому сигналу триггер 70 устанавливается в единицу, а через время, необходимое для установки программируемого коммутатора в исходное состояние, сбрасывается сигналом с выхода элемента 92 задержки через элемент ИЛИ 79 в нуль. Сформировавшийся на выходе триггера 70 импульс запуска через элементы И 87 и ИЛИ 74 устанавливает программируемый коммутатор в исходное состояние. Сигнал с выхода элемента И 87 через элемент ИЛИ 71 И 81 и элемент 94 задержки устанавливает триггер 69 в состояние логической единицы, одновременно выдает сигнал на выходе 66 установки в нуль счетчика 12 времени коммутации и через элементы ИЛИ 77 и ИЛИ 78 устанавливает в единицу триггер 68. На единичном выходе триггера 68 формируется сигнал Выборка. По сигналу с выхода элемента ИЛИ 77, задержанному на элементе 91 задержки на время выборки информации, срабатывает элемент И 85, формируя сигнал на выходе 64 для записи информации в регистры и для анализа на элементе И 100 команды конца программы. По сигналу на выходе 64 элемента и 100 блока записи в регистры, открытого единичным уровнем с выхода первого разряда регистра 96 сдвига, формируется сигнал на выходе 55, осуществляквдий запись в регистр 9 первого-управляющего слова команды. По сигиапу с выхода элемента УО задержки, определяющего время, необходимое для выборки информации из устройства 7 и для записи в один из регистров 9 и 10 или счетчик 12 времени коммутации, срабатывает элемент И 84, устанавливая в состояние логического нуля триггер 68 через элемент ИЛИ 75, счетчик б адреса увеличивает содержимое на единицу, срабатывает элемент И 89, формируя сигнал сдвига на выходе б 5 ,

Этот сигнал осуществляет сдвиг на один разряд вправо информации, находящейся в регистре 96.

По сигналу с выхода элемента 93 задержки, определяющего время пауз между двумя обращениями, срабатывает элемент И 88. Сигнал с выхода элемента И 83 через элементы ИЛИ 7 и 78 устанавливает триггер 68 в едничное состояние, формируя сигнал на, выходе 48 Выборка и сигнал на выходе 64 Запись в регистры. По сигналу на выходе 64 срабатывает элемент И 101, на выходе которого формируется сигнал на выходе 36, осуществляющий запись второго упраляющего слова команды в регистр 10. Затем формируются сигнал на выходе 42 для счетчика б адреса и сигнал сдвига на выходе 65. Сигн

с выхода элемента 93 задержки через элементы И 88, ИЛИ 77 и 78 вновь устанавливает триггер 68 в состояние логической единицы. По сигналу с единичного выхода триггера 68 осуществляется считывание третьего управляющего слова, которое по сигналу с выхода 34 элемента И 102 записывается в счетчик 12 времени коммутации, а по сигналу сдвигана выходе 47 четвертого разряда регистра 96 сдвига появляеся единичный уровень,устанавливающий триггер 97 в единичное состояние, а через элемент ИЛИ 76 блока управления памятью триггер 69 в нуль. Нулевой уровень с выхода триггера 69 запрещает прохождение сигнала с выхода элемента 93 задержки через элемент И 88 и далее на установку триггера 6В в единичное состояние.

На единичном выходе триггера 97 формируется сигнал на выходе 56, разрешающий дешифрацию кодов, поступающих по группе входов, 27 и 37 на дешифраторы 13 и 14 соответственно, и прохождение импульсов счета с генератора 98 через элемент И 99 на счетный вход счетчика 12 времени коммутации, Период импульсов счета определяет единицу измерения времени коммутации.

Коммутация входных и выходных импульсов производится в зависимости от состояний управляющих триггеров регистра коммутации выходных каналов 9 и регистра 10 коммутации входных каналов.

Возможны следующие режимы работы

59, инверсный по отношению к сигналу на выходе 58, разрешает прохождение информации с входного регистра 1 через группу элементов И 16 на выходные канальные элементы 4J накопительный регистр 11 позволяет по мере выполнения очередной команды открывать очередной выходной канальный элемент 4, не закрывая предыдущего.

Таким образом, в данном режиме осуществляется коммутация входных каналов 2 с соответствующими выходными каналами 5 с накоплением.

и ИЛИ 21 на сброс накопительного регистра 11, следовательно, будет осществляться поочередное подключение входных каналов 2 к соответствующим выходным каналам 5 без накопления.

58равен единице, сигнал на выходе 61 равен нулю). Сигнал на выходе 58 разрешает прохождение информации

с выхода элемента ИЛИ-НЕ 22 через элемент И-НЕ 20 на выходные канальные элементы 4, Сигнал на выходе

59запрещает прохождение информации с входного регистра 1 через группу элементов И 16, Появившийся на одном из выходов 38 дешифратора 14 сигнал единичного уровня проходит через соответствующий элемент ИЛИ из группы элементов ИЛИ 18 и открывает элемент И из группы элементов И 17. Соответствующий сигнал с одного из выходов 57 входного регистра 1 проходит через выбранный элемент И из группы элементов И 17, через элемент ИЛИ-НЕ 22 и элемент И-НЕ 20 на выходные канальные элементы 4, Поскольку в данном режиме реализуется работа программируемого коммутатора с накоплением (сигнал на выходе 62 равен нулю), то выбранный на дещифраторе 14 входной канал может быть скоммутирован с любым числом выходных каналов 5.

любое число выходных каналов 5.

сигнал на выходе 61 равен нулю). Сигнал на выходе 62 разрещает прохождение сигнала с выхода 32 на сброс I накопительного регистра, сигнал

на выходе 5 В разрешает прохождение информации с выхода элемента ИЛИ-НЕ 22 через элемент И-НЕ 20 на выходные канальные элементы, сигнал на выходе 59 блокирует группу элементов И 16. Таким образом, любой входной канал 2 может быть скоммутирован с любым выходным каналом 5.

равны единице). Сигнал на выходе 61 открывает все элементы И из группы элементов И 17 через группу элементов ИЛИ 18, т.е. осуществляется подача суммы сигналов по всем входным каналом 2 на один из выходных каналов 5.

Сигнал переполнения с выхода 29 счетчика 12 времени коммутации через элементы ИЛИ 71 и 81, элемент 94 задержки устанавливает в единичное состояние триггер 69. Сигнал с выхода элемента 94 задержки обнуляет счетчик 12 времени коммутации и через элементы ИЛИ 77 и 78 осуществляет повторный заriycK программируемого коммутатора.

Далее повторяется процесс чтения трех слов очередной команды и запись их в регистры 9 и 10 и счетчик 12 времени кoм 1yтaции. Сигнал на шине 54 Сброс команды производит те же действия, что и сигнал переполнения на выходе 29 счетчика 12 времени коммутации.

При поступлении внешнего сигнала по шине 53 Сброс программы сигнал с выхода элемента ИЛИ 71 через элементы И 80 и ИЛИ 74 производит начальную установку программируемого коммутатора. Одновременн с выхода элемента И 80 выдается синал на шину 30 0жидание, определяющий окончание работы программируемого коммутатора.

При появлении сигнала переполнения на шине 41 со счетчика 6 адреса и наличии единичного уровня на шине 45 Загрузка срабатывает элемент И 82, формируя через элементы ИЛИ 73 и 74 сигнал на выходе 24 начальной установки программируемого коммутатора, с выхода элмента ИЛИ 73 выдается сигнал на шину 31 Конец программы.

При появлении на входах элемента И 86 кода команды Конец програмы и сигнала с выхода элемента И 85, сигнал с выхода элемента И 86 через элемент ИЛИ 73 производит начальную установку программируемо коммутатора и выдает сигнал на шину 31 Конец программы.

При наличии сигнала на шине 51 Повторить сигнал с выхода элемента ИЛИ 73 через элементы И 83 и ИЛИ 71 осуществляет повторный запуск программируемого коммутатора

с начала программы.

Технический эффект использования предложенного программируемого коммутатора заключается в расширении его функциональных возможносте

что позволит в процессе выполнения программы осуществить соединение произвольного числа пар вход-выход подключить любой вход к произвольному числу выходов, подать сумму сигналов по любым входам на произвольное число выходов, соединить любой вход с любым выходом, програмировать время коммутации С возможностью принудительного сброса каждого шага программы внешним сигналом, производить зацикливание программы с возможностью сброса ее

,в любом месте внешним сигналом, осществлять повторный запуск программы. Благодаря использованию запоминающего устройства, коммутатор схематически универсален и специализируется для контактного применения сменой программы в запомичакяцем устройстве, что может быть

осуществлено управляющей ЭВМ. Благодаря возможности смены и хранения программы работы повышается эффективность взаимодействия коммутатора и управляющей ЭВМ, которой достатоЧно загрузить программу в запоминающее устройство коммутатора.

Реализацию программы коммутатор осуществляет автономно. Для локальных применений программа работы может быть помещена в постоянное запоминающее устройство (ПЗУ) .В этом случае смена программы работы коммутатора осуществляется простой сменой ПЗУ.

tsi

И

is

.

§

е

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| КОММУТИРУЮЩЕЕ УСТРОЙСТВО | 0 |

|

SU375789A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Коммутатор | 1979 |

|

SU822357A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-02-23—Публикация

1982-06-23—Подача