Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых позиционных регуляторах, информационных системах, системах- управления положением механизмо в.

Цель изобретения - повьппение достоверности передаваемой информации преобразователем.

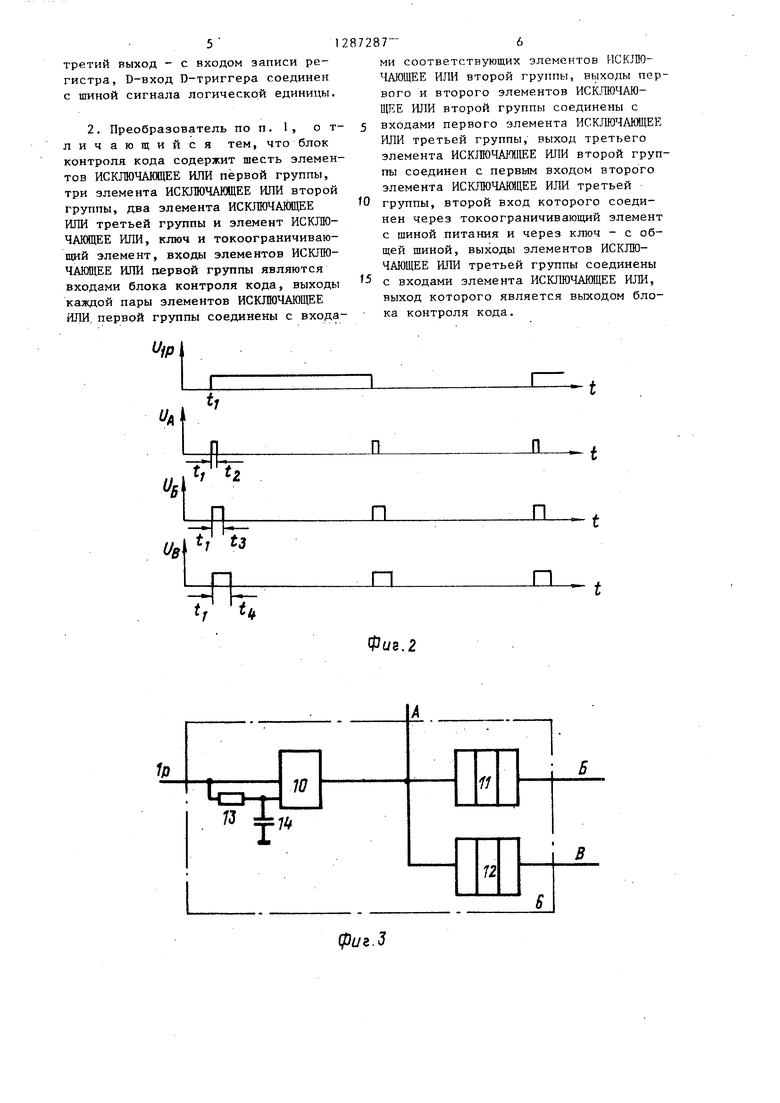

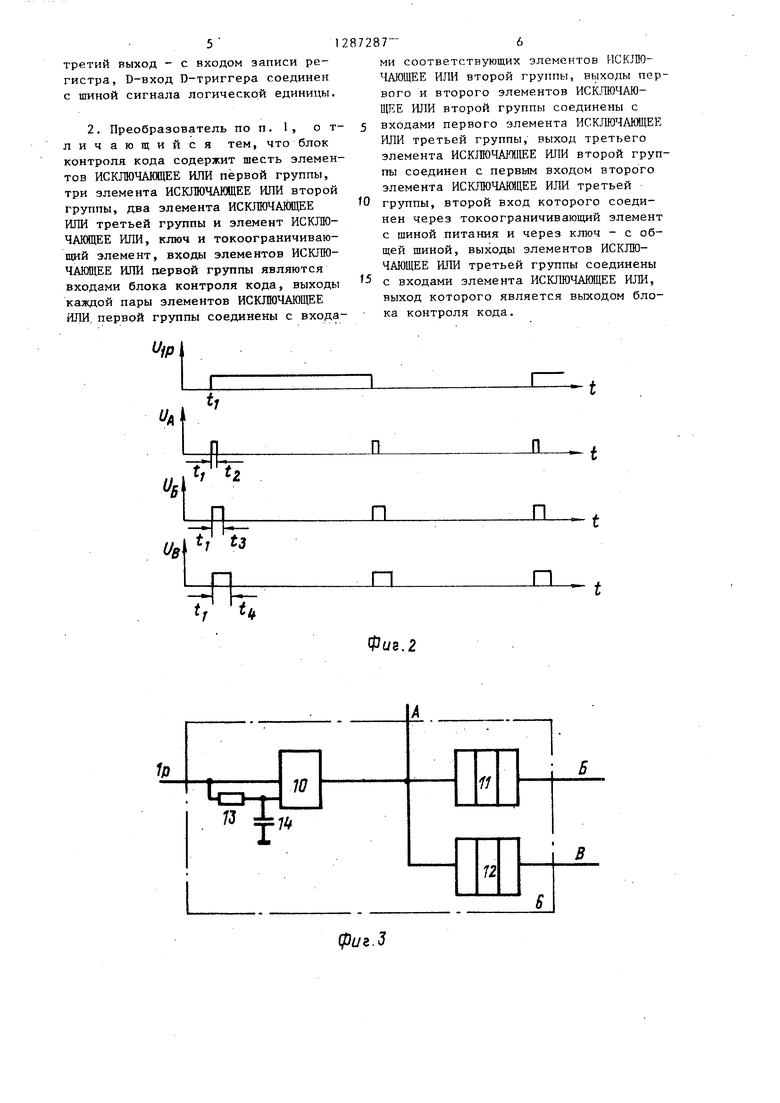

На фиг. 1 изображена схема преобразователя перемещения в параллельный код; на фиг. 2 - диаграмма работы формирователя импульсов; на фиг.З схема формиро вателя управляющих импульсов; на фиг. 4 - пример выполнения блока контроля кода для двенадцати разрядов.

Преобразователь перемещения в код содержит кодирующий элемент 1, блок 2 чувствительных элементов, преобразователь 3 кода, регистр 4, блок 5 контроля кода, формирователь 6 управляющих импульсов, элемент ИЛИ-НЕ 7, D-триггер 8, элемент ИЛИ 9

Формирователь 6 управляющих импульсов содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, ждущие мультивибраторы 11 и 12, резистор 13, конденсатор 14.

Блок 5 контроля кода содержит элементы ИСКЛЮЧАЩЕЕ ИЛИ 15-26, то- коограничивающий элемент на резисторе 27 и ключ 28. Формирователь 6 управляющих импульсов имеет выходы 29-31.

Преобразователь работает следующим образом.

Перемещение кодирующего элемента

1вызывает срабатывание чувствительных элементов блока 2, которые считывают информацию и передают ее на входы преобразователя 3 кода. Изменение уровня сигнала на выходе первого разряда чувствительных элементов блока

2влечет начало процесса коммутации элементов преобразователя 3 кода в соответствии с выбранным методом преобразования двойная щетка или V- считывания и формирования кода перемещения на его выходах, соответственно на входах регистра 4 и блока

5 контроля кода. Изменение кода на выходе преобразователя 3 кода вызывает срабатьшание элементов блока 5 контроля кода.

Изменение уровня сигнала первого разряда на выходе преобразователя 3 кода вызывает появление трех импульсов (фиг. 2) разной длительности

0

t5

20

25

87287-2

(t--t,) и;) выходах 29 - 31 формирователя 6 утгрявляющих импульсов, причем t.-r, , .

В исходном состоянки на выходах 29-31 формирователя 6 управляющих импульсов имеется низкий уровень сигнала, на выходе блока 5 контроля к-ода - высокий уровень сиг нала, на выходе элемента ИЛИ-НЕ 7 - низкий уровень сигнала, на выходе Готовность преобразователя - высокий уровень сигнала, соответствующий достоверной информации на выходах регистра 4, на первом и втором входах элементов ИЛИ 9 и на выходе Запрет Преобразователя установлены низкие уровни сигналов.

Если в интервалах между появлением импульсов на выходе 29 формирователя 6 управляюшлх импульсов на выходе блока 5 контроля кода по какой-либо причине изменился уровень сигнала на низкий, то на выходе эле мента ИЛИ-НЕ 7, соответственно и на R-входе D-триггера 8, устанавливается высокий уровень сигнала, в результате на выходе Готовность преобразователя устанавливается низкий уровень сигнала, соответствующий неготовности к работе преобрайовате- ля ввиду появления о шибки считывания. Одновременно на втором входе элемента ИЛИ 9 и на выходе Запрет преобразователя устанавливаютс я высокие уровни сигналов. Высокий уровень сигнала на выходе Запрет преобразователя в этом случае запрещает считывание информации с выходов регистра 4 из-за недостоверности кода на выходе регистра 4, что определяется низким уровнем сигнала на выходе Готовность преобразователя.

Изменение кода на выходе преобразователя 3 кода сопровождается переходными процессами в элементах преобразователя 3 кода и блока 5 контроля кода, причем при V-считы- вании этот процесс более продолжительный. Чтобы исключить запись сигнала с выхода блока 5 контроля кода в D-триггер 8 на время переходных процессов при смене кода, введен элемент ИЛИ-НЕ 7.

30

35

45

50

Импульс с выхода 29 формирователя 6 устанавливает на выходе элемента ИЛИ-НЕ 7 низкий уровень сигнала независимо от уровня сигнала на втором

3

входе ИЛИ-НЕ 7. Таким образом, длительность сигнала с выхода 29 формирователя 6 импульсов должна бы не менее времени протекания переходных процессов в элементах преобра- зователя 3 кода и блока 5 контроля. Импульс с выхода 29 формирователя, 6 импульсов своим передним фронтом подтверждает или устанавливает на выходе Готовность преобразователя высокий уровень сигнала, если на R-входе D-триггера 8 низкий уровень сигнала. Если на выходе блока 5 конроля кода имеется низкий уровень сигнала, соответственно на R-входе D-триггера 8 высокий уровень сигнала, то .установка высокого уровня синала на выходе Готовность преобразователя не происходит по переднему фронту импульса С выхода 29 формирователя 6 импульсов, ввиду приоритетности R-входа D-триггера 8 по отношению к остальным его входам. Низки уровень сигнала на R-входе D-триггера 8, устанавливаемый импульсом с выхода 29 формирователя 6 на время переходных процессов в преобразователе 3 кода и блока 5 контроля кода через элемент ИЛИ-НЕ 7, задерживается элементом 11ПИ-НЕ 7 на время пере ходных процессов в самом элементе ИЛИ-НЕ 7. Таким образом, передний фронт этого импульса поступает на С-вход D-триггера В несколько раньш Изменения уровня сигнала на R-входе D-триггера 8 и в результате исключается возможность промигивания сигнала низкого уровня на выходе Готовность преобразователя.

Импульс с выхода 30 формировате-

ля 6 в момент времени t (фиг. 2) осуществляет запись в регистр 4 кода, установившегося на его входах. Длительность , этого импульса выбирается с учетом переходных процессов в линиях связи и времени реакции системы потребителя информации, но не менее ,.

Импульс с выхода 31 формирователя 5 импульсов поступает на первый вход элемента ИЛИ 9, на выходе которого формируется сигнал Запрет, запрещающий считывание кода с выходов регистра 4 на время (. Длительност импульса выбирается из условия, что интервал времени не меньще времени переходных процессов в линии связи, по которой передается код с выходов регистра 4.

5 tO 5 0 5

0

5

Блок 5 контроля кода работает сле-- дуюшим образом.

Если общее число разрядов кода перемещения и дополнительного разряда, на которых установился высокий уровень сигнала, четное, то на выходе блока 5 контроля кода устанавливается высокий уровень сигнала. Контроль на нечетность возможен при соответствующем кодировании дополнительного разряда Доп.р. с одновременным подключением к источнику низкого уровня сигнала (Общий О). В этом случае при наличии достоверного кода на его выходе устанавливается высокий уровень сигнала.

В результате нарушения функционирования преобразователя по любому из разрядов, включая - контрольный, на выходе блока 5 контроля кода устанавливается низкий уровень сигнала, соответствующий недостоверному коду на входах блока 5 контроля кода и регистра 4.

Формула изобретения

5 tO 5 0 5

0

5

0

1

Преобразователь перемещения в код, содержащий последовательно соединенные кодирующий элемент, блок чувствительных элементов и преобразователь кода, выходы которого соединены с входами регистра, выходы которого являются выходами преобразователя, элемент КПИ-НЕ, отличающийся тем, что, с целью повышения фун :циональной надежности преобразователя за счет повышения достоверности выходного кода, в него введены блок контроля кода, формирователь управляющих импульсов, Dтриггер и элемент ИЛИ, выходы преобразователя кода соединены с входами блока контроля кода, выход которого соединен с первым входом элемента ИЛИ-НЕ, выход которого соединен с R-входом D-триггера, первый выход которого является выходом Готовность преобразователя, второй выход соединен с первым входом, .элемента ИЛИ, выход которого является выходом Запрет преобразователя, выход младшего разряда преобразователя кода соединен с входом формирователя управляющих импульсов, первый выход которого соединен с вторым входом элемента ИЛИ- НЕ и С-входом D-триггера, второй выход - с вторым входом элемента ИЛИ,

5 1

третий выход - с входом записи регистра, D-вход D-триггера соединен с шиной сигнала логической единицы.

2. Преобразователь по п. 1, отличающийся тем, что блок контроля кода содержит шесть элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, два элемента ИСКЛЮЧАЩЕЕ ИЛИ третьей группы и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, ключ и токоограничивающий элемент, входы элементов ИСКЛЮЧАЮЩЕЕ ИЖ первой группы являются входами блока контроля кода, выходы каждой пары элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. первой группы соединены с входа

287287 -6

ми соответствующих элементов ИСК1Ю- ЧАЮЩЕЕ ИЛИ второй группы, выходы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы соединены с

5 входами первого элемента ИСКЛЮЧАКЙЦЕЕ ИЛИ третьей группы, выход третьего элемента ИСКЛЮЧАЮиЩЕ ИЛИ второй группы соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ третьей

0 группы, второй вход которого соединен через токоограничивающий элемент с шиной питания и через ключ - с общей шиной, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ третьей группы соединены

5 с входами элемента ИСКЛЮЧАЩЕЕ ИЛИ,

выход которого является выходом бло- - ка контроля кода.

и.

UB

-fV t/

-fV

SL

Л

П

п

HL

П

Фаз.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство регистрации однополярных однократных импульсов | 1988 |

|

SU1594432A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРИОДА В КОД | 2000 |

|

RU2178908C1 |

| Устройство для автоматического контроля больших интегральных схем | 1985 |

|

SU1249518A1 |

| Устройство для кодирования | 1985 |

|

SU1287294A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Многоканальное устройство для контроля параметров | 1978 |

|

SU911539A2 |

| Устройство для управления ленточным перфоратором | 1985 |

|

SU1310860A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Преобразователь угла поворота вала в код | 1988 |

|

SU1522408A1 |

| Автопрокладчик пути судна на карте | 1989 |

|

SU1716554A1 |

Изобретение относится к автоматике и вычислительной технике, может быть использовано в цифровых позиционных регуляторах, информационных системах, системах управления положением механизмов. Целью изобретения является повьппение достоверности передаваемой информации преобразователем. Для этого в-преобразователь перемещения в код, содержащий кодирующий элемент 1, чувствительные элементы 2, преобразователь 3 кода, регистр 4 и элемент ИЛИ-НЕ 7, введены блок 5 контроля кода, формирователь 6 управляющих импульсов, D-триггер 8 и элемент ИЛИ 9. Поставленная цель достигается за счет того, что вместе с кодом, передаваемым потребителю, формируются сигналы Готовность и Запрет, которые запрещают считывание кода с выходов преобразователя при наличии ошибки кодирования и преобразования, а также на время переходных процессов в цепях преобразователя и линиях связи. I з.п. ф-лы, 4 ил. (/)

11

В

12

фиг.З

IL

2p

15

5p

6p

17

n

rOO

2B

.

Составитель E. Бударина Редактор E. Копча Техред Л.Сердюкова Корректоре. Шекмар

----- - -i-- - ....-. - - .««.«.- - «, i «, .«,.,.«i .«.«.. «.«.«

Заказ 7730/59 Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

1

2if

Авторы

Даты

1987-01-30—Публикация

1985-06-24—Подача