11

Изобретение относится к вычислительной технике, в частности к средствам контроля и диагностики неисправностей сложных цифровых объектов и может использовано для функционального контроля и поиска неис- правностей в микропроцессорных больших интегральных схемах (БИС).

Целью изобретения является расширение диагностических возможностей за счет анализа ошибок по прерыванию и повьш1ение быстродействия устройства.

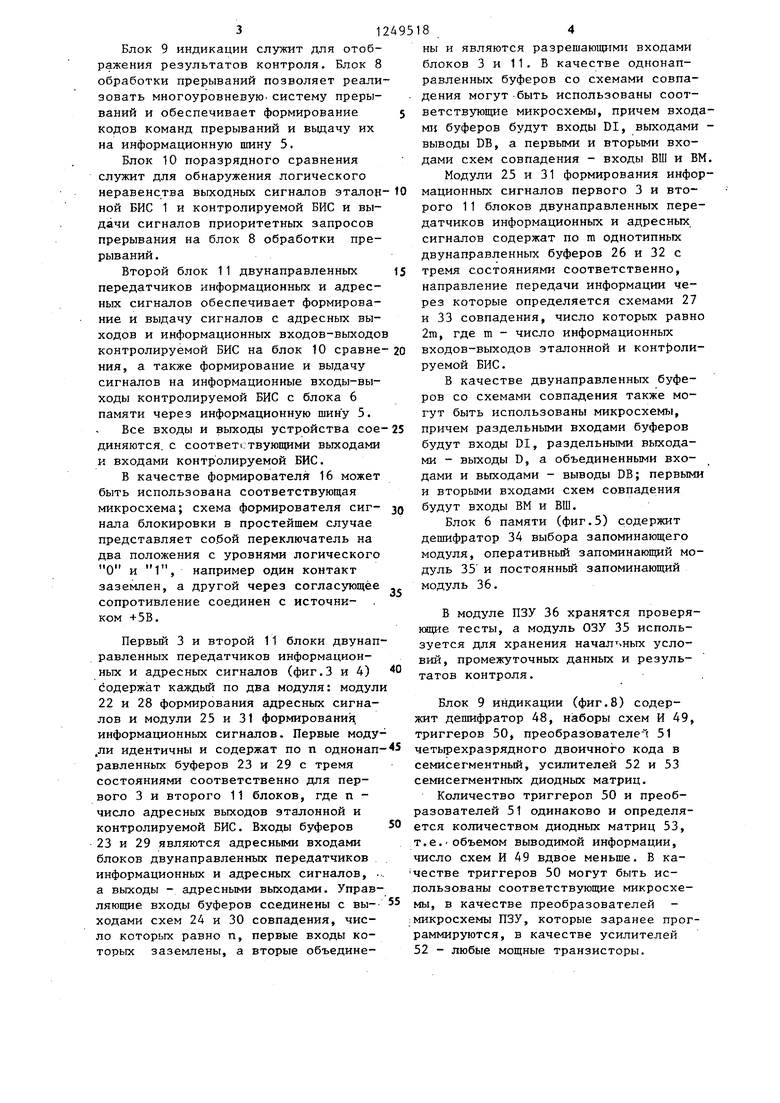

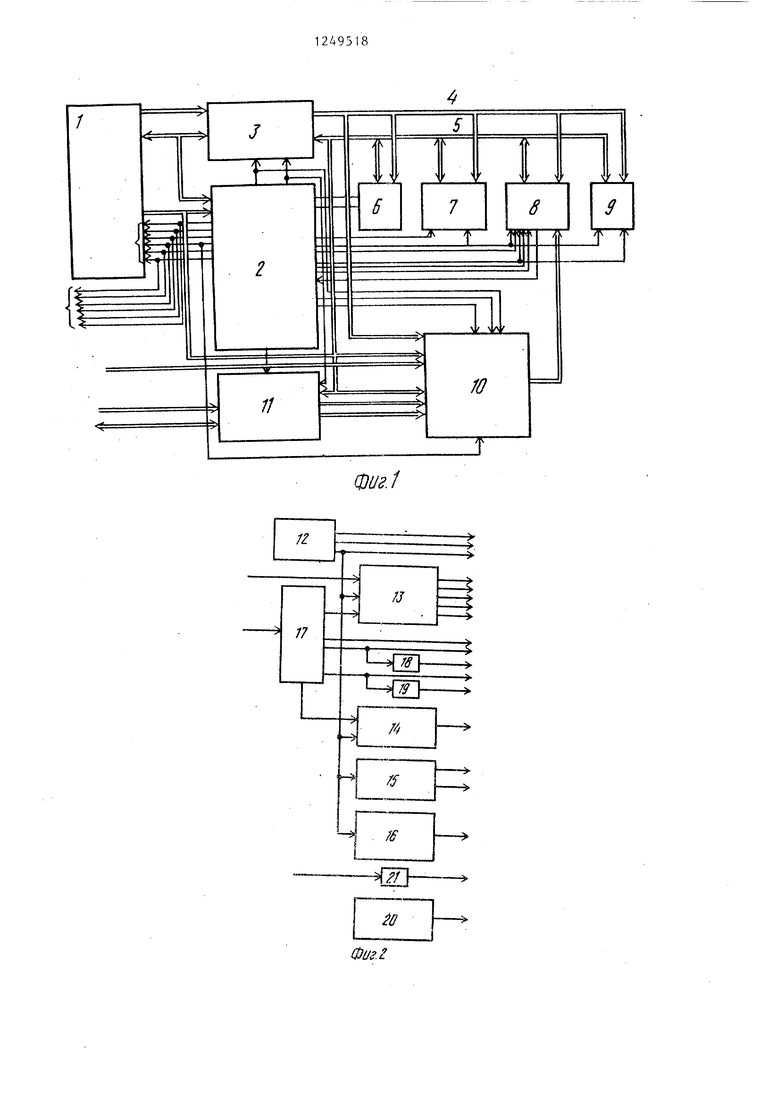

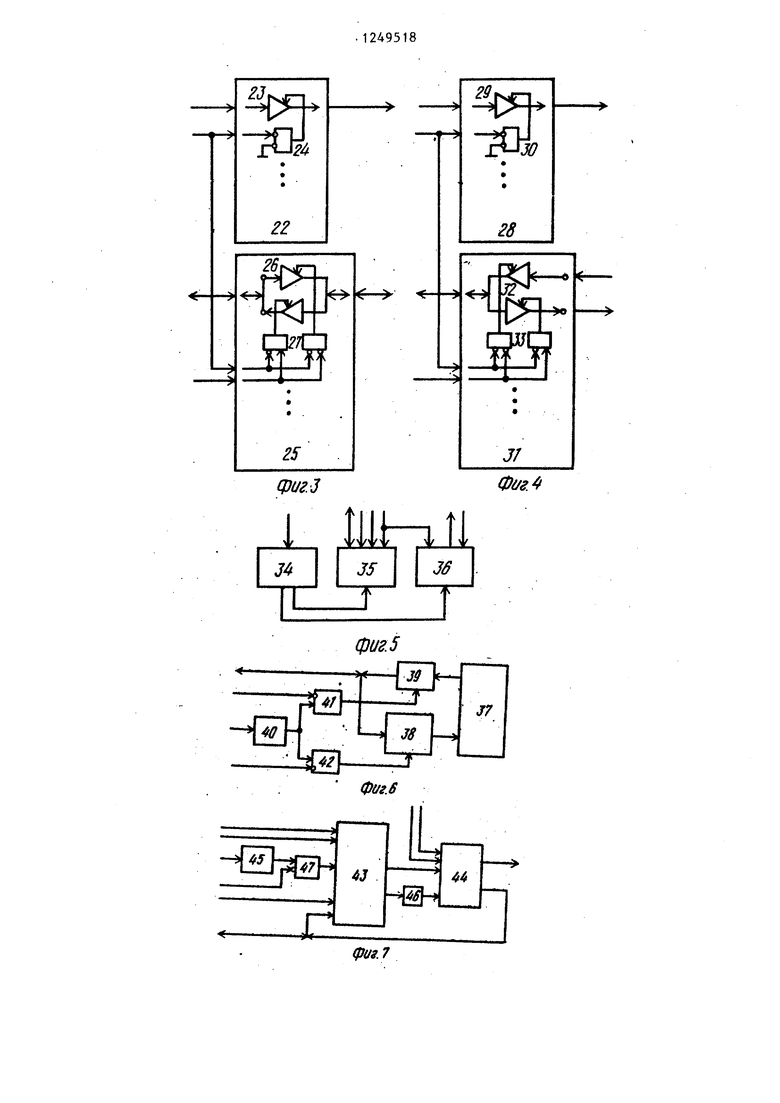

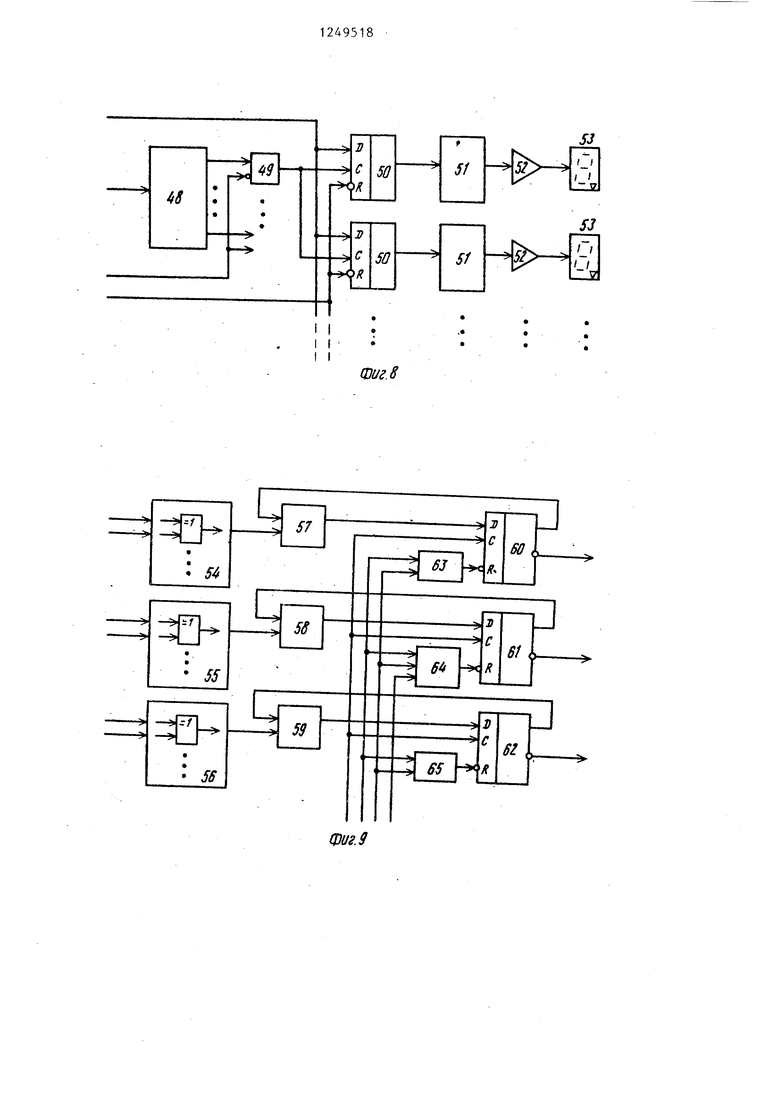

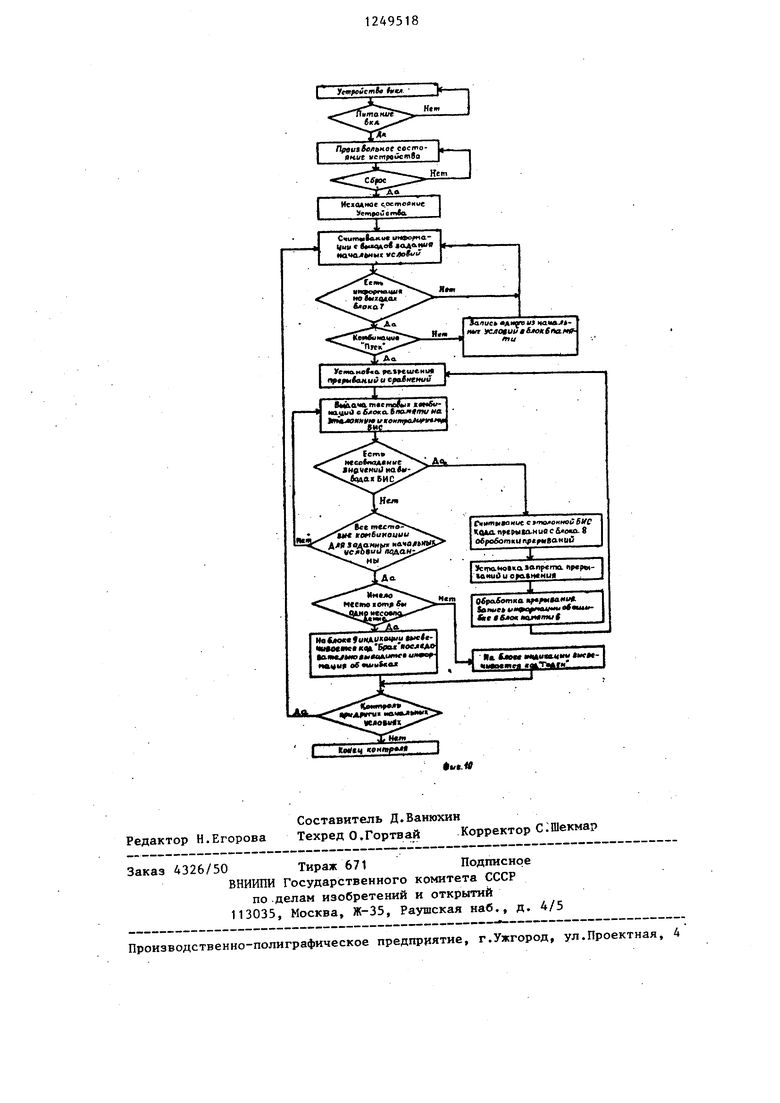

На фиг.1 представлена функциональная схема устройства для автоматического контроля БИС; на фиг.2-9 - функциональные схемы блоков соответственно управления, первого и второго блоков двунаправленных передатчиков информационных и адресных сигналов, памяти, задания начальных условий, обработки прерываний, индикации и поразрядного сравнения; на фиг.10 блок-схема алгоритма работы устройства.

Устройство для автоматического контроля БИС (фиг.1Х содержит микропроцессорную эталонную БИС 1, блок 2 управления, первый блок 3 двунаправ- )ленных передатчиков информационных и адресньпс сигналов, выходную адресную шину 4 блока 3, двунаправленную информационную шину 5 блока 3, блок 6 памяти, блок 7 задания начальных

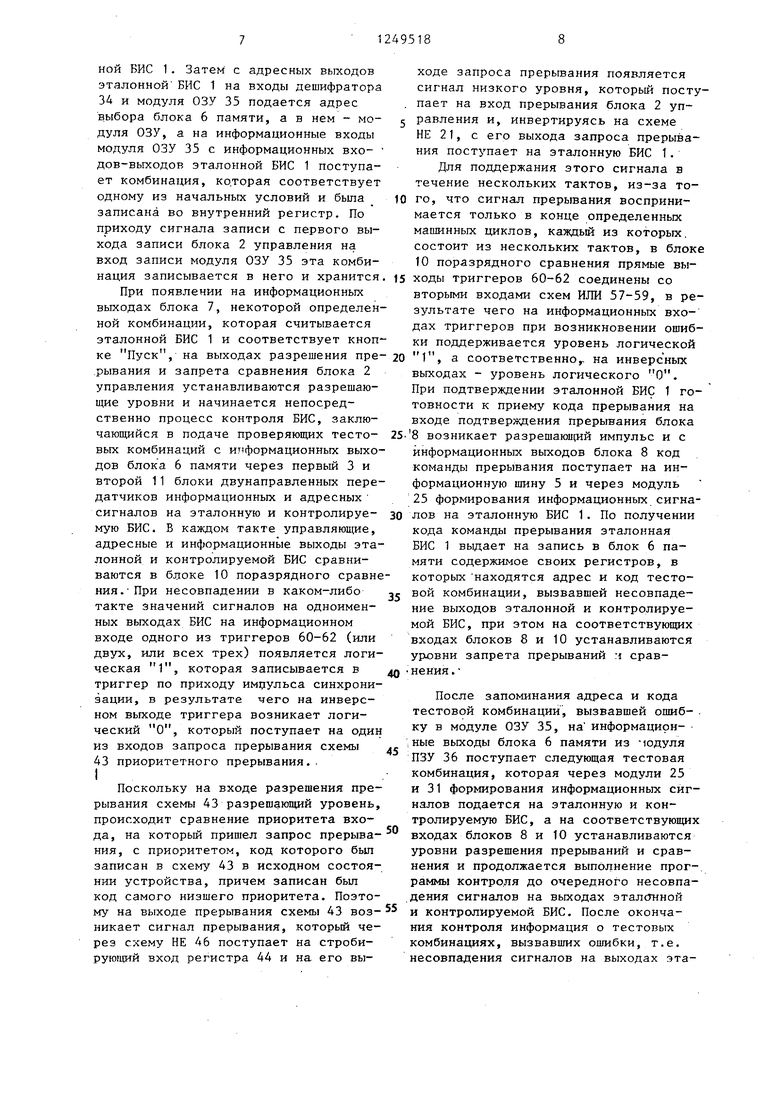

Блок поразрядного сравнения 10 (фиг.9) содержит, первый 54, второй 55 и третий 56 модули поразрядного сравнения, первый 57, второй 58 и третий 59 элементы ИЛИ, первый 60, второй 61 и третий 62 триггеры, перусловий, блок 8 обработки прерываний, 63, второй 64 и третий 65 элемен- блок 9 индикации, блок 10 поразряд- ИЛИ-НЕ.

ного сравнения, второй блок 11 двунап-- Первый блок 3 двунаправленных пе- равленньпс передатчиков информацион-. редатчиков информационных и адресных

ных и адресных сигналов.

Блок 2 управления (фиг.2) содер- , жит генератор 12 тактовых импульсов, формирователь 13 сигналов чтения, записи и подтверждения прерьшания, формирователь 14 сигнала готовности, формирователь 15 сигнала сброса, формирователь 16 сигнала синхронизации сравнения, дешифратор 17 управляющих сигналов, первый 18 и второй 19 элементы НЕ, формирователь 20 сигнала блокировки, третий 21 элемент НЕ.

Первый блок 3 двунаправленных передатчиков информационных и адресных сигналов (фиг.З) содержит модуль 22 формирования адресных сигналов, п однонаправленных буферов 23, п схем 24 совпадения, модуль 25 формирования информационных сигналов, m двунаправленных буферов 26, 2т схем 27 совпадения.

сигналов обеспечивает формирование 40 и выдачу сигналов с адресных выходов и информационных входов-выходов эталонной БИС 1 через шину 4 адреса и информационную шину 5 на остальные блоки устройства, а также формирова- 45 ние и вьщачу сигналов на информационные входы-выходы эталонной БИС с других блоков устройства через информационную шину 3.

Блок 6 памяти служит для хранения проверяющих тестов и исходных данных необходимых для проведения контроля, а -также для хранения промежуточных данных и результатов контроля.

55 Блок 7 задания начальных условий предназначен для записи в блок 6 пв мяти исходных данньк, необходимых для проведения контроля.

0

Второй блок 11 двунаправленных передатчиков информационных и адресных сигналов (фиг.4) содержит модуль 28 формирования адресных сиг налов, п однонаправленных буферов 29, п схем 30 совпа йения, модуль 31 формирования информационных сигналов, га двунаправленных буферов 32, 2ni схем 33 совпадения.

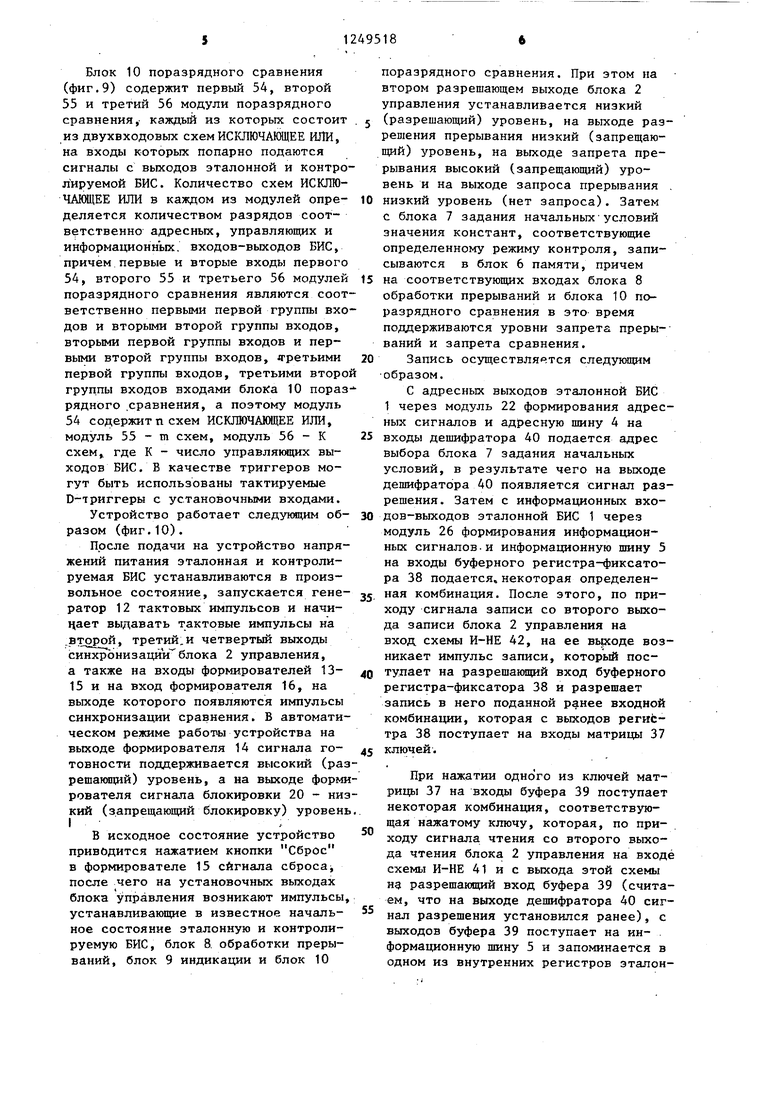

Блок 6 памяти (фиг.5) содержит дешифратор ЗА, модуль ОЗУ 35, модуль ПЗУ 36.

Блок 7 задания начальных условий (фиг.6) содержит матрицу 37 ключей, 5 буферный регистр-фиксатор 38, буфер 39, дешифратор 40, первый 41 и второй 43 элементы И-НЕ.

Блок 8 обработки прерываний (фиг.7) содержит блок 43 приоритетного прерывания, многорежимньй буфер- ньй регистр 44, дешифратор 45, элемент НЕ 46, элемент И-НЕ 47.

Блок .9 индикации (фиг.8) содержит дешифратор 48, элементы И 49, триггеры 50, преобразователь 51 четырехразрядного двоичного кода в семисег- ментный, усилители 52, диодные мат- рицы 53.

Блок поразрядного сравнения 10 (фиг.9) содержит, первый 54, второй 55 и третий 56 модули поразрядного сравнения, первый 57, второй 58 и третий 59 элементы ИЛИ, первый 60, второй 61 и третий 62 триггеры, пер0

5

0

63, второй 64 и третий 65 элемен- ИЛИ-НЕ.

сигналов обеспечивает формирование и выдачу сигналов с адресных выходов и информационных входов-выходов эталонной БИС 1 через шину 4 адреса и информационную шину 5 на остальные блоки устройства, а также формирова- ние и вьщачу сигналов на информационные входы-выходы эталонной БИС с других блоков устройства через информационную шину 3.

Блок 6 памяти служит для хранения проверяющих тестов и исходных данных необходимых для проведения контроля, а -также для хранения промежуточных данных и результатов контроля.

Блок 7 задания начальных условий предназначен для записи в блок 6 пв мяти исходных данньк, необходимых для проведения контроля.

Блок 9 индикации служит для отображения результатов контроля. Блок 8 обработки прерываний позволяет реализовать многоуровневую систему прерываний и обеспечивает формирование кодов команд прерываний и выдачу их на информационную шину 5.

Блок 10 поразрядного сравнения служит для обнаружения логического неравенства выходных сигналов эталон ной БИС 1 и контролируемой БИС и выдачи сигналов приоритетных запросов прерывания на блок 8 обработки прерываний.

Второй блок 11 двунаправленных передатчиков информационных и адресных сигналов обеспечивает формирование и выдачу сигналов с адресных выходов и информационных входов-выходо контролируемой БИС на блок 10 сравне НИН, а также формирование и выдачу сигналов на информационные входы-выходы контролируемой БИС с блока 6 памяти через информационную шину 5.

Все входы и выходы устройства сое диняются. с соответствующими выходами и входами контролируемой БИС.

В качестве формирователя 16 может быть использована соответствующая микросхема; схема формирователя сигнала блокировки в простейшем случае представляет со.бой переключатель на два положения с уровнями логического О и 1, например один контакт заземлен, а другой через согласующее сопротивление соединен с источником +5В.

Первый 3 и второй 11 блоки двунаправленных передатчиков информационных и адресных сигналов (фиг.З и 4) содержат каждый по два модуля: модули

22и 28 формирования адресных сигналов и модули 25 и 31 формирований информационных сигналов. Первые моду- ,ли идентичны и содержат по п однонаправленных буферов 23 и 29 с тремя состояниями соответственно для первого 3 и второго 11 блоков, где п - число адресных выходов эталонной и контролируемой БИС. Входы буферов

23и 29 являются адресными входами блоков двунаправленных передатчиков информационных и адресных сигналов, . а выходы - адресными выходами. Управляющие входы буферов соединены с вы- ходами схем 24 и 30 совпадения, число которых равно п, первые входы которых заземлены, а вторые объедине5

Ю

15 20

25

30

5

0

З 0

5

ны и являются разрешающими входами блоков 3 и 11. В качестве однонаправленных буферов со схемами совпадения могут быть использованы соответствующие микросхемы, причем входами буферов будут входы DI, выходами - выводы DB, а первыми и вторыми входами схем совпадения - входы ВШ и ВМ.

Модули 25 и 31 формирования информационных сигналов первого 3 и второго 11 блоков двунаправленных передатчиков информационных и адресных сигналов содержат по m однотипных двунаправленных буферов 26 и 32 с тремя состояниями соответственно, направление передачи информации через которые определяется схемами 27 и 33 совпадения, число которых равно 2т, где m - число информационных входов-выходов эталонной и конт{)оли- руемой БИС.

В качестве двунаправленных буферов со схемами совпадения также могут быть использованы микросхемы, причем раздельными входами буферов будут входы DI, раздельными выходами - выходы D, а объединенными входами и выходами - выводы DB; первыми и вторыми входами схем совпадения будут входы ВМ и ВШ.

Блок 6 памяти (фиг.5) содержит дешифратор 34 выбора запоминающего модуля, оперативный запоминающий модуль 35 и постоянньш запоминающий модуль 36.

В модуле ПЗУ 36 хранятся проверяющие тесты, а модуль ОЗУ 35 используется для хранения начальных условий, промежуточных данных и результатов контроля.

Блок 9 индикации (фиг.8) содержит дешифратор 48, наборы схем И 49, триггеров 50j преобразователе 51 четырехразрядного двоичного кода в семисегментный, усилителей 52 и 53 семисегментных диодных матриц.

Количество триггеров 50 и преобразователей 51 одинаково и определяется количеством диодных матриц 53, т.е.-объемом выводимой информации, число схем И 49 вдвое меньше. В качестве триггеров 50 могут быть использованы соответствующие микросхемы, в качестве преобразователей микросхемы ПЗУ, которые заранее программируются, в качестве усилителей 52 - любые мощные транзисторы.

Блок 10 поразрядного сравнения (фиг.9) содержит первый 54, второй 55 и третий 56 модули поразрядного сравнения, каждый из которых состоит из двухвходовых схем ИСКЛЮЧАЮЩЕЕ ИЛИ, на входы которых попарно подаются сигналы с выходов эталонной и контролируемой БИС. Количество схем ИСКЛЮЧАЮЩЕЕ ИЛИ в каждом из модулей опре- деляется количеством разрядов соответственно адресных, управляющих и информационн ых. входов-выходов БИС, причем первые и вторые входы первого 54, второго 55 и третьего 56 модулей поразрядного сравнения являются соответственно первыми первой группы входов и вторыми второй группы входов, вторыми первой группы входов и первыми второй группы входов, «третьими первой группы входов, третьими второ группы входов входами блока 10 пораз рядного .сравнения, а поэтому модуль 54 содержитп схем ИСКЛЮЧАЮЩЕЕ ИЛИ, модуль 55 - m схем, модуль 56 - К схем,, где К - число управляющих выходов БИС. В качестве триггеров могут быть использованы тактируемые D-триггеры с установочными входами.

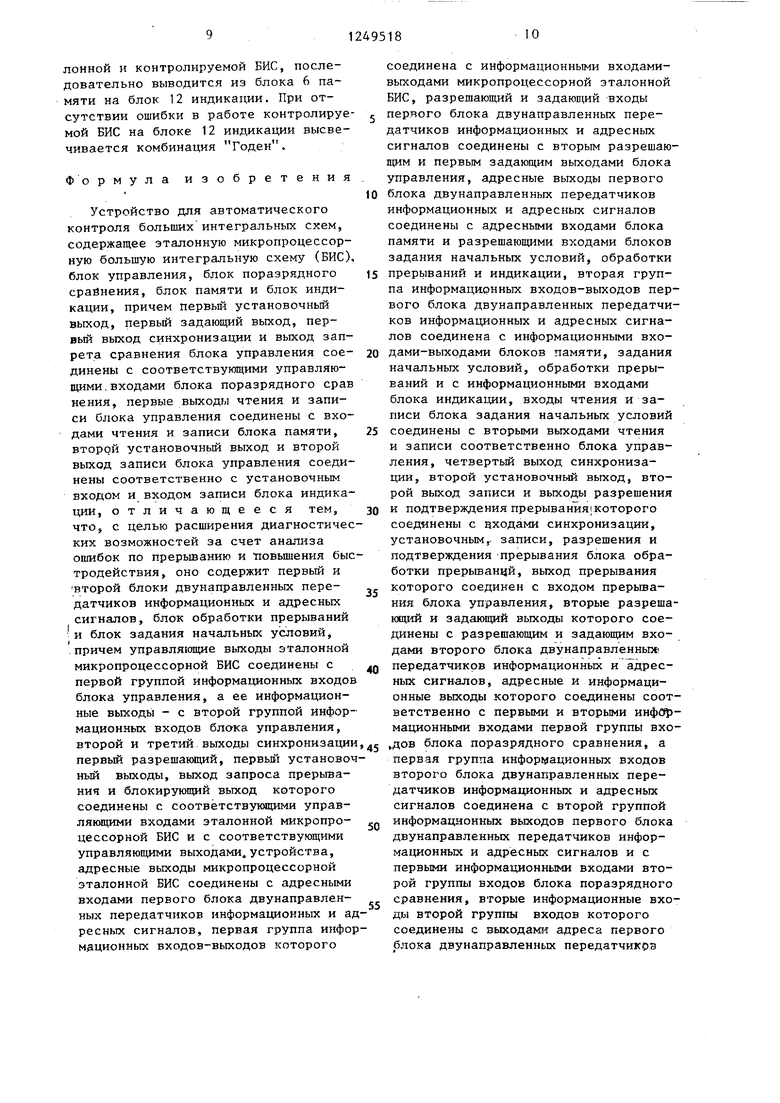

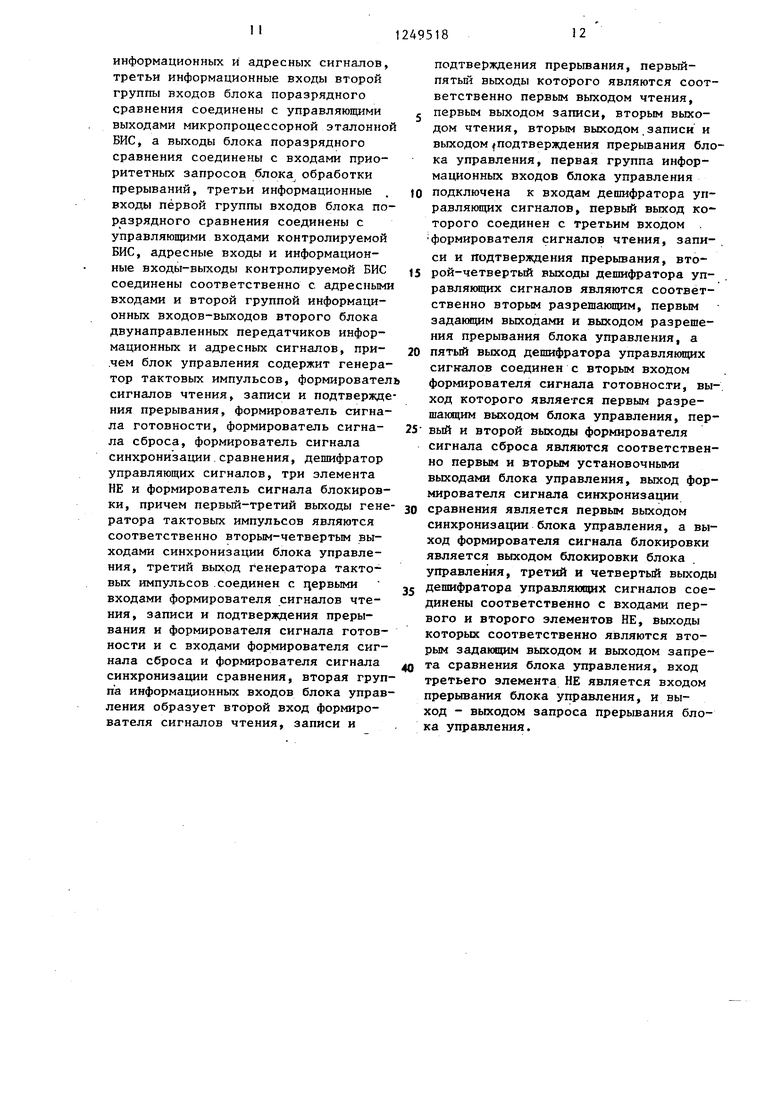

Устройство работает следукицим об- разом (фиг.10).

После подачи на устройство напряжений питания эталонная и контролируемая БИС устанавливаются в произвольное состояние, запускается гене- ратор 12 тактовых импульсов и начи- цает выдавать тактовые импульсы на второй, третий.и четвертый выходы синхронизации блока 2 управления, а также на входы формирователей 13- 15 и на вход формирователя 16, на выходе которого появляются импульсы синхронизации сравнения. В автоматическом режиме работы устройства на выходе формирователя 14 сигнала го- товности поддерживается высокий (раз решаняций) уровень, а на выходе формирователя сигнала блокировки 20 - низкий (запрещающий блокировку) уровень I

В исходное состояние устройство приводится нажатием кнопки Сброс в формирователе 15 сигнала сбросаj после чего на установочных выходах блока управления возникают импульсы, устанавливающие в известное начальное состояние эталонную и контролируемую БИС, блок 8 обработки прерываний, блок 9 индикации и блок 10

ч-

поразрядного сравнения. При этом на втором разрешающем выходе блока 2 управления устанавливается низкий (разрешающий) уровень, на выходе разрешения прерывания низкий (запрещаю- ) уровень, на выходе запрета прерывания высокий (запрещающий) уровень и на выходе запроса прерывания низкий уровень (нет запроса). Затем с блока 7 задания начальных условий значения констант, соответствующие определенному режиму контроля, записываются в блок 6 памяти, причем на соответствующих входах блока 8 обработки прерываний и блока 10 поразрядного сравнения в это время поддерживаются уровни запрета прерываний и запрета сравнения.

Запись осуществляется следующим образом.

С адресных выходов эталонной БИС 1 через модуль 22 формирования адресных сигналов и адресную шину 4 на входы дешифратора 40 подается адрес выбора блока 7 задания начальных условий, в результате чего на выходе дешифратора 40 появляется сигнал разрешения. Затем с информационных входов-выходов эталонной БИС 1 через модуль 26 формирования информационных сигналов-и информационную шину 5 на входы буферного регистра-фиксатора 38 подается.некоторая определенная комбинация. После этого, по приходу сигнала записи со второго выхода записи блока 2 управления на вход схемы И-НЕ 42, на ее вьрсоде возникает импульс записи, который пос- тулает на разрешающий вход буферного регистра-фиксатора 38 и разрешает запись в него поданной ранее входной комбинации, которая с выходов регистра 38 поступает на входы матрицы 37 ключей.

При нажатии одно го из ключей матрицы 37 на входы буфера 39 поступает некоторая комбинация, соответствующая нажатому ключу, которая, по приходу сигнала, чтения со второго выхода чтения блока 2 управления на вход схемы И-НЕ 41 и с выхода этой схемы нд разрешающий вход буфера 39 (считаем, что на выходе дешифратора 40 сигнал разрешения установился ранее), с выходов буфера 39 поступает на ин- . формационную шину 5 и запоминается в одном из внутренних регистров эталонной БИС 1. Затем с адресных выходов эталонной БИС 1 на входы дешифратора 34 и модуля ОЗУ 35 подается адрес выбора блока 6 памяти, а в нем - мо- дуля ОЗУ, а на информационные входы модуля ОЗУ 35 с информационных вхо- дов-выходов эталонной БИС 1 поступает комбинация, которая соответствует одному из начальных условий и бьша записана во внутренний регистр. По приходу сигнала записи с первого выхода записи блока 2 управления на вход записи модуля ОЗУ 35 эта комбинация записывается в него и хранится

При появлении на информационных выходах блока 7, некоторой определенной комбинации, которая считывается эталонной БИС 1 и соответствует кнопке Пуск, на выходах разрешения пре рывания и запрета сравнения блока 2 управления устанавливаются разрешающие уровни и начинается непосредственно процесс контроля БИС, заключающийся в подаче проверяющих тесто- вых комбинаций с информационных выходов блока 6 памяти через первый 3 и второй 11 блоки двунаправленных передатчиков информационных и адресных сигналов на эталонную и контролируе- мую БИС. В каждом такте управляющие, адресные и информационные выходы эталонной и контролируемой БИС сравниваются в блоке 10 поразрядного сравнения. При несовпадении в каком-либо такте значений сигналов на одноименных выходах БИС на информационном входе одного из триггеров 60-62 (или двух, или всех трех) появляется логическая 1, которая записывается в триггер по приходу имцульса синхронизации, в результате чего на инверсном выходе триггера возникает логический О, который поступает на один из входов запроса прерывания схемы 43 приоритетного прерывания.. I

Поскольку на входе разрешения прерывания схемы 43 разрешающий уровень, происходит сравнение приоритета входа, на который пришел запрос прерыва- ния, с приоритетом, код которого бьш записан в схему 43 в исходном состоянии устройства, причем записан был код самого низшего приоритета. Поэтому на выходе прерывания схемы 43 воз- никает сигнал прерывания, который через схему НЕ 46 поступает на строби- рующий вход регистра 44 и на его выходе запроса прерывания появляется сигнал низкого уровня, которьш поступает на вход прерывания блока 2 управления и, инвертируясь на схеме НЕ 21, с его выхода запроса прерывания поступает на эталонную БИС 1.

Для поддержания этого сигнала в течение нескольких тактов, из-за того, что сигнал прерывания воспринимается только в конце определенных машинных циклов, каждый из которых, состоит из нескольких тактов, в блок 10 поразрядного сравнения прямые выходы триггеров 60-62 соединены со вторыми входами схем ИЛИ 57-59, в результате чего на информационных входах триггеров при возникновении ошибки поддерживается уровень логической 1, а соответственно на инверс ных выходах - уровень логического О. При подтверждении эталонной БИС 1 го товности к приему кода прерывания на входе подтверждения прерывания блока 8 возникает разрешающий импульс и с информационных выходов блока 8 код команды прерывания поступает на информационную шину 5 и через модуль 25 формирования информационных сигналов на эталонную БИС 1. По получении кода команды прерывания эталонная БИС 1 выдает на запись в блок 6 памяти содержимое своих регистров, в которых находятся адрес и код тестовой комбинации, вызвавшей несовпадение выходов эталонной и контролируемой БИС, при этом на соответствующих входах блоков 8 и 10 устанавливаются урювни запрета прерываний :i срав- нения.

После запоминания адреса и кода тестовой комбинации, вызвавшей ошиб- ку в модуле ОЗУ 35, на информацион- :ные вькоды блока 6 памяти из юдуля ПЗУ 36 поступает следующая тестовая комбинация, которая через модули 25 и 31 формирования информационных сигналов подается на эталонную и контролируемую БИС, а на соответствующих входах блоков 8 и 10 устанавливаются уровни разрешения прерываний и сравнения и продолжается выполнение программы контроля до очередного несовпадения сигналов на выходах эталстнной и контролируемой БИС. После окончания контроля информация о тестовых комбинациях, вызвавших ошибки, т.е. несовпадения сигналов на выходах эталонной и контролируемой БИС, последовательно выводится из блока 6 памяти на блок 12 индикации. При отсутствии ошибки в работе контролируе- мой БИС на блоке 12 индикации высвечивается комбинация Годен.

Формула изобретения

Устройство для автоматического контроля больших интегральных схем, содержащее эталонную микропроцессорную большую интегральную схему (БИС), блок управления, блок поразрядного сравнения, блок памяти и блок индикации, причем первьш установочный выход, первый задающий выход, первый выход синхронизации и выход запрета сравнения блока управления сое- динены с соответствующими управляю- щими,входами блока поразрядного срав нения, первые выходы чтения и записи блока управления соединены с входами чтения и записи блока памяти, второй установочный выход и второй выход записи блока управления соединены соответственно с установочным входом и входом записи блока индикации, отличающееся тем, что, с целью расширения диагностических возможностей за счет анализа ошибок по прерьшанию и повьянения быстродействия, оно содержит первый и второй блоки двунаправленных пере- датчиков информационных и адресных сигналов, блок обработки прерываний и блок задания начальных условий, .причем управляющие выходы эталонной микропроцессорной БИС соединены с первой группой информационных входов блока управления, а ее информационные выходы - с второй группой информационных входов блока управления, второй и третий выходы синхронизации первый разрешанмций, первый установочный выходы, выход запроса прерьгаа- ния и блокирующий выход которого соединены с соответствукяцими управляющими входами эталонной микропро- цессорной БИС и с соответствующими управляющими выходами, устройства, адресные выходы микропроцессорной эталонной БИС соединены с адресными входами первого блока двунаправленных передатчиков информационных и адресных сигналов, первая группа информационных входов-выходов которого

s 0 5 о , 5

соединена с информационными входами- выходами микропроцессорной эталонной БИС, разрещающий и задающий входы первого блока двунаправленных передатчиков информационных и адресных сигналов соединены с вторым разрешающим и первым задающим выходами блока управления, адресные выходы первого блока двунаправленных передатчиков информационных и адресных сигналов соединены с адресными входами блока памяти и разрешающими входами блоков задания начальных условий, обработки прерываний и индикации, вторая группа информационных входов-выходов первого блока двунаправленных передатчиков информационных и адресных сигналов соединена с информационными входами-выходами блоков памяти, задания начальных условий, обработки прерываний и с информационными входами блока индикации, входы чтения и записи блока задания начальных условий соединены с вторыми выходами чтения и записи соответственно блока управления, четвертый выход синхронизации, второй установочный выход, второй выход записи и выходы разрешения и подтверждения прерывания;которого соединены с входами синхронизации, установочным,, записи, разрешения и подтверждения прерывания блока обработки прерываний, выход прерывания которого соединен с входом прерьша- ния блока управления, вторые разрешающий и задающий выходы которого соединены с разрешающим и задающим входами второго блока двунаправленных; передатчиков информационных и адресных сигналов, адресные и информационные выходы которого соединены соответственно с первыми и вторыми информационными входами первой группы вхо- ,дов блока поразрядного сравнения, а первая группа информационных входов BTOpoi o блока двунаправленных передатчиков информационных и адресных сигналов соединена с второй группой информационных выходов первого блока двунаправленных передатчиков информационных и адресных сигналов и с первыми информационными входами второй группы входов блока поразрядного сравнения, вторые информационные входы второй группы входов которого соединены с выходами адреса первого блока двунаправленных передатчиков

информационных и адресных сигналов, третьи информационные входы второй группы входов блока поразрядного сравнения соединены с управляющими выходами микропроцессорной эталонной БИС, а выходы блока поразрядного сравнения соединены с входами приоритетных запросов блока обработки прерываний, третьи информационные . входы первой группы входов блока поразрядного сравнения соединены с управляющими входами контролируемой БИС, адресные входы и информационные входы-выходы контролируемой БИС соединены соответственно с. адресными входами и второй группой информационных входов-выходов второго блока двунаправленных передатчиков информационных и адресных сигналов, при- .чем блок управления содержит генератор тактовых импульсов, формировател сигналов чтения, записи и подтверждения прерывания, формирователь сигнала готовности, формирователь сигна- ла сброса, формирователь сигнала синхронизации.сравнения, дешифратор управляющих сигналов, три элемента НЕ и формирователь сигнала блокировки, причем первый-третий выходы гене ратора тактовых импульсов являются соответственно вторым-четвертым выходами синхронизации блока управления, третий выход Генератора тактовых импульсов соединен с дервыми входами формирователя сигналов чтения, записи и подтверждения прерывания и формирователя сигнала готовности и с входами формирователя сигнала сброса и формирователя сигнала синхронизации сравнения, вторая группа информационных входов блока управления образует второй вход формирователя сигналов чтения, записи и

подтверждения прерьгоания, первый- пятый выходы KOTciporo являются соответственно первым выходом чтения, первым выходом записи, вторым выходом чтения, вторым выходом.записи и выходом подтверждения прерывания блока управления, первая группа информационных входов блока управления подключена к входам дешифратора управляющих сигналов, первый выход ко торого соединен с третьим входом . формирователя сигналов чтения, запи-

си и подтверждения прерывания, вто- рой-четвертый выходы дешифратора управляющих сигналов являются соответственно вторым разрешающим, первым задакнцим выходами и выходом разреще- ния прерывания блока управления, а пятый выход дешифратора управляющих сигн алов соединен с вторым входом формирователя сигнала готовности, выход которого является первым разре- шагацим выходом блока управления, первый и второй выходы формирователя сигнала сброса являются соответственно первым и вторым установочными выходами блока управления, выход формирователя сигнала синхронизации сравнения является первым выходом синхронизации блока управления, а выход формирователя сигнала блокировки является выходом блокировки блока управления, третий и четвертьй выходы дешифратора управлякяцих сигналов соединены соответственно с входами первого и второго элементов НЕ, выходы которых соответственно являются вторым задающим выходом и выходом запрета сравнения блока управления, вход третьего элемента НЕ является входом прерывания блока управления, и выход - выходом запроса прерывания блока управления.

фиг.1

Фиг.З

/ , Ф IФ

J

1 t

.4

JS

Jff

фиг.5

ф{/г.6

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между абонентами | 1986 |

|

SU1383376A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для контроля цифровых печатных узлов | 1983 |

|

SU1179233A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для обмена данными между процессором и периферийными устройствами | 1987 |

|

SU1501078A1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СИСТЕМА СБОРА СЕЙСМИЧЕСКИХ ДАННЫХ | 2003 |

|

RU2244945C1 |

| Система для обмена информацией | 1985 |

|

SU1298760A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| Устройство для сопряжения процессоров | 1990 |

|

SU1807495A1 |

Изобретение относится к вычислительной технике, в частности, к сред ствам контроля и диагностики неисправностей цифровых объектов. Оно; может быть использовано для функционального контроля и поиска неисцрав- ностей в микропроцессорных больших интe paльныx схемах (БИС). Цель изобретения - расширение диагностических возможностей за счет анализа ошибок по прерьшанию и повьш1ение быстродействия устройства - достигается тем, что в устройство для автоматического контроля БИС, содержащее блок управления, блок памяти, эталонную микропроцессорную БИС, блок сравнения и блок индикации, введены первый и второй блоки двунаправленных передатчиков информационных и адресных сигналов, блок задания начальных условий и блок обработки прерываний. 10 шт. сл 00

5

4J

Г

Уеряа. pe.tMuieHu« npt faujMi и ffetmHuu

/1p0i/j Ильное сесто- L

enut устройства

ianue «AinraM NaoAJUWT ICJIOtUUtблокеfICLftlfmu

Btttima. ni«nwbi 7w(ev- Hajiud e блска. CiKunrim/ иа lirNt Vffwyw 1/(внл| аА у«ч«|

Иа Смм f иМ. (ж4с- iiuM«ne K4ii 6pat «oejitAO aiM;f«MO«M«a uii i umemf ПАци об «шиСкод

:д

yctTKLMotKaianpemo. npcpw- I umuO и еуйккйш . j

OfpeuSomKO. i ftiiaMuf. Saiwe в6

fit 6ЛО mrMntwf

H. C«DM MiAUMJiini «МГМ- I

«atTTMLfM I

1(нт) J

Составитель Д.Ванюхин Редактор Н.Егорова Техред О.Гортвай Корректор С:Шекмар

Заказ 4326/50 Тираж 671Подписное

ВНИМ1И Государственного комитета СССР

по .делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| Russel S.C | |||

| Incoming inspection alternatives-Circuits manufacturing, 1980, № 2, p.68-75 | |||

| Устройство для автоматическогоКОНТРОля бОльшиХ иНТЕгРАльНыХ CXEM | 1978 |

|

SU798841A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-07—Публикация

1985-01-29—Подача