; Изобретение относится к контроль- но-измерительньм устройствам систем управления и может быть использовано в телеметрических контролирующих системах автоматики,а также для допускового контроля качества электрической энергии по колебаниям уровня величины напряжения.

Цель изобретения - повышение дос- товерности контроля при многоуровневой регистрации величины напряжения источника постоянного тока, величины и времени возникновения внешних, кондуктивных, импульсных, симметрич- ных и случайных помех.

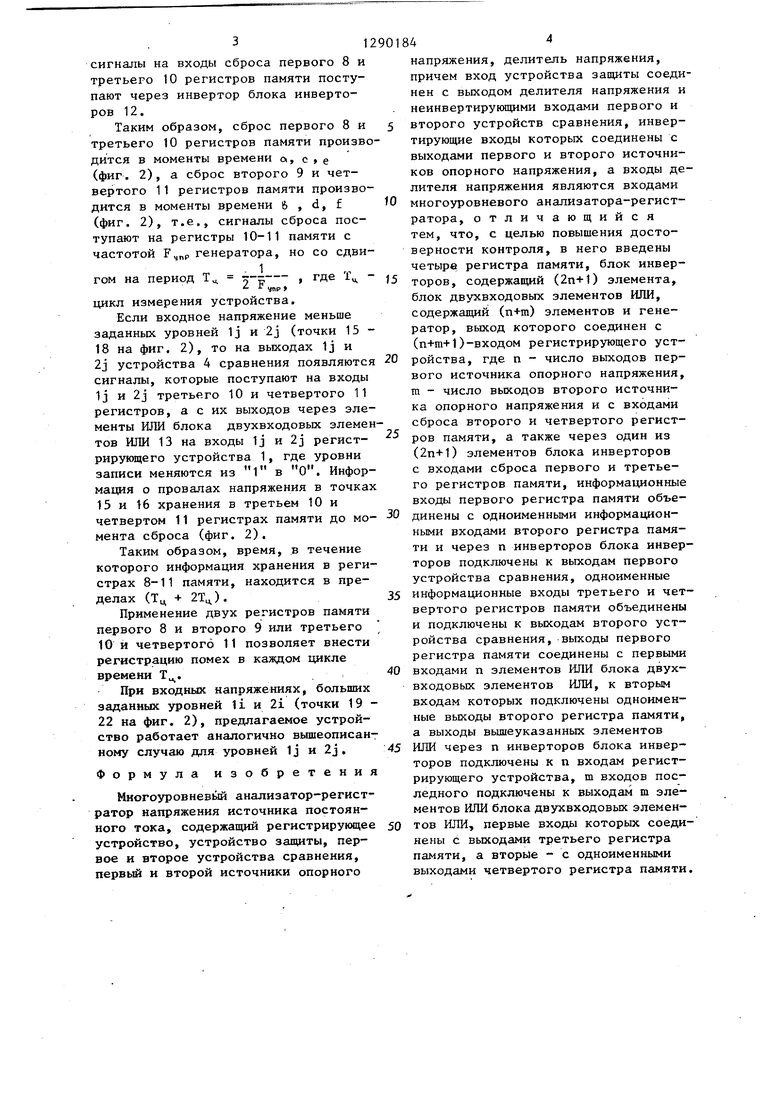

На фиг. 1 изображена структурная схема многоуровневого анализатора- регистратора для контроля п уровней, превышающих номинальное значение на- пряжения, и m уровней, меньших номинального значения; на фиг. 2 - временные диаграммы записи на регистраторе (и ) контролируемого напряжения (Up,,) для случая контроля номи нального напряжения U с помощью дву уровней: i (1,1U,1,5и„) и j(0,yu, 0,5и„).

Анализатор-регистратор содержит регистрирующее устройство 1, устрой- СТ.ВО 2 защиты, делитель 3 напряжения первое 4 и второе 5 устройства сравнения, первый 6 и второй 7 источники

опорного напряжения, первьй 8, второй- 9, третий 10 и четвертый 11 ре- гистры памяти, блок инверторов 12, .содержащий (2п+1) элемента, блок двухвходовых элементов ИЛИ 13, содержащий (п+т) элементов, генератор 14. Вход устройства 2 защиты соеди- нен с одним из входов делителя 3 напряжения и неинвертирующими входами первого 4 и второго 5 устройств сравнения, инвертирующие входы которых соединены с выходами первого 6 и второго 7 источников опорного напряжения. Выход генератора 14 соединен с (п+т+1)-входом регистрирующего устройства 1 и со входами сброса второго 9 и четвертого 11 регист- ров памяти, а также через один из (2п+1) элементов блока инверторов 12 - со входами сброса первого 8 и третьего 10 регистров памяти. Информационные входы первого регистра 8 памяти объединены с одноименными информационными входами второго регистра 9 памяти и подключены через п инверторов блока инверторов 12-к

выходам первого устройства 4 сравнения . Одноименные информационные входы третьего 10 и четвертого 11 регистров памяти объединены и подклчены к выходам второго устройства 5 сравнения. Выходы первого регистра 8 памяти соединены с первыми входами И элементов ИЛИ блока двухвходовых элементов ИЛИ 13, ко вторым входам которых подключены одноименные выходы второго регистра 9 памяти, а выходы вышеуказанных элементов ИЛИ через п инверторов блока инверторов 12 подключены к п входам регистри- рукицего устройства 1, m входов последнего подключены к выходам m эле- ментов ИЛИ блока двухвходовых элементов ИЛИ 13,первые входы которых соединены с выходами третьего регистра 10 памяти, а вторые - с одноименными выходами четвертого регистра 11 памяти.

Устройство работает следующим образом.

Контролируемое напряжение через делитель 3 поступает на неинвертирующие (+) входы первого 4 и второго 5 устройств сравнения, где оно непрерывно сравнивается с опорными напряжениями, поступающими на инвертирующие (-) входы устройств сра нения от первого 6 и второго 7 источников опорных напряжений. Результаты сравнения в виде логических уровней 1 и О поступают на регистры 8-11 памяти, причем с устройства 4 результаты сравнения поступают на входы первого 8 и второго 9 регистров памяти через элементы блока инверторов 12.

Результаты сравнения со второго устройства 5 сравнения поступают непосредственно на информационные входы третьего 10 и четвертого 11 регистров памяти.

Делитель 3 напряжения предназначен для согласования входных напряжений устройств 4 и 5 с контролируемыми напряжениями .

Устройство 2 защиты служит для защиты входов устройств 4 и 5 при и 1,5 и„, где и„ - номинальная величина контролируемого напряжения.

Генератор 14 выдает управлякицие сигналы на регистры 8-11 памяти, по которым производится их сброс и приведение в исходное состояние для приема новой информации. При этом

сигналы на входы сброса первого 8 и третьего 10 регистров памяти поступают через инвертор блока инверторов 12,

Таким образом, сброс первого 8 и третьего 10 регистров памяти производится в моменты времени о, с е (фиг, 2), а сброс второго 9 и четвертого 11 регистров памяти производится в моменты времени 6 , d, f (фиг. 2), т.е., сигналы сброса поступают на регистры 10-11 памяти с частотой генератора, но со сдви1

гом на период Т

2 F

где

дар

i

цикл измерения устройства.

Если входное напряжение меньше заданных уровней 1j и 2j (точки 15 - 18 на фиг. 2), то на выходах 1j и

напряжения, делитель напряжения, причем вход устройства загциты соединен с выходом делителя напряжения и неинвертирующими входами первого и второго устройств сравнения, инвертирующие входы которых соединены с выходами первого и второго источников опорного напряжения, а входы делителя напряжения являются входами многоуровневого анализатора-регистратора, отличающийся тем, что, с целью повышения достоверности контроля, в него введены четыре регистра памяти, блок инверторов, содержащий (2п+1) элемента, блок двухвходовых злементов ИЛИ, содержащий (n+m) элементов и генератор, ВЕлход которого соединен с (n+m+1)-входом регистрирующего уст2J устройства 4 сравнения появляются 20 ройства, где п - число вькодов персигналы, которые поступают на входы 1J и 2J третьего 10 и четвертого 11 регистров, а с их выходов через элементы ИЛИ блока двухвходовых элементов ИЛИ 13 на входы 1j и 2j регистрирующего устройства 1, где уровни записи меняются из 1 в О. Информация о провалах напряжения в точках 15 и 16 хранения в третьем 10 и четвертом 11 регистрах памяти до момента сброса (фиг. 2).

Таким образом, время, в течение которого информация хранения в регистрах 8-11 памяти, находится в пределах (Тц + 2Тц,),

Применение двух регистров памяти первого 8 и второго 9 или третьего 10 и четвертого 11 позволяет внести регистрацию помех в каждом цикле времени Т.

При входных напряжениях, больших заданных уровней 1i и 21 (точки 19 - 22 на фиг. 2), предлагаемое устройство работает аналогично вышеописанному случаю для уровней 1j и 2j,

Формула изобретения

вого источника опорного напряжения, m - число выходов второго источника опорного напряжения и с входами сброса второго и четвертого регистров памяти, а также через один из (2п+1) элементов блока инверторов с входами сброса первого и третьего регистров памяти, информационные входы первого регистра памяти объединены с одноименными информационными входами второго регистра памяти и через п инверторов блока инверторов подключены к выходам первого устройства сравнения, одноименные информационные входы третьего и четвертого регистров памяти объединены и подключены к выходам второго устройства сравнения, выходы первого регистра памяти соединены с первыми входами п элементов ИЛИ блока двухвходовых элементов ИЛИ, к вторым входам которых подключены одноименные выходы второго регистра памяти, а выходы вьшеуказанных злементов 45 ИЛИ через п инверторов блока инверторов подключены к п входам регистрирующего устройства, m входов пос- ледного подключены к выходам m элементов ИЛИ блока двухвходовых элеменМногоуровневый анализатор-регистратор напряжения источника постоянного тока, содержащий регистрирующее50 тов ИЛИ, первые входы которых соеди- устройство, устройство защиты, пер-нены с выходами третьего регистра вое и второе устройства сравнения,памяти, а вторые - с одноименными первый и второй источники опорноговыходами четвертого регистра памяти.

5 О15

напряжения, делитель напряжения, причем вход устройства загциты соединен с выходом делителя напряжения и неинвертирующими входами первого и второго устройств сравнения, инвертирующие входы которых соединены с выходами первого и второго источников опорного напряжения, а входы делителя напряжения являются входами многоуровневого анализатора-регистратора, отличающийся тем, что, с целью повышения достоверности контроля, в него введены четыре регистра памяти, блок инверторов, содержащий (2п+1) элемента, блок двухвходовых злементов ИЛИ, содержащий (n+m) элементов и генератор, ВЕлход которого соединен с (n+m+1)-входом регистрирующего уст5

0

вого источника опорного напряжения, m - число выходов второго источника опорного напряжения и с входами сброса второго и четвертого регистров памяти, а также через один из (2п+1) элементов блока инверторов с входами сброса первого и третьего регистров памяти, информационные входы первого регистра памяти объединены с одноименными информационными входами второго регистра памяти и через п инверторов блока инверторов подключены к выходам первого устройства сравнения, одноименные информационные входы третьего и четвертого регистров памяти объединены и подключены к выходам второго устройства сравнения, выходы первого регистра памяти соединены с первыми входами п элементов ИЛИ блока двухвходовых элементов ИЛИ, к вторым входам которых подключены одноименные выходы второго регистра памяти, а выходы вьшеуказанных злементов 5 ИЛИ через п инверторов блока инверторов подключены к п входам регистрирующего устройства, m входов пос- ледного подключены к выходам m элементов ИЛИ блока двухвходовых элемен5

0

0 тов ИЛИ, первые входы которых соеди- нены с выходами третьего регистра памяти, а вторые - с одноименными выходами четвертого регистра памяти.

Чо Ч Sv, Чя 4vi / V Д /р I

i

J

Д..

Составитель И. Мостовый Редактор А. Ревин Техред В.Кадар Корректор И. Эрдейи

Заказ 7894/40 Тираж 73) , Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб.,д.4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Сч) v. . «S -1 -Tj

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОУРОВНЕВЫЙ АНАЛИЗАТОР-РЕГИСТРАТОР НАПРЯЖЕНИЯ ИСТОЧНИКА ПОСТОЯННОГО ТОКА | 1991 |

|

RU2046357C1 |

| Устройство для умножения элементов конечного поля GF(2 @ ) при м @ 3 | 1990 |

|

SU1728858A1 |

| Устройство для управления группой из @ объединенных по выходу тиристорных преобразователей | 1986 |

|

SU1394376A1 |

| Устройство для измерения периодов следования импульсов при контроле перемещения магнитного носителя | 1989 |

|

SU1647644A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| Телеметрическая система со сжатием информации | 1989 |

|

SU1672502A1 |

| МОДУЛЯТОР ДИСКРЕТНОГО СИГНАЛА ПО ВРЕМЕННОМУ ПОЛОЖЕНИЮ | 2018 |

|

RU2677358C1 |

Изобретение относится к контрольно-измерительным устройствам систем управления и может быть использовано в телеметрических контролирующих системах автоматики. Цель изобретения - повышение достоверности контроля. Анализатор-регистратор содержит регистрирующее устройство 1, устройство 2 защиты, делитель 3 напряжения, устройства 4 и 5 сравнения и счетчики 6 и 7 опорного напряжения. Использование двух регистров 8, 9 или 10, 11 памяти позволяет внести регистрацию помех в каждом цикле времени измерения устройства, Кроме того, в устройство введены блок 12 инверторов, содержащий 2п+1 элементов, блок 13 двухвходовых элементов ИЛИ, содержащий п + m элементов и генератор 14.2 ил. (С ipuff.f

| Устройство допускового контроля постоянного напряжения | 1979 |

|

SU789825A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многоуровневый анализатор выбросов и провалов напряжения | 1976 |

|

SU591781A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-02-15—Публикация

1985-09-11—Подача