11

Изобретение относится к преобразовательной технике и предназначается для организации системы электроснабжения разнотипных массовых потребителей (например, цехов и заводов) на частотах, как правило, отличающихся от общепромышленной с применением тиристорных преобразователей.

Цель изобретения - уменьшение установленной мощности силового оборудования и повьш1ениё энергетических характеристик системы электроснабжения, состоящей из п преобразователей подключенных к общей выходной сети.

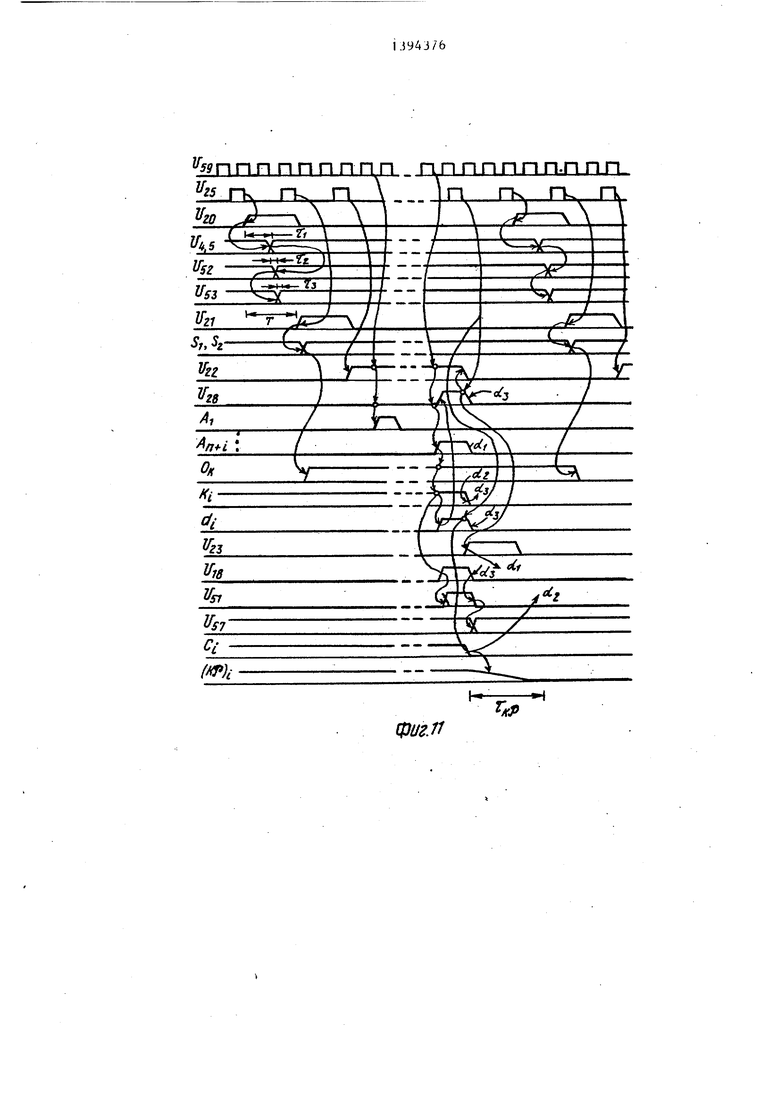

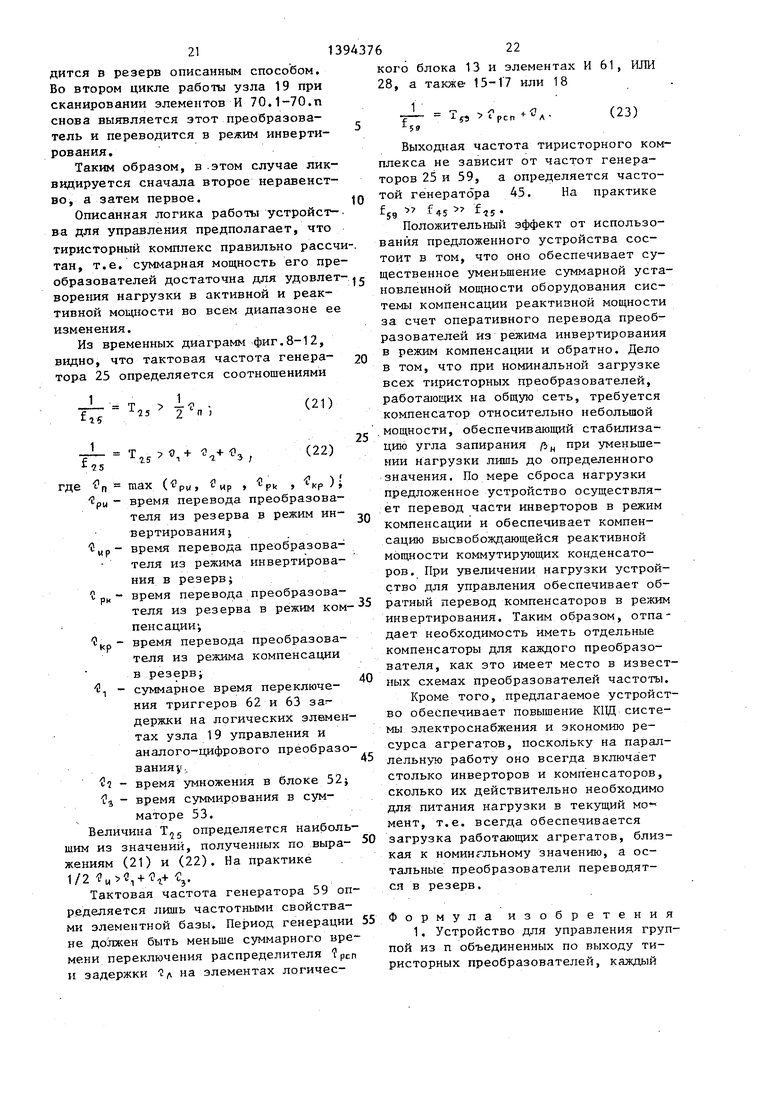

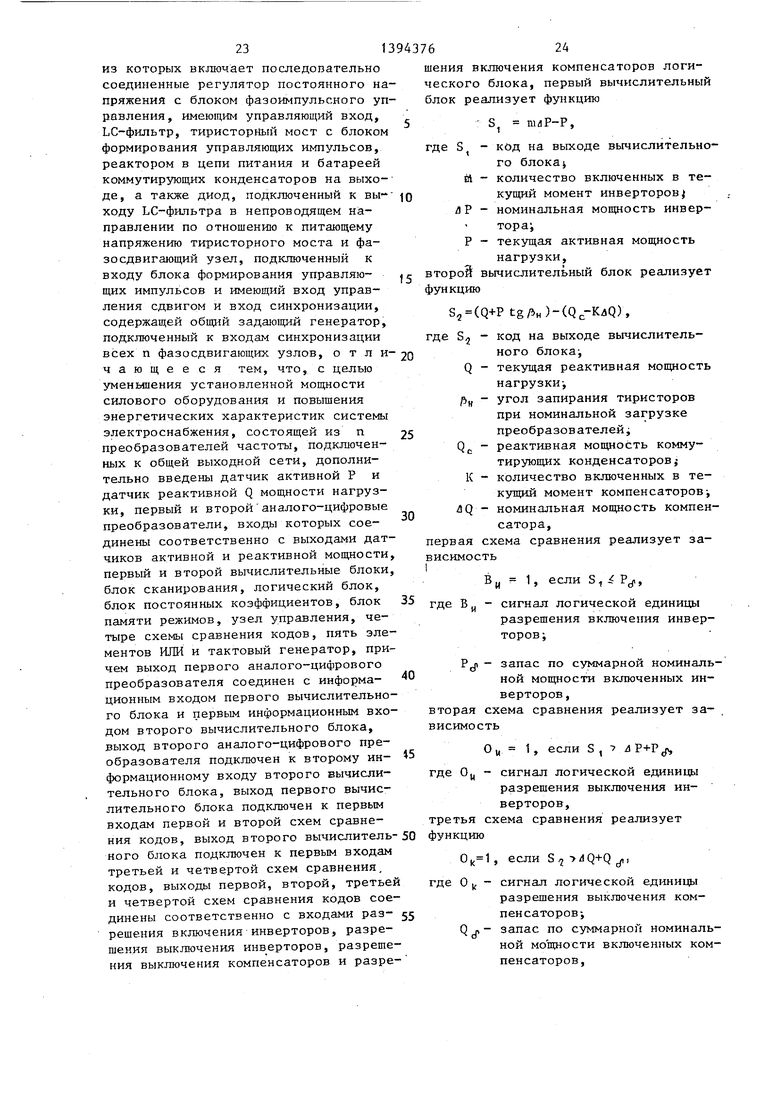

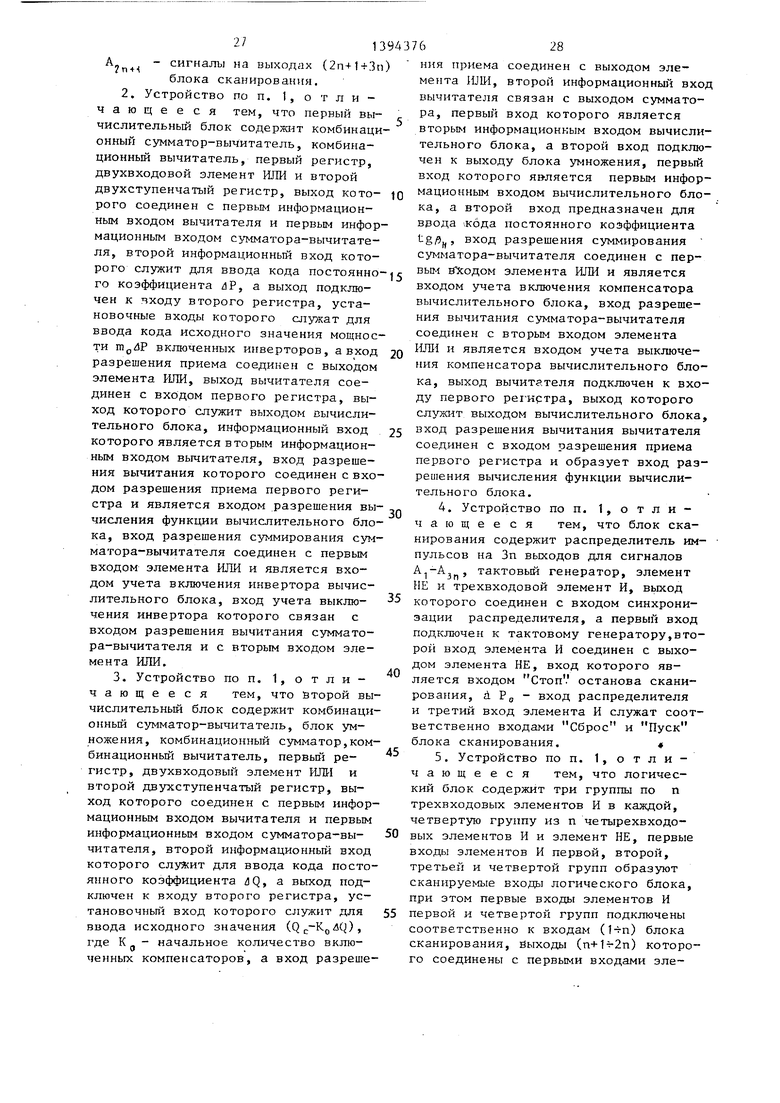

На фиг.1 представлена функциональная схема устройства для управления совместно с группой тиристорных пре- образователеЙ на фиг.2 - схема группы тиристорных преобразователей час- TOTbij на фиг.З - первый и второй вычислительные блоки-, на фиг.4 - блок сканирования и узел управления) на фиг.5 - логический блок} на фиг.6 - блок памяти режимовJ на фиг.7 - алгоритм работы устройства для управления-, на фиг.8 - временная диаграмма узла управления; на фиг.9 - временная диаграмма перевода преобразователя из резерва в режим инвертирования , на фиг.10 - временная диаграмма перевода преобразователя из режи- ма инйертирования в резерв на фиг.11 временная диаграмма перевода преобразователя из режима компенсации в резерву на фиг.12 - временная диаграмм перевода преобразователя из резерва в режим компенсации.

Устройство содержит датчики 1 и 2 соответственно.активной Р и реактивной Q мощностей нагрузки, подключенные к выходной сети группы тиристор ных преобразователей 3j аналого-цифрвые преобразователи 4 и 5, входы которых соединены с выходами соответственно датчиков 1 и 2. Выход аналого- цифрового преобразователя 4 подключен к информационному входу вычислительного блока 6 и первому информационному входу вычислительного блока 7, второй информационный вход которого соединен с выходом аналого-цифрового преобразователя 5. Выход вычислительного блока 6 связан с первыми входами схем 8 и 9 сравнения, а выход вычислительного блока 7 подключен к первым входам схем 10 и 11 сравнения. Блок 12 постоянных коэффициентов выходом для постоянного ко

0

5

5

Q 35

эффициента /Р (номинальная мощность инвертора) подключен к входу ввода кода постоянного коэффициента вычислительного блока 6, а выходами для постоянных коэффициентов 4Q (номинальная мощность компенсатора) и tg/i (тангенс угла запирания тиристоров) - к соответствующим входам ввода кодов постоянных коэффициентов вычислительного блока 7. Вторые входы схем 8-11 сравнения служат для ввода кодов постоянных коэффициентов соответственно Р,, (ЛР+Рр), (/JQ+Q ,) и Qg, и подключены к соответствукщим выходам блока 12 (Р, и запасы по суммарной номинальной мощности включенных инверторов и компенсато- ров соответственно).

Выходы схем сравнения 8-11 подключены соответственно к входам разрешения включения инверторов, разрешения выключения инверторов, разрешения выключения компенсаторов и разрешения включения компенсаторов логического блока. 13. Логический блок 13 четырьмя п-разрядными шинами, служащими для передачи сигналов (a,-Va), (b, f b), () и () приказов на изменение режимов работы тиристорных преобразователей, подключен к входам записи блока 14 памяти режимов. Кроме того, шина, передающая сигналы на включение инверторов через пвходовый элемент ИЛИ 15, соединена с входом учета включения инвертора вычислительного блока 6, шина, передающая сигналы , на отключение инверторов через п-входовый элемент ИЛИ 16, соединена с входом учета отключения инвертора вычислительного блока 6, шина, передающая сигналы приказов на включение компенсаторов через п-входовьй элемент ИШ1 17, подключена к входу учета включения компенсатора вычислительного блока 7, а шина, служащая для передачи сигналов приказов на отключение компенсаторов через п-входовый элемент ИЛИ 18, соединена с выходом учета отключения компенсатора вычислительного блока 7.

Блок 14 памяти режимов работы тиристорных преобразователей тремя п- разрядными шинами, служащими для пе- 55 редачи сигналов (), (),

() идентификации режимов рабо.ты тиристорных преобразователей, связан с осведомительными входами логичес0

40

45

50

Koi o блока 13. Упр авлякяцис Hbixci i блока 14 для сигналов (15,гВ„) н (С,- С) связаны соответственно с пходами управления включением-Быключением ин- . верторов и включения-выключения ком- пенсаторов группы 3 тиристорных преобразователей.

Узел 19 управления выходом 20 для первого управляющего сигнала соеди- IQ нен с входами Пуск аналого-цифровых преобразователей 4 и 5, а выходом 21 для второго управляющего сигнала - с входами разрешения вычисления функций S и S вычислительных блоков 6 и 7. i

Выходы 22 и 23 узла управления служат для передачи третьего и четвертого управляющих сигналов и подключены соответственно к входам Пуск и Сброс блока 24 сканирования. 20

Тактовый генератор 25 соединен с входами синхронизации записи блока 14 памяти режимов и входом синхронизации узла 19 управления, входы 26 и 27 которого являются соответственно 25 входами включения и сброса устройства для управления,

Выходы блока 24 сканирования подключены к сканируемым входам логического блока 13. Выходы элементов И 15- 18 и последний выход блока 24 сканирования через элемент ИЛИ 28 соединены с входом Стоп остановки сканирования блока 24 и входом разрешения выработки четвертого управляющего сигнала узла 19 управления. 5

Блок 14 памяти режимов имеет входы 29 для ручной установки режимов работы тиристорных преобразователей. Входы 30 и 31 вычислительных блоков 6 и 7 служат для ввода кодов Шр РцСр- -KpdQ) соответственно (Шо, К. о чальное количество включенных инверторов и компенсаторов соответственно, QC - реактивная мощность коммутирующих конденсаторов).

Группа тиристорных преобразователей 3 (фиг. 2) представляет собой п объединенных по выходу тиристорных .преобразователей 32, каждый из которых включает последовательно соеди- ненные регулятор 33 постоянного напряжения с блоком 34 фазоимпульсного управления, имеющим управляющий вход 35, LC-фильтр 36, тиристорный. мост 37 с блоком 38 формирования управляю-55 щих импульсов, реактором 39 в цепи питания и батареей 40 коммутирующих конденсаторов на выходе, а также диод

45

Q

0

5

5

5

41, иодклк чеиный к пыходу ЬО-фильтра 36 в ненгмшодящс м направлении по от- ношеник) к напряжению питания тирис- торного моста 37, и фазосдвигающий узел 42, подключенный к входу блока 38 формирования управляющих импульсов и и eющий 43 управления сдвигом и вход 44 синхронизации. Входы синхронизации всех узлов 42 подключены к выходу задающего генератора 45.

Вычислительный блок 6 вычисляет значение функции

S, гп и Р - Р,

где S, - код на выходе блока 6;

пг - количество включенных в текущий момент инверторов Р - номинальная мощность инвертораР - текущая активная мощность

нагрузки.

Для вычисления указанной функции вычислительный блок 6 содержит (фиг.3) комбинационный сумматор-вычитатель 46, комбинационный вычитатель 47, регистр 48, двухвходовый элемент ИЛИ 49 и двухступенчатый регистр 50. Выход регистра 50 соединен с первым информационным входом вычитателя 47 и первым информационным входом сумма- тора-вычитателя 46, второй информационный вход которого является входом ввода в вычислительный блок 6 кода постоянного коэффициента Р из блока 12 постоянных коэффициентов, а выход подключен к входу регистра 50, установочный вход 30 которого служит для ввода в вычислительный блок 6 кода исходного значения мощности включенных инверторов, а вход разрешения приема соединен с выходом элемента ИЛИ-49. Выход вычитателя 47 соединен с выходом регистра 48, выход которого является выходом вычислительного блока 6, информационный вход которого вторым информационным входом вычитателя 47. Вход разрешения приема регистра 48 и вход разрешения вычитания вычитателя 47 объединены и образуют вход разрешения вычисления функции вычислительного блока 6. Вход разрешения сумми- рования сумматора-вычитателя 46 соединен с первым входом элемента ИЛИ 49 и служит входом учета включения инвертора (перевода тиристорного преобразователя в инверторный режим)

вычислительного блока 6. Вход разрешения вычитания сумматора-вычитателя 46 и второй вход элемента ИЛИ 49 объединены и образуют вход учета выключения инвертора (перевода преобразователя в резерв) вычислительного блока 6.

Вычислительный блок 7 вычисляет значения функции

Sj (Q+P tg/iH)-(),.

где S код на выходе вычислительного блока-, Q текущая реактивная мощность нагрузкиi

р„ - угол запирания тиристоров при номинальной загрузке преобразов ателя ; Q. - реактивная мощность комму-

тирующих конденсаторовJ К - количество включенных в текущий момент компенсаторов; aQ - номинальная мощность компенсатора. Для вычисления указанной функции блок 7 содержит (фиг.З) комбинационный сумматор-вычитатель 51, блок 52 умножения, комбинационный сумматор 53, комбинационный вычитатель 54, регистр 55, двухвходовый элемент ИЛИ 56 и двухступенчатый регистр 57.Первый информационный вход вычитателя 54 соединен с выходом регистра 57 и первым информационным входом сумматора-вычитателя 5 1 , второй информаци- онньм вход которого предназначен для ввода кода постоянного коэффициента dQ. Выход сумматора-вычитателя 51 подключен к входу регистра 57, уста- новочньй вход которого является вхо- дом 31 блока 7 для ввода кода исходного значения (), а вход разрешения приема соединен с выходом элемента ИЛИ 56. Второй информационный вход вычитателя 54 подключен к выходу сумматора 53, первый вход которого является вторым информационны входом вычислительного блока 7, а второй вход соединен с выходом блока 52 умножения, первый вход которого является первым информационным входо вычислительного блока 7, а второй вход служит для ввода кода постоянного коэффициента tg|b. Вход разрешени суммирования сумматора-пычитателя 51 соединен с первым входом элемента ИЛ 56 и является входом учета включения компенсатора вычислительного блока 7

Вход разрешения вычитания сумматора- вычитателя 49 соединен с вторым.входом элемента ИЛИ 56 и является входом учета выключения компенсатора вычислительного блока 7. Выход вычитателя 54 подключен к входу регистра 55, выход которого служит выходом вычислительного блока 7. Вход разрешения вычитания вычитателя 54 является входом разрешения вычисления функции вычис- лительного блока 7 и соединен с входом разрешения приема регистра 55.

Блок 24 сканирования (фиг.4) содержит распределитель 58 импульсов на Зп выходов для сигналов А,-А. , выход которого соединен с входом синхронизации распределителя 58, а первый вход подключен к тактовому генератору 59. Второй вход элемента И 61 соединен с выходом элемента НЕ 60, вход которого является входом Стоп останова сканирования, а Ец-вход распределителя 58 и третий вход элемента И 61 служат соответственно входами Сброс и Пуск блока 24 ,скани- ров ания.

Узел 19 управления содержит (фиг. 4) двухступенчатые RS-тригге- ры 62 и 63 .и двухвходовые элементы И 64-69. Входы RO триггеров 62 и 63 объединены и образуют вход 27 Сброс узла 19 управления. Прямой выход триггера 62 подключен к первым входам элементов И 64 и 65, а инверсньш выход - к первым входам элементов И 66 и 67. Прямой выход триггера 63 соединен с вторыми входами элементов И 65 и 66, а инверсный - с вторыми входами элементов И 64 и 67. Выход элемента И 66 подключен к S-входу триггера 62 и является выходом 20 узла 19 управления. Выход элемента И 65 соединен с R-входом триггера 63 и является выходом 21 узла 19 управления. Выход элемента И 64 соединен с первым входом элемента И 68 и является выходом 22 узла 19 управления. Выход элемента И 67 является выходом 23 узла 1 9 и подключен к первому входу элемента И 69, выход которого соединен с S-входом триггера 63. Вход R триггера 62 соединен с выходом элемента И 68, второй вход которого является входом разрешения выработки управляющего сигнала на выходе 23 узла 19. Второй вход элемента И 69 является входом 26 включения устройства для управления, а С-иходы TpHi reров 62 и 63 объединены и образуют вход синхронизации узла 19.

Логический блок 13 вычисляет значение логических функций:

а,р / В„лА, (); Л .Л В„, (); , ЛО.ЛА, , (); g.U,0 ,,, ().

где a- - сигнал приказа на включение

i-ro инвертора; b - сигнал приказа на включение .с

i-ro компенсатора-, d J - сигнал приказа на выключение

i-ro компенсатора g. - сигнал приказа на выключение

i-ro инвертора-,20

pj ,К,и-.-сигналы идентификации состо - яния тиристорных преобразователей:

при Pi 1 i-й преобразователь находится в резерве 95 при К. 1 Ч-й преобразователь - в режиме компенсации при i-й преобразователь находится в режиме инвертирования;..- А , - сигналы на первых п выходах

блока сканирования 24, А,, - сигналы на вторых п выходах

блока 24, А - сигналы на третьих п выходах.

блока 24.35

Логический блок 13 содержит (фиг.5) группу элементов ЗИ 70.1-70,п, группу элементов ЗИ 71.1-71.п, группу элементов ЗИ 72.1-72.П, группу элементов 4И 73.1-73.п и элемент НЕ 74. Первые входы элементов. ЗИ 70.1-70.п и элементов 4И 73.1-73.п подключены соответственно к первым п выходам блока 24 сканирования, вторые п выходов которого соединены соответственно с пер- 5 выми входами элементов ЗИ 71.1-71.п, а третьи п выходов - с первыми входами элементов ЗИ 72.1-72.п. Вторые входы элементов ЗИ 70.1-70.п и элементов 4И 73.1-73.п связаны соответ- 50 ственно с выходами для сигналов /, - Фиблока 14 памяти режимов, выходы которого для сигналов (К,-Кр) и ( ,) подключены соответственно к вторым входам элементов ЗИ 71.1-71.п 55 и 72.1-72.п. Третьи входы элементов ЗИ 70. 1-70.п, 71.1-.71.П, 72.1-72.П и элементов 4И 73.1-73.П являются

40

0

с

0

5 .-

5

5 0 5

0

соответственно входами разрешения включения инверторов, выключения компенсаторов, выключения инверторов и включения компенсаторов блока 13 и подключены соответственно к выходам схем 8-11 сравнения, при этом третьи входы элементов ЗИ 70.1-70.п через элемент НЕ 74 соединены с четвертыми входами элементов 4И 73.1-73.п. Выходы элементов ЗИ 70.1-70.П, 71.1- 1.п, 72.1-72.п и элементов 4И 73.1- 73.П являются выходами логического блока 13 соответственно для сигналов . n,-u; , d,Td, g,fg и , на включение инверторов, выключе.ние компенсаторов, выключение инверторов и включение компенсаторов.

Блок 14 памяти режимов (фиг.6) содержит два регистра 75.1-75.п и 76.1- 76.п на синхронизируемых двухступенчатых RS-триггерах и п двухвходовых элементов И 77.1-77.п. S-и R-входы триггеров 75.1-75.п и 76.1-76.п образуют входы записи блока 14, при этом S-входы триггеров 75.1-75.п и 76.1 - 76.п подключены к выходам логического блока 13 соответственно для сигналов (n,fa) и (di-f-d), а R-входы триггеров 75.1-75.п и 76.1-76.п соединены с выходами логического блока 13 соответственно для сигналов ( и (). Прямые выходы триггеров 75.1-75.П являются выходами блока 14 для сигналов В,-Б управления включением-выключением инверторов и одновременно служат выходами блока 14, на которых образуются сигналы и.,-и идентификации тиристорных преобразователей, работающих в режиме инвертирования. Инверсные выходы триггеров 76.1-76.п образуют выходы блока 14, служащие для выдачи сигналов С,-Сп включения-выключения компенсаторов и одновременно являются выходами блока 14 памяти режимов для сигналов идентификации преобразователей, работающих в режиме компенсации. Инверсные выходы триггеров 75.1-75.П и прямые выходы триггеров 76.1-76.п подключены к входам соответствующих двухвходовых элементов И 77.1-77.п, выходы которых служат для выдачи сигналов идентификации преобразователей, находящихся в резерве. Установленные входы S,, R триггеров 75.1-75.п и 76.1-76.п об- разуют входы 29 блока 14 и для ручной установки режима работы

тиристорных преобразователей 32.1- 32.п.

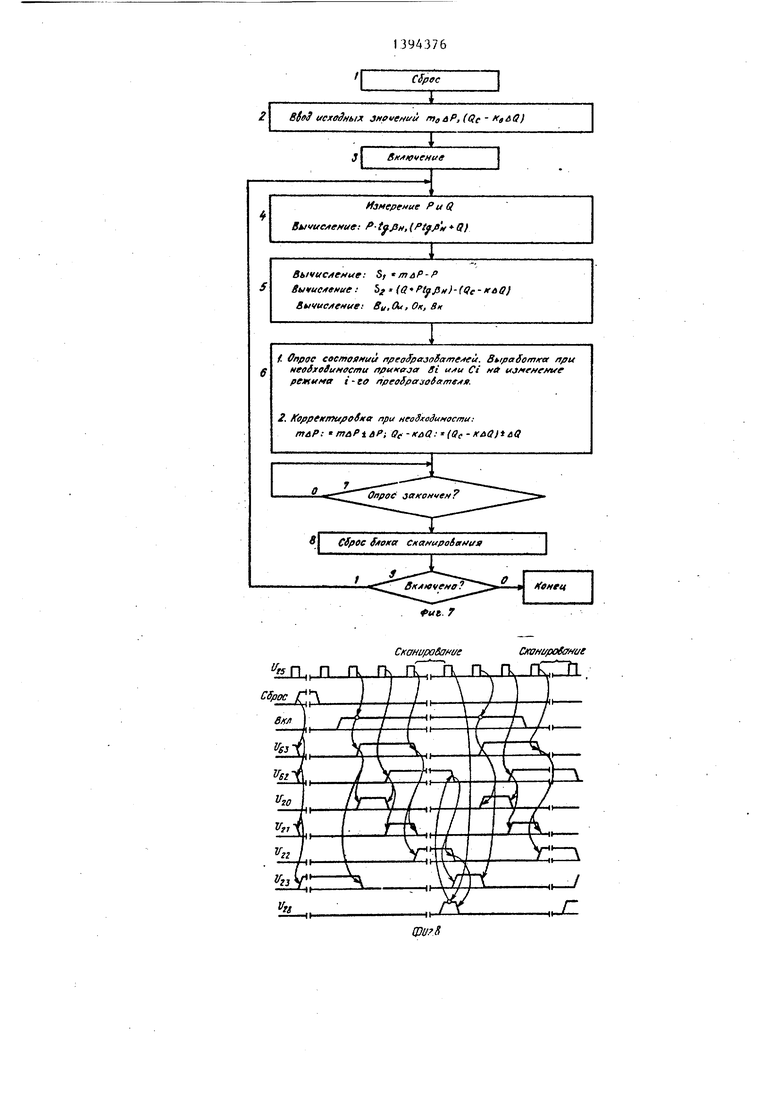

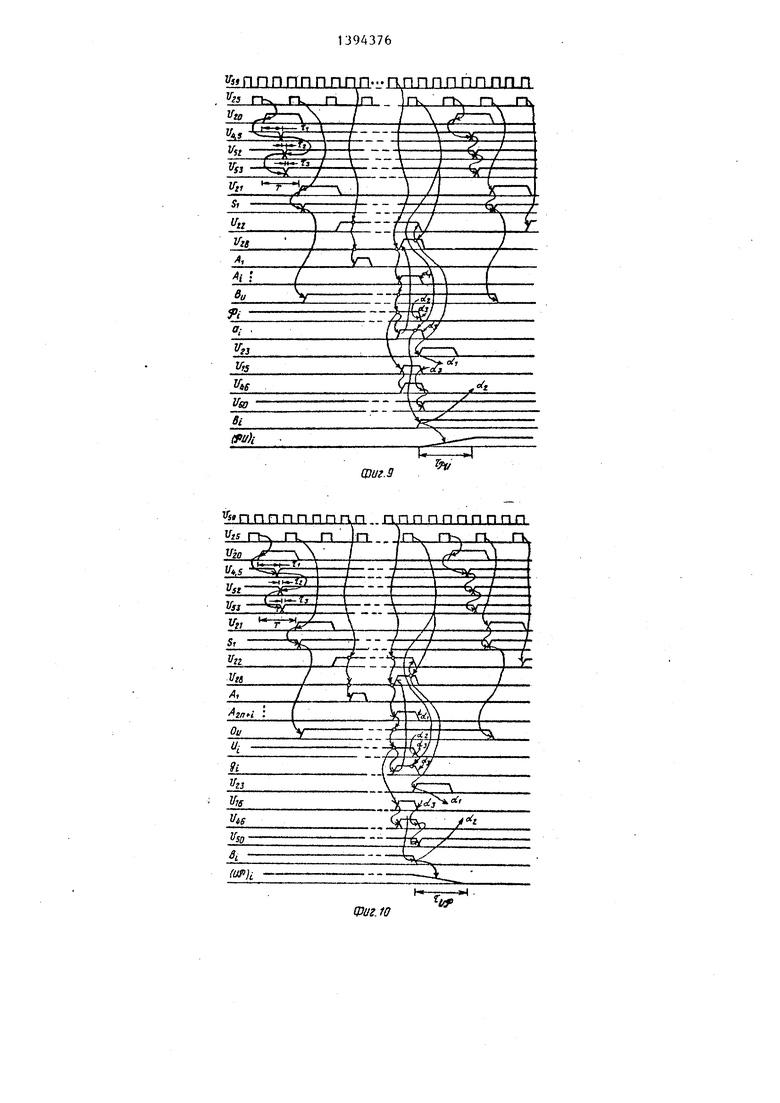

На временных диаграммах принять следующие обозначения:

Ujs сигнал на входе генератора 25;

сигнал на прямом выходе триггера 63

- сигнал на прямом выходе триггера 62j

Ujg - сигнал на выходе 20 узла 19 управления;

Uj - сигнал на выходе 21 узла 19 управления;

Ujj - сигнал на выходе 22 узла 19 управления;

сигнал на выходе 23 узла 19 управленияJ

Ujg - сигнал на выходе элемента ИЛИ 28;

Uyg - сигнал на выходе генератора 59;

и, Uj - процесс изменения кодов на выходах аналого-цифровых преобразователей 4 и 5;

Uy/j - процесс изменения кода на выходе блока умножения 52,

и53 процесс изменения кода на выходе сумматора 53;

S 5, процесс изменения ко.да на

выходе вычислительного блока 6 ;

5 - процесс изменения кода на

выходе вычислительного блока 7;

сигнал на первом выходе распределителя 58 j сигнал на i-ом выходе распределителя 58 (1 1-:-п); сигнал на выходе (n+i) распределителя 58 ();

jn+1 сигнал на выходе (2n+i) распределителя 58 ()j By - сигнал разрешения включения инверторов (разрешения перевода преобразователя из резерва в режим инвертирования) на выходе схемы 8 сравнения; (

Оу - сигнал разрешения выключения инверторов (разрешения перевода преобразователя из режима инвертирования в резерв) на выходе схемы 9 сравнения;

0|, - сигнал разрешения выключения компенсаторов (разрешения перевода преобразователя из

25

А, А. IH-

139437610

режима компенсации в резерв)

на выходе схемы 10 сравнения ;

с k сигнал разрешения включения компенсаторов (разрешения .перевода преобразователя из резерва в режим компенсации) на выходе схемы

10 11 сравнения;

(р| - сигнал на выходе элемента 77.1 (сигнал идентификации преобразователя, находящегося в резерве);

15 сигнал на прямом выходе

триггера 75.1 (сигнал идентификации преобразователя, работающего в режиме инвертирования) ;

20 сигнал на инверсном выходе триггера 76.1 (сигнал идентификации преобразователя, работающего в режиме компенсации) {

сигнал на выходе элемента 70.1 (сигнал приказа на включение 1-го инвертора) сигнал на выходе элемента 73.1 (сигнал приказа на включение 1-го компенсатора) ;

сигнал на выходе элемента 71.1 (сигнал приказа на в ыключение 1-го компенсатора) i

сигнал на выходе 72.1 (сигнал приказа на выключение 1-го инвертора)J сигнал на выходе элемента И 15 (сигнал разрешения суммирования сумматором-вычита- телем 46); сигнал на выходе элемента И

16(сигнал разрешения вычитания сумматором-вычитате- лем 46);

сигнал на вьгходе элемента И

17(сигнал разрешения суммирования сумматором-вычитате- лем 51);

и. - сигнал на выходе элемента И

18(сигнал разрешения вычитания сумматора-вычитате- лем 51);

44 процесс изменения кода на выходе сумматора-вычитате- ля 46

Ujj - процесс записи кода в регистр 50;

30

35

40

45

50

55

CLi b, d. gi

и

15u

и

17

25

CLi b, d. 35

gi

и

15u

и

17

Ц

it

процесс изменения кода на выхода сумматора-вычитателя 51;

Vg-f - процесс записи кода в регистр 57; В, - сигнал на прямом выходе

триггера 75.1 (сигнал включения-выключения i-ro инвертора) )

Cj - сигнал на инверсном выходе триггера 76.1 (сигнал включения-выключения i-ro компенсатора) ;

(9U); - процесс перевода преобразователя 32.1 из резерва в режим инвертирования; (),- - процесс перевода преобразователя 32.1 из режима инвертирования в резерв; (K P)j - процесс перевода преобразователя 32.1 из режима компенсации в резерв;

(РК); - процесс перевода преобразователя 32.1 из резерва в режим компенсации. Работа тиристорного энергетического комплекса происходит следующим образом.

Известно, что КПД вентильного преобразователя (как впрочем и любого электротехнического оборудования) падает с уменьшением нагрузки. При использовании группы тиристорных преобразователей, подключенных к общей выходной сети и обладающих свойством изменять свой режим работы из ин- верторного в компенсационный и обратно, появляется принципиальная возможность обеспечить высокий КПД системы электроснабжения при минимальных затратах силового оборудования. Для этого необходимо все время поддерживать соотношения

тлР Р+Р ; ийР min ,

(1) (2)

где m - количество преобразователей, работающих в генераторном (инверторном) режиме; ЛР - номинальная мощность одного преобразователя, работающего в режиме инвертирования; Р - текущая активная мощность

нагрузки;

Р , - мощность запаса для обеспечения надежности. Выражения (1) и (2) означают, что суммарная мощность преобразователей.

10

5

20

5

0

5

0

5

0

5

переведенных в режим инвертирования, т.е. генерации активной мощности, должна быть минимальной и в то же время достаточной для питания потребителей и создания некоторого запаса PJ, для обеспечения надежности. Следовательно, на параллельную работу должно быть включено ровно столько инверторов, сколько их действительно необходимо для питания нагрузки в Данный момент. Шаг дискретности регулирования по активной мощности равен ЛР при одинаковой величине мощности преобразователей. В этом случае отклонение мощности нагрузки от суммарной мощности включенных инверторов должно находиться в пределах

(тйР-Р) 7 Р. (3)

При (тдР-Р) Р необходимо в ре- жим инвертирования перевести из резерва или режимй компенсации дополнительный преобразователь. Если (тЛР- -Р) лр+Р,, то это означает, что один из инверторов должен быть отключен.

Изменение величины и характера нагрузки приводит также к изменению потребности потребителей в реактивной мощности. При этом реактивная мощность коммутирующих конденсаторов расходуется на покрытие реактивной мощности нагрузки и создание угла запирания/3.

Баланс реактивных мощностей в инверторе тока определяется известным выражением

Q Q+Ptg/5, (4)

где Q с реактивная мощность коммутирующих конденсаторов; Q - реактивная мощность нагрузки; Р - активная мощность нагрузки; Р - угол запирания.

В инверторе с компенсатором выра- .жение (4) записывается в виде

QC Q + Ptg/iK+ Q, (5)

где Q - реактивная мощность, вносимая компенсатором для стабилизации угла запирания; f - номинальный угол запирания, соответствующий номинальной мощности преобразователя. Величина реактивной мощности, вносимой компенсатором, определяется на основании (5) как

QK QC - Q - Р tg р„. (6)

13

Естественно, что компенсатор должен быть рассчитан так, iToObi его номинальная мощность Q,(H была достаточна для покрытия максимально возможной нескомпенсированной нагрузкой реактивной мощности коммутирующих конденсаторов

139437614

Из выражений (12) и (13) видно,, что превьшение суммарной номинальной мощности К liQ включенных компенсаторов над нескомпенсированным нагрузкой значением ( tg/j) мощности коммутирующих конденсаторов должно находиться в пределах

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| Устройство для управления преобразователем частоты | 1988 |

|

SU1629953A1 |

| Параллельный инвертор тока | 1980 |

|

SU904154A1 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2000 |

|

RU2182358C2 |

| Устройство для возбуждения синхронной электрической машины | 1985 |

|

SU1387152A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| СИСТЕМА ЭЛЕКТРОСНАБЖЕНИЯ | 1994 |

|

RU2079960C1 |

| Электромагнитный расходомер | 1987 |

|

SU1578481A1 |

| Устройство для обмена информацией | 1986 |

|

SU1424001A1 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

Изобретение предназначено для организации системы электроснабжения массовых потребителей, например цехов., участков, энергоемкого оборудования, на частотах, отличающихся от общепромьшленной частоты 50 Гц, и регулируемых частотах. Цель изобретения - уменьшение установленной мощности силового оборудования путем исключения звена компенсации реактивной мощности из каждого преобразова- теля и повышение энергетических показателей системы электроснабжения за счет оперативного изменения режимов работы тиристорных преобразователей при изменении нагрузки. Эффект достигается за счет того, что в группу из п параллельно работающих преобразователей частоты дополнительно введены датчик активной и датчик реактивной мощностей нагрузки, два ана- логоцифровых преобразователя, два вычислительных блока, блок сканирования, логический блок, блок памяти режимов, блок постоянных коэффициентов, узел управления и тактовый генератор, соединенные таким образом, что в зависимости от величины и характера нагрузки обеспечивается оперативный перевод необходимого числа преобразователей в один изтрех режимов: инвертирования, компенсации или резерва. 6 з.п. ф-лы, 12 ил. с (Л со со 4;:а СО vj ot

10

(4Q+Qjp).

Из выражений (12) и (13) следует Q+Q(Q+Ptg H)-(Qc-K4Q) Q. (14)

При (Q+P tg/iH)-(Qc+KdQ)74Q+Qji не- ном уровне (/i). Поэтому важно, что- . обходимо отключить один из компенсаQ Qc-(Q+Ptg/5H)M«H- (7)

Компенсаторы выпрямительно-индук- тивного типа, используемые в данном объекте, обеспечивают автоматическую стабилизацию угла запирания на заданбы при изменении нагрузки отдаваемая включенными компенсаторами мощность не превысила их номинального значения. Поскольку в данном объекте изменение суммарной номинальной мощности включенных компенсаторов К/) Q осуществляется дискретно с шагом лQ необходимо поддерживать ее значение на уровне

20

торов, a при (Q+P tgjTj )-() Qj, следует перевести в режим компенсации один из преобразователей, находящихся в резерве или в режиме инвертирования.

Режим работы i-ro преобразователя определяется состоянием пары одноименных триггеров регистров 75 и 76. Режиму инвертирования соответствует состояние U 5, i ., 1, т.е. оба триггера находятся в единичном состоянии. При зтом на управляющий вход блока фазоимпульсного управления 34.1 подан сигнал логической единицы В| -1, а на управляющий вход фазосдвигающего узла 42.1 - сигнал логического нуля С.0, которые вызывают отпирание регулятора 33.1 и устанавливают фазовый сдвиг управляющих импульсов моста 37.1, соответствующий инверторному режиму. Режиму компенсации отвечает состояние U 7j. , /1

К (Q+P );

mm

(8) (9)

К aQ

Выражения (8) и (9) означают, что суммарная номинальная мощность пре- рбразователей, переведенных в режим . компенсации, должна быть минимальной но в то же время достаточной для покрытия избыточной реактивной мощности коммутирующих конденсаторов, т.е. мощности,нескомпенсированной нагрузкой. Следовательно, на параллельную работу должно быть включено ровно столько компенсаторов, сколько их действительно необходимо для компенсации избыточной реактивной мощности коммутирующих конденсаторов.

Выражения (8) и (9) задают диапазон, в котором должна поддерживаться суммарная номинальная мощность ком- пенсаторов с учетом шага дискретности 4 Q

K/5Q7Qc-(Q+P )+Qji; (10)

,-(Q+Ptg/jH), (П)

где Q ,, - некоторый запас мощности включенных компенсаторов

для обеспечения надежности. На основании (10) и (11) получим

(K/sQ-Qc) + (Q+Ptg/iH) Qrf -, 12) (KiQ-Q J + (Q+Ptg /bH).Q- -Qj - (3)

При (Q+P tg/iH)-(Qc+KdQ)74Q+Qji не- обходимо отключить один из компенса

торов, a при (Q+P tgjTj )-() Qj, следует перевести в режим компенсации один из преобразователей, находящихся в резерве или в режиме инвертирования.

Режим работы i-ro преобразователя определяется состоянием пары одноименных триггеров регистров 75 и 76. Режиму инвертирования соответствует состояние U 5, i ., 1, т.е. оба триггера находятся в единичном состоянии. При зтом на управляющий вход блока фазоимпульсного управления 34.1 подан сигнал логической единицы В| -1, а на управляющий вход фазосдвигающего узла 42.1 - сигнал логического нуля С.0, которые вызывают отпирание регулятора 33.1 и устанавливают фазовый сдвиг управляющих импульсов моста 37.1, соответствующий инверторному режиму. Режиму компенсации отвечает состояние U 7j. , /1

ли

74,

Т.е. оба триггера находят

ся в нулевом состоянии, при зтом на управляющий вход 35.1 блока 34.1 фа- зош пульсного управления подается сигнал логического нуля В.0, а на управляющий вход фазосдвигающего узла 42.1 - сигнал логической единицы С 1, что приводит к запиранию регулятора 33.1 и сдвигу импульсов управления тиристорным мостом 37.1 в сторону опережения (по сравнению с ин- верторным режимом) на угол о РН где д} - коэффициент, зависящий от схемы компенсатора и равный 1/2 для трехфазной мостовой схемы. Режиму резерва соответствует состояние 1, т.е. триггер 75.1 находится в нулевом состоянии, а триггер 76.1 - в единичном. При этом на управляющем входе 33.1 блока 34.1 присутствует сигнал В.0, а на управляющем входе 43 i фазосдвигагацего узла 42.1 - сигнал , что вызывает запирание реглятора 33.1 и установление фазового сдвига импульсов управления мостом 37.1, соответствующего инверторному режиму.

Таким образом, режим инвертирования характеризуется тем, что регулятор 33.1 постоянного напряжения откры и на тиристоры моста 37.1 подаются импульсы, вызывающие преобразование постоянного напряжения в переменное частотой f. Для перевода преобразователя в режим резерва производится запирание регулятора 33.1, что приводит к прекращению передачи активной мощности в нагрузку преобразователя 32.1 Импульсы управления на тиристоры моста 37.1 при этом продолжают поступать Перевод преобразователя в режим ком- пенсации осуществляется из режима резерва путем сдвига импульсов управления тиристорным мостом 37.1 на угол „ в сторону опережения по отношению к импульсам управления, подаваемым на тиристорные мосты, работающие в режиме инвертирования или находящиеся в резерве.

Перевод преобразователя 32.1 из режима компенсации в режим инвертиро- вания производится также через промежуточный режим резерва путем сдвига импульсов управления мостом 37.1 в обратную сторону до совмещения по фазе с импульсами управления инверторами и последзпощего отпирания регулято- ра 33.1.

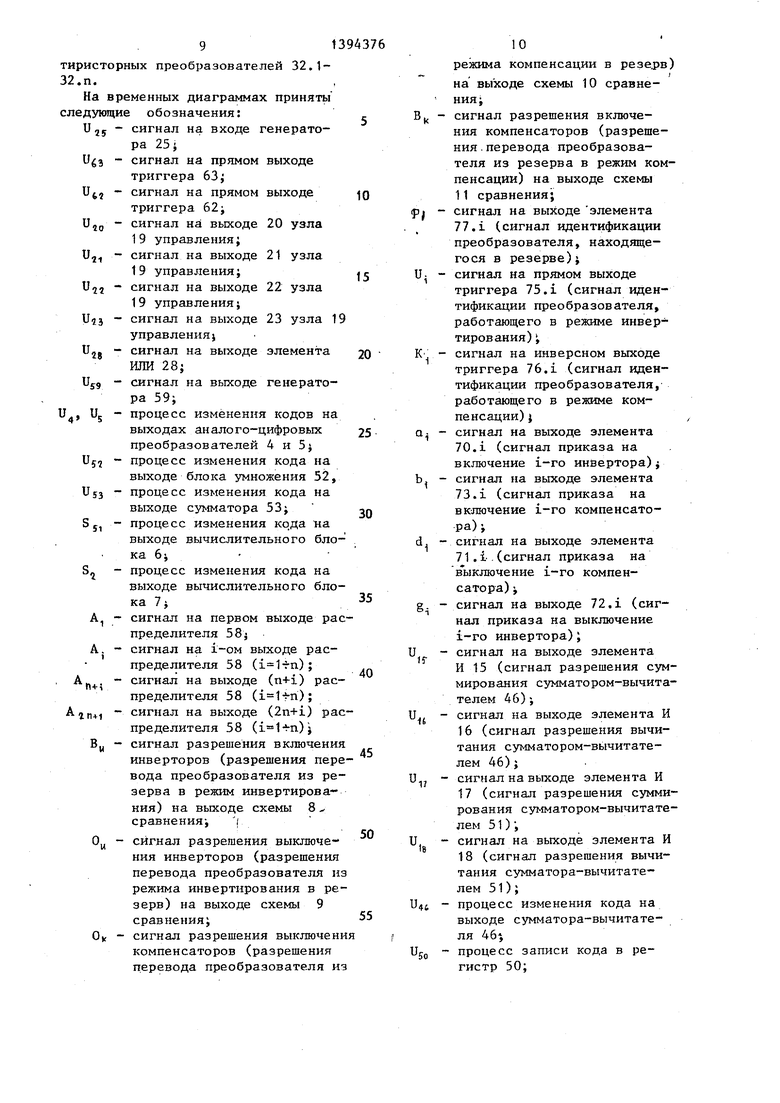

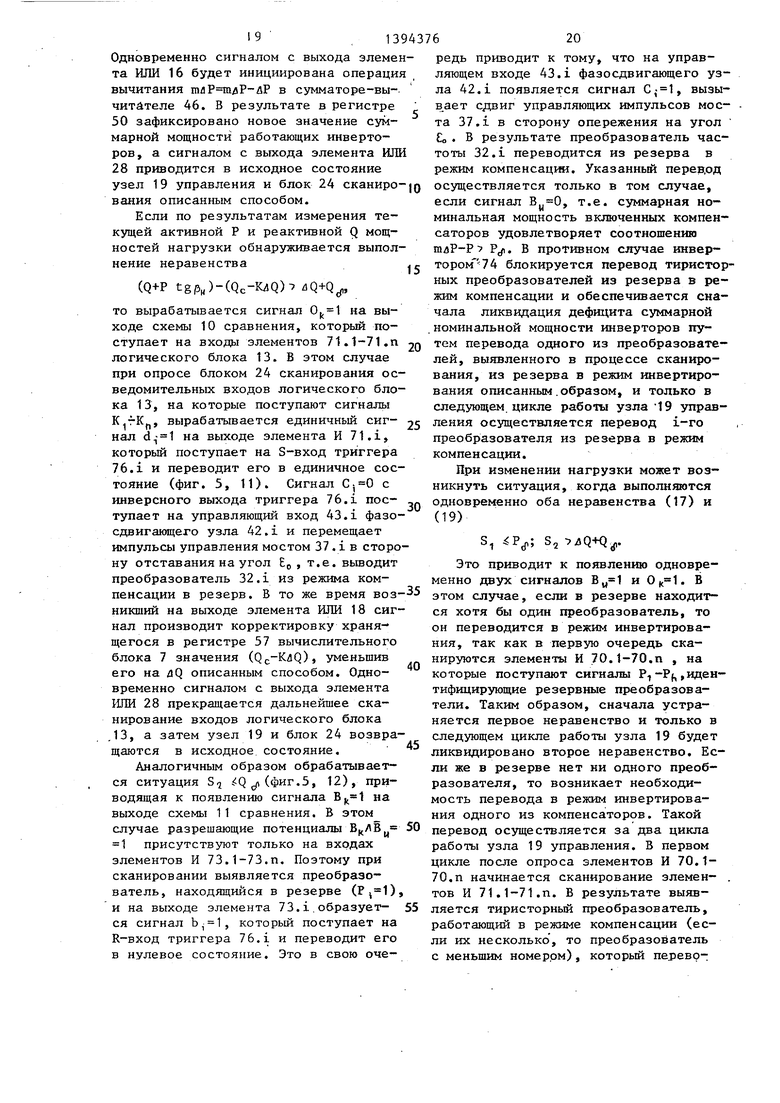

Управление группой тиристорных преобразователей осуществляется согласно алгоритму, представленному на фиг.7. Процедура ввода преобразователей в работу состоит в следующем.

После включения питания устройства для управления по входам 29 блока -14 памяти режимов необходимо устано вить такие состояния триггеров 75.1- 75.п и 76.1-76.п, которые автоматически обеспечат требуемый режим работы каждого преобразователя. При этом количество преобразователей, предназначенных для работы в инвер- торном режиме, количество преобразователей, которым назначается компенсаторный режим, и количество резервных преобразователей определяется ожидаемой величиной и характером на- . В частном случае при включении тиристорного комплекса на холостой ход одному из преобразователей

дг 0 5

5

5

0

5

следует назначить инверторный режим, а остальным установить режим компенсации. В дальнейшем система управления автоматически переведет преобразователи в режим, определяемый нагрузкой. Одновременно по входу 30 в регистр 50 вычислительного блока 6 заносится код исходного значения суммарной мощности ШрЛР преобразователей, предназначенных для работы в ин- варторном режиме, а по входу 31 в регистр 57 вычислительного блока 7 вводится исходное значение мощности (Qj. где Kj, - количество компенсаторов, намеченных к включению в режим компенсации.

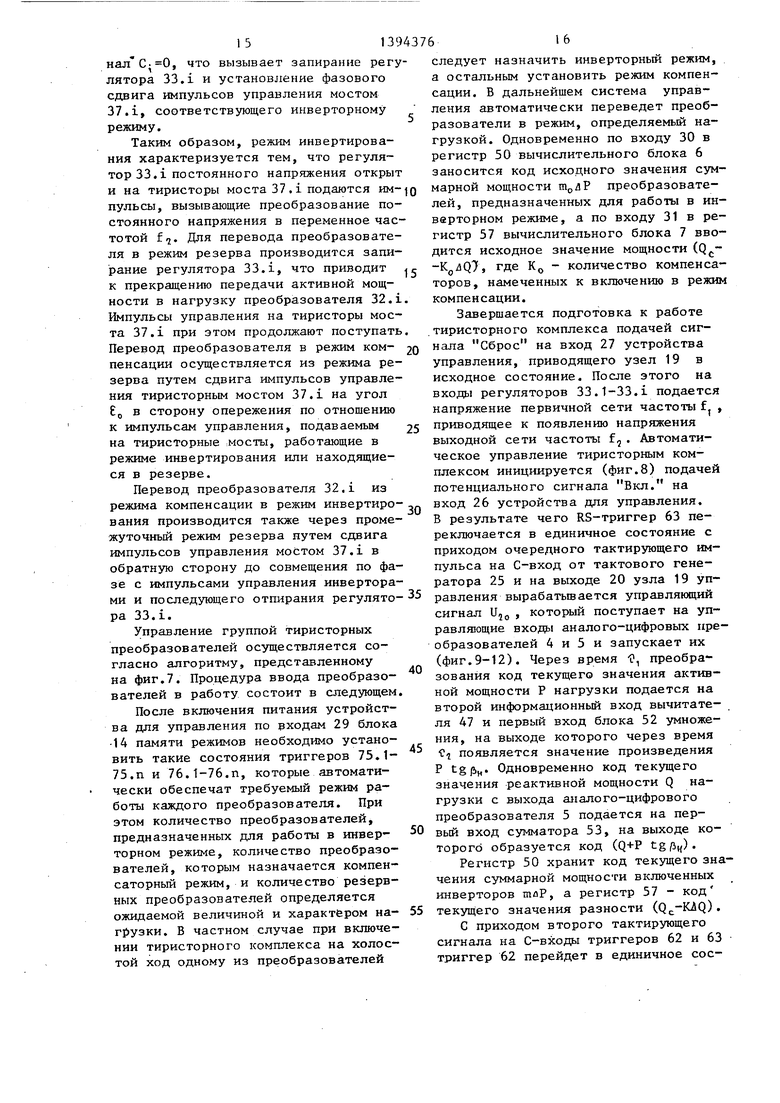

Завершается подготовка к работе .тиристорного комплекса подачей сигнала Сброс на вход 27 устройства управления, приводящего узел 19 в исходное состояние. После этого на входы регуляторов 33.1-33.1 подается напряжение первичной сети частоты f , приводящее к появлению напряжения выходной сети частоты f,. Автоматическое управление тиристорным комплексом инициируется (фиг.8) подачей потенциального сигнала Вкл. на вход 26 устройства для управления. В результате чего RS-триггер 63 переключается в единичное состояние с приходом очередного тактирующего импульса на С-вход от тактового генератора 25 и на выходе 20 узла 19 управления вырабатьшается управляющий сигнал UjQ , который поступает на управляющие входы аналого-цифровых преобразователей 4 и 5 и запускает их (фиг.9-12). Через время 1, преобразования код текущего значения активной мощности Р нагрузки подается на второй информационный вход вычитате- ля 47 и первый вход блока 52 умножения, на выходе которого через время 7 появляется значение произведения Р tg/i. Одновременно код текущего значения реактивной мощности Q нагрузки с выхода аналого-цифрового преобразователя 5 подается на первый вход сумматора 53, на выходе которого образуется код (Q+P tg/i).

Регистр 50 хранит код текущего значения суммарной мощности включенных инверторов тдР, а регистр 57 - код текущего значения разности (Q -ICAQ).

С приходом второго тактирующего сигнала на С-входы триггеров 62 и 63 триггер 62 перейдет в единичное соетояние и выработает сигнал на выходе 21, который поступит на входы разрешения вычитания вычитателей 47 и 54 и входы разрешения приема регистров 48 и 55 соответственно. В результате на выходе регистра 48 устанавливается код функции .

S, га лР - Р, (15)

а на выходе регистра 55 - код функции

S(Q+P tg/5,)-(). (16)

Коды значений S и S поступают на первые входы схем 8-11 сравнения, на выходах которых по результатам сравнения с постоянным коэффициентом -вырабатьшаются сигналы логической единицы соответственно

,при S, (17)

,при S, 7 ЛР+Pji;(18)

,при S, (19)

,при S, Q.(20)

С приходом третьего тактирующего сигнала (фиг. 4 и 7) на С-входы триггеров 62 и 63 триггер 62 переключается в нулевое состояние и на выходе 22 узла 19 сформируется единичный сигнал, который поступает на вход- элемента И 61 и разрешает подачу тактирующих сигналов на С-вход распределителя 58 от тактового генератора 59. Дальнейшая выработка управляющих сигналов узлом 19 приостанавливается (фиг.8-12), так как на втором входе элемента И 68 присутствует сигнал логического нуля, блокирутощий переключение триггера 62. С началом поступления тактирующих сигналов на С-вход распределителя 58 он начинает вырабатывать импульсы А ,-А последовательно на своих Зп выходах. Тем самым вначале просматриваются осведомительные входы логического блока 13, на которые поступают сигналы , идентифицирующие наличие ,и номера преобразователей частоты, находящихся в резерве. Если при этом сигнал Bj,1, то при обнаружении осведомительного входа, на котором присутствует уровень логической единицы р.1, на выходе элемента И 70.1.вырабатывается сигнал Q.1, который поступает на S-вход триггера 75.1 и переводит его в единичное состояние

15

20

25

(фиг. 6, 9). Сигнал с прямого выхода триггера 75.1 поступает на уп- .равляющий вход 35.1 блока 34.1 фазо- импульсного управления и открывает регулятор 33.1 постоянного напряжения. В результате преобразователь 32,1 переводится из резерва в режим инвертирования (фиг.8).

Q Одновременно сигнал с выхода элемента И 70.1 поступает через элемент ИЛИ 15 на вход разрешения суммирования сумматора-вычитателя 46, на вход элемента ИЛИ 49 вычислительного блока 6, а также на вход элемента ИЛИ 28. В результате (фиг. 3, 9) сумма- тором-вычитателем 46 вырабатывается новое, увеличенное на аР, значение мощности включенных инверторов тЛР m/JP+4P и заносится в регистр 50. Сигнал логической единицы с выхода элемента РШИ 28 инвертируется инвертором 60 и блокирует поступление тактирующих сигналов на С-вход распределителя. Тем самым останавливается сканирование, т.е. прекращается дальнейший просмотр режимов преобразователей. Одновременно сигнал логической единицы с выхода элемента ИЛИ 28 поступает на вход элемента И 68, разрешая сброс в нулевое состояние триггера 62. С приходом очередного тактирующего сигнала на С-вход триггера 62 он переключается в нулевое состояние, в результате чего на выходе 23 узла 19 формируется единичный сигнал, который поступает на К(,-вход распределителя 58 и сбрасывает его в исходное состояние.

Начинается новый цикл управления тиристорным комплексом, который протекает аналогично описанному. Если при этом выясняется, что сигнал 0 1, то в процессе сканирования будет выявлен осведомительный вход, содержащей сигнал и.1, идентифицирующий преобразователь, находящийся в режиме инвертирования. В результате на выходе элемента 72.1 появится сигнал , который поступит на R50 вход триггера 75.1 и переведет его в нулевое состояние (фиг. 6, 10). Сигнал В .0 с прямого выхода триггера 75.1 поступит на управляющий вход 35,1 блока фазоимпульсного управле55 .ния 34.1 и закроет регулятор постоянного напряжения 33.1. В результате преобразователь 32.1 перейдет из ре- яо1ма инвертирования в резерв (фиг. 10).

30

35

40

45

Одновременно сигналом с выхода элемента ИЛИ 16 будет инициирована операция вычитания 1плР т/5Р-ДР в сумматоре-вы- читателе 46. В результате в регистре 50 зафиксировано новое значение суммарной мощности работающих инверторов, а сигналом с выхода элемента ИЛИ 28 приводится в исходное состояние узел 19 управления и блок 24 сканирования описанным способом.

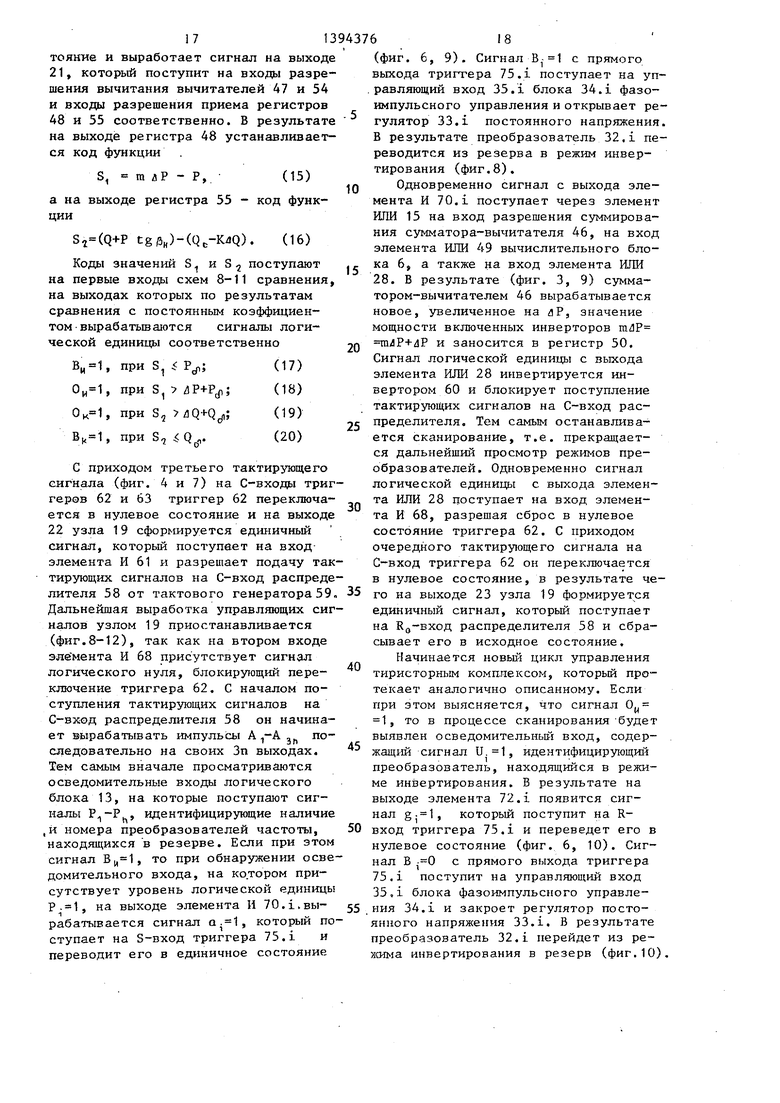

Если по результатам измерения текущей активной Р и реактивной Q мощностей нагрузки обнаруживается выполнение неравенства

(Q+P tgp,)-(Qc-KjQ)-7 dQ+Q,

то вырабатывается сигнал 0, 1 на выходе схемы 10 сравнения, который поступает на входы элементов 71.1-71.п логического блока 13. В этом случае при опросе блоком 24 сканирования осведомительных входов логического блока 13, на которые поступают сигналы , вырабатывается единичный сиг- нал d,- 1 на выходе элемента И 71.1, который поступает на S-вход триггера 76.1 и переводит его в единичное состояние (фиг. 5, 11). Сигнал с инверсного выхода триггера 76.1 поступает на управляющий вход 43.1 фазо сдвигающего узла 42.1 и перемещает импульсы управления мостом 37 .1 в сторону отставания на угол Ед , т.е. вьшодит преобразователь 32.1 из режима компенсации в резерв. В то же время возникший на выходе элемента ИЛИ 18 сигнал производит корректировку хранящегося в регистре 57 вычислительного блока 7 значения (), уменьшив его на /iQ описанным способом. Одновременно сигналом с выхода элемента 1ШИ 28 прекращается дальнейшее сканирование входов логического блока .13, а затем узел 19 и блок 24 возвращаются в исходное состояние.

Аналогичным образом обрабатывается ситуация БЭ Q ,.( (фиг.5, 12), приводящая к появлению сигнала на выходе схемы 11 сравнения. В этом случае разрешающие потенциалы 1 присутствуют только на входах элементов И 73.1-73.п. Поэтому при сканировании выявляется преобразователь, находящийся в резерве (), и на выходе элемента 73.1.образует- ся сигнал , который поступает на R-вход триггера 76.1 и переводит его в нулевое состояние. Это в свою оче-

д

с

о 5 5

0

0

0

редь приводит к тому, что на управляющем входе 43.1 фазосдвигающего узла 42.1 появляется сигнал С,- 1, вызы- сдвиг управляющих импульсов моста 37.1 в сторону опережения на угол Со. В результате преобразователь частоты 32.1 переводится из резерва в режим компенсации. Указанный перев,од осуществляется только в том случае, если сигнал В 0, т.е. суммарная номинальная мощность включенных компенсаторов удовлетворяет соотношению тйР-Р Р. В противном случае инвер- тором 74 блокируется перевод тиристор- ных преобразователей из резерва в режим компенсации и обеспечивается сначала ликвидация дефицита суммарной номинальной мощности инверторов путем перевода одного из преобразователей, выявленного в процессе сканирования, из резерва в режим Ш1вертиро- вания описанным.образом, и только в следующем, цикле работы узла 19 управления осуществляется перевод 1-го преобразователя из резерва в режим компенсации.

При изменении нагрузки может возникнуть ситуация, когда выполняются одновременно оба неравенства (17) и (19)

S S, Q+Qj.

Это приводит к появлению одновременно двух сигналов и . В этом случае, если в резерве находится хотя бы один преобразователь, то он переводится в режим инвертирования, так как в первую очередь сканируются элементы И 70.1-70.п , на которые поступают сигналы (,,идентифицирующие резервные преобразователи. Таким образом, сначала устраняется первое неравенство и только в следующем цикле работы узла 19 будет ликвидировано второе неравенство. Если же в резерве нет ни одного преобразователя, то возникает необходимость перевода в режим инвертирования одного из компенсаторов. Такой перевод осуществляется за два цикла работы узла 19 управления. В первом цикле после опроса элементов И 70.1- 70.п начинается сканирование элемен- . тов И 71.1-71.п. В результате выявляется тиристорный преобразователь, работающий в режиме компенсации (если их несколько, то преобразователь с меньшим номер.ом), который переводится в резерв описанным способом. Во втором цикле работы узла 19 при сканировании элементов И 70.1-70.п снова выявляется этот преобразователь и переводится в режим инверти- рования.

Таким образом, в .этом случае ликвидируется сначала второе неравенство а затем первое.

Описанная логика работы устройства для управления предполагает, что тиристорный комплекс правильно рассч тан, т.е. суммарная мощность его преобразователей достаточна для удовлет ворения нагрузки в активной и реактивной мощности во всем диапазоне ее изменения.

Из временных диаграмм фиг.8-12, видно, что тактовая частота генера- тора 25 определяется соотношениями

-Т 1 25 2

п )

,

(21)

(22)

где t n - max (рм, Сцр , -йр , i kp ) i Срм - время перевода преобразователя из резерва в режим инвертирования j

время перевода преобразователя из режима инвертирования в резерв;

рк

- время перевода преобразова,

теля из резерва в режим ком пенсации;

- время перевода преобразователя из режима компенсации в резерв;

йт - суммарное время переключения триггеров 62 и 63 задержки на логических элементах узла 19 управления и аналого-цифрового преобразования у :.

время умножения в блоке 52; время суммирования в сумматоре 53. Величина Тлч определяется наиболь

шим из значений, полученных по выра- жениям (21) и (22). На Практике

1/2 , ЯТактовая частота генератора 59 определяется лишь частотными свойствами элементной базы. Период генерации не должен быть меньше суммарного времени переключения распределителя llpcn и задержки г л на элементах логичес 1 5

кого блока 13 и элементах И 61, ИЛИ 28, а также 15-17 или 18

i

f5

реп ,

(23)

Q

-, 5

20

25

30

35

40

45

СП

-

55

Выходная частота тиристорного комплекса не зависит от частот генераторов 25 и 59, а определяется частотой генератора 45. На практике

59 T-SПоложительный эффект от использования предложенного устройства состоит в том, что оно обеспечивает существенное уменьшение суммарной установленной мощности оборудования системы компенсации реактивной мощности за счет оперативного перевода преобразователей Из режима инвертирования в режим компенсации и обратно. Дело в том, что при номинальной загрузке всех тиристорных преобразователей, работающих на общую сеть, требуется компенсатор относительно небольшой .мощности, обеспечивающий стабилизацию угла запирания /ь при уменьшении нагрузки лишь до определенного значения. По мере сброса нагрузки предложенное устройство осуществляет перевод части инверторов в режим компенсации и обеспечивает компенсацию высвобождающейся реактивной мощности коммутирующих конденсаторов. При увеличении нагрузки устройство для управления обеспечивает обратный перевод компенсаторов в режим инвертирования. Таким образом, отпадает необходимость иметь отдельные компенсаторы для каждого преобразователя, как это имеет место в известных схемах преобразователей частоты.

Кроме того, предлагаемое устройство обеспечивает повышение К1Щ системы электроснабжения и экономию ресурса агрегатов, поскольку на параллельную работу оно всегда включает столько инверторов и компенсаторов, сколько их действительно необходимо для питания нагрузки в текущий мо- мент, т.е. всегда обеспечивается загрузка работающих агрегатов, близкая к номингльному значению, а остальные преобразователи переводятся в резерв.

Формула изобретения 1. Устройство для управления группой из п объединенных по выходу тиристорных преобразователей, каждый

231

из которых включает последовательно соединенные регулятор постоянного напряжения с блоком фазоимпульсного управления, имеющим управляющий вход, ЬС-фш1ьтр, тиристорньш мост с блоком формирования управляющих импульсов, реактором в цепи питания и батареей коммутирующих конденсаторов на выходе, а также диод, подключенный к выходу LC-фильтра в непроводящем направлении по отношению к питающему напряжению тиристорного моста и фа- 30сдвигающий узел, подключенный к входу блока формирования управляю- щих импульсов и имеющий вход управления сдвигом и вход синхронизации, содержащей общий задающий генератор, подключенный к входам синхронизации всех п фазосдвигающих узлов, о т л и чающееся тем, что, с целью уменьшения установленной мощности силового оборудования и повышения энергетических характеристик системы электроснабжения, состоящей из п преобразователей частоты, подключенных к общей выходной сети, дополнительно введены датчик активной Р и датчик реактивной Q мощности нагрузки, первый и второй аналого-цифровые преобразователи, входы которых соединены соответственно с выходами датчиков активной и реактивной мощности первый и второй вычислительные блоки блок сканирования, логический блок, блок постоянных коэффициентов, блок памяти режимов, узел управления, че

,

тыре схемы сравнения кодов, пять элементов ИЛИ и тактовый генератор, причем выход первого аналого-цифрового преобразователя соединен с информа ционным входом первого вычислительного блока и первым информационным входом второго вычислительного блока, выход второго аналого-цифрового преобразователя подключен к второму информационному входу второго вычислительного блока, выход первого вычислительного блока подключен к первым входам первой и второй схем сравнения кодов, выход второго вычислительного блока подключен к первым входам третьей и четвертой схем сравнения, кодов, выходы первой, второй, третьей и четвертой схем сравнения кодов соединены соответственно с входами раз- решения включения инверторов, разрешения выключения инверторов, разрешения выключения компенсаторов и разре76

24

шения включения компенсаторов логического блока, первый вычислительный блок реализует функцию

- S шлР-Р,

где S - код на выходе вычислительного блокад

и - количество включенных в текущий момент инверторов аР - номинальная мощность инверTopaiР - текущая активная мощность

нагрузки,

второй вычислительный блок реализует функцию

S5(Q+P tgЛн)-(Qc-K4Q),

где Sj - код на выходе вычислительного блока-, Q - текущая реактивная мощность

нагрузки-,

р„ - угол запирания тиристоров при номинальной загрузке преобразователей; QJ, - реактивная мощность коммутирующих конденсаторов; К - количество включенных в текущий момент компенсаторов-, dQ - номинальная мощность компенсатора,

первая схема сравнения реализует зависимость

BH

1, если S, Р,

где Bj, - сигнал логической единицы

разрешения включения инверторов;

40

5055Pd-запас по суммарной номинальной мощности включенных инверторов,

вторая схема сравнения реализует зависимость

0«

1,

если S,

4Р+Р

где Oj - сигнал логической единицы разрешения выключения инверторов,

третья схема сравнения реализует

функцию

0,1, если S 4QH-Q,

где О ,; - сигнал логической едини1ф1 разрешения выключения компенсаторов-,

Q J, - запас по суммарной номинальной мощности включенных компенсаторов.

25

четвертая схема сравнения реализует функцию

В 1, если S, Q

где Вц - сигнал логической единицы разрешения включения компенсаторов J

входы ввода кодов постоянных коэффициентов АР первого вычислительного блока, tg 5„ и uQ второго вычислительного блока подключены к соответствующим выходам блока постоянных коэффициентов, вторые входы первой, второй, третьей и четвертой схем сравнения предназначены для ввода кодов постоянных коэффициентов Рп, (Р+Р, Qjji, (/iQ+Qjt) соответственно и подключены к соответствующим выходам блока постоянных коэффициентов, выходы логического блока четырьмя п- разрядными шинами, служащими для передачи сигналов приказов на изменение режима работы тиристорных преобразователей, подключены к входам записи блока памяти режимов, при этом

10

139437626

образователей, второй выход для второго управляющего сигнала узла управления соединен с входами разрешения вычисления функций вычислительных блоков, третий выход узла управления для третьего управляющего сигнала подключен к входу Пуск блока сканирования а четвертый выход для четвертого управляющего сигнала узла управления соединен с входом Сброс блока сканирования, Зп выходов которого подключены к сканируемым входам логического блока, выход тактового генератора соединен с входом синхронизации узла управления и входом синхронизации записи блока памяти режимов, выходы первого, второго, третьего и четвертого элементов ИЛИ и Зп-й.выход блока сканирования через пятый пяти- входовый элемент ШШ связаны с входом Стоп блока сканирования и входом разрешения выработки четвертого управляющего сигнала узла управления, 25 имеющего входы Сброс и Вкл., служащие для приведения устройства уп15

20

шина приказов на включение инверторо через первый п-входовый элемент ИЛИ соединена с входом учета включения инвертора первого вычислительного блока, шина приказов на отключение инверторов через второй птвходовый элемент ИЛИ соединена с входом учета отключения инвертора первого вычислительного блока, шина приказов на включение компенсаторов через третий п-входовый элемент ИЛИ соединена с входом учета включения компенсатора второго вычислительного блока, шина приказов на отключение компенсаторов через четвертый п-входовьй элемент ШШ соединена с входом учета отключения компенсатора второго вычислительного блока, блок памяти режимов работы тиристорных преобразователей тремя п-разрядными шинами идентификации режимов связан с осведомительными входами логического блока, п выходов управления включением-выключением инверторов блока памяти режимов соединены соответственно с управляющими входами блоков фазоймпуль сного управления, а п выходов управления включением-выключением компенсаторов - соответственно с входами управления фазосдвигающих узлов, пер вый выход для первого управляющего сигнала узла управления подключен к входам запуска аналого-цифровых ппе

30

35

55

равления в исходное состояние и запуска, логический блок реализ функции

а. BM Л А; , (); Ь,,Л Вц/ А; , (); d,K./ 0,ЛА,, , ( Vn) ; О„ЛА,„. , ()j

0

5

b-

g; 5

0

где a. - сигнал приказа на включение i-ro инвертораi сигнал приказа на включение i-ro компенсатораi сигнал приказа на выключение i-ro компенсатора; сигнал приказа на выключение i-ro инвертора}

9-,К,,11.- сигналы идентификации состояний тиристорных преобразователей}

при i-й преобразователь находится в резерве-, при К; 1 i-й преобразователь находится в режиме компенсации;

при i-й преобразователь находится в режиме инвертирования;

сигналы на выходах (l-i-n) блока сканированияi сигналь на выходах () блока сканирования;

А. 2/1394376

- сигналы на выходах ()

блока сканирования. 2. Устройство по п. 1, о т л и мв в ч в м к в с вы в вы ни со 1Ш ни к в с п т

чающееся тем, что первый вы- числительньш блок содержит комбинационный сумматор-вычитатель, комбинационный вычитатель, первый регистр, двухвходовой элемент ШШ и второй двухступенчатый регистр, выход которого соединен с первым информационным входом вычитателя и первым информационным входом сумматора-вычитате- ля, второй информационный вход которого служит для ввода кода постоянно го коэффициента dP, а выход подключен к входу второго регистра, установочные входы которого служат для ввода кода исходного значения мощности тПдйР включенных инверторов, а вход разрешения приема соединен с выходом элемента ИЛИ, выход вычитателя соединен с входом первого регистра, выход которого служит выходом вычислительного блока, информационный вход которого является вторым информационным входом вычитателя, вход разрешения вычитания которого соединен с входом разрешения приема первого регистра и является входом разрешения вычисления функции вычислительного блока, вход разрешения суммирования сум- матора-вычитателя соединен с первым входом элемента ИЛИ и является входом учета включения инвертора вычислительного блока, вход учета выключения инвертора которого связан с входом разрешения вычитания суммато- ра-вычитателя и с вторым входом элемента ИЛИ.

информационным входом сумматора-вы- 50 вых элементов И и элемент НЕ, первые

читателя, второй информационный вход которого служит для ввода кода постоянного коэффициента uQ, а выход подключен к входу второго регистра, ус- тановочньш вход которого служит для ввода исходного значения (Q(,-KQ4Q), где К - начальное количество включенных компенсаторов, а вход разреше28

0

5

0

0

5

0

5

НИН приема соединен с выходом элемента Ш1И, второй информационный вход вычитателя связан с выходом сумматора, первый вход которого является вторым информационным входом вычислительного блока, а второй вход подключен к выходу блока умножения, первый вход которого яв ляется первым информационным входом вычислительного блока, а второй вход предназначен для врода к6да постоянного коэффициента , вход разрешения суммирования сумматора-вычитателя соединен с первым вводом элемента ИЛИ и является входом учета включения компенсатора вычислительного блока, вход разрешения вычитания сумматора-вычитателя соединен с вторым входом элемента 1ШИ и является входом учета выключения компенсатора вычислительного блока, выход вычитателя подключен к входу первого рег истра, выход которого служит выходом вычислительного блока, вход разрешения вычитания вычитателя соединен с входом разрешения приема первого регистра и образует вход разрешения вычисления функции вычислительного блока.

и третий вход элемента И служат соответственно входами Сброс и Пуск блока сканирования.«

0

5

0

5

0

5

0

5

0

5

приказов на отключение компенсаторов, R-входы триггеров второго регистра подключены к выходам логического блока для сигналов приказов на включение компенсаторов, прямые выходь триггеров первого регистра являются выходами для сигналов В,гВ управления включением-выключением инверторов блока памяти режимов и одновременно служат выходами сигналов идентификации работающих инверторов, инверсные выходы триггеров второго регистра являются выходами блока памяти режимов для сигналов управления включением-выключением компенсаторов и одновременно служат выходами сигналов идентификации работающих компенсаторов, прямые выходы триггеров второго регистра и инверсные выходы триггеров первого регистра подключены соответственно к первому и второму входам соответствующих элементов И, выходы .которых являются выходами сигналов идентификации тиристорных преобразователей, находящихся в резерве, установочные входы Sj, и R g триггеров являются входами блока памяти режимов, предназначенными для. ручного задания режима работы тиристорных преобразователей,

t

четвертым управляющим выходом узла управления и подключен к первому входу шестого элемента И, выход которого соединен с S-входом второго триггера, К-вхОд первого триггера соединен с выходом пятого элемента И, вто... г

CSp9C nycK

рой вход которого является входом разрешения выработки четвертого уп- равлякщего сигнала узла управления, а второй вход шестого элемента И является входом включения устройства для управления.

VS

т

Фаг.

Of

зг

Q,.

L...

19

Jl, ,

,, 5,/ I I

RT /j I

г

fffKlf

f

i t-a

1

вЛ

#/

Л7

ErJ

г /у

Sw

гл

BtffS исхоЗмыя jHifveHuu rnoAP,(Qe - euS)

Измерение Pud B vue/tfffuff ,(ftffi M Q)

Вычисление: S/ тлР-Р 8bi fuC t nue 1 bg (Q PtjflH)- (Qc - Лв) Вичие/ieHue: Su,0u OK, SM

f. Опрос состоянии преа розо9ате еа. B ipaiomira при неовхойиности npuxaja Si Ci нЛ pe itune i-eo ftpeofflarjfffame.

тйР; тйР tafi Of - (Of - к Ad) t uO

9 CSpoc (лака снамиро6а ия

CKOHUpoSaweСтнироеанае

Г5П„ п n гк гГрп rk а rQl

«

CSpec

X

Sx ioveHue

.. г

V П П П ПП П ПП П... П П П ПЛЛПЛ

i П П П П П П П ПП П П ПППППППП

Vis гьу PL П In )гк гУч гг гк

:эь.

V,t

Z

9i

%

%

%

-

№; -

фиг. 9

%

Z

JJC

i

(w

г-л

У-У- т (Риг. W

iff

гг,

5gnnn пп п пп п

п ппппп.ппп

фиг.

| Устройство для электроснабжения | 1981 |

|

SU1069101A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Групповой преобразователь | 1980 |

|

SU896724A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1988-05-07—Публикация

1986-07-14—Подача