возможность возникновения сбоев при смене информации из-за того, что моменты записи информации в регистры памяти не синхронизированы с работой каналов формирования последовательностей.

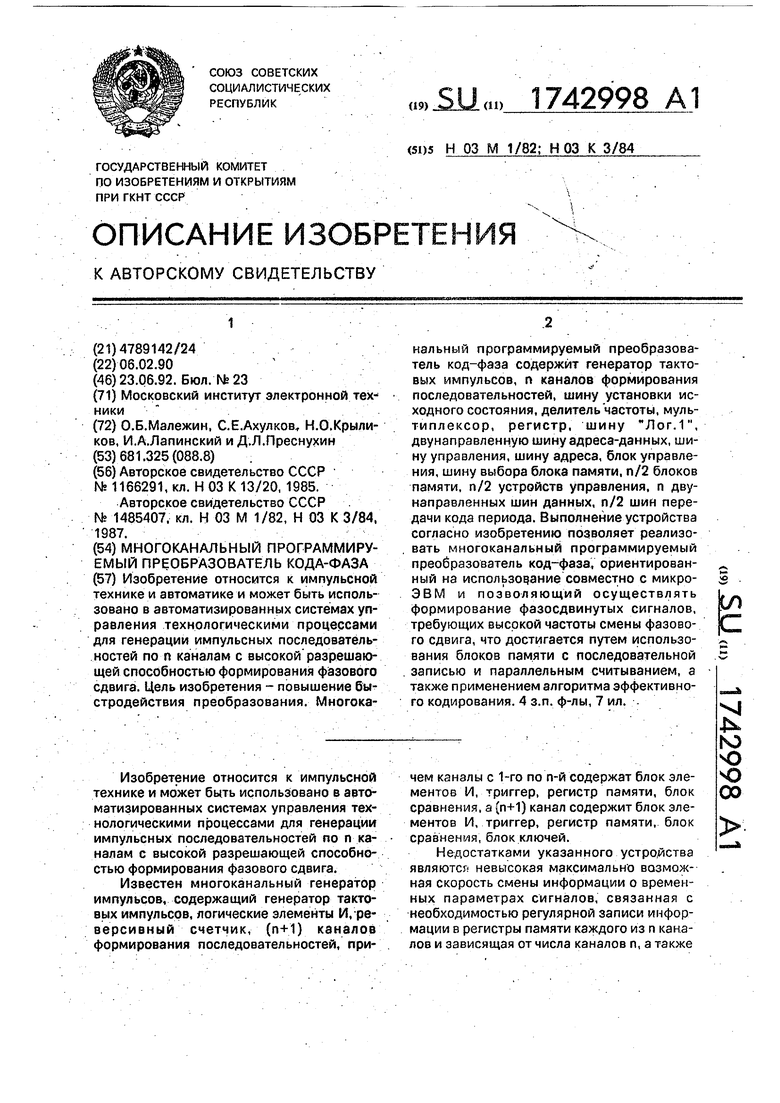

Известен также многоканальный преобразователь кода во временной интервал, содержащий генератор импульсов, распределитель каналов, реверсивный счетчик, блок сравнения, запоминающее устройство, п элементов И, п триггеров.

Недостатком указанного устройства является невозможность изменения информации о временных интервалах более чем по одному из п каналов в каждом цикле считывания запоминающего устройства, а следовательно, невозможность использования указанного преобразователя при требовании высокой скорости смены информации. Наиболее близким к заявляемому по технической сущности и достигаемому результату является многоканальный программируемый преобразователь код-фаза, содержащий генератор тактовых импульсов, регистр памяти, реверсивный счетчик, счетный триггер, п каналов формирования последовательностей, п элементов ИЛИ- НЕ, шину данных, шину строба данных, регистр данных, шину состояний и шину строба состояний, регистр состояний, шину установки исходного состояния, делитель частоты, мультиплексор, регистр адреса 1 мультиплексора, дешифратор, триггер, три элемента ИЛИ-НЕ, два инвертора, элемент 2И-ИЛИ-НЕ, счетчик периодов, шину Лог.1, при этом каждый канал формирования последовательностей с первого по п-й содержит регистр памяти, схему сравнения, счетныйтриггер, элемент2И-ИЛИ-НЕ и инвертор, шина Лог.1 присоединена к первому входу мультиплексора, второй вход которого присоединен к выходу генератора тактовых импульсов и к входу делителя частоты, t выходов которого соединены с входами мультиплексора с третьего по (t+2)-ft вход, h адресных входов которого соединены с выходами регистра адреса мультиплексора.

Недостатком известного устройства является ограниченная частота изменения ин- формации в каждом из каналов формирования последовательностей, зависящая от скорости передачи информации из внешнего устройства в регистры памяти каналов, которая не может превышать предельного, сравнительно низкого значения, определяемого применяемым интерфейсом связи, а также от числа каналов формирования последовательностей и уменьшающаяся при увеличении числа каналов п.

Целью изобретения является повышение быстродействия.

Указанная цель достигается тем, что в многоканальный программируемый преобразователь код-фаза, содержащий генератор тактовых импульсов, выход которого соединен с входом делителя частоты и первым информационным входом мультиплексора, второй информационный вход

0 которого является шиной логической единицы, информационные входы с третьего по (х+2}-й включительно соединены с соответствующими из t выходов делителя частоты, адресные входы подключены к соответству5 ющим выходам регистра, а выход соединен с первым входом синхронизации блока управления, входы установки адреса которого подключены к шине адреса, первый выход первой группы выходов соединен с такто0 вым входом регистра, входы строба адреса . и сигнала записи являются соответственно входными шинами строба адреса и сигнала записи, а вход установки исходного состояния, являющийся входной шиной установки

5 исходного состояния, объединен с одноименными входами п каналов формирования последовательностей, выходы которых являются соответствующими информационными выходными шинами, введены двунап0 равленная шина адресов-данных, п/2 устройств управления и п/2 блоков памяти, первые и вторые вход-выходы данных Ьго блока памяти, где I 1, 2,..., п/2 соответственно соединены с соответствующими вхо5 дами-выходами данных 2 1-го и (2-Ы)-го каналов формирования последовательностей, выходы соединены с соответствующими входами группы входов 2-1-го и (2-1-1)-го каналов формирования последовательноо стей, а третьи входы-выходы данных объединены с соответствующими входами-выходами данных блока управления и соединены с соответствующими входами-выходами двунаправленной шины

5 адресов-данных, являющейся входно-вы- ходной шиной адресов-данных, первый выход делителя частоты соединен с первыми входами синхронизации п/2 блоков памяти и вторым входом синхронизации блока уп0 равления, второй выход первой группы выходов которого соединен с входами пуска п/2 устройств управления и с первыми входами пуска п/2 блоков памяти, выходы с третьего по восьмой включительно первой

5 группы выходов блока управления соединены соответственно с входами строба периодов, записи-чтения, записи адреса, строба адреса, инкрементации адреса и выбора кристалла п/2 блоков памяти, вход сброса первого из которых объединен с входами

сброса остальных (п/2-1) блоков памяти, регистра, с входами установки исходного состояния п/2 устройств управления и с входом установки исходного состояния блока управления, третий вход синхронизации 5 которого соединен с вторым входом делитея частоты, первый вход синхронизации объединен с входами синхронизации п/2 устройств управления и с вторыми входами синхронизации п/2 блоков памяти, выходы 10 с девятого по двенадцатый включительно первой группы выходов блока управления соединены соответственно с входами строба данных п каналов формирования послеовательностей, с входами первого строба 15 данных п/2 устройств управления, вторыми входами пуска п/2 блоков памяти и входами второго строба данных п/2 устройств управения, выход окончания ввода-вывода первого блока памяти объединен с одноименными 20 входами остальных (п/2-1) блоков памяти и подключен к одноименному входу блока управления, выходы с первого по n/2-й второй группы выходов которого соединены с входами выбора канала соответствующего блока 25 памяти, (п/2 + 1)-й и (п/2+2)-й выходы второй группы выходов блока управления соответственно соединены с первыми входами управления направлением передачи п/2 блоков памяти, выход и вход чтения 30 блока управления являются соответственно выходной шиной сигнала ответа и входной шиной чтения, информационные входы регистра соединены с соответствующими входами-выходами двунаправленной шины 35 адресов-данных, выходы с первого по четвертый 1-го устройства управления соединены соответственно с входами записи 2-i-ro и (2-1-1)-го и с входами сравнения 2-1-го и (2х i-1)-ro каналов формирования последова- 40 ельностей, выходы старших разрядов которых соединены соответственно с первым и вторым входами старших разрядов устройтва управления.

Кроме того, блок управления содержит 45 ва селектора адреса, двухканальный программируемый таймер, три элемента ИЛИ- НЕ, два элемента ИЛИ, восемь регистров сдвига, четыре триггера, регистр периода, счетчик периода, четыре инвертора, четыре 50 элемента 2И, элемент2И-НЕ, мультивибраор, при этом вход сброса таймера подклюен к входам сброса регистров сдвига с первого по восьмой, триггеров с первого по третий, регистра периода, мультивибрато- 55 ра. к второму входу второго элементами и является входом сброса блока управления, входы адреса-данных первого и второго се- ектора адреса соединены между собой, с входами-выходами данных таймера, с входами данных регистра периода и являются входами-выходами адреса-данных блока управления, первый вход-выход,адреса-данных подключен к установочным входам первого и четвертого триггеров, входы строба адреса, считывания и записи первого се- лектора адреса соединены с соответствующими входами второго селектора адреса и являются входами управления блока управления с первого по третий соответственно, выход ответа первого селектора адреса соединен с выходом, ответа второго селектора адреса и является выходом ответа блока управления, адресные входы первого и второго селекторов адреса являются соответственно первой и второй группой входов установки адреса, выход записи первого селектора адреса подключен к установочному входу первого регистра сдвига, к вторым входам элементов ИЛИ-НЕ с первого по третий и к вторым входам первого и второго элементов ИЛИ, вход готовности соединен с выходом первого сдвигового регистра, первый, второй, четвертый и пятый выходы выборки кристалла подключены к первым входам соответственно первого и второго элементов ИЛИ-НЕ, второго элемента ИЛИ, третьего элемента ИЛИ-НЕ, третий выход выборки кристалла соединен с первым входом первого элемента ИЛИ и является пятым выходом первой группы сигналов управления, выход записи второго селектора адреса соединен с входом записи двухканального программируемого таймера и является выходом (п/2+1)-го разряда второй группы сигналов управления, вход готовности подключен к выходу первого элемента 2И, выход чтения соединен с входом чтения таймера и является выходом (п/2+2)-го разряда второй группы сигналов управления, выходы выборки кристалла с первого по п/2 являются соответственно выходами (1 ..,(п/2)) разрядов второй группы Сигналов управления, выходы выборки кристалла с ((п/2)+1)-го по ((п/2)+3)-й подключены соответственно к входам выборки кристалла таймера с первого по третий, первый синхровход которого соединен с выходом четвертого элемента 2И, второй синхровход подключен к первому выходу этого же таймера и к установочному входу второго регистра сдвига, вход сброса второго канала соединен с выходом второго элемента 2 И и со входом сброса четвертого триггера, второй выход подключен к установочному входу третьего регистра сдвига, выход готовности соединен с первым входом первого элемента 2И, второй вход которого подключен к выходу четвертого инвертора, вход которого является тринадцатым разряом первой группы сигналов управления, выходы первого элемента ИЛИ-НЕ, первого триггера, первого элемента ИЛИ, первого инвертора, второй выход второго регистра

сдвига, выход пятого регистра сдвига, первый и второй выходы шестого регистра сдвига и выход седьмого регистра сдвига являются соответственно первым, четвертым, шестым-двенадцатым выходами первой -группы сигналов управления, прямой выход четвертого триггера и выход второго элемента ИЛИ подключены соответственно к второму входу четвертого элемента 2И и к установочному входу второго триггера и являются соответственно вторым и третьим выходами первой группы сигналов управления, выходы второго и третьего элементов ИЛИ-НЕ соединены с синхровходами соответственно первого и четвертого триггеров, синхровход второго триггера подключен к синхровходам третьего триггера, первого, второго и третьего регистров сдвига и является первым синхровходом блока управления, синхровход восьмого регистра сдвига является вторым синхровходом блока управления, синхровход счетчика периода подключен к синхровходам пятого, шестого, седьмого регистров сдвига и является третьим синхровходом блока управления, вход разрешения счета счетчика периода соединен с инверсным выходом четвертого триггера, входы данных подключены к выходам данных регистра периода, вход записи соединен с установочным входом мультивибратора и с выходом третьего элемента 2И, выход индикации нулевого состояния подключен к первому входу третьего элемента 2И. второй вход которого соединен с выходом третьего триггера, установочный вход которого подключен к инверсному выходу второго триггера и к входу записи регистра периода, первый выход второго регистра сдвига соединен с входом первого инвертора, третий выход подключен к входу второго инвертора, выход которого соединен с установочным входом четвертого регистра сдвига, синхровход которого подключен к выходу восьмого регистра сдвига, выходы с первого по третий соединены с установочными входами соответственно пятого, шестого и седьмого регистров сдвига, первый выход третьего регистра сдвига подключен к входу третьего инвертора, выход которого соединен с вторым входом элемента 2И- НЕ, первый вход которого подключен к второму выходу третьего регистра сдвига, а выход соединен с первым входом второго элемента 2И, прямой и инверсный выходы мультивибратора подключены соответственно к установочному входу восьмого регистра сдвига и к первому входу четвертого элемента 2И, Каждый из блоков памяти содержит три магистральных приемопередатчика, тринадцать элементов ИЛИ, элемент

ИЛИ-НЕ, инвертор, четыре элемента ЗИ, два регистра сдвига, три триггера, элемент 2И-НЕ с открытым коллектором, два элемента 2И, регистр периода, счетчик периода, счетчик адреса, два оперативных

запоминающих устройства, внутреннюю двунаправленную шину данных, при этом вход сдброса первого регистра сдвига подключен к входам сброса второго регистра сдвига, первого и второго триггеров, регистра периода, счетчика адреса и является входом сброса блока памяти, первый двунаправленный канал передачи данных первого магистрального приемопередатчика является входами-выходами данных блока памяти, первая группа сигналов управления подключена к составным частям блока памяти, при этом вход сброса третьего триггера является входом первого пуска, первый вход второго элемента ИЛИ соединен с третьими входами первого и второго элементов ЗИ и является входом строба периода блока памяти, входы записи-считывания первого и второго оперативных запоминающих устройств объединены между собой и являются входами записи-считывания блока памяти, вход записи счетчика адреса соединен с вторым входом первого элемента ЗИ и является входом записи адреса блока памяти, второй вход второго элемента ЗИ подключен к первому входу элемента ИЛИ-НЕ и является входом строба адреса блока памяти, первый вход двенадцатого элемента ИЛИ является входом инкрементации адреса блока памяти, вторые входы третьего и четвертого элементов ЗИ соединены между собой и являются входом выбора кристалла блока памяти, синхровход третьего триггера является входом второго пуска блока памяти, выход элемента 2И-НЕ с открытым коллектором является выходом завершения ввода-вывода, вторая группа сигналов управления подключена к составным частям блока памяти так, что первый вход первого элемента ЗИ соединен с

первым входом первого элемента ИЛИ, с вторыми входами пятого и шестого элементов ИЛИ и является входом выбора канала, первый вход второго элемента ЗИ подключен к вторым входам седьмого и тринадцатого элементов ИЛИ и является первым входом указания направления передачи, первый вход четвертого элемента ИЛИ соединен с вторыми входами первого и третьего элементов ИЛИ и является вторым входом указания

направления передачи блока памяти, синх- ровходы первого и второго регистров сдвига, первого и второго триггеров объединены между собой и являются первым синхровхо- дом блока памяти, синхровход счетчика периода является вторым синхровходом блока памяти, вход выборки кристалла первого магистрального приемопередатчика соединен с выходом первого элемента ЗИ, первый вход указания направления передачи подключен к выходу второго элемента ЗИ, второй вход указания направления передачи соединен с выходом четвертого элемента ИЛИ, второй двунаправленный канал передачи данных подключен к внутренней дву- направленной шине данных, выход Выполнено соединен с первыми входами третьего и седьмого элементов ИЛИ, с вторыми входами второго элемента ИЛИ и элемента ИЛИ-НЕ, выход которого подключен к второму входу двенадцатого элемента ИЛИ, выход которого соединен с синхровходом счетчика адреса, входы данных которого соединены с входами данных регистра периода, первыми двунаправленными каналами передачи данных второго и третьего магистральных приемопередатчиков и внутренней двунаправленной шиной данных, выходы, кроме старшего разряда, подключены к адресным входам первого и второго оперативного запоминающего устройства, выход старшего разряда соединен с первым входом шестого элемента ИЛИ и с входом инвертора, выход которого подключен к первому входу пятого элемента ИЛИ, выход которого соединен с вторыми входами восьмого, десятого элементов ИЛИ и с входом выборки кристалла третьего магистрального приемопередатчика, второй двунаправленный канал передачи данных которого подключен к входам-выходам второго оперативного запоминающего устройства и является второй группой выходов данных блока памяти, второй вход указания направления передачи подключен к второму входу указания направления передачи второго магистрального приемопередатчика и к первому выходу второго регистра сдвига, первый вход указания направления передачи соединен с выходом седьмого элемента ИЛИ и с первым входом указания направления передачи второго магистрального приемопередатчика, вход выборки кристалла которого соединен с вторыми входами девятого и одиннадцатого элементов ИЛИ и с выходом шестого элемента ИЛИ, второй двунаправленный канал передачи данных подключен к входам-выходам первого оперативного запоминающего устройства и является первой группой выходов данных

блока памяти, выход Выполнено соединен с первым входом первого элемента 2И. второй вход которого подключен к выходу Выполнено третьего магистрального 5 приемопередатчика, выход соединен с вторым входом четвертого элемента ИЛИ и с первым входом тринадцатого элемента ИЛИ, выход которого подключен к установочному входу первого регистра сдвига,

0 первый выход которого соединен с первыми входами восьмого и девятого элементов ИЛИ, второй выход подключен к второму входу элемента 2И-НЕ с открытым коллектором, первый вход которого соединен с

5 выходом третьего элемента ИЛИ, выход первого элемента ИЛИ подключен к установочному входу второго регистра сдвига, второй выход которого соединен с первым входом десятого элемента ИЛИ и с первым входом

0 одиннадцатого элемента ИЛИ, выход которого подключен к третьему входу четвертого элемента ЗИ, первый вход которого соединен с выходом девятого элемента ИЛИ, выход подключен к входу выборки кристалла пер5 вого оперативного запоминающего устройства, вход выборки кристалла второго оперативного запоминающего устройства соединен с выходом третьего элемента ЗИ, первый и третий входы которого подключе0 ны соответственно к выходам восьмого и девятого элементов ИЛИ, выход второго элемента ИЛИ соединен с установочным входом первого триггера, инверсный выход которого подключен к синхровходу регистра

5 периода и к установочному входу второго триггера, инверсный выход которого соединен с вторым входом второго элемента 2И, первый вход которого подключен к выходу индикации нулевого состояния счетчика пе0 риода, выход соединен с входом записи счетчика периода, вход разрешения счета которого подключен к инверсному выходу третьего триггера, входы данных соединены с выходами данных регистра периода, выхо5 ды данных являются группой выходов передачи кода периода блока памяти. Каждый из каналов формирования последовательностей содержит регистр памяти, регистр фазовращателя, схему сравнения, счетный

0 триггер г инвертор, при этом вход сброса регистра памяти соединен с входами сброса регистра фазовращателя и счетного триггера и является входом установки исходного состояния канала, входы данных регистра

5 памяти являются входами данных канала, синхровход регистра памяти является входом строба данных канала, выход старшего разряда является выходом старшего разряда канала, выходы данных, кроме старшего разряда, подключены к входам данных регистра фазовращателя, синхровход которого является входом записи кайалэ, выходы данных соединены с второй группой входов схемы сравнения, первая группа входов которой является группой входов передачи кода периода, вход разрешения сравнения является входом сравнения канала, выход подключен к синхровходу счетного триггера, установочный вход которого соединен со своим инверсным выходом и входом инвертора, выход которого является выходом Uk канала с номером k. Каждое из устройств управления каналами формирования последовательностей содержит шесть триггеров, пять инверторов, два элемента ИЛИ-НЕ, два элемента ЗИ, четыре элемента 2И- ИЛИ-НЕ, при этом вход первого инвертора является входом установки исходного состояния устройства управления, второй вход первого элемента ЗИ соединен с вторым входом второго элемента ЗИ и является синхровходори устройства управления, вход сброса первого триггера является входом пуска устройства управления, синхровход соединен с синхровходом третьего триггера, с вторым входом второго элемента ИЛИ-НЕ, с входом третьего инвертора и является входом первого строба данных фазовращателя, вход пятого инвертора соединен с вторым входом первого элемента ИЛИ-НЕ и является входом второго строба данных фазовращателя, синхровход второго триггера подключен к входу второго инвертора, к второму входу второго элемента 2И-ИЛИ-НЕ и является первым входом старшего разряда устройства управления, синхровход пятого триггера соединен с входом четвертого инвертора, с третьим входом четвертого элемента 2И-ИЛИ-НЕ и является вторым входом старшего разряда устройства управления, выход первого триггера подключен к первым входам первого и второго элементов ЗИ, третьи входы которых соединены соответственно с выходами первого и третьего элементов 2И-ИЛИ-НЕ, выходы являются соответственно четвертым и третьим выходами устройства управления, выход первого инвертора подключен к первым входам первого и второго элементов ИЛИ- НЕ, выходы которых соединены с входами сброса соответственно второго, третьего, пятого, четвертого, шестого триггеров, выход второго триггера соединен с первым входом первого элемента 2И-ИЛИ-НЕ, второй вход которого подключен к выходу третьего триггера и к второму входу третьего элемента 2И-ИЛИ-НЕ, третий и четвертый входы соединены между собой и с выходом четвертого триггера, синхровход которого подключен к выходу второго инвертора и к третьему входу второго элемента 2И-ИЛИ-НЕ, первый вход которого соединен с выходом пятого инвертора и с четвертым входом четвертого элемента 2ИИЛИ-НЕ, выход является первым выходом устройства управления, четвертый вход соединен с выходом третьего инвертора и с вторым входом четвертого элемента 2И- ИЛИ-НЕ, выход которого является вторым

0 выходом устройства управления, первый вход соединен с выходом четвертого инвертора и с синхровходом шестого триггера, выход которого подключен к третьему и четвертому входам третьего элемента 2И5 ИЛИ-НЕ, первый вход которого соединен с выходом пятого триггера,

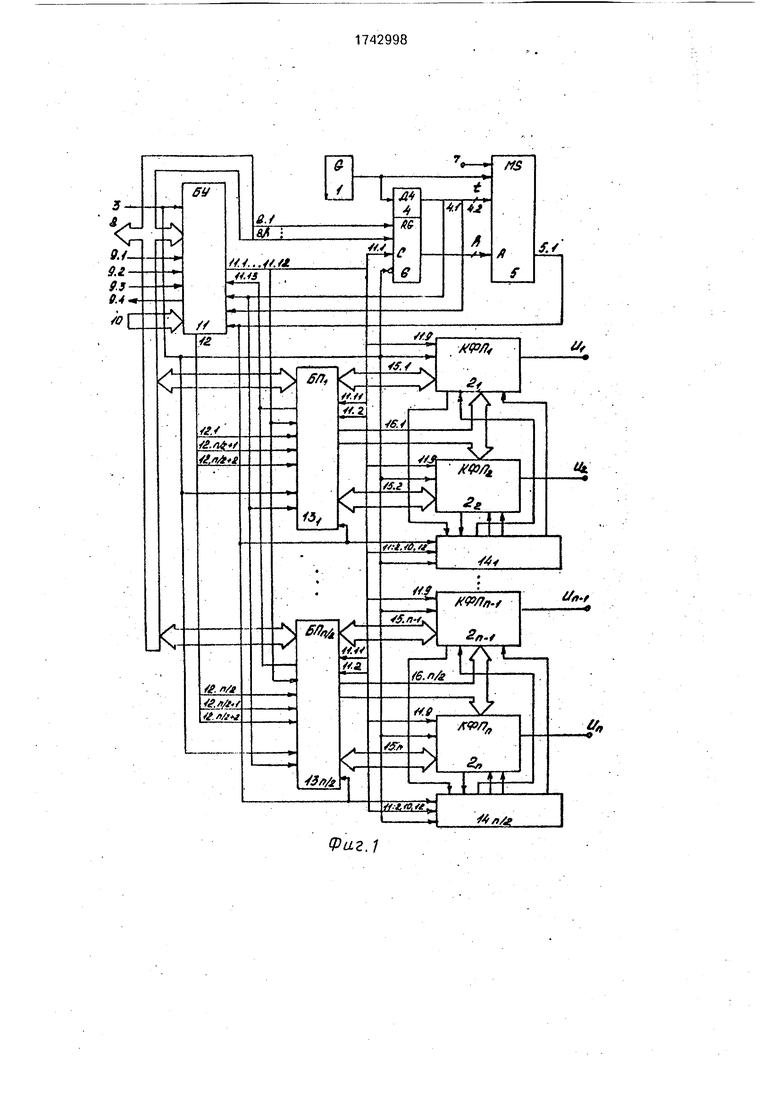

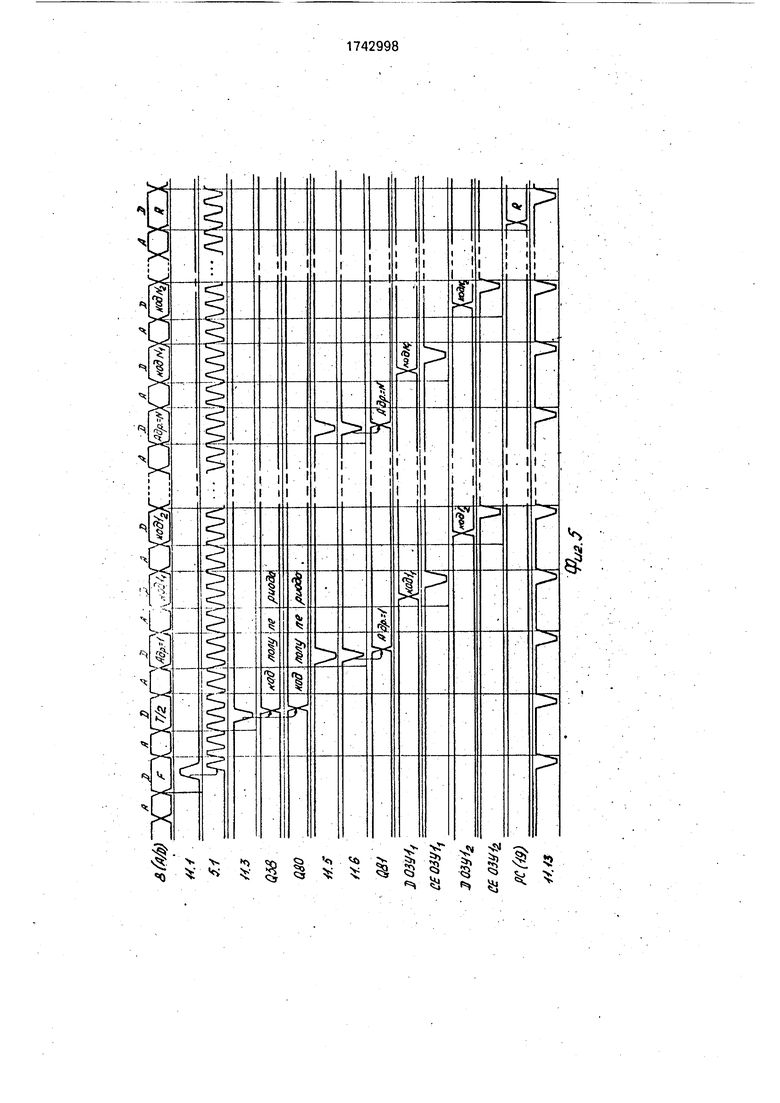

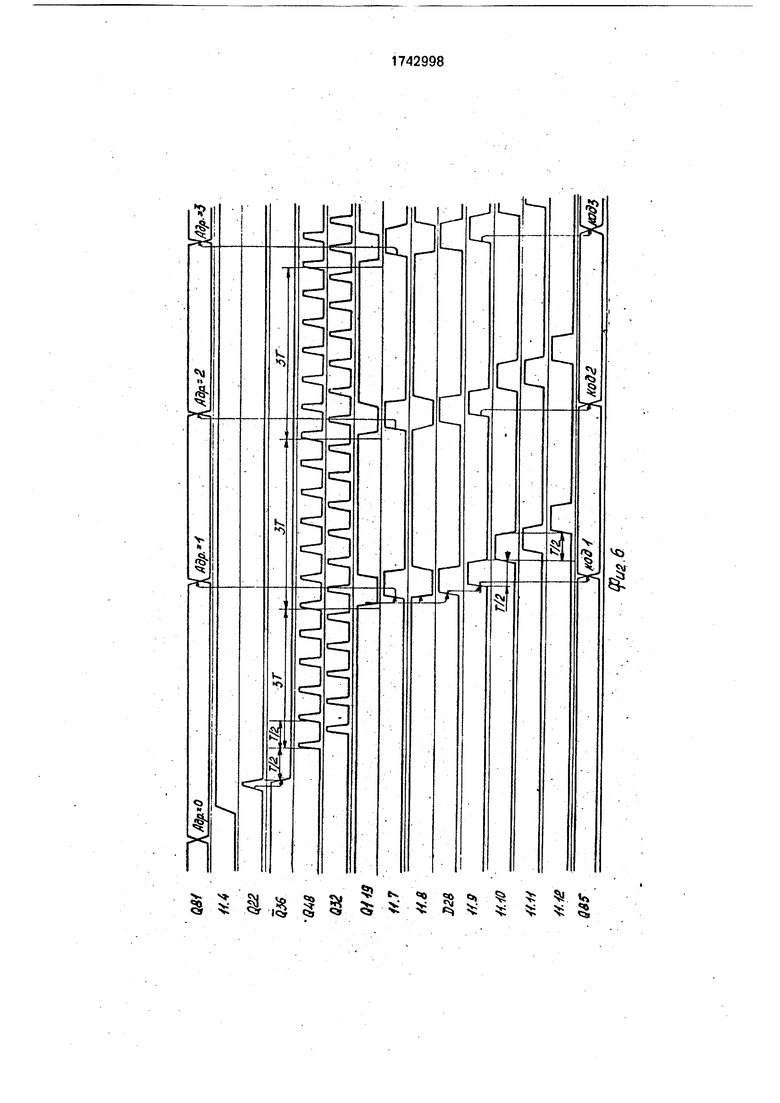

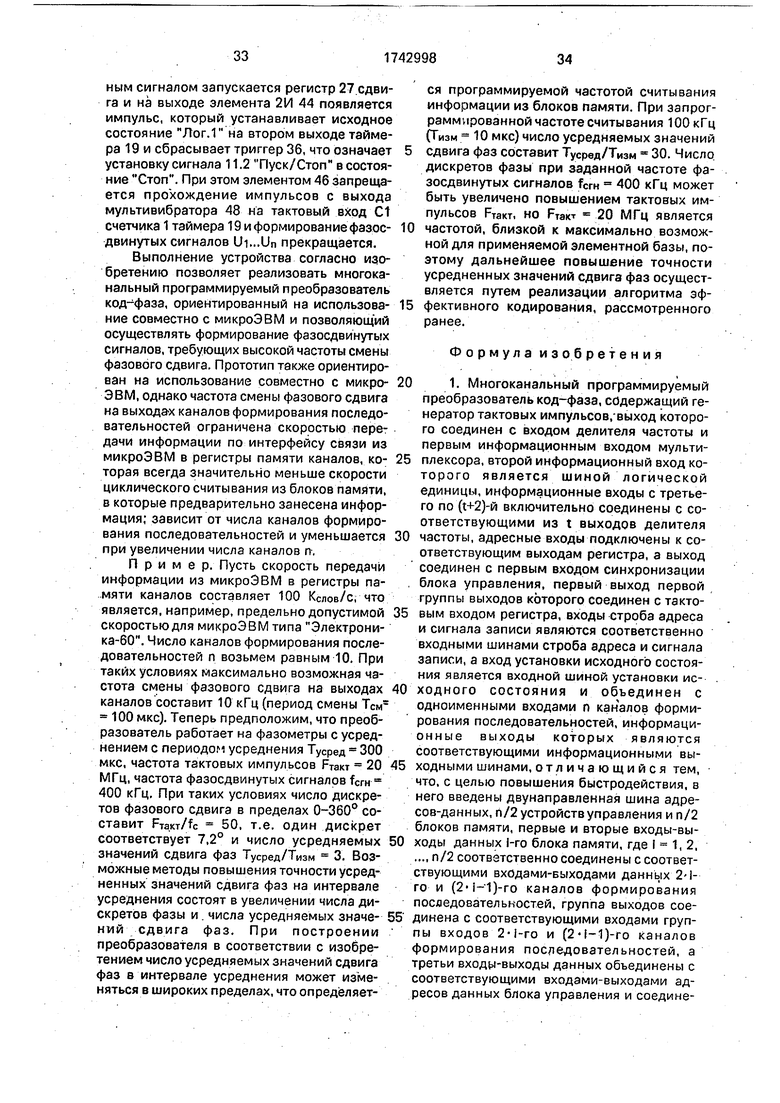

На фиг.1 приведена функциональная схема многоканального программируемого преобразователя код-фаза; на фиг.2 - фун0 кциональная схема устройства управления; на фиг.З - функциональная схема блока памяти; на фиг.4 - функциональные схемы каналов формирования последовательностей и устройства управления каналами формирова5 ния последовательностей; на фиг,5 - времен- ные диаграммы режима начального программирования преобразователя; на фиг.6 - временные диаграммы режима формирования фазосдвинутых последовательно0 стей; на фиг.7 - временные диаграммы работы каналов формирования последовательностей и устройствуправления каналами. Преобразователь (фиг.1) содержит генератор 1 тактовых импульсов, п каналов 2

5 формирования последовательностей, шину

3установки исходного состояния, делитель

4частоты, мультиплексор 5, регистр 6, шину Лог,1 7, двунаправленную шину 8 адреса- данных, шину 9 управления, шину 10 адре0 са, блок 11 управления, шину 12 выбора блока памяти, п/2 блоков 13 памяти, п/2 устройств 14 управления каналами формирования последовательностей, п двунаправленных шин 15 данных, п/2 шин 16

5 передачи кода периода. Выход генератора 1 тактовых импульсов соединен с вторым входом мультиплексора 5 и входом делителя 4 частоты, t выходов которого соединены с входами мультиплексора 5 с третьего по

0 (г+2)-й вход, первый вход мультиплексора присоединен к шине Лог.1, h адресных входов соединены с выходами регистра 6, выход 5.1 соединен с третьим синхровходом блока 11 управления, с вторыми синхровхо5 дами блоков памяти 13i...13n/2, с синхровхо- дами устройств 14i...14n/2 управления, с третьим синхровходом блока 11 управления, второй синхровход которого соединен с вторым выходом 4.2 делителя частоты, первый синхровход подключен к первому

выходу 4.1 делителя 4 частоты и к первым синхровходам блоков 13i...13n/2 памяти, вход сброса соединен с шиной 3 установки исходного состояния, с входом сброса регистра 6, с входами установки исходного состояния каналов 2i...2n формирования последовательностей, с входами установки исходного состояния устройств 14i...14n/2 управления каналами формирования последовательностей, с входами сброса блоков 13i..,13n/2 памяти, входы-выходы адреса- данныхподключены к двунаправленной шине 8 адреса-данных, входам-выходам данных блоков 13i...13n/2 памяти и к h информационным входам регистра 6, входы управления с первого по третий соединены с соответствующими разрядами шины 9 управления, выход ответа подключен к четвертому разряду шины 9 управления, входы установки адреса подключены к шине 10 адреса, первая группа сигналов управления соединена с составными частями преобразователя так, что первый выход 11.1 подключен к синхровходу регистра адреса мультиплексора б, выходы 11.2,11.10,11.12 подключены соответственно к входам пуска, первого строба данных фазовращателя и второго строба данных фазовращателя устройств 14i...14n/2 управления каналами формирования последовательностей, выходы 11.2... 11.8, 11.11 соединены соответственно с входами первого пуска, строба периода, записи-считывания, записи адреса, строба адреса, инкрементации адреса, выбора кристалла, второго пуска блоков 131...13п/2-памяти, выход 11.9 подключен к входам строба данных каналов 2i...2n формирования последовательностей, 13-й разряд первой группы сигналов управления, являющийся входом, соединен с выходом завершения ввода-вывода блоков 131...13л/2 памяти, вторая группа сигналов управления подключена к шине выбора блока 12 памяти так, «то разряды 12.1...12.П/2 соединены соответственно с входами выбора канала блоков 13i...13n/2 памяти, разряды 12.П/2-М и 12.П/2+2 подключены соответственно к первому и второму входам указания направления передачи блоков 13i...13n/2 памяти, каждый из которых соединен с двумя каналами 2 формирования последовательностей, при этом первая и вторая группа выходов данных каждого блока 13 памяти посредством двунаправленных шин 15 данных соединена с входами данных каналов 2 формирования последовательностей, имеющих соответственно нечетные и четные номера, группа выходов передачи кода периода посредством шин 16 передачи кода периода соединена с группами входов передачи кода периода каналов 2, имеющих нечетные и четные номера, каждое из устройств 14 управления каналами формирования последовательностей соеди- 5 нено с двумя каналами 2 формирования по- следовательностей, при этом выходы старшего разряда каналов 2, имеющих нечетные и четные номера, соединены соответственно с первыми и вторыми входами

0 старших разрядов устройства 14 управления каналами, выходы с первого по четвертый каждого из устройств управления каналами подключены соответственно к входам записи каналов 2 с нечетными и чет5 ными номерами и к входам сравнения каналов 2 с четными и нечетными номерами, выходы каналов формирования последовательностей 2 являются выходами преобразователя.

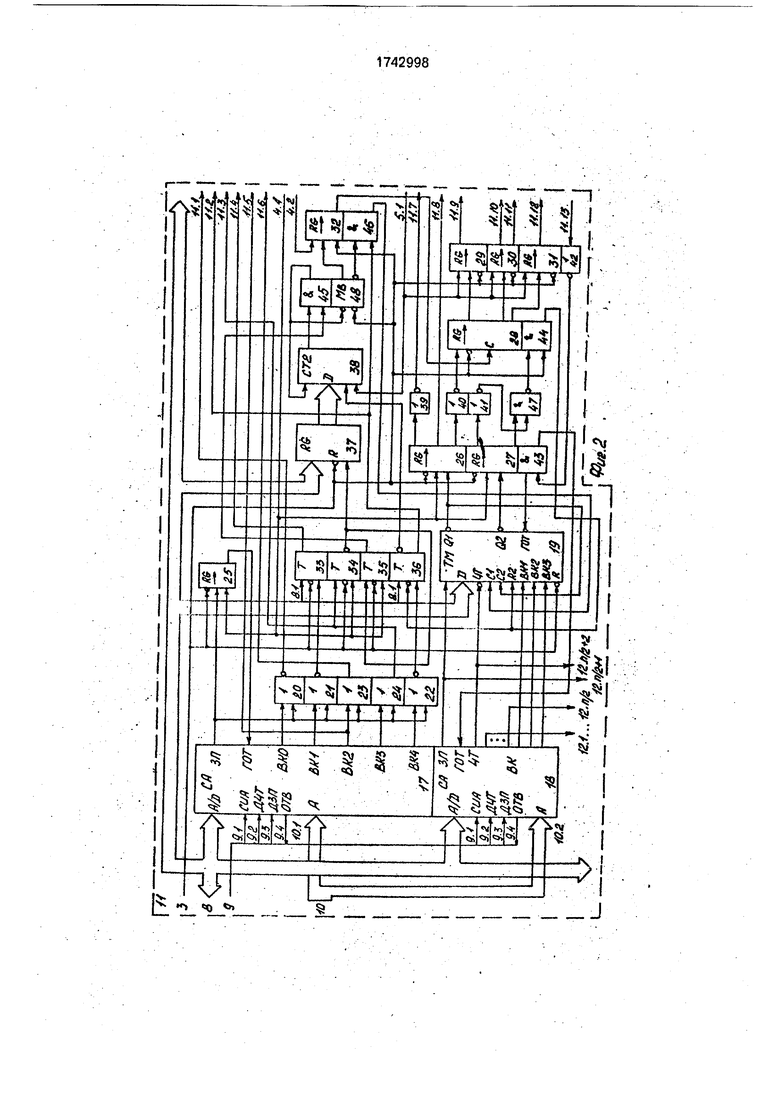

0 Блок 11 управления (фиг.2) содержит два селектора 17 и 18 адреса двухканальный программируемый таймер 19,-три элемента ИЛИ-НЕ 20-22, два элемента ИЛИ 23 и 24, восемь регистров 25-32 сдвига, четыре

5 триггера 33-36,, регистр 37 периода, счетчик 38 периода, четыре инвертора 39-42, четыре элемента 2И 43-46, элемент 2И-НЕ 47, мультивибратор 48, при этом вход сброса таймера 19 подключен к входам сброса ре0 гистров 25-32 сдвига, триггеров 33-35, регистра 37 периода, мультивибратора 48, к второму входу элемента 2И 44 и является входом сброса блока управления, входы адреса-данных селекторов 17 и 18 адреса сое5 динены между собой, с входами-выходами данных таймера 19, с входами данных регистра 37 периода и являются входами-выходами адреса-данных блока управления, первый вход-выход адреса-данных подклю0 чен к установочным входам триггеров 33 и 36, входы строба адреса, считывания и записи селектора 17 адреса соединен с соответствующими входами селектора 18 адреса и являются входами управления блока управ5 ления с первого по третий соответственно, выход ответа селектора 17 адреса соединен с выходом ответа селектора 18 адреса и является выходом ответа блока управления, адресные вхсды селекторов 17 и 18 адреса

0 являются соответственно первой и второй группой входов установки адреса,-выход записи селектора 17 адреса подключен к установочному входу регистра Я5 сдвига, к вторым входам элементов ИЛИ-НЕ 29-22 и

5 к вторым входам элементов ИЛИ 23 и 24, вход готовности соединен с выходом сдвигового регистра 25, первый, второй, четвертый и пятый выходы выборки кристалла подключены к первым входам соответственно элементов ИЛИ-НЕ 20 и 21, элемента

ИЛИ 24, элемента ИЛИ-НЕ 22, третий выход выборки кристалла соединен с первым входом элемента ИЛИ 23 и является выходом 11.5 первой группы сигналов управления, выход записи второго селектора 18 адреса соединен с входом записи таймера 19 и является выходом 12.П/2-Н второй группы сигналов управления, вход готовности подключен к выходу элемента 2И 43 выход чтения соединен с входом чтения таймера 19 и является выходом 12.П/2+2, выходы выборки кристалла с первого по п/2 являются соответственно выходами 12.1...12.п/2 блока управления, выходы выборки кристалла с ((п/2)+1)-го по ((п/2)+3)-й подключены соответственно к входам выборки кристалла с первого по третий таймера 19, первый синхровход которого соединен с выходом элемента 2И 46, второй синхровход подключен к первому выходу этого же таймера 19 и к установочному входу регистра 26 сдвига, вход сброса второго канала соединен с выходом элемента 2И 44 и с входом сброса триггера 36, второй выход подключён к установочному входу регистра 27 сдвига, выход готовности соединен с первым входом элемента 2И 43, второй вход которого подключен к выходу инвертора 42, вход которого является входом 11.13 первой группы сигналов управления, выходы элемента ИЛИ-НЕ 20, триггера 33, элемента ИЛИ 23, инвертора 39, второй выход регистра 26 сдвига, выход регистра

29сдвига, первый и второй выходы регистра

30сдвига и выход регистра 31 сдвига являются соответственно выходами 11.1, 11.4, 11.6...11.12 блока управления, прямой вы- ход триггера 36 и выход элемента 24 подключены соответственно к второму входу элемента 2И 46 и к установочному входу триггера 34 и являются соответственно выходами 11.2 и 11.3 блока управления, выходы элементов ИЛИ-НЕ 21 и 22 соединены с синхровходами триггеров 33 и 36 соответственно, синхровход триггера 34 подключен к синхровходам триггера 35, регистров 25-27 сдвига и являются первым синхровходом блока управления, синхровход регистра 32 сдвига является вторым синхровходом блока управления, синхровход счетчика 38 периода подключен к синхровходам регистров 29-31 сдвига и является третьим синхровходом блока управления, вход разрешения счета счетчика 38 периода соединен с инверсным выходом триггера 36, входы данных подключены к выходам данных регистров 37 периода, вход записи соединен с установочным входом мультивибратора 48 и с выходом элемента 2И 45 выход индикации нулевого состояния подключен к

первому входу элемента 2И 45, второй вход которого соединен с выходом триггера 35, установочный вход которого подключен к инверсному выходу триггера 34 и к входу

записи регистра 37 периода, первый выход регистра 26 сдвига соединен с входом инвертора 39, третий выход подключен к входу инвертора 40, выход которого соединен с установочным входом регистра 32 сдвига,

0 выходы с первого по третий соединены с установочными входами регистров 29-31 сдвига соответственно, первый выход регистра 27 сдвига подключен к входу инвертора 41, выход которого соединен с вторым вхо5 дом элемента 2И-НЕ 47, первый вход которого подключен к второму выходу регистра 27 сдвига, а выход соединен с первым входом элемента 2И 44, прямой и инверсный выходы мультивибратора 48 подключены

0 соответственно к установочному входу регистра 32 сдвига и к первому входу элемента 2И46.

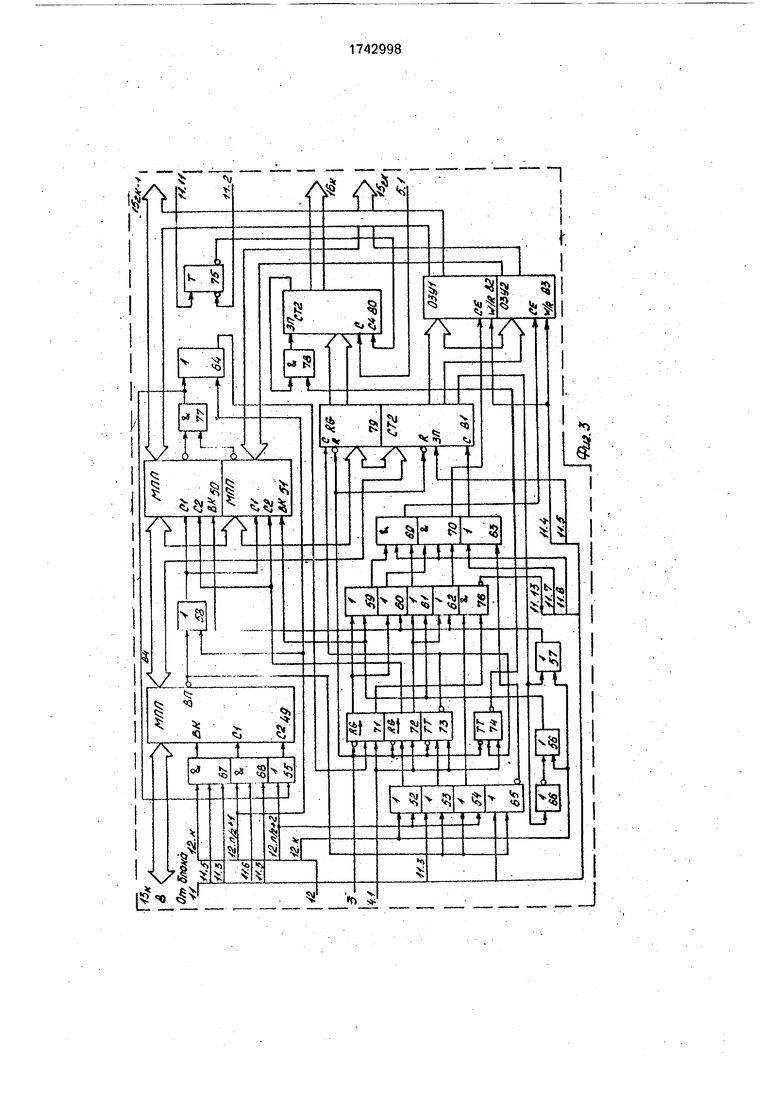

Каждый из блоков 13i...13n/2 памяти (фиг.З) содержит три магистральных при5 емопередатчика 49-51, тринадцать элементов ИЛИ 52-64, элемент ИЛИ-НЕ 65, инвертор 66, четыре элемента ЗИ 67-70, два регистра 71 и 72 сдвига, три триггера 73-75, элемент 2И-Н Е с открытым коллектором 76,

0 два элемента 2И 77 и 78, регистр 79 периода, счетчик 80 периода, счетчик 81 адреса, два оперативных запоминающих устройства 82 и 83, внутреннюю двунаправленную шину 84 данных, при этом вход сброса реги5 стра 71 сдвига подключен к входам сброса регистра 72 сдвига, триггеров 73 и 74, регистра 79 периода, счетчика 81 адреса и является входом сброса блока памяти, первый двунаправленный канал передачи данных

0 магистрального приемопередатчика 49 является входами-выходами данных блока памяти, первая группа сигналов управления подключена к составным частям блока памяти, при этом вход сброса триггера 75 яв5 ляется входом первого пуска, первый вход элемента ИЛИ 53 соединен с третьими входами элементов ЗИ 67 и 68 и является входом строба периода блока памяти, входы записи-считывания оперативных запомина0 ющих устройств 82 и 83 объединены между собой и являются входом записи-считывания блока памяти, вход записи счетчика 81 адреса соединен с вторым входом элемента ЗИ 67 и является входом записи адреса бло5 ка памяти; второй вход элемента ЗИ 68 подключен к первому входу элемента VIЛИ-НЕ 65 и является входом строба адреса блока памяти, первый вход элемента ИЛИ 63 является входом инкрементации адреса блока памяти, вторые входы элементов ЗИ 69 и 70

соединены между собой и являются входом выбора кристалла блока памяти, синхров- ход триггера 75 является входом второго пуска блока Памяти, выход элемента 2И-НЕ с открытым коллектором 76 является выхо- дом завершения ввода-вывода, вторая группа сигналов управления подключена к составным частям блока памяти так, что первый вход элемента ЗИ 67 соединен с первым входом элемента ИЛИ 52, с вторыми входами элементов ИЛИ 56 и 57 и является входом выбора канала, первый вход элемента ЗИ 68 подключен к вторым входам элементов ИЛИ 58 и 64 и является первым входом указания направления передачи, первый вход элемента ИЛИ 55 соединен с вторыми входами элементов ИЛИ 52 и 54 и является вторым входом указания направления передачи блока памяти, синхровходы регистров 71 и 72 сдвига, триггеров 73 и 74 объединены между собой и являются первым синхровходом блока памяти, синхров- ход счетчика 80 периода является вторым синхровходом блока памяти, вход выборки кристалла магистрального приемопередат- чика 49 соединен с выходом элемента ЗИ 67, первый вход указания направления передачи подключен к выходу элемента ЗИ 68, второй вход указания направления передачи соединен с выходом элемента ИЛИ 55, вто- рой двунаправленный канал передачи дан- ных подключен к внутренней двунаправленной шине 84 данных, выход Выполнено соединен с первыми входами элементов ИЛИ 54 и 58, с вторыми входами элемента ИЛИ 53 и элемента ИЛИ-НЕ 65, выход которого подключен к второму входу элемента ИЛИ 63, выход которого соединен с синхровходом счетчика 81 адреса, входы данных которого соединены с входами дан- ных регистра 79 периода, первыми двунаправленными каналами передачи данных приемопередатчиков 50 и 51 и внутренней шиной 84 данных, выходы, кроме старшего разряда, подключены к адресным входам оперативных запоминающих устройств 82 и 83, выход старшего разряда соединен с первым входом элемента ИЛИ 57 и с входом инвертора 66, выход которого подключен к первому входу элемента ИЛИ 56, выход ко- торого соединен с вторыми входами элементов ИЛИ 59 и 61 и с входом выборки кристалла магистрального приемопередатчика 51, второй двунаправленный канал передачи данных которого подключен к входам-выходам оперативного запоминающего устройства 83 и является второй группой выходов данных блока памяти, второй вход указания направления передачи подключен к второму входу указания направления передачи магистрального приемопередатчика 50 и к первому выходу регистра 72 сдвига, первый вход указания направления передачи соединен с выходом элемента ИЛИ 56 и с первым входом указания направления передачи магистрального приемопередатчика 50, вход выборки кристалла которого соединен с вторыми входами элементов ИЛИ 60 и 62 и с выходом элемента ИЛИ 57, второй двунаправленный канал передачи данных подключен к входам-выходам оперативного запоминающего устройства 82 и является первой группой выходов данных блока памяти, выход Выполнено соединен с первым входом элемента 2И 77, второй вход которого подключен к выходу Выполнено магистрального приемопередатчика 51, выход соединен с вторым входом элемента ИЛИ 55 и с первым входом элемента ИЛИ 64, выход которого подключен к установочному входу регистра 71 сдвига, первый выход которого соединен с первыми входами элементов ИЛИ 59 и 60, второй выход подключен к второму входу элемента 2И-НЕ с открытым коллектором 76, первый вход которого соединен с выходом элемента ИЛИ 54, выход элемента ИЛИ 52 подключен к установочному входу регистра 72 сдвига, второй выход которого соединен с первым входом элемента ИЛИ 61 и с первым входом элемента ИЛИ 62, выход которого подключен к третьему входу элемента ЗИ 70, первый вход которого соединен с выходом элемента ИЛИ 60, выход подключен к входу выборки кристалла оперативного запоминающего устройства 82, вход выборки кристалла оперативного запоминающего устройства 83 соединен с выходом элемента ЗИ 69, пер вый и третий входы которого подключены Соответственно к выходам элементов ИЛИ 59 и 61, выход элемента ИЛИ 53 соединен с установочным входом триггера 73, инверсный выход которого подключен к синхровхо- ду регистра 79 периода и к установочному входу триггера 74, инверсный выход которого соединен с вторым входом элемента 2И 78, первый вход которого подключен к выходу индикации нулевого состояния счетчика 80 периода, выход соединен с входом записи счетчика 80 периода, вход разрешения счета которого подключен к инверсному выходу триггера 75, входы данных соединены с выходами данных регистра 79 периода, выходы данных являются группой выходов передачи кода периода блока памяти.

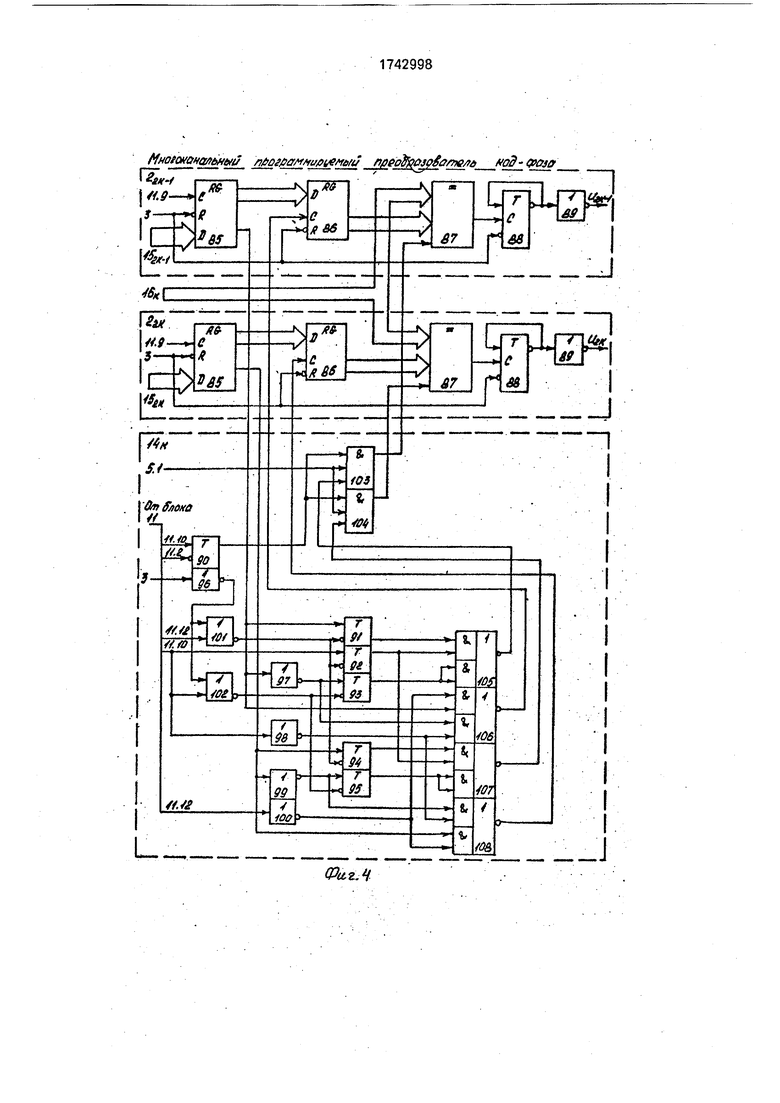

Каждый из каналов 2i...2n формирования последовательностей (фиг.4) содержит регистр 85 памяти, регистр 86 фазовращателя, схему 87 сравнения, счетный триггер 88,

инвертор 89, при этом вход сброса регистра 85 памяти соединен с входами сброса регистра фазовращателя 86 и счетного триггера 88 и является входом установки исходного состояния канала, входы данных регистра 85 памяти являются входами данных канала, синхровход регистра 85 памяти является входом строба данных канала, выход старшего разряда является выходом старшего разряда канала, выходы данных, кроме старшего разряда, подключены к входам данных регистра фазовращателя 86, синхровход которого является входом записи канала, выходы данных соединены с второй группой входов схемы 87 сравнения, первая группа входов которой является группой входов передачи кода периода, вход разрешения сравнения является входом сравнения канала, выход подключен к синхровходу счетного триггера 88, установочный вход ко- торого соединен со своим инверсным выходом и входом инвертора 89, выход которого является выходом Uk канала с номером к.

Каждое из устройств 14i...14n/2 управления каналами формирования последова- тельностей (фиг.4) содержит шесть триггеров 90-95, пять инверторов 96-100, два элемента ИЛИ-НЕ 101 и 102, два элемента ЗИ 103 и 104, четыре элемента 2И- ИЛИ-НЕ 105-108, при этом вход инвертора 96 является входом установки исходного состояния устройства управления, второй вход элемента ЗИ 103 соединен с вторым входом элемента ЗИ 104 и является синх- ровходом устройства управления, вход сброса триггера 90 является входом пуска устройства управления, синхровход соединен с синхровходом триггера 92, с вторым входом элемента И Л И-НЕ 102, с входом инвертора 98 и является входом первого строба данных фазовращателя, вход инвертора 100 соединен с вторым входом элемента ИЛИ-НЕ 101 и является входом второго строба данных фазовращателя, синхровход триггера 91 подключен к входу инвертора 97, к второму входу элемента 2И-ИЛИ-НЕ 106 и является первым входом старшего разряда устройства управления, синхровход триггера 94 соединен с входом инвертора 99, с третьим входом элемента 2И-ИЛИ-НЕ 108 и является вторым входом старшего разряда устройства управления, выход триггера 90 подключен к первым входам элементов ЗИ 103 и 104, третьи входы которых соединены соответственно с выхо- дами элементов 2И-ИЛИ-НЕ 105 и 107, выходы являются соответственно четвертым и третьим выходами устройства управления, выход инвертора 96 подключен к первым входам элементов ИЛИ-НЕ 101 и 102, выходы которых соединены с входами сброса триггеров 91, 92 и 94 и триггеров 93 и 95 соответственно, выход триггера 91 соединен с первым входом элемента 2И-ИЛИ-НЕ 105, второй вход которого подключен к выходу триггера 92 и к второму входу элемента 2И-ИЛИ-НЕ 107, третий и четвертый входы соединены между собой и с выходом триггера 93, синхровход которого подключен к выходу инвертора 97 и к третьему входу элемента 2И-ИЛИ-НЕ 106, первый вход которого соединен с выходом инвертора 100 и с четвертым входом элемента 2И-ИЛИ-НЕ 108, выход является первым выходом устройства управления, четвертый вход соединен с выходом инвертора 98 и с вторым входом элемента 2И-ИЛИ-НЕ 108, выход которого является вторым выходом устройства управления, первый вход соединен с выходом инвертора 99 и с синхровходом триггера 95, выход которого подключен к третьему и четвертому входам элемента 2И- ИЛИ-НЕ 107. первый вход которого соединен с выходом триггера 94. Генератор 1 тактовых импульсов служит для выдачи тактовых импульсов, синхронизирующих работу всего преобразователя. Каналы 2i...2n формирования последовательностей предназначены для формирования импульсных последовательностей, программируемых по частоте и фазовому сдвигу. Шина 3 установки исходного состояния служит для установки составных частей преобразователя в исходное состояние. Делитель 4 частоты предназначен для выработки t сигналов с частотами, полученными делением тактовой частоты генератора 1. Мультиплексор 5 служит для выработки тактовых импульсов с частотой, зависящей от кода, записанного в регистре 6. Шина Лог. Г 7 предназначена для установки уровня Лог.1 на первом входе мультиплексора 5. При этом, если на ад- ресных входах мультиплексора (А) установлен код, соответствующий подключению первого входа, то на выходе мультиплексора отсутствуют тактовые импульсы, а присутствует сигнал с уровнем Лог. Г. Двунаправленная шина 8 адреса-данных предназначена для связи преобразователя с внешними усройствами, например с микро- ЭВМ, а также для связи составных частей преобразователя между собой. По шине 8 могут передаваться как адреса, так и данные, при этом передача адреса сопровождается стробом 9.1 адреса. При чтении данных внешним устройством формируется сигнал 9.2 чтения, при записи внешнее устройство выдает сигнал 9.3 записи, сигнал 9.4 ответа формируется преобразователем при завершении цикла обмена с внешним устройством. Шина 10 адреса состоит из двух составляющих шин 10.1 и 10.2, служащих для установки адресов селекторов 17 и 18 адреса соответственУю, по которым к ним обращается внешнее устройство. Блок 11 управле- ния 11 предназначен для выработки сигналов управления составными частями преобразователя. Шина выбора блока 12 памяти служит для передачи сигналов выбора любого из (п/2) блоков памяти. Блоки 13i...13n/2 памяти предназначены для записи, хранения и считывания информации о фазовом сдвиге.

Устройство 14i...14n/2 управления каналами формирования последовательностей служат для выработки сигналов, управляющих работой каналов формирования импульсныхпоследовательностей. Двунаправленные шины 15i...15n данных предназначены для передачи информации между блоками 13i...13n/2 памяти и каналами 21...2п-формирования последовательностей. Шины 16i...16n/2 передачи кода периода служат для передачи указанного кода из соответствующего блока 13 памяти в каналы 2 формирования последовательностей. Селектор 17 адреса служит для формирования:

сигнала записи (ЗП) при совпадении старших разрядов адреса, передаваемого по шине 8 и сопровождаемого стробом 9.1 адреса и сигналом 9.3 записи с соответствующими разрядами адреса, установленными на шине 10;

сигналов выборки кристаллов ВКО...ВК4 в зависимости от 4 младших разрядов посту лающего адреса; номер выбираемого выхода В К соответствует коду в младших разрядах адреса, деленному на два.

Назначение сигналов ВКО...ВК4 следу- ющее:

ВКО - для формирования сигнала записи в регистр 6 (11.1) адреса мультиплексора;

ВК1 - для выработки сигнала записи- считывания, поступающего в блоки 13i...13n/2 (11.4) памяти;

ВК2 -для формирования сигналов записи и синхронизации счетчиков 81 (11.5,11.6) адреса;

ВКЗ - для выработки сигналов синхро- низации регистров 79 периода (11.3);

ВК4-для формирования сигнала управления блоками 13i...13n/2 пуск/стоп (11.2) памяти.

Например, пусть внешним устройством устанавливается двоичный адрес ХХ...ХХОООО, (где ХХ...ХХ - соответствует разрядам, установленным на шине 10 адреса), при этом появится импульс выборки на выходе ВКО селектора 17 адреса, а при по

даче, например, двоичного адреса ХХ...ХХ0110 импульс выборки появится на выходе ВКЗ.

Селектор 18 адреса служит для формирования:

сигналов ЗП и чтения (ЧТ) при совпадении старших разрядов адреса, передаваемого по шине 8 и сопровождаемого стробом

9.1адреса и сигналом записи 9.3 или чтения

9.2с соответствующими разрядами адреса, установленными на шике 10;

сигналов В К в зависимости от младших разрядов поступающего адреса; номер выбираемого выхода ВК соответствует коду в младших разрядах адреса, деленному на два.

Назначение сигналов ВК следующее:

BKi...BKn/2 - для формирования сигналов выборки соответствующего блока 13 памяти;

ВКп/2+1 - выбор счетчика 1 таймера 19;

ВКп/2+2 - выбор счетчика2 таймера 19;

В Kn/2+з- выбор регистра состояний таймера 19.

Например, пусть внешним устройством устанавливается двоичный адрес YY...YY0100, (где YY...YY - соответствует разрядам, установленным на шине 10 адреса), при этом появится импульс выборки на выходе ВК2 селектора 18 адреса. Таймер 19 предназначен для задания временных интервалов обращения к блокам 13 памяти, каналам 2 формирования последовательностей и устройствам 14 управления каналами. Таймер содержит два независимых суммирующих счетчика, обращение к которым происходит по сигналам ВК1 и ВК2 соответственно, и регистр состояний (PC), задающий режим работы таймера, обращение к PC происходит по сигналу ВКЗ. Регистры 25-32 сдвига служат для формирования задержанных или сдвинутых относительно друг друга импульсов, используемых в качестве внутренних и внешних управляющих сигналов блока 11 управления. Триггеры 34 и 35 служат для выработки из сигнала 11.3 записи двух сдвинутых относительно друг друга импульсов, по первому из которых происходит запись кода полупериода в регистр 37 периода, а по второму - в счетчик 38 периода. Регистр 37 периода представляет собой регистр памяти, в. котором запоминается код. соответствующий сдвигу фаз в 180°, т.е. полупериоду следования фазосдвинутых импульсов.

Счетчик 38 периода представляет собой синхронный реверсивный двоичный счетчик, формирующий на выходе индикации нулевого состояния временные интервалы, соответствующие записанному в регистре

38 коду полупериода. Мультивибратор 48 предназначен для удлинения коротких импульсов, поступающих на его вход запуска с выхода элемента И 45. Магистральный приемопередатчик (МПП) 49 предназначен для передачи информации из двунаправленной шины 8 адреса-данных во внутреннюю двунаправленную шину 84 данных при подаче сигнала выборки приемопередатчика (В К) и сигнала направления передачи(С1) и обратной передачи из шины 84 в шину 8 при подаче сигнала выборки (ВК) и сигнала направления передачи (С2). МПП 50 и 51 служат для передачи информации из внутренней шины 84 по соответствующей шине 15 на входы-выходы соответственно первого и второго оперативных запоминающих устройств (ОЗУ1 и ОЗУ2) 82 и 83 (при подаче сигналов ВК и С1) и обратной передачи из ОЗУ1 82 и ОЗУ2 83 во внутреннюю шину 84 (при подаче сигналов ВКиС2). Информация, прошедшая через приемопередатчики 49- 51, сопровождается соответствующим сигналом Выполнено (ВП). Регистры 71 и 72 сдвига служат для выработки сдвинутых относительно друг друга импульсов, используемых.для формирования управляющих сигналов блока 13 памяти. Регистр 79 периода аналогично регистру 37 периода представляет собой регистр памяти, служащий для запоминания кода полупериода следования фазосдвинутых импульсов, но информация, запоминаемая в регистре 79 каждого из блоков 13 памяти, сдвинута по времени относительно информации в регистре 37. Счетчик 80 периода, представляющий собой синхронный реверсивный счетчик, работает в режиме циклического вычитания содержимого счетчика в пределах от записанного кода полу периода до нуля и выдачи промежуточных значений кода через соответствующую шину 16 непосредственно в каналы 2 формирования последовательностей. Счетчик 81 адреса, представляющий собой синхронный двоичный счетчик, предназначен для записи, хранения и выдачи кода адреса на адресные входы ОЗУ1 82 и ОЗУ2 83. ОЗУ1 82 и ОЗУ2 83 служат для записи, хранения и считывания информации о фазовом сдвиге, . которая представляет собой последовательность кодов, каждый из которых соответствует фазовому сдвигу в диапазоне 0-360°, причем старший разряд указывает на принадлежность к диапазону 0-180° (при Лог.О) или 180-360° (при Лог.Г), а код, записанный в остальных разрядах, соответствующий фазовому сдвигу в пределах 180°, не должен превышать кода полупериода, записанного в регистрах 37 и 79 периода. При этом при обмене информацией с внешним устройством каждый блок 13 памяти имеет свой адрес, а ОЗУ1 82 и ОЗУ2 83 каждого из блоков 13 представляются внешнему устройству имеющими адреса 00... 0001...11 и 10...00-11...11 соответственно. В режиме формирования фазовых сдвигов информация считывается из всех ОЗУ1 и ОЗУ2 блоков 13i...13n/2 памяти параллельно, т.е. в этом режиме по одному адресу происхо0 дит считывание из всех ОЗУ преобразователя. Элементы ИЛИ 56 и 57 и инвертор 66 служат для формирования сигналов обращения к ОЗУ1 82 или ОЗУ2 83 в режиме обмена информацией с внешним устройст5 вом. Внутренняя двунаправленная шина 84 данных предназначена для двунаправленной передачи информации между МПП 49- 51 и для однонаправленной передачи данных из приемопередатчика 49 в регистр

0 79 периода или счетчик 81 адреса. В связи с чем, что в каждом цикле формирования фазосдвинутых последовательностей формируется фазовый сдвиг в диапазоне 0-180°, моменты считывания информации из ОЗУ1

5 и ОЗУ2 и записи ее в регистры 86 фазовращателей не должны совпадать при считывании из соседних ячеек памяти кодов, отличающихся в старшем разряде, поэтому в состав каналов 2i...2n формирования по0 следовательностей введены регистры 85 памяти,предназначенныедля промежуточного хранения информации, считанной из памяти, и регистры 86 фазовращателей, необходимые для хранения той

5 же информации о сдвиге фаз, но смена информации в которых происходит в моменты времени, зависящие от состояния старшего разряда кода. Схемы 87 сравнения предназначены для сравнения кодов, записанных в

0 регистры 86 фазовращателей с циклически изменяющимся кодом, поступающим из счетчиков 80 периода по шинам 16. Счетные триггеры 88 служат для формирования фазосдвинутых сигналов из импульсов, появ5 ляющихся на выходах схем 87 сравнения при равенстве кодов на его двух группах входов, т.е. схемы 87 сравнения и триггеры 88 в каждом из каналов образуют собственно фазовращатели. Инверторы 89 выполня0 ют функции буферов и предназначены для согласования выходов преобразователя с нагрузкой. Логические элементы 97,98,100, 106 и 108,- входящие в состав устройств 14 управления, предназначены для формиро5 вания импульсов записи в регистры 86 фазовращателей в зависимости от Старшего разряда кода. Триггеры 90-95 и логические элементы 96-105, 107, также входящие в состав устройств 14 управления, служат для формирования серий импульсов, разрешающих сравнение кодов схемами 87 сравнения.

Устройство работает следующим образом.

Перед началом работы внешним уст- ройством по шине 3 подается сигнал установкиисходногосостояния, устанавливающий в нулевое состояние составные части преобразователя. При этом на выходе регистра 6 устанавливается нуле- вой код и в мультиплексоре 5 открывается канал, имеющий нулевой адрес. Указанному адресу соответствует первый вход мультиплексора, присоединенный к шине Лог. 1 7, поэтому тактовые импульсы с выхода ге- нератора 1 или делителя 4 частоты не проходят на выход 5.1 мультиплексора и на указанном выходе появляется сигнал с уровнем Лог.1. Преобразователь может работать в двух режимах: начального про- граммирования и формирования фазосдви- нутых последовательностей импульсов. Рассмотрим первый режим (фиг.5). На шине 8 адреса-данных внешним устройством по адресу ХХ...ХХОООО устанавливается код ча- стоты(Р), при этом селектор 17 адреса вырабатывает сигналы ЗП и В КО, из которых на элементе ИЛИ-НЕ 20 формируется импульс 11.1 (фиг.5), производящий запись п-разряд- ного кода, поступающего по шине 8 в ре-- гистр 6. В соответствии с записанным в регистр 6 кодом открывается определенный канал мультиплексора и на его выходе 5.1 появляются тактовые импульсы, снимаемые с выхода генератора 1 или с одного из выхо- дов делителя 4 частоты (фиг.5, 5.1). Следующим шагом в этом режиме является запись кода полупериода фазосдвинутых сигналов в регистры 37 и 79 периода и в соответствующие им счетчики 38 и 90 периода. Для этого внешнее устройство по адресу XX,..XXOt10 подает код полупериода (Т/2). На выходах селектора 17 адреса появляются сигналы ЗП и В КЗ, используемые для формирования элементом ИЛИ 24 сигнала записи в регистры 37 и 79 периода и счетчики периода 38 и 80 (11.3) (фиг.5). На выходах триггеров 34 и 35 формируются два сдвинутых относительно друг друга импульса, по первому из которых происходит запись кода полупериода в регистр 37 периода, а по второму - в счетчик 38 периода (фиг.5, Q 38). Аналогичным образом на выходах триггеров 73 и 74 из сигнала 11.3 формируются два импульса, по первому из которых происхо- дит запись кода полупериода в регистры 79 периода, а по второму - в счетчики 80 периода (фиг.5, Q 80). При этом код полупериода передается из двунаправленной шины 8 во внутреннюю шику 84 через МПП 49, поэтому триггер 73 каждого из каналов 13i...13n/2 запускается снимаемым с выхода элемента ИЛИ 53 импульсом, появляющимся при наличии сигнала 11.3 записи и сигнала Выполнено, свидетельствующем о появлении кода полупериода на выходе МПП 49. Следующим шагом в этом режиме является запись информации о фазовом сдвиге в блоки 13i...13n/2 памяти. Рассмотрим вопрос о том, каким образом происходит кодирование указанной информации. При этом под кодированием понимается, установление взаимно однозначного соответствия между теоретически значением сдвига фаз с и соответствующим значением кода Ст в соответствии с формулой Ст (рс)0/б0;,

где d - требуемая дискретность формирования фазового сдвига, град.

Процесс кодирования предшествует режиму начального программирования и осуществляется во внешнем устройстве (например, в микроЭВМ). Пусть известно, что преобразователь работает на фазометры с усреднением с периодом усреднения Тусред 300 мкс, при этом известны законы изменения сдвига фаз в каждом из каналов формирования последовательностей. Рассчитаем теоретические значения сдвига фаз с дискретом времени, равным указанному периоду усреднения. Полученные значения сдвига фаз можно закодировать различными способами, отличающимися получаемой точностью кодирования. Простейший способ кодирования, дающий наименьшую точность, заключается в том, что для полученного теоретического значения сдвига фаз в соответствии с приведенной формулой рассчитывается значение кода Ст, которое аппроксимируется ближайшим целым значением кода Ск, т.е. Ск С + 0,5, где квадратные скобки означают операцию взятия целой части числа. С целью повышения точности кодирования разбивают период усреднения на к подинтервалов и кодируют теоретические значения сдвига фаз на каждом из подинтервалов аналогичным образом. При этом способе кодирования можно записать к - m/l, I 1 и имеет физический смысл количества соседних значений кода, которым кодируется теоретическое значение сдвига фаз на подинтервале. Таким образом к m и теоретическое значение сдвига фаз на интервале усреднения кодируется m значениями кода. Дальнейшее повышение точности кодирования может быть достигнуто при применении алгоритма эффективного кодирования, т.е. при разбиении интервала усреднения на k подинтервалов при I 1 (выражение I 1

означает, что каждое значение сдвига фаз на подинтервале кодируется несколькими соседними значениями кода). При использовании указанного алгоритма теоретическое значение кода на подинтервале Ст аппрок: симируется набором из I - х + у соседних целых значений кода в соответствии с формулой

. Ск «( + )/(х + у);

где х и у - число значений кода Ст и Ст+1 в наборе соответственно. Пусть, например, необходимо аппроксимировать полученное теоретическое значение кода на подинтервале Ст 16,32. При простейшем способе кодирования получим Ск 16,32 + 0,5 16, а при использовании алгоритма эффективного кодирования и I - 10 приведенная формула дает наиболее точный результат при х 7иу 3,т.е.Ск«(7 -16 + 3-17).3. Для получения наиболее точного приближения к теоретическому значению Ст 16,32 необходимо из 10 последовательно расположенных ячеек памяти считать 7 значений кода 16 и 3 значения кода 17. Для установления значений параметров I и к, при которых достигается наилучшее приближение усредненных значений сдвига фаз на интервале усреднения к соответствующим теоре- тическим значениям, проведено математическое моделирование, в ходе которого получены точностные параметры приближений при различных I и k. По результатам моделирования можно сделать вывод, что наилучшая точность кодирования реализуется при значениях I и k, близких друг к другу, т.е. для случая m - 30 возможны две комбинации значений I и k, обеспечивающих наилучшую точность: I 5, k 6Hl 6, k 5. Итак, для получения высокой точности приближения интервал усреднения должен быть разбит на k подин- тервалов, а для каждого подинтервала должна быть проведена кодировка соответствующего теоретического значения набором из I соседних значений кодов, т.е. усредненное значение кода на интервале усреднения складывается из m k I зна- чений кода. Это означает, что по сравнению с простейшим способом кодирования в m раз должны бьггь увеличены частота смены информации о фазовом сдвиге и емкость оперативных запоминающих устройств, входящих в состав каждого из блоков 2 памяти. Кодирование в соответствии с алго ритмом эффективного кодирования приводит к тому, что усредненное значение сдвига фаз на интервале усреднения является более точным значением (более близким к теоретическому значению), чем значение, полученное простейшим способом кодирования. Рассмотрим теперь вопрос о том, каким образом закодированная информация заносится в блоки памяти. В исходном состоянии на входах адреса оперативных запоминающих устройств ОЗУ1 82 и ОЗУ2 83 установлен адрес 00...00, так как перед началом работы счетчики 81 адреса были обнулены; блоки ОЗУ1 82 и ОЗУ 83 блоков 13 памяти находятся в режиме записи (на выходе 11.4 блока 11 управления присутствует уровень Лог.О). Первоначально происходит установка адреса в счетчиках 81 адреса каждого из блока 13 памяти. Для этого внешнее устройство по адресу ХХ...ХХ0100 подает код адреса 00...01 (А - 1). Селектором 17 адреса формируются сигналы ЗП и В К2, используемые для

формирования сигнала разрешения предварительной записи в счетчик 11.5 адреса и сигнала синхронизации счетчика (11.6) (на элементе ИЛИ 23)(фиг.5.11.5,11.6). Элементами ЗИ 67 и 68 формируются сигналы, поступающие соответственно на вход ВК и С1 МПП 49 и разрешающие передачу кода адреса через МПП 49 по внутренней шине 84 данных на информационные входы счетчика 81 адреса (фиг.5, Q 81). Код адреса записывается в счетчик по сигналу синхронизации (С), формируемому элементами ИЛИ-НЕ 63 и И 65. После установки адреса происходит запись кодов, соответствующих фазовым сдвигам в диапазоне 0-360° в ОЗУ1 82 блоков 13i...13n/2 памяти. Для этого внешнее устройство по адресу YY...YYOOOO устанавливает предназначенный для записи в ОЗУ1 блока 13i памяти код (код И), селектор 18 адреса, дешифровав поступивший адрес,

формирует сигналы ЗП и ВКО, передающиеся низким уровнем и поступающие в блок 13i памяти. Элементами ЗИ 67 и 68 вырабатываются сигналы, поступающие соответст- венно на входы ВК и С1, МПП 49 и

разрешающие прохождение информации через МПП 49 во внутреннюю шину 84 данных. Прошедшая информация, сопровождаемая сигналом Выполнено, через МПП 50 (так как ВК 0 и CI - О), поступает по

шине I5i на входы-выходы данных ОЗУ 82 (фиг.5, D ОЗУ10. Параллельно с этим на выходе элемента ИЛИ 64 формируется сигнал Лог.О, поступающий на установочный вход регистра 71 сдвига. Регистр 71 сдвига

формирует два задержанных относительно друг друга сигнала.

Первый сигнал, проходя через элементы ИЛИ 60 и ЗИ 70, поступает на вход выборки кристалла ОЗУ1 (СЕ), разрешая

запись поступающей по шине 15i информации в ОЗУ1 (фиг.5. СЕОЗУ11).

Второй сигнал, задержанный на время, необходимое для окончания записи информации в ОЗУ1, проходя через элемент 2И- НЕ с открытым коллектором 76 (11.13), используется для формирования инвертором 42 и элементом 2И 43 сигнала, поступающего на вход готовности (ГОТ) селектора 18 адреса и свидетельствующего об оконча- нии цикла записи информации (фиг.5, 11.13). Селектор 18 адреса, получив сигнал ГОТ, устанавливает сигнал ОТВ (9.4), извещающий внешнее устройство об окончании цикла. Элементы 2И-НЕ 76 выполнены с отк рытым коллектором, для того чтобы обеспечить схему МОНТАЖНОЕ ИЛИ для (п/2) сигналов 11.13, снимаемых с блоков 13i...13n/2 памяти. После того, как закончена запись информации по адресу 00...01 ОЗУ1 блока 131 памяти, аналогичным образом происходит запись информации (код 12...код 1п/2) по указанному адресу в ОЗУ1 82 блоков 132...13п/2 памяти (фиг.5, D ОЗУ1а,, СЕОЗУ12). При этом внешнее уст- ройство последовательно устанавливает коды сдвига фаз по адресам YY...YY0010, YY...YY0100 и т.д.. о завершении каждого цикла записи свидетельствует появление сигнала ОТВ (9.4). По завершении записи информации в ячейки ОЗУ1 82 блоков 13i...13n/2 памяти с адресами 00...01 аналогичным образом устанавливаются следующие адреса (2...N) и происходит запись информации (код 2i... код 2п/2, код 3i... код Nn/2) по установленным адресам в соответствующие ячейки ОЗУ1 82 блоков 13i...13n/2 памяти. После того, как вся необходимая информация записана в ОЗУ1 каждого из блоков 13 памяти, происходит запись кодов сдвига фаз (код 1п/2+1... код 1П, код 2п/2+1... код Nn) в ОЗУ2 83. Все операции осуществляются аналогичным образом, за исключением:

запись происходит, начиная с адреса 10...01;

передача информации из внутренней шины 84 на входы-выходы данных ОЗУ2 83 происходит через МПП 51 по шинам 152k,1

сигналы СЕ ОЗУ2, разрешающие за- пись поступающих по шинам 152k данных, формируются элементами ИЛИ 59 и ЗИ 69.

По завершении записи информации в ОЗУ1 82 и ОЗУ2 83 всех блоков 13i...13n/2 памяти происходит программирование внешним устройством таймера 19;

в регистр состояний (PC) заносится код режима (R) (фиг.5, РС(19)), означающий что запуск счетчиков СТ1 и СТ2 таймера будет происходить под действием тактирующих

сигналов С1, С2 соответственно, счетчик СТ1 будет работать в режиме программируемого делителя частоты, а СТ2 - в режиме интервального таймера;

в счетчик СТ1 заносится код, соответствующий числу полупериода фазосдвинутых сигналов, через которое должна происходить смена информации в каналах 2i...2n формирования последовательностей;

в счетчик СТ2 заносится код, соответствующий числу циклов считывания информации из блоков памяти, т.е. максимальному адресу (N), по которому происходит обращение к блокам памяти в течение одного опыта.

Предположим, что теоретически рассчитаны и занесены в ОЗУ 1 82 и ОЗУ2 83 блоков 13i...13n/2 памяти по N значений кодов сдвигов фаз, период смены фазового сдвига должен быть не более Тем, частота фазосдвинутых сигналов должна составлять fCm. При таких условиях в счетчик СТ1 необходимо занести код, соответствующий числу полупериодов I 2-fcrH TcM, а в счетчик СТ2 - код, соответствующий максимальному адресу N. По завершении программирования рабочей частоты F, регистров 37 и 79 и счетчиков 38 и 80 периода, блоков 13i...13n/2 памяти и таймера 19 начинается второй режим работы преобразователя-формирование фазосдвинутых последовательностей (временные диаграммы, фиг.6). Для этого внешнее устройство устанавливает нулевой адрес в счетчиках 81 адреса каждого из блоков 13i...13n/2 памяти (фиг.6, 081) и переводит их в режим считывания, устанавливая триггер 33 (выход 11,4 блока 11 управления в состояние Лог.1 путем подачи по адресу ХХ...ХХ0010 кода 00...01 (фиг.6, 11.4). Далее внешнее устройство подает команду Пуск, устанавливая по адресу ХХ...ХХ1010 код 00...01, при этом селектор 17 адреса формирует сигналы ЗП и ВК4, передающиеся низким уровнем, на выходе элемента ИЛИ-НЕ 22 появляется импульс (фиг.6, Q22), по которому происходит запись состояния разряда 8.1 (т.е. Лог.Г) в триггер 36 (фиг.6, 036). По этому сигналу, поступающему на вход разрешения счета счетчика 38 периода, запускается указанный счетчик, работающий в режиме вычитания. По достижении счетчиком нулевого состояния импульсом с выхода индикации нулевого состояния, прошедшим через элемент И 45, происходит очередная запись в счетчик 38 кода полупериода, хранящегося в регистре 37 периода, запуск мультивибратора 48 (фиг.6, О 48) и счет продолжается. .Частота импульсов, появляющихся на выходе индикации нулевого состояния, равна удвоенной требуемой частоте фазосдвинутых сигналов на выходе преобразователя. Импульсами с инверсного выхода мультивибратора 48 запускается счетчик СТ1 таймера 19. По прохождению числа импульсов с выхода мультивибратора 48, соответствующих коду деления частоты счетчика СТ1, на первом выходе таймера 19 циклически формируются импульсы смены информации. На временной диаграмме фиг.6 (Q1 19) показан случай, когда смена информации происходит через 6 полупериодов. Регистры 26, 28-32 сдвига и инверторы 39 и 40 образуют распределитель импульсов, формирующий управляющие импульсы 11.7...11.12 в каждом цикле смены информации. Назначение сигналов 11.7...11.12 следующее:

увеличение содержимого счетчика 81 адреса на 1 (фиг.6, 11.7);

выбор кристалла памяти (фиг.6, 11.8); запись в регистр 85 памяти каждого из каналов 2i...2n формирования последовательностей (фиг.6, 11.9);

запись информации в регистры 86 фазовращателей каждого из каналов 2i...2n в начале цикла смены информации (11.10) (фиг.6, 11.10) или через промежуток времени, равный длительности полупериода фазосдвинутых последовательностей (11.12) (фиг.6, 11.12);

пуск режима формирования последовательностей (11.11) (фиг.6, 11.11). По сигналу 11.7, прошедшему через элемент ИЛИ 63, в каждом цикле смены информации происходит увеличение содержимого счетчиков 81 адреса на 1, а по сигналу 11.8, прошедшему через элементы ЗИ 69 и 70, информация о полном фазовом сдвиге в диапазоне 0-360° параллельно считывается из ячеек ОЗУ1 82 и ОЗУ2 83 каждого из каналов 13i...13n/2 no установленному адресу. Считанная информация по сигналам 11,9 запоминается в регистрах 85 памяти каналов формирования последовательностей 2i...2n (фиг.6, Q 85). Сигналы с выходов старшего разряда каждого из регистров 85 памяти поступают в устройство 14 управления, где используются для формирования импульсов записи в регистры 86 фазовращателей и серий импульсов, разрешающих сравнение кодов схемами 87 сравнения. При сигнале Лог.О на выходе старшего разряда запись кода сдвига фаз в регистры 86 фазовращателей происходит по импульсам 11.10, прошедшим через элементы 106 или 108 в начале диапазона 0-180°, а при сигнале Лог. Г запись кода происходит по импульсам 11.12 в начале диапазона 180-360°, что иллюстрируется временными диаграммами на фиг,7. Для исключения неоднозначности измерения фазового сдвига присоединенными к выходам преобразователя фазометрами при переходах из диапазона в диапазон принято соглашение, что после момента перехода из диапазона в диапазон в течение времени, равного полупериоду фазосдвину- того сигнала, фазовый сдвиг не формируется. Для этого на выходах элементов И-ИЛИ-НЕ 105 и 107 формируются сигналы

запрета сравнения (фиг.7, Q 105), которые запрещают в указанные моменты времени прохождение тактовых импульсов 5.1 через элементы И 103 и 104 на входы разрешения сравнения схем 87 сравнения. В связи с

указанным соглашением на временных диаграммах (фиг.7) пропущен импульс 9 сигнала U2k-i. В разрешенные для сравнения моменты времени при совпадении установленного в регистрах 86 фазовращателей кода с циклически изменяющимся параллельным кодом поступающим по шинам 16с выходов счетчиков 80 периода схемы 87 сравнения, вырабатывают на выходах импульсы равенства (фиг,7, Q 87), из которых счетными триггерами 88 формируются фазосдвинутые сигналы в диапазоне изменения фазового сдвига 0-360°. При этом цикличность работы счетчиков 80 периода обеспечивается тем, что счетчики работают

в режиме вычитания и по достижении счетчиком нулевого состояния (фиг.7, О 80) импульсом с выхода индикации нулевого состояния, прошедшим через элемент И 78, происходит очередная запись в счетчик 80

кода полупериода, хранящегося в регистре 79 периода, и счет продолжается. На временных диаграммах (фиг.7) изображены выходные сигналы U2k-i и U2k, снимаемые с выходов инверторов 89, причем фазовые

сдвиги pi ...фь сигнала U2k-i представлены относительно сигнала U2k, выбранного в качестве опорного (опорный сигнал с нулевым фазовым сдвигом может быть получен путем занесения во все ячейки ОЗУ

одного из каналов того же кода, что и в регистры периода). При этом количество каналов опорных сигналов (по) и каналов формирования сдвинутых по фазе последовательностей (пс) выбирается исхо0 дя из требований конкретного применения так, что по + пс п.

Формирование фазосдвинутых сигналов продолжается до тех пор пока на втором выходе (Q2) таймера 19 не появится сигнал

5 с уровнем Лог.О, свидетельствующий о достижении счетчиком 2 таймера 19 нулевого состояния (фиг.7, Qa 19), т.е. о том, что счетчик 2 отсчитал запрограммированное число циклов считывания информации. Указанным сигналом запускается регистр 27 сдвига и на выходе элемента 2И 44 появляется импульс, который устанавливает исходное состояние Лог.1 на втором выходе таймера 19 и сбрасывает триггер 36, что означает установку сигнала 11.2 Пуск/Стоп в состояние Стоп. При этом элементом 46 запрещается прохождение импульсов с выхода мультивибратора 48 на тактовый вход С1 счетчика 1 таймера 19 и формирование фазос- двинутых сигналов Ui...Un прекращается.

Выполнение устройства согласно изобретению позволяет реализовать многоканальный программируемый преобразователь код-фаза, ориентированный на использова- ние совместно с микроЭВМ и позволяющий осуществлять формирование фазосдвинутых сигналов, требующих высокой частоты смены фазового сдвига. Прототип также ориентирован на использование совместно с микро- ЭВМ, однако частота смены фазового сдвига на выходах каналов формирования последовательностей ограничена скоростью передачи информации по интерфейсу связи из микроЭВМ в регистры памяти каналов, ко- торая всегда значительно меньше скорости циклического считывания из блоков памяти, в которые предварительно занесена информация; зависит от числа каналов формирования последовательностей и уменьшается при увеличении числа каналов п.

Пример. Пусть скорость передачи информации из микроЭВМ в регистры памяти каналов составляет 100 Кслов/с, что является, например, предельно допустимой скоростью для микроЭВМ типа Электрони- ка-60. Число каналов формирования последовательностей п возьмем равным 10. При таких условиях максимально возможная частота смены фазового сдвига на выходах каналов составит 10 кГц (период смены Тем 100 мкс). Теперь предположим, что преобразователь работает на фазометры с усреднением с периодом усреднения Тусред 300 мкс, частота тактовых импульсов Ртакт 20 МГц, частота фазосдвинутых сигналов fc™ 400 кГц. При таких условиях число дискретов фазового сдвига в пределах 0-360° составит Ртакт/fc 50, т.е. один дискрет соответствует 7,2° и число усредняемых значений сдвига фаз ТуСред/Тизм 3. Возможные методы повышения точности усредненных значений сдвига фаз на интервале усреднения состоят в увеличении числа дискретов фазы и. числа усредняемых значе- ний сдвига фаз. При построении преобразователя в соответствии с изобретением число усредняемых значений сдвига фаз в интервале усреднения может изменяться в широких пределах, что определяется программируемой частотой считывания информации из блоков памяти. При запрограммированной частоте считывания 100 кГц (Тизм 10 мкс) число усредняемых значений сдвига фаз составит Тусред/Тизм 30. Число дискретов фазы при заданной частоте фазосдвинутых сигналов fcm 400 кГц может быть увеличено повышением тактовых импульсов Ртакт, НО Ртакт 20 МГц является частотой, близкой к максимально возможной для применяемой элементной базы, поэтому дальнейшее повышение точности усредненных значений сдвига фаз осуществляется путем реализации алгоритма эффективного кодирования, рассмотренного ранее.

Формула изобретения

1. Многоканальный программируемый преобразователь код-фаза, содержащий генератор тактовых импульсов/выход которого соединен с входом делителя частоты и первым информационным входом мультиплексора, второй информационный вход которого является шиной логической единицы, информационные входы с третьего по (1+2)-й включительно соединены с соответствующими из t выходов делителя частоты, адресные входы подключены к соответствующим выходам регистра, а выход соединен с первым входом синхронизации блока управления, первый выход первой группы выходов которого соединен с тактовым входом регистра, входы строба адреса и сигнала записи являются соответственно входными шинами строба адреса и сигнала записи, а вход установки исходного состояния является входной шиной установки исходного состояния и объединен с одноименными входами п каналов формирования последовательностей, информационные выходы которых являются соответствующими информационными выходными шинами, отличающийся тем, что, с целью повышения быстродействия, в него введены двунаправленная шина адресов-данных, п/2 устройств управления и п/2 блоков памяти, первые и вторые входы-выходы данных 1-го блока памяти, где 1 1,2, .... п/2 соответственно соединены с соответствующими входами-выходами данных 24- го и (2-i-1)-ro каналов формирования последовательностей, группа выходов соединена с соответствующими входами группы входов 2-1-го и (2«(-1)-го каналов формирования последовательностей, а третьи входы-выходы данных объединены с соответствующими входами-выходами адресов данных блока управления и соединены с соответствующими входами-выходами двунаправленной шины адресов-данных и являются входной-выходной шиной адресов-данных, первый выход делителя соединен с первыми входами синхронизации п/2 блоков памяти и вторым входом синхронизации блока управления, входы установки адреса которого являются входной шиной адреса, второй выход первой группы выходов соединен с входами пуска п/2 устройств управления и с первыми входами пуска п/2 блоков памяти, выходы с третьего по восьмой включительно первой группы выходов блока управления соединены соответственно с входами строба периодов, записи-чте- ния. записи адреса, строба адреса, инкрементации адреса и выбора кристалла п/2 блоков памяти, вход сброса первого из которых объединен с входами сброса остальных (п/2-1) блоков памяти, регистра, с входами установки исходного состояния п/2 устройств управления и с входом установки исходного состояния блока управления, третий вход синхронизации которого соединен с вторым выходом делителя часто- ты, первый вход синхронизации объединен с входами синхронизации п/2 устройств управления и с вторыми входами синхронизации п/2 блоков памяти, выходы с девятого по двенадцатый включительно первой труп- пы выходов блока управления соединены соответственно с входами строба данных п каналов формирования последовательностей, с входами первого строба данных п/2 устройств управления, вторыми входами пу- ска п/2 блоков памяти и входами второго строба данных п/2 устройств управления, выход окончания ввода-вывода первого блока памяти объединен с одноименными входами остальных (п/2-1) блоков памяти и подключен к одноименному входу блока управления, выходы с первого по n/2-й второй группы выходов которого соединены с входами выбора канала соответствующего блока памяти, (п/2+1)-й и (п/2+2)-й выходы второй группы выходов блока управления соответственно соединены с первым и вторыми входами управления направлением передачи п/2 блоков памяти, выход и вход чтения блока управления являются соответ- ственно выходной шиной сигнала ответа и входной шиной сигнала чтения, информационные входы регистра соединены с соответствующими вход-выходами двунаправленной шины адресов-данных, выходы с первого по четвертый 1-го устройства управления соединены соответственно с входами записи 2 1-го и ()-го и с входами сравнения 2-l-ro и (2-1-1)-го каналов формирования последовательностей, выходы старших разрядов которых соединены соответственно с первым и вторым входами старших разрядов устройств управления.

2. Преобразователь по п. 1, от л и ч a rout и и с я тем, что блок управления выполнен в виде первого и второго селекторов адреса, с первого по третий элементов ИЛИ-НЕ, первого и второго элементов ИЛИ, с первого по восьмой регистров сдвига, с первого по четвертый триггеров, регистра периода, счетчика периода, с первого по четвертый инверторов, с первого по четвертый элементов И, элемента И-НЕ, мультивибратора и двухкзнального программируемого таймера, вхзды-выходы данных которого объединены с соответствующими входами данных регистра периода, с соответствующими входами-выходами адресов-данных первого и второго селекторов адресов и являются соответствующими входами-выходами адресов-данных блока, первый вход сброса объединен с входами сброса с первого по восьмой включительно регистров сдвига, регистра периода, первого, второго и третьего триггеров, мультивибратора, с первым входом второго элемента И и является входом установки исходного состояния блока, второй вход сброса обьединен с входом сброса четвертого триггера и подключен к выходу второго элемента И, а первый вход синхронизации соединен с выходом четвертого элемента И, первый вход которого подключен к прямому выходу четвертого триггера и является вторым выходом первой группы выходов блока, а второй вход соединен с инверсным выходом мультивибратора, прямой выход которого соединен с установочным входом восьмого регистра сдвига, а установочный вход обьединен с входом записи счетчика периодов и подключен к выходу третьего элемента И, первый вход которого подключен к прямому выходу третьего триггера, а второй вход соединен с выходом переноса нулевого состояния счетчика периода, вход синхронизации которого обьединен с входами синхронизации пятого, шестого, седьмого регистров сдвига и является первым входом синхронизации блока, вход разрешения счета подключен к инверсному выходу четвертого триггера, а входы данных соединены с соответствующими выходами регистра периода, вход за писи которого объединен с установочным входом третьего триггера и подключен к инверсному выходу второго триггера, вход синхронизации которого объединен с входами синхронизации третьего триггера, первого, второго и третьего регистров сдвига и является вторым входом синхронизации блока, а установочный вход является