Изобретение относится к импульсной технике-и может быть использовано в устройствах обработки информации.

Целью изобретения является повышение точности измерения разности длительностей наносекундных интервалов.

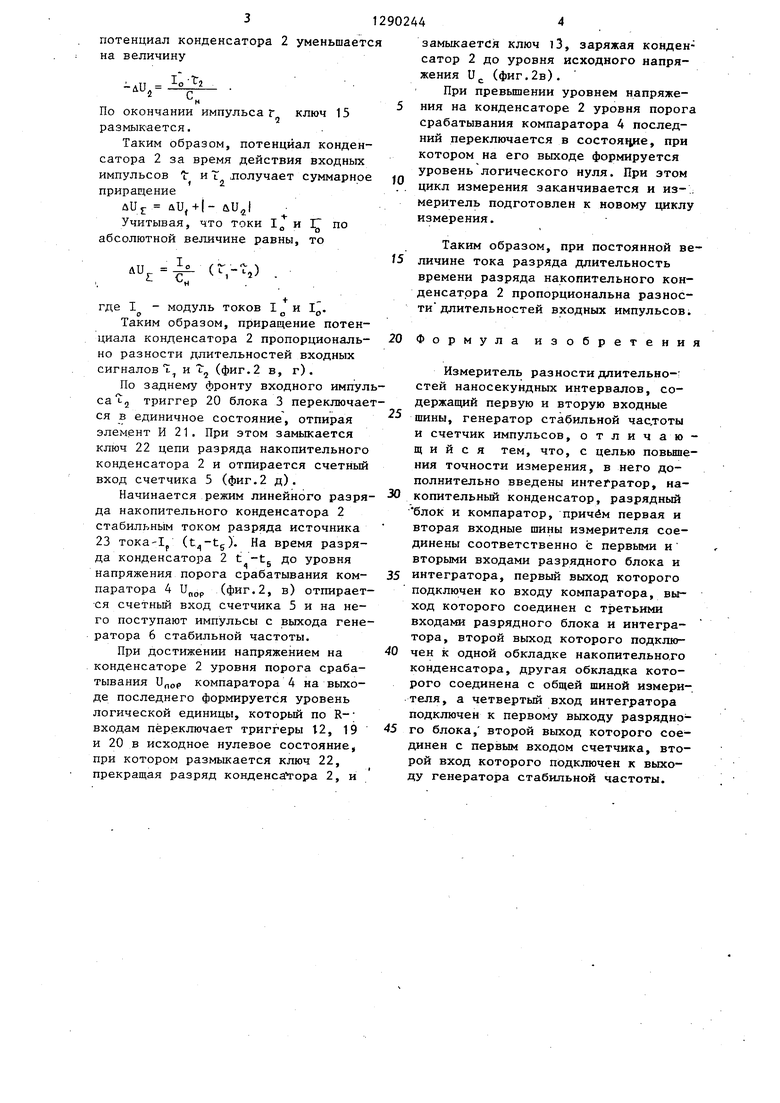

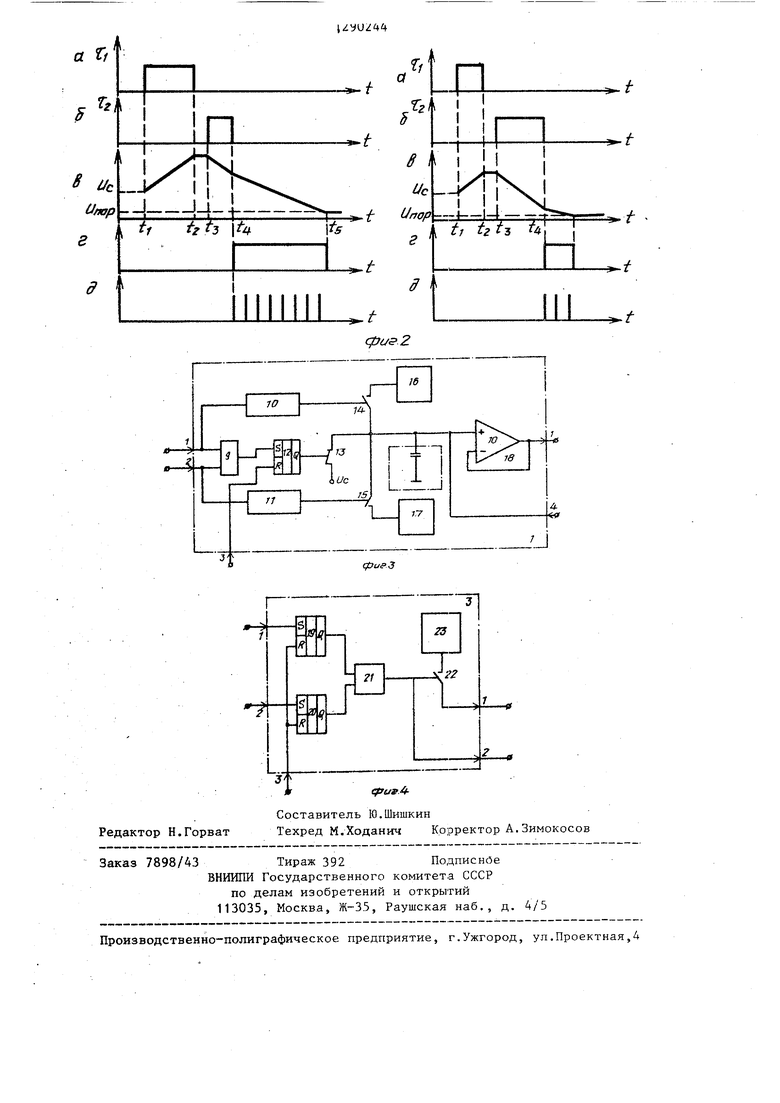

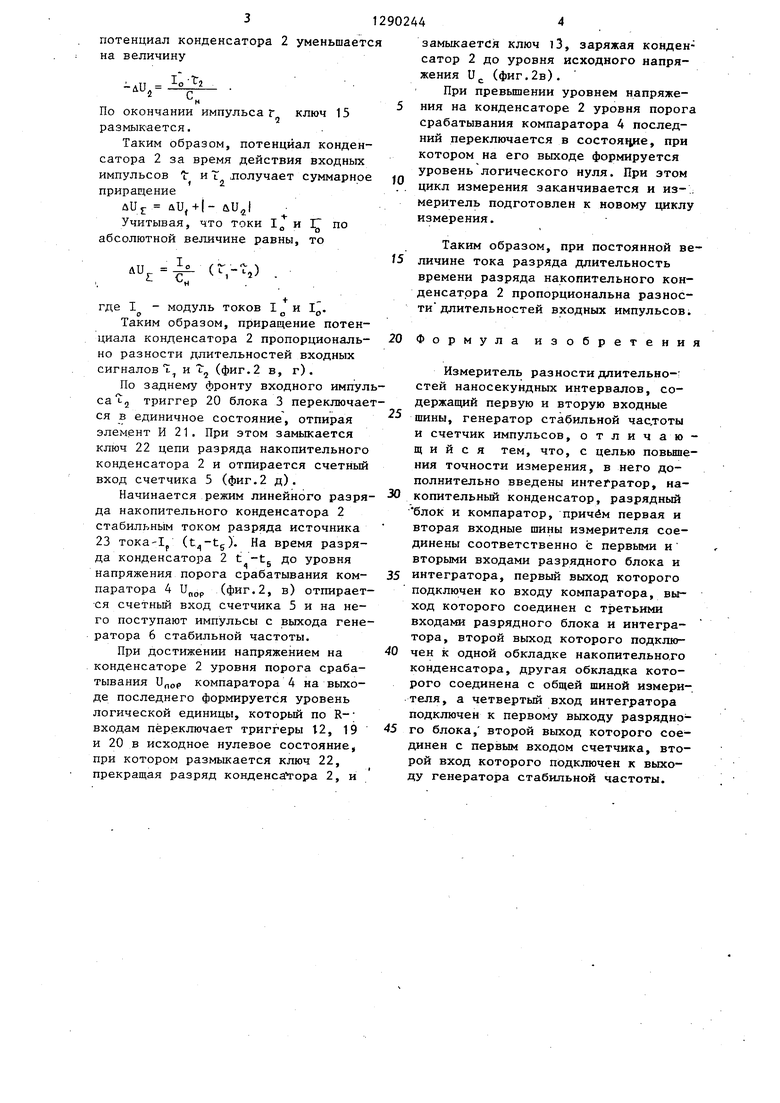

На фиг.1 представлена структурная схема измерителя разности длительностей наносекундных интервалов, на фиг.2 - временные диаграммы, поясняющие его работу; на фиг.З и 4 - структурные схемы соответственно интегратора и разрядного блока.

Измеритель (фиг.1) содержит интегратор 1, накопительньй конденсатор 2, разрядный блок 3, компаратор 4, счетчик 5, генератор 6 стабильной частоты, входные шины 7 и 8.

Входные шины 7 и 8 измерителя соединены соответственно с первым и вторым входами разрядного блока 3 и интегратора 1, первый выход которого через компаратор 4 подключен к третьим входам интегратора 1 и разрядного блока 3, второй выход которого соединен с первым входом счетчика 5 второй вход которого подключен к выходу генератора 6 стабильной частоты, причем первый выход разрядного блока 3 соединен с четвертым входом интегратора 1, а накопительный конденсатор 2 подключен ко второму выходу интегратора 1.

Интегратор 1 (фиг.З) может быть выполнен на элементе ИЛИ 9, элементах 10 и 11 задержки, RS-триггере 12, управляемых ключах 13-15, источниках 16 и 17 тока и повторителе 18 напряжения. Первый и второй входы интеграто ра. через элементы задержки 10 р 11 подключены соответственно к управляемым входам ключей 15, 14 и через элемент ИЛИ 9 к S-входу RS- триггера 12,.К-вход которого соединен с третьим входом интегратора, а прямой выход подключен к управляемому входу ключа 13. Первый вход повторителя 18 напряжения подключен к четвертому входу и второму выходу интегратора, а через сигнальные контак .ты ключей 13-15 соединен соответственно с источником опорного напряжения, источниками 16 и 17 тока, а второй вход повторителя 1.8 подключе к его выходу, которьй является первым выходом интегратора.

5

0

5

0

Разрядный блок 3 (фиг.4) может быть выполнен- на RS-триггерах 19 и 20, элементе И 21, управляемом ключе 22 и источнике 23 тока разряда.

Первый и второй входы разрядного блока соединены с S-входами соответственно RS-триггеров 19 и 20,, прямые выходы которых через элемент И 21 подключены к управляемому входу ключа 22 и второму выходу разрядного блока, выход источника 23 тока разряда через сигнальные контакты ключа 22 соединен с первым выходом разрядного блока, третий вход которого подключен к объединенным R.-BXO- дам RS-триггеров 19 и 20.

Измеритель работает следующим образом.

В исходном состоянии ключи 14, 15 и 22 разомкнуты, ключ 13 замкнут, конденсатор 2 заряжен до уровня И, (в интеграторе 1 и блоке 3), счетчик 5 обнулен, на выходе компаратора 4 формируется уровень логического нуля.

В течение длительности входного импульЬа l() (фиг.2а,б), поступающего на шину 7 измерителя, накопительньй конденсатор 2 подключается ключом 14 к источнику 16 стабильного положительного тока 1. Потенциал конденсатора 2 при этом получает положительное приращение,рав35

ное

ди il:b

0

5

0

5

где С - емкость накопительного конденсатора 2.

При поступлении входного импульса L , триггер 12 через элемент ИЛИ 9 интегратора 1 переключается в единичное состояние и разрывает контакты ключа 13, отключая источник опорного напряжения U от накопительно- го конденсатора 2. Одновременно триггер 19 разрядного блока 3 по заднему фронту входного импульса переключается в единичное состояние, подготавливая к отпиранию элемент И 21 блока 3.

По окончании длительности импульса t ключ 14 размыкается. Заряд конденсатора 2 заканчивается.

На время действия HMnynbca1( ) конденсатор 2 подключается ключом 15 к источнику 17 стабильного отрицательного тока 1о, в результате чего

потенциал конденсатора на величину

2 уменьшается

1.-Г.

,

По окончании импульса г ключ 15 размык-ается.

Таким образом, потенциал конденсатора 2 за время действия входных импульсов t и приращение

uUj; аи,+j- ли

Учитывая, что токи 1 и 1 по абсолютной величине равны, то

тт-1- П ч

ли - (L,-,) .

L лолучает суммарное

1;и

-о

где I - модуль токов

Таким образом, приращение потенциала конденсатора 2 пропорционально разности длительностей входных сигналов 1, и t (фиг.2 в, г),

По заднему фронту входного импулса LJ триггер 20 блока 3 переключаеся в единичное состояние, отпирая элемент И 21, При этом замыкается ключ 22 цепи разряда накопительного конденсатора 2 и отпирается счетный вход счетчика 5 (фиг.2 д).

Начинается режим линейного разряда накопительного конденсатора 2 стабильным током разряда источника 23 тока-Хр (). На время разряда конденсатора 2 t -tg до уровня срабатывания

порога срабатывания ком- и„„„ (фиг.2, в) отпираетнапряженияпаратора 4 „„ ся счетный вход счетчика 5 и на него поступают импульсы с выхода генератора 6 стабильной частоты.

При достижении напряжением на конденсаторе 2 уровня порога срабатывания УПОР компаратора 4 на выходе последнего формируется уровень логической единицы, который по R- входам переключает триггеры 12, 19 и 20 в исходное нулевое состояние, при котором размыкается ключ 22, прекращая разряд конденса/тора 2, и

замыкается ключ i3, заряжая конденсатор 2 до уровня исходного напряжения и (фиг.2в).

При превышении уровнем напряжения на конденсаторе 2 уровня порога срабатывания компаратора 4 последний переключается в состояцне, при котором на его выходе формируется уровень логического нуля. При этом цикл измерения заканчивается и измеритель подготовлен к новому циклу измерения.

Таким образом, при постоянной величине тока разряда длительность времени разряда накопительного конденсатора 2 пропорциональна разности длительностей входных импульсов.

Формула изобретения

Измеритель разности длительно-: стей наносекундных интервалов, содержащий первую и вторую входные

шины, генератор стабильной частоты

и счетчик импульсов, о щ и и с я тем, что, с ния точности измерения.

т л и ч а ю - целью повьнпе- в него дополнительно введены интегратор, накопительный конденсатор, разрядный блок и компаратор, причём первая и вторая входные шины измерителя соединены соответственно е первыми и вторыми входами разрядного блока и

интегратора, первый выход которого подключен ко входу компаратора, выход которого соединен с третьими входами разрядного блока и интегратора, второй вькод которого подключен к одной обкладке накопительно.го конденсатора, другая обкладка которого соединена с общей шиной измерителя, а четвертый вход интегратора подключен к первому выходу разрядного блока, второй выход которого соединен с первым входом счетчика, второй вход которого подключен к выходу генератора стабильной частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор | 1982 |

|

SU1062726A1 |

| ИНТЕГРИРУЮЩИЙ ИЗМЕРИТЕЛЬ ОТНОШЕНИЯ ДВУХ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1992 |

|

RU2032884C1 |

| Измеритель частоты и отношения частот | 1986 |

|

SU1345131A1 |

| Измеритель временных интервалов | 1987 |

|

SU1550471A1 |

| Измеритель коэффициента нелинейности пилообразного напряжения | 1980 |

|

SU894607A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1986 |

|

SU1473083A1 |

| Система автономного электроснабжения | 1985 |

|

SU1343537A1 |

| Дискретно-аналоговый интегратор | 1986 |

|

SU1372337A1 |

| ИЗМЕРИТЕЛЬ СКОРОСТИ ЗВУКА | 1998 |

|

RU2152597C1 |

| Измеритель флуктуации периода и фазы электрических колебаний | 1977 |

|

SU679892A1 |

Изобретение может быть использовано в устройствах обработки информации. Цель изобретения - повышение точности измерения разности длительности наносекундных интервалов. Измеритель содержит счетчик 5, генератор 6 стабильной частоты и шины 7 и 8. Введение интегратор 1, накопительного конденсатора 2, разрядного блока 3 и компаратора 4 позволяет при постоянной величине тока разряда иметь длительность времени разряда накопительного конденсатора 2 пропорциональной разности длительностей входных импульсов. 4 ил. . (Л со о N9 4 4 cfruff.i

| Устройство для определения разности временных интервалов | 1981 |

|

SU983632A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-02-15—Публикация

1985-06-18—Подача